ISE原理图输入方法

FPGA详细教程基于ISE52的输入方法

原理图符号的放置

设计需要的是一个两输入的异或门(xor2)和一 个两输入的与门(and2)。在Symbols窗口中找到and2 然后选择Add Symbol,于是鼠标上出现了and2的 原理图符号,在绘图区中单击鼠标左键便可以将 “and2”放在任何地方。或者也可以在Symbols窗口中 单击“and2”也可以完成原理图符号的放置。同样的 方法放置好“xor2”。单击工具栏中的 可以放大 显示。放大后如图所示。

放置好端口的半加器

对象属性设置

完成端口放置后, 要为每一个端口取一个 名称。单击工具栏中 的 ,然后双击一个端 口,跳出如右图所示的 Object Properties(对象 属性对话框)。在 Name ( 名 称 ) 属 性 的 Value ( 属 性 值 ) 中 键 入A。

端口方向设置

同时也可以在PortPolarity(端口方向属性)的 Value中设定端口的方向。单击OK完成端口属性的 设定。用同样的方法完成所有端口名称的设定,设 定好的端口如下图所示。

电气连线

放置好了原理图,下一步就是根据逻辑表达 式进行电气连线。单击工具栏中的 或者选择 Add Wire,然后如Fra bibliotek图所示画好连线。

画好连线的原理图

标注输入输出端口

单击工具栏中的 或者选择Add I/O Marker都 可以在相应的节点放置出输入输出端口,端口是输 入还是输出可以从左边的Option选项中选择:Add a input marker(输入),Add a output marker(输出), Add a bidirectional marker(输入输出),Remove the marker(删除端口)。如图所示。

生成的ECS工作环境

ISE使用指南(输入)

第4章ISE开发环境使用指南第1节ISE套件的介绍与安装4.1.1 ISE简要介绍Xilinx是全球领先的可编程逻辑完整解决方案的供应商,研发、制造并销售应用范围广泛的高级集成电路、软件设计工具以及定义系统级功能的IP(Intellectual Property)核,长期以来一直推动着FPGA技术的发展。

Xilinx的开发工具也在不断地升级,由早期的Foundation 系列逐步发展到目前的ISE 9.1i系列,集成了FPGA开发需要的所有功能,其主要特点有:∙包含了Xilinx新型SmartCompile技术,可以将实现时间缩减2.5倍,能在最短的时间内提供最高的性能,提供了一个功能强大的设计收敛环境;∙全面支持Virtex-5系列器件(业界首款65nm FPGA);∙集成式的时序收敛环境有助于快速、轻松地识别FPGA设计的瓶颈;∙可以节省一个或多个速度等级的成本,并可在逻辑设计中实现最低的总成本。

Foundation Series ISE具有界面友好、操作简单的特点,再加上Xilinx的FPGA芯片占有很大的市场,使其成为非常通用的FPGA工具软件。

ISE作为高效的EDA设计工具集合,与第三方软件扬长补短,使软件功能越来越强大,为用户提供了更加丰富的Xilinx平台。

4.1.2 ISE功能简介ISE的主要功能包括设计输入、综合、仿真、实现和下载,涵盖了FPGA开发的全过程,从功能上讲,其工作流程无需借助任何第三方EDA软件。

∙设计输入:ISE提供的设计输入工具包括用于HDL代码输入和查看报告的ISE文本编辑器(The ISE Text Editor),用于原理图编辑的工具ECS(The Engineering Capture System),用于生成IP Core的Core Generator,用于状态机设计的StateCAD以及用于约束文件编辑的Constraint Editor等。

∙综合:ISE的综合工具不但包含了Xilinx自身提供的综合工具XST,同时还可以内嵌Mentor Graphics公司的LeonardoSpectrum和Synplicity公司的Synplify,实现无缝链接。

ISE使用教程(修改稿)

点击project菜单的New Source

设计输入

• 要完成这个计数器模块,可以在ISE自动生成的代 码框架基础上通过自己编写代码完成,也可使用 ISE的语言模板(ISE Language Template)工具 来完成。 • 选择Edit->Language Template或者通过点击工 具栏中最右端的灯泡按钮 来打开语言模板。 在语言模版(Language Template )窗口中,有 很多Xilinx提供的参考代码片断,找到需要的 counter代码片断。

保存后进行功能仿真

仿真结果

下载验证

在生成可用于下载的Bit流文件前,必须生成ucf约 束文件,否则生成的bit流文件将无法在硬件上正 常运行。 约束文件中可包含:时序约束,周期约束,偏移 约束,管脚约束等。其中管脚约束是必不可少的, 它将你设计文件中的I/O与实际硬件管脚进行关联。 管脚约束可调用ISE的PASE工具实现。 最后使用ISE IMPACT工具通过JTAG口下载bit流 至硬件。

管脚约束源文件的建立

管脚约束文件的建立

3.在此编辑窗口进行管脚约束编写 例如:net "ckout(3)" loc="k12"; net "ckout(2)" loc="p14"; net "ckout(1)" loc="l12"; net "ckout(0)" loc="n14"; net "clk" loc= "t9" ; net"direction" loc = "f12";

1.选中

2.双击 编写完成后保存

ISE软件使用说明(两篇)

引言:概述:ISE软件是由Xilinx公司开发的一款集成电路设计工具,使用该软件可以进行数字电路设计、仿真、验证以及实现等多个阶段的工作。

在设计阶段,ISE软件提供了丰富的组件库和设计工具,方便用户进行电路原理图的绘制和逻辑设计。

在验证阶段,ISE软件可以进行功能仿真和时序仿真,以确保设计的正确性和稳定性。

在实现阶段,ISE软件提供了先进的布局与布线工具,能够将设计转化为实际的电路板。

正文内容:1.安装与启动1.1ISE软件安装包1.2安装ISE软件1.3启动ISE软件2.项目管理2.1创建新项目2.2导入已有项目2.3添加设计文件2.4设定项目属性2.5保存和备份项目3.设计流程3.1电路原理图设计3.1.1组件选择3.1.2连接元件3.1.3设置元件属性3.2逻辑设计3.2.1设计约束3.2.2逻辑优化3.2.3时序约束3.3约束文件编辑3.3.1约束规则3.3.2约束语法3.3.3约束检查3.4时序仿真3.4.1创建仿真波形3.4.2设定初始状态3.4.3运行仿真3.5功能仿真3.5.1设置输入信号3.5.2运行仿真3.5.3分析仿真结果4.仿真与验证4.1时序分析4.1.1设定时钟4.1.2时序路径分析4.1.3时序优化4.2时序约束验证4.2.1满足约束4.2.2修复时序错误4.3灵敏度分析4.3.1设定输入敏感性4.3.2分析敏感性4.4逻辑分析4.4.1切换敏感性4.4.2分析逻辑状态5.布局与布线5.1物理约束5.1.1面积约束5.1.2信号完整性约束5.1.3电源与接地约束5.2布局5.2.1网表导入5.2.2管理物理资源5.2.3进行布局布线5.3时序优化5.3.1满足时序约束5.3.2缩短信号传输路径5.3.3优化时钟分配5.4布线5.4.1管理布线资源5.4.2进行布线5.4.3路由与优化5.5设计规约检查5.5.1检查布局布线规约5.5.2修复设计规约错误总结:引言概述:ISE软件是一款功能强大的集成开发环境工具,广泛应用于数字电路设计和实现。

Xilinx ISE 使用入门

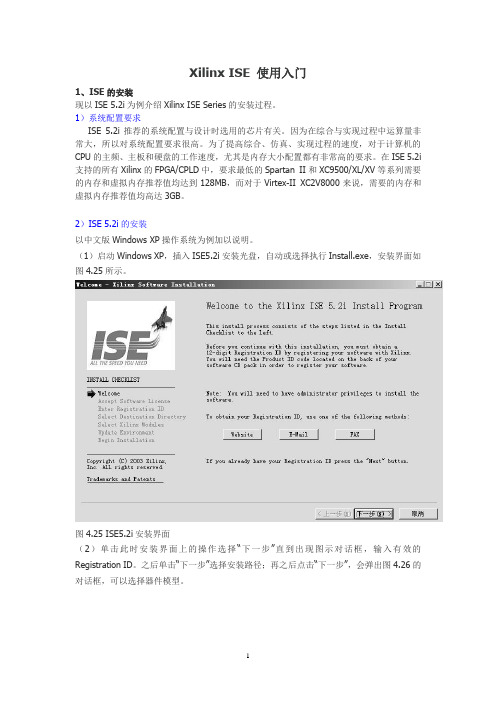

Xilinx ISE 使用入门1、ISE的安装现以ISE 5.2i为例介绍Xilinx ISE Series的安装过程。

1)系统配置要求ISE 5.2i推荐的系统配置与设计时选用的芯片有关。

因为在综合与实现过程中运算量非常大,所以对系统配置要求很高。

为了提高综合、仿真、实现过程的速度,对于计算机的CPU的主频、主板和硬盘的工作速度,尤其是内存大小配置都有非常高的要求。

在ISE 5.2i 支持的所有Xilinx的FPGA/CPLD中,要求最低的Spartan II和XC9500/XL/XV等系列需要的内存和虚拟内存推荐值均达到128MB,而对于Virtex-II XC2V8000来说,需要的内存和虚拟内存推荐值均高达3GB。

2)ISE 5.2i的安装以中文版Windows XP操作系统为例加以说明。

(1)启动Windows XP,插入ISE5.2i安装光盘,自动或选择执行Install.exe,安装界面如图4.25所示。

图4.25 ISE5.2i安装界面(2)单击此时安装界面上的操作选择“下一步”直到出现图示对话框,输入有效的Registration ID。

之后单击“下一步”选择安装路径;再之后点击“下一步”,会弹出图4.26的对话框,可以选择器件模型。

图4.26 器件模型选择对话框(3)点击“下一步”,如图4.27所示,可以选择器件种类。

图4.27 器件种类选择对话框通过以上步骤后,可根据具体情况来选择,继续“下一步”即可完成安装。

安装完成后,环境变量应作如下描述:若操作系统是Windows NT/2000/XP,选择开始->控制面板->系统->选项->系统->高级->环境变量,在环境变量中加入:变量名:Xilinx变量值:C:Xilinx(即安装路径)具体设置如图4.28所示。

3 VHDL设计操作指南首先进入ISE工程管理器(Project Navigator)界面,如图4.30所示。

ISE的使用说明

ISE的使用说明建立工程 (2)综合 (12)管脚约束 (14)布局布线的综合 (18)添加波形 (19)仿真 (21)下载 (25)启动桌面上名为Project Navigator的ISE软件图标,进入ISE开发系统如图所示。

在上拉菜单file栏打开,单击New project选项,开始新建一项工程。

如果想打开已有的ISE工程文件(文件格式为*.npl),则单击open project选项。

下面我们将以一个包括了24进制和60进制计数器的复合计数器的VHDL程序为例,来说明ISE的具体使用。

首先单击New project选项,出现如图所示对话框:在Project name一栏填上工程文件名,我们在此工程名命名为counter,放在目录F:\teacher_li 下。

下一步,进行可编程器件型号的选择以及设计流程的设置。

在器件型号栏有Device family ,Device (型号),封装,speed grade,可以根据实验平台所用的可编程逻辑器件分别设置相应选项。

对话框下半部分是对设计语言和综合仿真工具的选择。

然后下一步,采用默认设置,完成了New Project Information的设置。

如图所示:单击“完成”按钮,进入到如下对话框:在Source in Project一栏,选择菜单Module View选项,在工程名counter的图标位置单击右键,出现如下对话框。

New Project :新建一项文件,单击ew Project图标,出现的对话框包括了以下选项:新建IP核,电路设计,状态机,新建测试波形,用户文档,Verilog编写文件,Verilog测试文件,VHDL库,VHDL编写文件,VHDL包,VHDL测试平台。

Add Source :添加一项已经存在的文件。

本例中,首先选择VHDL Module项,我们file name命名为count。

下一步,进行管脚信号名称,位数和方向的设置。

实验一 ISE的简单使用

主要功能

1设计输入:原理图、VHDL、Verilog语言 2综合(Synthesize):综合工具 XST 3仿真(ISim Simulator):创建用于仿真的输入 激励文件(VHDL线后的设计文件转换为位流 文件

界面介绍

• 标题栏、菜单栏、工具栏、工程管理区、源文 件编辑区、过程管理区、信息显示区、状态栏。

• 菜单介绍: Project 菜单包含了对工程的各个操作,是设计中 最常用的菜单之一。 Set as Top Module命令:用于将选中的文件设置 成顶层模块。只有设置成顶层模块,才能对其综 合、实现以及生成相应的二进制比特流文件。

操作简介

• 新建工程 • 新建设计文件,代码输入 • 综合:将 HDL 语言、原理图等设计输入翻

译成与、或、非门和 RAM、触发器等基本 逻辑单元的逻辑连接。 在过程管理区双击Synthesize-XST • 双击 View RTL Schematics 来查看RTL级结构 图

• 仿真

1.在工程管理区选择Simulation

2.新建测试文件Test Bench(Project\New source\VHDL test bench)

3.选中Test bench文件,双击processes中的 Simulate Behavioral Model,即可完成功能仿真。

实验内容

1、熟悉ISE开发流程 2、AND-OR电路设计 3、完成综合和功能仿真

ISE原理图输入方法

5)建立和编辑顶层原理图文件对于顶层文件,即可使用VHDL文本输入方式,也可使用原理图输入方式。

这里我们将使用原理图的输入方式来建立顶层文件。

(1)原理图形符号的生成(Symbol)为了在原理图的设计中利用前面已使用VHDL进行有关设计的成果,我们先要将经过编译后的VHDL程序生成可供原理图设计中直接调用的原理图形符号。

选择 count_t.vhd,执行Create Schematic Symbol操作(如图4.47所示),即可生成可供原理图设计中直接调用的原理图形符号count_t。

同理,对其他两个文件执行相同的操作。

图4.47 原理图形符号的创建操作(2)顶层原理图文件的创建选中工程,鼠标右点,在弹出的窗口中选择New Source(如图4.48所示),再在弹出的窗口中选择文件的类型为Schematic,并输入文件名pic_top后,执行”下一步”,即完成了原理图文件的创建,进入原理图的编辑状态。

图4.48 原理图的创建操作(3)原理图的编辑① 放置元件(Symbols):在Symbols 的e:/xilinx/bin/24sec中选中所需元件的原理图符号,并在右边的图中期望的位置点左键进行放置,如图4.49所示。

若位置不合适,可进行移动调整。

图4.49 在原理图中放置元件的操作② 元件间的连线:点,进行连线操作。

③ 放置I/O端口并编辑端口名:点,放置I/O端口。

选中端口,点右键,在弹出的对话框中选择“Rename Port”后,再在弹出的对话框中输入系统设定的端口名。

或者双击端口,在弹出的对话框中输入系统设定的端口名。

④ 原理图的保存:原理图编辑好后(如图4.50所示),应执行存盘操作,将原理图进行保存。

图4.50 编辑好的顶层原理图⑤ 原理图错误的检查:为了检查原理图是否有错,可执行原理图的检错操作。

若有错,则改正,直到完全正确为止。

⑥ 原理图的逻辑综合:若原理图经过检查没有错误,可进行逻辑综合。

ISE软件使用说明

说明这个说明主要介绍了使用开发板可能使用到的3个工具,主要以串口功能的实现作为例子,讲述了ISE, Plantform和EDK的使用方法以及操作的基本流程。

ISE的使用一.启动Xilinx ISE:开始Æ所有程序ÆXilinx ISE 7.1iÆProject Navigator二.新建/打开一个工程:如果已经有了工程,则在FileÆOpen Project弹出的对话框里面选择你的工程。

如果没有合适的工程就需要通过FileÆNew Project来新建一个工程。

具体操作步骤如下:分别在Project Name和Project Location里面填写您想要创建的工程的名称和路径。

在Top-Level Module Type的下拉菜单里面选择您的工程的顶层模块的类型。

本次串口通信的实验的顶层为原理图,所以选择Schematic。

然后点击下一步:在这个对话框的上半部分选择您使用的芯片的族(Spartan3),型号(xc3s400),封装(pq208)和速度(-4)。

下面选择您要使用编译和综合的软件,建议使用ISE自带的软件,一是使用简便,二是Xilinx公司对自己的FPGA了解程度比第三方要高很多,所以使用Xilinx公司自己的软件有的时候会获得意想不到的收获。

具体参数选择如图,然后单击下一步:在这个对话框里面新建工程里面的文件,这步也可以放到后面来实现,这里我们先选择下一步:这一步用来添加已经存在的文件,同样,我们在后面实现这步。

点击下一步:在最后这个对话框里面显示了我们即将建立的工程的详细信息,确认无误以后点击完成,ISE将为您创建一个名字为uart_test的工程:三.为刚创建的工程添加源文件:1.添加已经存在的源文件:选中屏幕右上的xc3s400-4pq208,单击ProjectÆAdd Source,在弹出的对话框里面选择您已经存在的程序文件(.v .vhd)。

ISE使用方法

附录附录1:利用ISE对器件仿真时的步骤:1.1在ISE中建立一个新的项目首先进入ISE TCAD运行的Linux操作环境,进入操作界面按照以下顺序进行创建新目录,Project →New → New Project。

在工作主界面的Family Tree目录下的No Tools边框上面,右键Add →Add Tool →Tools →MDraw →OK,在Create Default Experime边框选定OK ,Tool边框上点击确定After Last Tool →Apply →Tools →Inspect →OK。

这样,工作界面Family Tree目录下就有MDraw、Dessis、Inspect这三个工具组了。

之后进行保存Project →Save As →输入工作名称→OK就可以了,或者也可以直接点击保存的快捷图标进行保存。

1.2.建立器件网格利用Mdraw模块建立SiC MESFET器件结构模型,包括器件的边界、掺杂、网格的划分和关键区域的加密;首先要进行MDraw的绘制器件工作,右键MDraw →Edit Input →Boundary 进入MDraw的绘制器件结构工作区。

在MDraw绘制过程中,可以徒手绘制,这是默认模式的绘制方式。

然而在大多数情况下,需要按照器件尺寸精确绘制,这时可以从Performance Area中点击Exact Coordinates选择精确坐标绘制。

接下来要选择器件的制作材料,打开Materials菜单,选择MESFET器件材料SiC。

绘制器件结构图时,选择Exact Coordinates,点击Add Rectangle增加矩形框,输入预先设计的各点坐标,设定器件各个结构的尺寸大小。

器件结构绘制完成后,需要在源、漏的欧姆金属和SiC接触面上添加欧姆接触层,另外栅的肖特基金属和SiC接触面上需要添加肖特基接触层,衬底和衬底合金界面同样需要添加接触层,这样仿真出来的结果才能更加符合实际情况。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

5)建立和编辑顶层原理图文件

对于顶层文件,即可使用VHDL文本输入方式,也可使用原理图输入方式。

这里我们将使用原理图的输入方式来建立顶层文件。

(1)原理图形符号的生成(Symbol)

为了在原理图的设计中利用前面已使用VHDL进行有关设计的成果,我们先要将经过编译后的VHDL程序生成可供原理图设计中直接调用的原理图形符号。

选择 count_t.vhd,执行Create Schematic Symbol操作(如图4.47

所示),即可生成可供原理图设计中直接调用的原理图形符号count_t。

同理,对其他两个文件执行相同的操作。

图4.47 原理图形符号的创建操作

(2)顶层原理图文件的创建

选中工程,鼠标右点,在弹出的窗口中选择New Source(如图4.48所示),再在弹出的窗口中选择文件的类型为Schematic,并输入文件名pic_top后,执行”下一步”,即完成了原理图文件的创建,进入原理图的编辑状态。

图4.48 原理图的创建操作

(3)原理图的编辑

① 放置元件(Symbols):在Symbols 的e:/xilinx/bin/24sec中选中所需元件的原理图符号,并在右边的图中期望的位置点左键进行放置,如图4.49所示。

若位置不合适,可进行移动调整。

图4.49 在原理图中放置元件的操作

② 元件间的连线:点,进行连线操作。

③ 放置I/O端口并编辑端口名:点,放置I/O端口。

选中端口,点右键,

在弹出的对话框中选择“Rename Port”后,再在弹出的对话框中输入系统设定的端口名。

或者双击端口,在弹出的对话框中输入系统设定的端口名。

④ 原理图的保存:原理图编辑好后(如图4.50所示),应执行存盘操作,将原理图进行保存。

图4.50 编辑好的顶层原理图

⑤ 原理图错误的检查:为了检查原理图是否有错,可执行原理图的检错操作。

若有错,则改正,直到完全正确为止。

⑥ 原理图的逻辑综合:若原理图经过检查没有错误,可进行逻辑综合。

6)设计ucf文件

首先选中pic_top ,按右键在弹出的窗口中选择New Source,再在弹出的新建文件窗口中选择Implementation Constraints File,并输入文件名top.ucf(如图4.51所示)。

接着执行“下一步”,即进入ucf文件的编辑操作,这时我们可根据系统的输入输出要求并参照下载板的用户手册,对系统的端口进行管脚锁定(如图4.52所示)。

管脚全部锁定并检查无误后应进行存盘操作。

图4.51 ucf文件的建立操作示意图

图4.52 本设计的ucf文件

7)设计实现

运行设计实现(Implement Design):选中pic_top,运行Implement Design,如图4.53所示。

图4.53 运行设计实现操作图

在FloorPlanner中查看设计布局:展开Place & Route,运行View/Edit Placed Design (FloorPlanner),即可查看设计布局,如图4.54所示。

图4.54 在FloorPlanner中查看设计布局操作图

8)系统的时序仿真

在完成任务上述步骤后,我们可以按照前面已经介绍的方法,对系统(顶层文件)进行时序仿真。

系统分类: CPLD/FPGA| 用户分类:

ASIC/FPGA/CPLD| 来源: 无分类| 【推荐给朋友】| 【添加到收藏夹】。