PCB叠层设计规范 文档

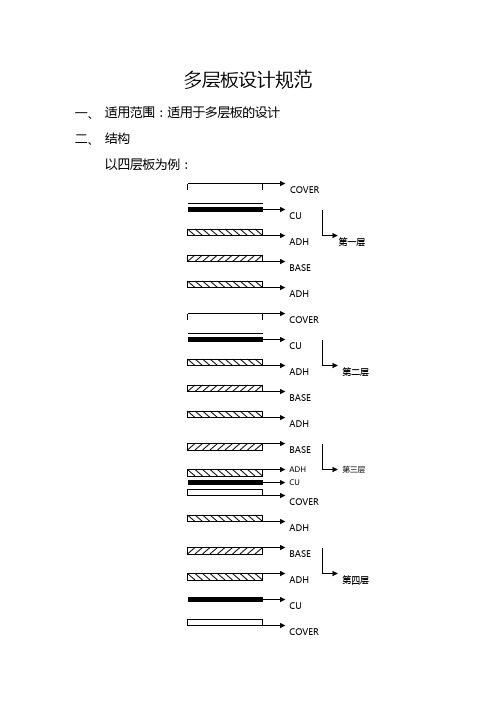

多层板设计规范

多层板设计规范一、适用范围:适用于多层板的设计二、结构以四层板为例:COVERCUADHBASEADHCOVERCUADH 第二层BASEADHBASEADH 第三层CUCOVERADHBASEADH 第四层CUCOVER三、工艺流程A.三层板开料→一次钻孔→贴干膜(二层)→曝光显影(二层)→蚀刻脱膜(二层)→贴覆盖膜(二层)→压覆盖膜(二层)→投影打孔(二层)→压合(1,2,3)→二次钻孔→沉镀铜→贴干膜→曝光显影(1,3)→蚀刻脱膜→贴覆盖膜→压覆盖膜→表面处理→针测→冲外形→品检→入库B.四层板开料→一次钻孔→二四层压合→贴干膜(2,4)→曝光显影(2,4)→蚀刻脱膜(2,4)→贴2,4层覆盖膜→压2,4层覆盖膜→1,2,3,4层压合→二次钻孔→贴干膜→曝光显影1,4→蚀刻脱膜→贴覆盖膜→压覆盖膜→表面处理→针测→冲外形→品检→入库C、四层板以上均可参照四层板流程四、定位系统4.1:定位系统包括四个方面:图形转移定位、二次钻孔定位、多层压合对位、贴盖膜对位4.2三层板4.2.1:三层板中间层直接做线路,只考虑二钻的销钉孔和1、2、3层的对位孔4.2.2:压合对位孔与二钻销钉孔在第二层菲林设计出来,具体说明如下:`4.2.3:一次钻带(TOP\BOT)定位系统的设计:包括:校位孔、排气孔和图中所有的孔,hole大小为:校位孔φ1.0mm;排气孔φ1.5mm;监视孔φ1.4mm;对位孔大小同投影打出孔相同;二钻销钉孔大小比内层投影打出的孔单边大0.5mm.4.2.4:二钻销钉孔与监视孔的设计:包括:校位孔、曝光对位孔、监视孔、销钉孔、通孔;Hole的大小:校位孔φ1.0mm;通孔大小根据客户要求;监视孔同板内通孔相同;曝光对位孔φmm;销钉孔放在二钻内,但图形中不钻出,只钻基板上,目的是固定。

必须先钻监视孔,判定是否偏位后,再钻图形孔。

4.2.5:盖膜膜、热固胶膜的面向及钻孔的设计4.2.5.1:中间层盖膜和顶层盖膜面向为膜面向上,底层膜面向下4.2.5.2:热固胶膜规定贴在中间层,顶面为膜面向下,底面为膜面向上。

PCB叠板文件.

B

Initial version新发布

目录页码

1.0目的4

2.0范围4

3.0参考文件4

4.0定义4

5.0职责权限4

6.0流程图4

7.0程序5-9

8.0记录9

9.0附件9

1.0目的

本程序的目的是为了满足客户要求的叠层结构,规范产品工程部对选择板材的生产指示,以确保产品品质。

2.0范围

本程序适用于产品工程部选择叠层结构指示规范。

实际介厚=(PP或RCC)理论厚度-(1-X1%)*A1-(1-X2%)*A2 –A3

说明:

1、(PP或RCC)理论厚度:指的是(PP或RCC)在两张铜箔之间的厚度。半固化片及RCC理论厚度见附件.

2、X1%.X2%:指的是芯板上的含铜百分比;

3、A1或A2:指铜厚,(1)若直接为铜箔,则1OZ=35 um;(2)若经过电镀,则取电镀后总的铜厚计算,即以MI中的最小的铜厚加上5um计算;

B:表面处理为ENIG、IS或OSP,PTH孔壁铜厚客户要求最小值不小于0.026mm的,压板后厚度中值=完成板厚度中值-[0.089+2.5*(PTH孔铜最小厚度-0.026mm)]mm,压板后厚度公差=完成板厚度公差-0.025mm。

C:多次层压的板,以最后一次压板厚度减去外层介质厚度及相应次外层镀铜厚度,获得前一次压板厚度,依次类推直至获得第一次的压板厚度。

7.1.3设计完成的叠板介质厚度必须符合客户设计的板厚,并且符合阻抗要求。我司能力为:完成板厚0.3mm—0.5mm(不包括0.5mm),公差为+/-0.05mm。

完成板厚0.5mm—4.0mm,若铜箔间为单张半固化片,公差为+/-0.5mil;若铜箔间为多张半固化片,公差为+/-10%。

PCB设计规范

PCB设计规范个人收集整理的PCB Layout设计规范,可下载修改PCB设计规范项目名称:文件编号:编制日期:个人收集整理的PCB Layout设计规范,可下载修改1. 布局设计规则1.1. 确认结构图纸是最新的。

1.2. 根据结构图设置板框尺寸,按照结构要素布置安装孔、接插件等需要定位的器件,并给这些器件赋予不可移动属性。

1.3. 根据结构图和生产加工所需的夹持边设置PCB的禁止布线区、禁止布局区。

1.4. 优先摆放电路功能块的核心元件及体积较大的元器件,再以核心元件为中心摆放周围的电路元件。

质量较大的元器件应避免放在板的中心,应靠近板在机箱中的固定边放置,以免引起PCB翘曲。

1.5. 发热元件要均匀分布,以利于散热,除温度检测元件意外的温度敏感器件应远离发热量大的元器件,如电解电容、晶振、电池等。

注意结构通风流向,发热量大的器件应尽量不被其他器件挡住。

1.6. 布局应尽量满足以下要求:总的连线尽可能短,关键信号线最短;高电压、大电流信号与小电流、低电压的弱信号完全分开;模拟信号与数字信号分开;高频信号与低频信号分开;有高频连线的元件尽可能靠近。

1.7. 元件的布局应便于调节和维修,如跳线、可变电容、电位器等器件周围要有足够的空间;小元件周围不能放置大元件,以免维修时无法焊接;BGA与其他贴片元件的距离大于2mm,以便于拆焊;压接的接插件周围5mm内正面不能有高度超过压接插件高度的元器件,背面5mm内不允许有元件或焊点。

1.8. BOTTOM层的贴片元件和接插件的管脚焊盘间距大于3mm,以保证波峰焊良率;如果贴片元件的高度较大,则间距应大于5mm。

1.9. 同类型的插装元件优先朝一个方向放置,同一类型的有极性分立元件也应力争在方向上保持一致,以便于生产和检验,如电解电容。

个人收集整理的PCB Layout设计规范,可下载修改1.10. 打开TOP层和BOTTOM层的place-bound,查看重叠引起的DRC是否允许,特别注意元件叠放是否会引起短路或者生产时候焊接不良等问题。

PCB叠层设计范文

PCB叠层设计范文PCB(Printed Circuit Board)叠层设计是电子产品设计中的重要环节之一、通过优化PCB叠层设计,可以有效减少电子产品的体积、提高系统的可靠性和性能。

下面是一篇关于PCB叠层设计的范文,供参考。

一、引言电子产品的快速发展进入了一个全新的时代,使得人们对产品的要求越来越高。

作为电子产品的核心部件之一,PCB叠层设计直接影响了产品的性能和可靠性。

本文将以一款基于ARM架构的嵌入式系统为例,介绍PCB叠层设计的优化方法和步骤。

二、PCB叠层设计的重要性在电子产品的设计中,PCB叠层设计是最重要的环节之一、首先,合理的PCB叠层设计可以有效减小电子产品的体积,提高其集成度。

其次,合理的叠层设计可以降低电子产品的能耗,提高其性能。

最后,合理的叠层设计可以提高PCB的可靠性,减少电子产品的故障率。

三、PCB叠层设计的优化方法1.分析系统的功能模块在进行PCB叠层设计之前,首先需要对整个系统的功能模块进行详细的分析。

通过了解系统的硬件架构和各个功能模块之间的关系,可以有针对性地进行PCB叠层设计。

2.合理规划信号和电源层在PCB叠层设计中,信号和电源层的规划非常重要。

一般来说,信号层应尽量靠近地层,电源层应尽量靠近电源。

这样可以有效减少相互干扰,提高系统的性能。

3.避免信号干扰和电磁辐射在PCB叠层设计中,需要尽量避免信号的干扰和电磁辐射。

为了达到这一目的,可以采用屏蔽层和地层的结构,有效地减少信号之间的相互干扰和电磁辐射。

4.合理规划元器件的布局在进行PCB叠层设计时,需要合理规划元器件的布局。

首先,元器件之间应保持足够的间距,以免互相干扰。

其次,应根据元器件的功耗、尺寸等因素合理规划元器件的位置,以便于散热和维修。

5.选择合适的材料在进行PCB叠层设计时,需要选择合适的材料。

一般来说,PCB的基材可以选择FR-4,其有良好的绝缘性能和机械强度。

另外,需要根据系统的特性和需求选择合适的层压板。

PCB设计规范DOC

PCB设计规范DOC1.PCB尺寸和形状:PCB尺寸应根据实际应用需求进行合理选择。

在进行PCB布局时,应根据特定需求确定PCB的形状,边缘应呈规整的矩形或圆角矩形。

2.PCB层次和层数:根据设计需求,合理选择PCB的层数,常见的有单层、双层和多层PCB。

根据信号完整性要求,可在多层PCB中加入地层和电源层,提高抗干扰能力和信号传输质量。

3.线宽和线距:合理选择线宽和线距对于PCB的稳定性和抗干扰能力至关重要。

一般来说,较窄的线宽和线距有助于减小PCB的尺寸,但也会增加制造和焊接的难度。

因此,需根据具体应用需求和制造工艺要求进行合理选择。

4.确保电磁兼容性(EMC):在进行PCB设计时,应考虑电磁兼容性,以降低电磁干扰和提高系统的抗干扰能力。

通过合理分布和布线可以降低干扰源和受干扰源之间的耦合,使用屏蔽罩和地层来减小电磁辐射和接收。

5.元件布局与布线:合理的元件布局和布线有助于优化PCB性能、降低串扰和噪声。

对于模拟和数字信号,应按照不同的信号类型进行分区布局,减少互相干扰的机会。

高频和敏感信号线应尽量短且平行布线,降低引入的噪声。

6.引脚映射和标识:为了便于排查和维护,应做好引脚映射和标识。

对于器件的引脚和连接器的引脚应有明确的标识,方便布线和调试。

7.保留特定区域:在PCB设计中,可能存在一些需要保留的特定区域,如机械固定孔、散热器或接口连接器的安装区域。

在布局时要合理规划这些区域,以免干扰到其他电路或器件。

8.禁止区域和引脚验证:有些器件在工作时可能会产生较大的电磁辐射或高温,需要在设计时设置禁止区域,并在设计验证阶段进行引脚验证,确保没有错误连接。

9.工艺规范:在PCB设计中,还应根据制造工艺的要求制定相应的工艺规范。

如焊盘的孔径和间距、复杂线路的线宽要求等,这些规范可以在整个制造和组装过程中起到指导作用。

10.DFM/DFT设计原则:DFM(Design for Manufacturability)和DFT(Design for Testability)是一系列设计原则,旨在方便制造和测试过程。

7 PCB叠层设计

PCB的叠层结构设计

➢十层板叠层设计方案 :

十层板叠层设计方案很多,推荐使用设计方案1和2:

(a)方案1

(b)方案2

方案1是最佳选择方案,可以做到很好的阻抗控制

方案2适合接插件较多的高速背板设计

8

2

PCB的叠层结构设计

对于高速背板,一般层叠原则如下:

➢ Top面、Bottom面为完整的地平面,构成屏蔽腔体。 ➢ 无相邻层平行布线,以减少串扰,或者相邻布线层间距远远大于

参考平面间距。 ➢ 所有信号层尽可能与地平面相邻,以保证完整的回流通道。

需要说明的是,在具体的PCB层叠设置时,要对以上原则进 行灵活掌握和运用,根据实际单板的需求进行合理的分析, 最终确定合适的层叠方案,切忌生搬硬套。

适用于多数器件为插件,且走线简单的PCB层板叠层设计方案 :

(a)方案1

(b)方案2

(c)方案3

方案1的优点:

✓各信号层均有完整的参考层,而且没有信号层相邻,避免了信号之间的串

扰,信号层2为最优布线层;

✓电源和地层相邻,电源阻抗减小;

方案1的缺点:

✓布线层只有三层,对于布线量较大的设计,只能选择其他方案或增加板

3

PCB的叠层结构设计

➢四层板叠层设计方案 :

(a)方案1

(b)方案2

方案1:信号层1应走线较多,且包含关键信号,因而将其直 接与参考面的地层相邻。从GND层到Power层的阻抗控制芯板 不宜过厚,以降低电源以及地平面的分布阻抗,保证电源平面 的去藕效果。

方案2: 整板无电源平面,只有GND和PGND各占一个平面,

✓S1 、S2、S3 、S4全部裸露在外,只有S2 才有较好的参考平面;

✓S1 和S2、S3和S4 信号容易串扰;

PCB堆叠设计规范总则

PCB设计规范总则CHECKLIST自检人:________________检查人:________________检查日期:_____年_____月_____日审查内容:____________________________________________________________________审查结果:通过□不通过□说明:____________________________________________________________________序总则条款执行情况说明号是[ ] 否[ ] 免[ ] ¹3-3:当电源和地区分为数字和模拟时,退耦电容不得跨接,数字电源和模拟电源不得重叠:¹是[ ] 否[ ] 免[ ] ¹3-4:独立的电源或地之间不得在隔开处采用电容或走线跨接:¹是[ ] 否[ ] 免[ ] ¹3-5:同一位置采用并联电容退耦时,电容之间采用不同数量级的容值,如10nF和100nF.是[ ] 否[ ] 免[ ] ¹3-6:晶振必须放置在离IC最近的旁边,晶振时钟信号走线最长1cm,两晶振时钟走线之间间距尽量小,最大间距0.5mm.是[ ] 否[ ] 免[ ]¹3-7:晶振时钟信号走线尽量不要打孔,保持同层走线。

是[ ] 否[ ] 免[ ] ¹3-7:晶振走线周围地需要用地包围起来,其中的地应与其他电源供电地和信号地分开。

¹¹是[ ] 否[ ] 免[ ] ¹3-8:匹配电阻要靠近信号的驱动端,对于I2C如果驱动多个I2C元器,匹配电阻尽量放置在被驱动的终端。

序总则条款执行情况说明号¹3-9:功放输出走线最小宽度为40MIL。

是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ] ¹3-10:走线不得有一端浮空的情况,¹是[ ] 否[ ] 免[ ] ¹3-11:对于重要高频信号,其布线长度不得与其波长成整数倍关系。

印制电路板(PCB)设计规范V1.0.

印制电路板(PCB设计规范(第0修改)编制审核批准2011-11-15 发布2011-12-15印制电路板(PCB设计规范No. 版次更改原因更改内容AW实施1目的为了规范公司产品的 PCB工艺设计要求,使得 PCB的设计从生产、应用等角度满足良好的生产装配性、测试性、安全性等要求,并在产品设计过程中构建产品的工艺、技术、质量、成本优势。

2适用范围本文件适用于公司自主开发的 PCB 设计以及PCB 审核。

职责一般职责参考PCB 管理规范。

工作程序使用CADENCES 件设计PCB 可以直接选择使用设计模版:Template.brd ,模版中已经配置完成了以下4.1.1-4.1.6 的内容。

模版使用时可以直接将模版文件复制、重新命名形成新的 文件。

4.1.1设置 Drawing Parameters按照IPC 标准,PCB 设计中使用的绘图单位为毫米( mm ,精度一般精确到小数点后 3位。

根 据我们通常的PCB 尺寸,选择PCB 设计图纸尺寸为A3,如果PCB 尺寸超过A3大小,则可选择A2或其 他。

根据以上设置Drawing Parameters 如下:User unit : Millimeter Size : A3 Accuracy : 3Drawing Extents : W:440,H:3174.1.2 PCB 设计 Format 文件PCB 设计图纸框图FormatA3.dra 文件保存在Cade nee 封装库中。

通用模版已经将该文件导入完成。

4.1.3器件布局栅格的设置元件密集的PCB 栅格设置为0.05mm ,其他PCB 的栅格以0.05mm 的倍数递增。

4.1.4文字字体设计规则根据PCB 丝印层设计规范的要求,共需要四种字体规格,即常规、小字体、对外接口的接插件丝印PCB 模版中已经将以下几种字体在“ TEXT SIZE ”中的1、2、3项中增加。

设计使用时可以直接选择。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

层压设计规则

作者:刘军喜2010/10/20

1.0设计规则:

1.1非客户指定结构设计、非阻抗板压板结构设计

1.1.1底铜厚度≤1OZ板最外层介电层(L1-2,LN-LN-1层)厚度设计为

2.8-14.6MIL,其它层介电

层设计为

3-14.6MIL;

1.1.2无耐高压测试要求的板压板结构设计

a、3oz≥底铜厚度≥2OZ介电层厚度设计至少大于4.5MIL;

b、4oz≥底铜厚度≥3OZ介电层厚度设计至少大于6.5MIL;

c、底铜厚度≥5oz的板需工程出工程评估给工艺组评估后再确定。

1.1.3有耐高压测试板要求的板,根据客户高压要求设计具体的压合结构,通常高压测试在

2000V-2800V时,介电层设计至少大于6MIL,具体客户要求的板材TG、CTE、CTI、耐CAF

等详细情况需工程出工程评估给工艺组评估后再确定。

备注:介电层指PP层,含core介电层,介电层厚度及core厚度均指中值,不含公差,

当厚度>5MIL时公差按IPC4101三级公差进行控制;当厚度≤5MIL时,公差按±0.5MIL控

制;超IPC4101三级公差的MI备注要求特别控制及备料.

1.2 客户指定结构板、阻抗板压板结构设计

若客户指定结构,工程组在接单时尽量与客户沟通按以上要求设计,当不能满足以上要求时,出工程评估单给工艺评估.

1.3板边尺寸设计制作标准

1.3.1所有板MI设计开料尺寸需比压合后成型尺寸单边大0.1~0.2″,同时预留开料刀具损耗

每刀0.1″。

1.3.2四层板板边一般设计为≥0.5″,特殊情况下可以做到0.4″,但必须满足以下条件:

A、非阻抗板;

B、介电层厚<8.0MIL;

C、内层铜厚<2OZ;

1.3.3六层及以上板按照板边≥0.75″控制,六层板特殊情况下可做0.6″(min),但需满足上

述a、b、c条件。

1.3.4两张及以上芯板压合的四层板板边设计要求同六层板。

1.3.5 OPE系统设计单元边到开料边一般为≥0.9″,最小可生产0.80″。

按0.80″设计时需

优先保证OPE系统靶标完整,其他靶标可移位处理。

1.3.6对于内层铜厚≥2OZ底铜板,板边设计≥0.8″,以防止流胶过大导致板厚超公差及板边

白点。

1.3.7对于阻抗板及金手指板板边设计特别要求:

a、阻抗TEST COUPON设计在板中,无法设计在板中的,TEST COUPON边距板边须满足≥

0.4″,金手指位的方向尽量朝板中。

b、设计拼图时,加大板边尺寸,板边尺寸按≥0.8inch设计。

1.4高层板、内层厚铜板无铜区叠加及薄介电层板内层需添加辅助铜皮以避免压合起皱:

备注:

①无铜区面积包括单元内、单元间距及相连折断边的无铜区;

②金手指须闸板、跳V-CUT的除外;

③单元内及折断边添加辅助铜皮需问客同意;

④添加辅助铜皮形状优先选用顺序为:实心铜皮、平行四边形、倒梯形及圆PAD,单元之间添加辅助铜皮交

叉位置需设计4~7MM宽的通道保证压合过程中单元间树脂流动,避免设计为封闭或半封闭图形(如“口”、“П”、“十”或“×”等形状,OPEN窗除外),特殊情况需设计为以上图形时,需出难点给工艺评估或知会工艺确认。

1.5压合结构设计的一般原则如下:

①优先选用厚度较大的基板(尺寸稳定性相对较好);

②优先选用低成本(或低成本组合)pp;

备注:对于同种玻璃布型prepreg,树脂含量高低基本不影响价格,PP厚度与价格无必然关系,特殊PP(如2113、2112、3313、1506、106)价格较一般普通PP要贵(7628、7630、1080、2116),为节约成本,在保证压合品质的情况下,PP张数尽量少用,如7628H*1可代替2116L*2。

③优先选用对称结构(包括铜厚对称、拼图设计对称、PP使用对称、二次压合core/PP厚度对称);

④ 1-2层及n-1/n层间禁止单张使用低树脂含量prepreg,如7628(R/C:42%)×1(n为层数);;

⑤对于有5张或以上的半固化片排在一起或介电层厚度大于25mil,除最外层与最里层使用PP外,中

间PP用光板代替,以满足介电层厚度的均匀性;

⑥对于含有无铜区大于3″×3″或1″×5″的1OZ或1OZ以上底铜多层板,芯板间一般不单张使用PP;

⑦介电层厚度=PP硫化厚度-(1-残铜率%)*铜厚;

⑧≥2OZ底铜二张及二张以上PP结构,使用PP含量较高PP靠core

⑨板料和PP须使用同一供应商(特殊情况除外)

⑩由于PP和基板来料的差异,所有的压合结构的设计和使用均以试板结果调整为准;(11)、≤1OZ底铜二张及二张以上PP结构,使用厚度较厚PP靠core。

1.6 PP硫化厚度参考。