verilog_m序列代码

常用Verilog代码

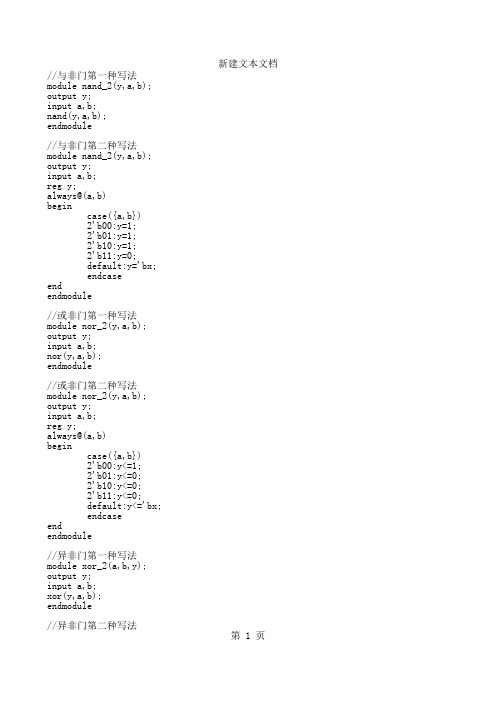

新建文本文档 begin if(en) begin a=b; end else begin a='bz; end end end endmodule //使用always过程语句描述的简单算术逻辑单元 `define add 3'd0; `define minus 3'd1; `define band 3'd2; `define bor 3'd3; `define bnot 3'd; module alu(out,opcode,a,b); output reg [7:0] out; input [2:0] opcode; input [7:0] a,b; always@(opcode or a or b) begin case(opcode) `add:out=a+b; `minus:out=a-b; `band:out=a&b; `bor:out=a|b; `bnot:out=~a; default:out=8'hx; endcase end endmodule //8线-3线编码器 module encode8_3(i,y); input [7:0] i; output reg [2:0] y; always@(i) begin case(i[7:0]) 8'b00000001:y[2:0]=3'b000; 8'b00000010:y[2:0]=3'b001; 8'b00000100:y[2:0]=3'b010; 8'b00001000:y[2:0]=3'b011; 8'b00010000:y[2:0]=3'b100; 8'b00100000:y[2:0]=3'b101; 8'b01000000:y[2:0]=3'b110; 8'b10000000:y[2:0]=3'b111; default:y[2:0]=3'b000; endcase end endmodule //3_8译码器 module decoder3_8(a,y); 第 3 页

Verilog程序代码集

1.全加器Sum=A⊕B⊕CinCount=AB+Cin(A+B)①数据流module adder(a,b,Cin,Sum,Count); input [2:0]a,b;input Cin;output [2:0] Sum;output Count;assign {Count,Sum}=a+b+Cin; endmodule②行为描述always语句module adder(a,b,c,Cin,Sum,Count); input [4:0] a,b;input Cin;output reg [4:0] Sum;output reg Count;reg T1,T2,T3;always@(a or b or Cin)beginSum=a^b^Cin;T1=A&B;T2=Cin&A;T3=Cin&B;Count=T1|T2|T3;endendmodule③结构体module adder (a,b,Cin,Sum,Count);input a,b,Cin;output Sum,Count;Xor a1(s1,a1,b);Xor a2(Sum,s1,Cin);and a3(T1,a,b);or a4(T2,a,b);and a5(T3,Cin,T2);or a6(Count,T1,T3);Endmodule2.数值比较器①判断两值是否相等module compare(a,b,equal);input [7:0] a,b;output equal;assign equal=(a==b)?|0; ②谁大谁输出module compare(a,b,out);input [7:0] a,b;output reg[7:0] out;always@(a or b)beginif (a>b) out<=a;else if (a==b) out<=a;else out<=b;endendmodule③输出参数module compare(a.b.xgy,xsy,xey);input [7:0] x,y;output reg xgy,xsy,xey;always@(x or y)beginif (x==y) xey=1;else xey=0;if (x>y) begin xgy=1;xsy=0;endelse if (x<y) begin xgy=0;xsy=1;end endendmodule3.编码器(4-2 8-3 16-4编码)①case语句8-3编码(优先)module code (in ,out);input [7:0] in;output reg [2:0] out;always@(in)case x(in)begin f=1;8’b1xxxxxxx:out=3’b111;end begin f=1;8’b01xxxxxx:out=3’b110;end begin f=1;8’b001xxxxx:out=3’b101;end begin f=1;8’b0001xxxx:out=3’b100;end begin f=1;8’b00001xxx:out=3’b011;end begin f=1;8’bxx:out=3’b010;endbegin f=1;8’bx:out=3’b001;endbegin f=1;8’b:out=3’b000;end default:begin f=0:out=3’b000;end endcaseendmodule②if-else语句(4-2优先编码)module code(in,out);input[3:0] in;output reg [1:0] out;always@(in)if (in[3]==1):begin f=1;out=2’b11;end else if (in[2]==1):begin f=1;out=2’b10;end else if (in[1]==1):begin f=1;out=2’b01;end else if (in[0]==1):begin f=1;out=2’b00;end else begin f=0;out=2’b00;end endmodule4.多路选择器①行为描述(4选1)module choice(A,B,C,D,ncs addr out);input [7:0]A,B,C,D;input ncs;input [1:0] addr ;output reg[7:0] out;always@(A or B or C or D or ncs or addr) beginif (!ncs)case(addr)2’b00:out=A;2’b01:out=B;2’b10:out=C;2’b11:out=D;endcaseelse out=0;endendmodule5.设计一个4位双向移位寄存器。

基本门Veriog代码modelsim代码及波形图

基本门Veriog代码modelsim代码及波形图作者:日期: 231、与门* /ondgfltrjrlg^Sst/fc.. * /andgatE_旳上t/dk 小 /wd3aiiF_ylaJtetjfe */andjatejrtg^st/b ' /andgatE_)1g_&t/c2、或门□rgatE.Y闕站齐車舞死発10s a c1M LC Elrtcdule oxgate (cli r a r i>r c);3inpuL elk;号input a;5inpu 匸 to;6aurput c;7 P"工皂g num;%> ? always^(poi^dGe elk)10 □ begin11num <— < i | bi12-end13assign c =nuir :Q 歸镖打學厲川%%曲斑I E 0園也T F 二2(clk,^,b z c);23lnFTit elk; 些input a:5 h;6 output c :7匸=eg mini;(gus 亡dg 令 elk) begi10 nun; <■ 12 -end二 E 13羊:导■!*;; cendir.adule15 —Hn.odule ^andgate always Q 16oid Wiv# -De^ult14IS L endmociole453ibtVrm dgate.v□絹廿辜隼4 % % %缁g5 0靈臨77+ T1 E7 Bmaa'ale nard^ate (cllr, a r b, c); £ 3 inpur cl3c;4 5lnpur A ; inpvt b;6 output c ;7 reg nun;gg always @ (TC sedg ■& clt)10 白 begin11 num !(a £ b};12 -end13assj-grn c — num;仙15Lendir.Qdulemitia 1begin clk=l ; endalways begin #1 clk='<clk; endinitial begin a=0;b=0, endEl* Jtrgnfr_Mg_=t/rik“ jcsrgatr_M^_St^ * 问 MkjlQ —HlJS 1 ■* 间学4*乂-泌忆■1—-1_—F L-■ —p~l~L J□—F L -Lr ■—■3always begin #2 8二#2 呂二0;b二1;tt2a=l;b=0;#2 a=l4b=l;end6nor^ata.v踊1 M臨可車李4%%%% ® 5s凰如 1 一* 匚■2 EJinodule II ornate (cLZ f a, t>, c);23input elk;4input a;5input ©:E c;7 reg nuirjgaluayg @ (pesedj^ tL上)10 曰begin11 num 5 ! (a | b-);12- end13 a s s i g.n & = num;14115-eTidifrOdule5、异或门«:a7xorgate,v闔M富百章谨A % %况?4 I 5 ¥2霾剜1 □module xoxgate (匚二23兮lnpur elk; anput a;5input t);6cutpnt c;7Areg num;¥always @ (pcsedge elk)10 H b^gin11num <= a^to;12 - end13assign c = num;14 ■15andn.odLilej4、或非门7M»D* 2 *5上4寺vk;.醐灿1£ 鈕『01口_曲上1用斗gnatr」lff_te谕■* /BnrgHtp」©_j3址86同或门67391011IE13ie151617clt;input inputa; input b;output CFreg num;always 3 (pasedge elk) fcegi^inuiL <= a zd assign c = num;b;M詁a■舟屯怙曲—9。

一次输出8bit_n4_m序列Simulink仿真Verilog实现

1.4阶m序列生成器一开始希望通过使用8个PN序列生成器并行实现,但是,每个生成器都不能得到后8个状态的值。

由于后面的8bit PN序列,通过一个clk不可能通过状态转换实现,所以,只能通过计算得到利用Matlab计算得到后8位PN码与初始状态的关系,得到一个输出生成矩阵,使用生成矩阵与初始状态相乘,即可得到8位PN码同时,计算得到生成第8位PN码时移位寄存器的状态,得到一个初始值生成矩阵,使用此矩阵与初始状态相乘,即可得到生成第8位PN码时移位寄存器的状态,从而为下一次迭代提供初始状态。

两个矩阵在PN码生成过程中保持不变,而初始状态得到不断更新,8位PN码不断输出。

clc; clear;n = 4; % 4 orderbit = zeros(9,n^2);bit(1,:) = [1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1];initial = [1 0 0 0];for i = 2:9% generate polynimial, 1 + x + x^4, ==========x + x^4,bit(i,:) = [ mod( bit(i-1,1:n)+bit(i-1,3*n+1:4*n), 2), bit(i-1,1:3*n)];endgenmatrix = bit(2:9,3*n+1:4*n) % generate matrix remain the samefor j = 1:1mseq = mod(genmatrix*initial', 2)% Update initialtemp = initial;for k = 1:ninitial(k) = mod( sum(bit(9,(k-1)*n+1:k*n)*temp'), 2);endend输出生成矩阵为:genmatrix =0 0 1 00 1 0 01 0 0 01 0 0 11 0 1 11 1 1 10 1 1 11 1 1 0初始状态值生成矩阵为:gm_init =1 1 0 11 0 1 00 1 0 11 1 1 0Verilog代码:`timescale 1ns / 1ps////////////////////////////////////////////////////////////////////////////////// // Company:// Engineer://// Create Date: 15:24:21 05/01/2012// Design Name:// Module Name: PNcode8bit//////////////////////////////////////////////////////////////////////////////////// module PNcode8bit(clk,rst,init,PNout);// PN code n = 4, f(x) = 1 + x + x^4// Output 8 bit per clkparameter order = 4;input clk;input rst;output [order-1 : 0] init;output [7 : 0] PNout;// Output use registerreg [7 : 0] PNout = 0;reg [order-1 : 0] init = 0;// Generate matrix of output, use memoryreg [order-1 : 0] gm_out [7 : 0];// Generate matrix of initial state, use memoryreg [order-1 : 0] gm_init [3 : 0];integer i, j;//////////////////////////////////////////// Memory initialization file read here, generate by Matlabinitialbegin$readmemb("gm_out.txt", gm_out, 7, 0);$readmemb("gm_init.txt", gm_init, 3, 0);end//////////////////////////////////////////always @ (posedge clk)if(rst == 1)beginPNout <= 8'b0;init <= 4'b1000;endelsebeginfor(i=0; i<8; i=i+1)PNout[i] <= (gm_out[i][3] & init[3]) ^ (gm_out[i][2] & init[2]) ^ (gm_out[i][1] & init[1]) ^ (gm_out[i][0] & init[0]);for(j=0; j<4; j=j+1)init[j] <= (gm_init[j][0] & init[0]) ^ (gm_init[j][1] & init[1]) ^ (gm_init[j][2] & init[2]) ^ (gm_init[j][3] & init[3]);endendmodule说明:1.使用readmemb实现存储器数据的初始化,读取二进制内容,因为两个生成矩阵会比较大$readmemb("gm_out.txt", gm_out, 7, 0);"gm_out.txt"为读取的文件,gm_out为存放的存储器名字,7, 0为起始地址和结束地址,最好注明地址范围,不注明好像不太确定2.按位与、按位异或实现二进制矩阵乘法第一个for是输出生成矩阵(8x4)与初始值(4x1)相乘,得到8bit PN码的输出第二个for是初始状态值生成矩阵(4x4)与初始值(4x1)相乘,得到新的初始值gm_out.txt内容:没有空格00100100100010011011111101111110gm_init.txt内容:没有空格1101101001011110测试文件代码:`timescale 1ns / 1ps////////////////////////////////////////////////////////////////////////////////// Company:// Engineer://// Create Date: 16:27:38 05/01/2012// Design Name: PNcode8bit// Module Name: E:/me/CAST/Project/FPGAcomm/PNcode8bit/PNcode8bit_tb.v// Project Name: PNcode8bit////////////////////////////////////////////////////////////////////////////////// module PNcode8bit_tb;// Inputsreg clk;reg rst;// Outputswire [3:0] init;wire [7:0] PNout;// Instantiate the Unit Under Test (UUT)PNcode8bit uut (.clk(clk),.rst(rst),.init(init),.PNout(PNout));initial begin// Initialize Inputsclk = 0;rst = 1;// Wait 100 ns for global reset to finish#100;rst = 0;// Add stimulus hereendalways beginforever #10 clk = !clk;endendmoduleModelSim仿真结果局部放大图,绿色竖线为周期间隔,一个周期的PN码为:001111010110010。

基于verilog的CMI编码实现

/*m序列时钟carry1翻转,divider1重新从origin1计数

/*14.336M/256K=56,所以计数初值为63-56=8

origin2=35;

/*原理同上,14.336M/512K=28,计数初值为63-28=35

3.2程序流程

要求根据输入的时钟信号(14.336MHz)产生一个m序列(256KHz),并对该m序列进行CMI码型变换,最后将CMI码型输出。因为1位输入码元对应2位编码输出,所以输出CMI码频率是输入m序列的2倍,即512KHz。

1、m序列产生

m序列是最长线性反馈移存器序列的简称,它具有均衡性,无直流分量,能够起到载频抑制的作用。

2、实验仪器

JH5001(Ⅲ)通信原理基础实验箱

电脑

3、实验原理

3.1CMI编码规则

CMI码一般作为PCM四次群数字中继接口的码型。它具有检错能力,并且不具有直流分量,是一种很重要的码型。

它的编码规则如下:

表格1CMI编码规则

输入码字

编码结果

0

01

1

00/11交替表示

当输入码字为0时,输出为01码型;对于输入为1的码字,输出有两种情况:输出不仅与当前码字有关,还与前一个1码的输出有关,1码对应的00或11码型,交替出现。由此可以看出,在同步的情况下,输出只对应三种有效码型,10码型无效,因此可以根据这个特点进行检错。

框图如下所示:

所以,易知寄存器各位算式和输出表达式如下:

当初始状态 =1000时,根据上式可以计算出输出m序列的值为000111101011001

2、CMI的1状态记忆

根据CMI编码规则可以看出,1码对应的输出与前一个1码的状态有关,所以在程序中,需要对1码进行记忆,根据上一个1码来判断下一个1码的输出码型。

经典Verilog代码标准

一、工程建立规范:1、工程的组成:(1)一个顶层文件夹(2)顶层文件夹下,至少包括以下四个子文件夹a)project文件夹:存放ISE工程文件,包括ise、bit、mac等文件b)source文件夹:存放verilog源文件c)explain文件件:存放注释说明文档d)test文件夹:存放测试程序代码,可进一步分为软件调试程序、硬件调试程序2、工程的命令:(3)定层文件夹命令为top_xxx,xxx为工程的识别名称(4)顶层文件夹的子文件夹分别命名为:project、source、explain、test二、RTL CODE 规范1.标准的文件头在每一个版块的开头一定要使用统一的文件头,其中包括作者名,模块名,创建日期,概要,更改记录,版权等必要信息。

统一使用以下的文件头:// **************************************************************// COPYRIGHT(c)2005, Hislicon Technologies Co, Ltd// All rights reserved.//// IP LIB INDEX : IP lib index just sa UTOPIA_B// IP Name : the top module_name of this ip, usually, is same// as the small ip classified name just as UTOPIA// File name : file_name of the file just as “tx_fifo.v”// Module name : module_name of this file just as “TX_FIFO”// Full name : complete Emglish nme of this abbreviated//// Author : Athor/ID// Email : Author‟s email// Data :// Version : V 1.0////Abstract :// Called by : Father Module//// Modification history// ------------------------------------------------------------------------------------------------------// //// $Log$//// *********************************************************************2. 标准的module 格式(module 整体结构)对于模块的书写采用统一的格式便于项目内部成员的理解和维护,我们用批处理建立了一个MODULE模块,其内容解释如下:●端口定义按照输入,输出,双向的顺序:●模块名、模块例化名统一,例化名前加大写U_以区分(多次例化另加标识),三者关系:文件名:xxx .v (小写)模块名:Xxx (首字母大写)例化名:U1_xxx (首字母大写)IP 内部所有的模块名都要加IP名或者IP名简称作前缀,如USB_CTRL、USB_TX_FIFO。

M序列原理及代码

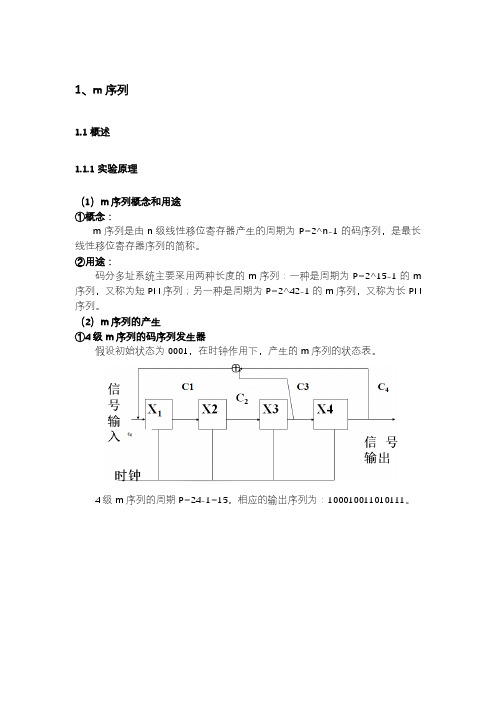

1、m序列1.1概述1.1.1实验原理(1)m序列概念和用途①概念:m序列是由n级线性移位寄存器产生的周期为P=2^n-1的码序列,是最长线性移位寄存器序列的简称。

②用途:码分多址系统主要采用两种长度的m序列:一种是周期为P=2^15-1的m 序列,又称为短PN序列;另一种是周期为P=2^42-1的m序列,又称为长PN 序列。

(2)m序列的产生①4级m序列的码序列发生器假设初始状态为0001,在时钟作用下,产生的m序列的状态表。

4级m序列的周期P=24-1=15,相应的输出序列为:100010011010111。

②线性移位反馈移位寄存器反馈系数Ci③m序列特性均衡性:在一个周期中,m序列中“1”的个数比“0”的个数多1个。

游程特性:长度为k的游程数占游程总数的1/2^k移位相加特性:一个m序列与其循环移位逐位比较,相同码的位数与不同码的位数相差1位。

自相关特性:表征一个信号与延迟后自身信号的相似性。

④m序列的构造——反馈线性反馈移存器1.1.2实验意义m序列是目前广泛应用的一种伪随机序列,在所有的伪随机序列中,m序列是最重要、最基本的一种伪随机序列。

它容易产生,规律性强,有很好的自相关性和较好的互相关特性。

m序列的生成是接下来的实验的基础,具有指导性的意义。

1.1.3系统的主要功能设计本原多项式系数为13、23、103、203的m序列。

1.1.4使用方法输入m后,输出相应的m序列。

1.2程序设计1.2.1设计思想由m序列的产生过程,即通过带反馈的移位寄存器产生,容易想到EDA中的结构化的程序设计思想,即以DFF触发器作为底层文件,进行顶层文件设计,获得m序列。

此设计的优点是程序思路简单,结构清晰,只要做出一种反馈系数的m序列,容易得到其他反馈系数的m序列;但也存在缺点,那就是结构化的设计使得代码写的过长。

1.2.2软件设计流程及描述(1)流程图(2)描述clk上升沿触发程序,用case语句选择m为13,23,103,203中的哪种情况。

基于FPGA的VHDL语言m序列生成详解+源码

说明可控m序列产生器我分成四个小模块来做,M,M1,M2,M3分别对应为:m序列产生器、控制器、码长选择器、码速率选择器。

一、M: m序列产生器这是该设计的核心部分,原理就是设计一个通用m序列产生子单元,然后由外部选择器来写入码型,码长等参数,加以循环可连接成任意长度的m序列产生器,其子单元结构如下:如上图,若N=15,就有15个这样的子单元首尾相接。

注意:开头和结尾的两个子单元会有所不同,因为首单元需要输入初值,尾单元要进行直通反馈,在程序里请多留意。

图中,主要部件是一个D触发器,Q(N+1)为上一级输出;Q(N)既是本级输出;CP为选择后的时钟脉冲;B(N)为本级参数选择控制;A(N)受控于B(N),决定本级输出Q(N)是否反馈(B(N)为1时反馈);C(N)为本级反馈;C(N-1)为下一级反馈。

具体原理参看m序列组成结构。

此外,本程序还加入了EN(发送控制)、RN(首单元置数)、SEL1(码长选择,即N的选择,N=2-15)、SEL2(码型选择,即正逆码选择)四个控制端,可满足设计要求。

OP为码输出端。

二、M1:控制器控制器主要是将外部的序列发送控制信号STA转换为EN和RN 两个控制信号。

其中,EN与STA的波形基本一致,只是它与CP进行了同步处理;RN在EN为‘1’的头一个脉冲周期里置高电平,以达到为序列发生器的首端置数的目的。

如果不清楚的话可以看一下它的模拟波形。

(注意:STA要采用自锁定开关,高电平有效)三、M2:码长选择序列的码长选择既是N值的选择,码长=2**N-1。

核心就是一个计数器,可从2计到15。

按一次PUSH就可以自动加一(注意:按键建议采用自弹跳按键,如过需要软件清除按键震颤的话,我再做发给你),没有0,1两个状态。

如果需要的话还可以扩展7段数码管的接口,以显示N值。

四、M3:码速率选择器码的传输速率是靠CP来控制的,CP的频率就等于码元速率。

这段程序包含一个倍频器,一个5分频的分频器,可把5MHZ的脉冲源CLK扩展成1MHZ和10MHZ。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

// 可综合模块

// 此模块将signal.v 中产生的indata信号进行编码:

// 1 编码成为31位的+M序列;0 编码为-M 序列。

// 其中包括了一个5级的移位寄存器用于产生M序列。

`timescale 1ns/1ns

module coder( c lk_1, //数据输入时钟

clk_31, //数据输出时钟

indata, //输入数据

outdata, //输出数据

rst, //启动信号

en); //使能信号

input clk_1,clk_31;

input rst,en;

input indata;

output [1:0] outdata; //输出信号:+1表示代码1 ;-1表示代码0

wire [1:0] outdata;

reg indata_buf; //输入积存器

reg [4:0] shift_buf; //M序列产生的5位移位积存器

assign outdata =(en)?(((indata_buf^shift_buf[0])==1)?2'b11:2'b01):2'b00; //当en信号高电

平时,

//输入信号为1时产生+M序列

//输入信号为-1时产生-M序列

always@(posedge clk_1) //clk_1信号来临则将输入信号indata积存到indata_buf中

indata_buf <=indata;

always@(posedge clk_31)

begin

if(!rst)

shift_buf <=5'b10000; //五位初始为10000

if(en)

begin

shift_buf[4] <=shift_buf[0]^shift_buf[3]; //5级M序列编码规则

shift_buf[0] <= shift_buf[1];

shift_buf[1] <= shift_buf[2];

shift_buf[2] <= shift_buf[3];

shift_buf[3] <= shift_buf[4];

end

end。