GD32VF103R-START评估板用户指南_V1.1

GD32固件库使用手册 (USART TIMER)

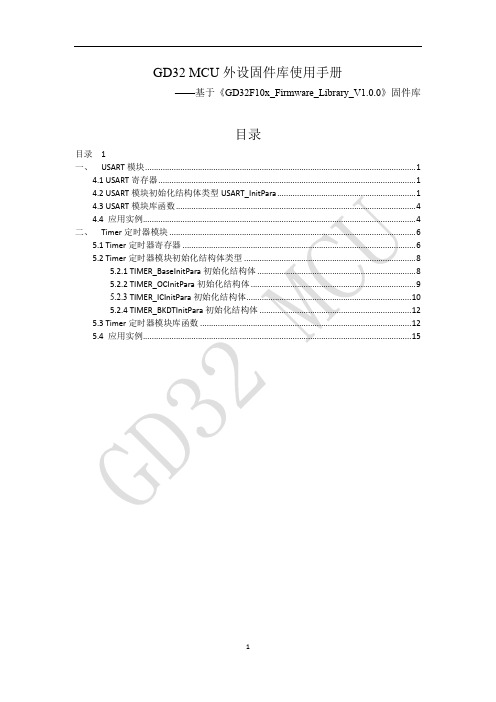

GD32 MCU外设固件库使用手册——基于《GD32F10x_Firmware_Library_V1.0.0》固件库目录目录 1一、USART模块 (1)4.1 USART寄存器 (1)4.2 USART模块初始化结构体类型USART_InitPara (1)4.3 USART模块库函数 (4)4.4 应用实例 (4)二、Timer定时器模块 (6)5.1 Timer定时器寄存器 (6)5.2 Timer定时器模块初始化结构体类型 (8)5.2.1 TIMER_BaseInitPara初始化结构体 (8)5.2.2 TIMER_OCInitPara初始化结构体 (9)5.2.3 TIMER_ICInitPara初始化结构体 (10)5.2.4 TIMER_BKDTInitPara初始化结构体 (12)5.3 Timer定时器模块库函数 (12)5.4 应用实例 (15)一、USART模块USART模块的固件库文件为gd32f10x_usart.c和gd32f10x_usart.h,包含USART模块初始化、使能、发送数据、接受数据等功能。

4.1 USART寄存器USART模块寄存器的定义见代码清单4.1.1所示。

代码清单4.1.1 USART模块寄存器定义USART_InitPara-> USART_STBits成员变量可从USART_STBits所定义的宏中取值,USART_STBits的宏定义如代码清单4.2.2所示。

代码清单4.2.2 USART_STBits宏定义代码USART_InitPara-> USART_Parity成员变量可从USART_Parity所定义的宏中取值,USART_Parity的定义如代码清单4.2.3所示。

其中USART_PARITY_RESET表示无奇偶校验,其中,USART_HARDWAREFLOWCONTROL_NONE表示不使用硬件流控制;USART_HARDWAREFLOWCONTROL_RTS表示使用RTS流控制;USART_HARDWAREFLOWCONTROL_CTS表示使用CTS流控制;USART_HARDWAREFLOWCONTROL_RTS_CTS表示使用RTS/CTS流控制。

RISC-V MCU的FreeRTOS移植与应用开发

4M i c r o c o n t r o l l e r s &E m b e d d e d S ys t e m s 2021年第1期w w w .m e s n e t .c o m .c nR I S C V M C U 的F r e e R T O S 移植与应用开发付元斌,张爱华,何小庆(北京麦克泰软件技术有限公司,北京100085)摘要:具有相同的R I S C V 指令集的处理器实现并不相同㊂本文将针对基于R I S C V 开源指令集的处理器芯片G D 32V F 103M C U ,介绍F r e e R T O S 在I A R E WR I S C V 编译和开发环境下的移植过程㊂采用R T O S 后,嵌入式系统很难监控系统的运行时行为㊁发现应用存在的问题,本文基于T r a c e a l y z e r 分析工具直观地跟踪系统行为,分析系统中可能的错误,提高代码的鲁棒性㊂关键词:B u m b l e b e e 内核;T r a c e a l yz e r ;F r e e R T O S 移植;R I S C V 处理器中图分类号:T P 316.2 文献标识码:AP o r t i n g a n d A p p l i c a t i o n D e v e l o pm e n t o f F r e e R T O S B a s e d o n R I S C V M C U F u Y u a n b i n ,Z h a n g A i h u a ,H e X i a o q i n g(B e i j i n g M i c r o t e c R e s e a r c h S o f t w a r e T e c h n o l o g y C o .L t d .,B e i j i n g 100085,C h i n a )A b s t r a c t :P r o c e s s o r i m p l e m e n t a t i o n s w i t h t h e s a m e R I S C V i n s t r u c t i o n s e t a r e n o t t h e s a m e .T h i s p a p e r w i l l i n t r o d u c e t h e m i gr a t i o n p r o c e s s o f F r e e R T O S u n d e r I A R E WR I S C V e n v i r o n m e n t f o r t h e p r o c e s s o r c h i p G D 32V F 103b a s e d o n R I S C V o p e n s o u r c e i n s t r u c -t i o n s e t .W i t h t h e R T O S ,i t i s d i f f i c u l t t o m o n i t o r t h e r u n t i m e b e h a v i o r o f t h e s y s t e m a n d f i n d p r o b l e m s i n t h e a p pl i c a t i o n .T h i s a r t i c l e w i l l u s e t h e T r a c e a l y z e r a n a l y s i s t o o l t o v i s u a l l y s y s t e m b e h a v i o r ,a n a l y z e p o s s i b l e e r r o r s i n t h e s y s t e m ,a n d i m pr o v e t h e r o b u s t n e s s o f t h e c o d e .K e yw o r d s :B u m b l e b e e K e r n e l ;T r a c e a l y z e r ;F r e e R T O S p o r t i n g ;R I S C V M C U 0 引 言R I S C V 是基于精简指令集(R I S C )原则的开源指令集架构(I S A ),具有良好的应用前景㊂目前R I S C V 架构的处理器陆续发布,其生态环境及应用也在不断丰富,但相对于A R M 架构,R I S C V 的应用还处于起步阶段,复杂的应用需要R T O S 支撑㊂目前许多R T O S ,如μC /O SI I I ㊁F r e e R T O S ㊁R T T h r e a d ㊁Z e p h y r O S ㊁e m b O S 等,都提供了对R I S C V 处理器的支持㊂采用了R T O S 后,传统的调试手段很难监控系统的实时行为,在R T O S 上进行开发时需要额外的工具和方法验证你的软件行为,提高代码的可靠性㊂本文使用兆易创新的G D 32V F 103V E V A L 开发板,基于I A R E W R I S C V 编译和开发环境,介绍如何将F r e e R T O S移植到G D 32V F 103上,并使用P e r c e p i o 的T r a c e a l y z e r 工具分析基于F r e e R T O S 的应用程序运行时行为㊂1 G D 32V F 103R I S C V M C UG D 32V F 103R I S C V M C U 基于N u c l e i B u m b l e b e e内核,芯片提供了108MH z 的主频,以及16~128K B 的片上闪存和6~32K B 的S R AM ,具有多个通用定时器和多通道D MA 控制器㊂G D 32V F 103M C U 的中断控制器(E C L I C )提供了多达68个外部中断并可嵌套16个可编图1 G D 32V F 103V E V A L 评估板程优先级,G D 32V F 103M C U 支持多种外设如U A R T ㊁S P I ㊁I 2C ㊁G P I O 等㊂GD 32V F 103VE V A L 评估板(见图1)使用G D 32VF 103V B T 6作为主控制器,板载J T A G接口以及丰富的外设资源㊂R T O S 在G D 32V F 103上的移植仅使用了内核相关的资源㊂N u c l e i B u m b l e b e e 内核支持R V 32I MA C 指令集架构;特权模式支持机器模式和用户模式,可以实现R T O S 与应用的隔离,提升软件安全;寄存器组包含32个通用寄存器㊁R I S CV 标准的状态寄存器以及内核自定义敬请登录网站在线投稿(t o u g a o.m e s n e t.c o m.c n)2021年第1期5的C S R寄存器㊂内核提供了计时器单元(T i m e r U n i t, T I M E R),产生的计时器中断和软件中断可以用于R T O S 时钟节拍处理和任务切换㊂B u m b l e b e e内核支持在R I SC V标准C L I C基础上优化而来的改进型内核中断控制器(E n h a n c e d C o r e L o c a l I n t e r r u p t C o n t r o l l e r,E C L I C),用于管理所有的中断源㊂E C L C的每个中断源可以配置为向量或非向量处理模式㊂向量模式中断被处理器内核响应后,处理器直接跳入该中断的向量入口存储的目标地址;非向量模式中断被处理器响应后,处理器直接跳入所有中断共享的入口地址㊂但中断响应时,处理器硬件不会保存上下文,需要软件实现㊂2F r e e R T O S和T r a c e a l y z e r介绍F r e e R T O S是英国人R i c h a r d B a r r y2003年发布的开源实时内核㊂F r e e R T O S支持超过35种C P U架构,是世界最受开发者欢迎的R T O S,在2017年每3分钟就有一次下载㊂F r e e R T O S有一个系列软件,包括F r e e R T O S(开源版本)㊁O p e n R T O S(授权版本)㊁S A F E R T O S(安全版本)和A m a z o n F r e e R T O S(开源物联网操作系统),开源的F r e e R T O S遵循M I T l i c e n s e模式㊂在多线程软件系统中,R T O S带来的复杂度让源代码和运行时行为的关联变得不那么明显,传统的调试器不足以理解系统的行为,特别是运行时行为㊂P e r c e p i o的T r a c e a l y z e r工具运行在W i n d o w s或L i n u x P C上,可用于目标系统运行L i n u x㊁F r e e R T O S㊁O p e n R T O S㊁S A F E R T O S㊁W i n d R i v e r V x W o r k s㊁μC/O SI I I和e m b O S的R T O S应用行为分析㊂2.1F r e e R T O S的功能F r e e R T O S支持抢占和时间片轮询两种任务调度方式,支持无限数量的应用任务;提供队列㊁信号量㊁互斥信号量㊁事件标志等内核机制,满足任务间同步及通信需求;此外,针对低功耗应用提供了t i c k l e s s模式㊂最新版本F r e e R T O S提供了针对I A R及G C C工具链的标准R I S C V处理器内核移植示例,支持32位及64位架构内核(R V32I和R V64I)㊂它包含了预配置的O p e n I S A V E G-A b o a r d㊁S i F i v eH i F i v e开发板㊁Q E MU模拟器以及用于M i c r o c h i p M2G L025开发板的A n t m i c r o R e n o d e模拟器示例,可以扩展支持任何RI S C V处理器,但因为每种R I S C V处理器在微架构实现上的不同,需要有移植的工作㊂2.2T r a c e a l y z e r分析工具T r a c e a l y z e r软件工具能够快速㊁轻松地收集多任务软件有用和有意义的行为,可以快速集成到现有的开发环境,通过快照模式或流模式采集系统运行时数据㊂T r a c e-a l y z e r提供超过30种视图可视化R T O S运行时行为,视图间以直观的方式相互关联,洞察运行时行为(包括任务运行时间信息㊁各任务之间的通信流㊁C P U的使用率等),帮助开发人员解决问题,提高软件的可靠性,改善软件的性能㊂3F r e e R T O S移植到G D32V F103M C UF r e e R T O S内核绝大部分都采用C语言编写,只有与处理器相关的上下文切换采用汇编语言实现,目的是保证上下文切换的效率㊂将F r e e R T O S移植到G D32V F103 M C U上的关键要点是实现以下4个步骤:开启和关闭中断的方式;进入和退出临界区的方式;产生周期性的中断作为系统的时钟节拍;任务的上下文切换㊂3.1中断管理和临界区实现代码的临界区也称为代码的临界段,这部分代码在执行时不允许被打断㊂F r e e R T O S的临界区通过关中断来实现,在进入临界段之前须关中断,而临界段代码执行完毕后要立即开中断㊂G D32V F103M C U的E C L I C中断控制器有一个中断目标阈值级别寄存器(m t h),可以实现部分中断屏蔽,优先级别低于该阈值的中断将不会被响应㊂在移植F r e e R T O S时,通过设置m t h来实现开关中断,对于优先级别比阈值高的中断则不受F r e e R T O S管理,中断不存在额外的延迟㊂3.2系统时钟节拍支持操作系统需要一个时钟节拍,以实现系统的延时㊁超时等与时间相关的处理㊂时钟节拍是特定的周期性中断,中断的周期就是节拍的时间㊂节拍的时间长短根据实际应用决定,时钟节拍的频率越高,系统的开销就越大㊂R I S C V架构定义了一个64位宽度的m t i m e计数器,当m t i m e计数值增加到与m t i m e c m p寄存器预设的值相等时,可以产生中断㊂选择m t i m e计数器来产生系统时钟节拍,根据m t i m e的时钟频率和系统节拍频率算出m t i m e c m p的值,当中断发生后,通过改写m t i m e c m p或者m t i m e的值来清除中断㊂3.3实现上下文切换上下文是某一时间点C P U的寄存器内容,F r e e R T O S 能够正确完成任务调度的关键是上下文切换㊂上下文切换的过程包括:把即将退出运行态的任务的运行现场保存到其任务堆栈;从下一个要运行的任务的堆栈中恢复它的运行现场㊂上下文切换的时间应尽可能短,一般由汇编代码编写,作为操作系统移植的一部分㊂上下文切换分为任务级别及中断级别的切换㊂上下文切换的代码通常放在异常处理程序中,该异常的优先级别应设置为最低㊂在R I S C V架构的处理器上,能够用来作为任务切6M i c r o c o n t r o l l e r s &E m b e d d e d S ys t e m s 2021年第1期w w w .m e s n e t .c o m .c n换的异常有两种:e c a l l 异常和软件中断㊂e c a l l 异常通过调用e c a l l 指令来触发;软件中断通过往m s i p 寄存器写 1 触发,写 0 清除㊂G D 32V F 103的软件中断连接到E C L I C 单元进行统一管理㊂我们实现的F r e e R T O S 移植选用软件中断作为上下文切换的实现机制㊂3.4 移植文件修改F r e e R T O S 与处理器相关的移植代码存储在p o r t -m a c r o .h ㊁po r t A S M.s 和p o r t .c 三个文件当中㊂p o r t m a c -r o .h 头文件定义了F r e e R T O S 使用的数据类型㊁进入和退出临界区的宏㊁实现开关中断的宏,以及触发和清除软件中断的宏㊂po r t A S M.s 中用汇编语言实现v P o r t S t a r t F i r s t T a s k ()函数,用于启动第一个任务,它的核心操作是从p x C u r r e n t -T C B 中取出当前就绪任务中优先级最高任务的堆栈指针S P ,通过S P 恢复寄存器现场㊂此外,实现软件中断的服务函数e c l i c _m s i p _h a n d l e r ()将当前的寄存器现场(通用寄存器x 1㊁x 5~x 31,机器模式状态寄存器m s t a t u s 以及机器模式异常P C 寄存器m e p c )保存到当前在运行任务的堆栈当中,然后从p x C u r r e n t T C B 取出下一个就绪中优先级最高任务的堆栈指针S P 恢复寄存器现场,完成任务的上下文切换㊂po r t .c 文件中重点实现堆栈初始化函数p x P o r t I n i t i a -l i s e S t a c k ()㊁启动F r e e R T O S 调度器特定的处理函数x P o r t S t a r t S c h e d u l e r ()㊁系统时钟节拍定时器初始化函数v P o r t S e t u p T i m e r I n t e r r u pt (),以及系统时钟节拍中断服务函数x P o r t S y s T i c k H a n d l e r ()㊂这几个函数分别需要根据R I S C V 架构和G D 32V F 103M C U 硬件特性来实现其功能㊂3.5 移植测试和验证验证移植采用调试和借助相应的辅助工具来进行,使用I A R E WR I S C V 建立项目,在代码中创建两个用户任务进行调试,代码调试时需要验证:①通过在系统时钟节拍I S R 和软件中断I S R 中添加断点,结合R I S C V 的m t i m e 和m c y c l e 寄存器验证系统时钟节拍正确产生,且软件中断能够正常触发㊂②启动第一个任务时,通过添加断点查看从任务堆栈中恢复的寄存器内容是否与堆栈初始化时写入的内容一致,从而测试p x P o r t I n i t i a l i s e S t a c k ()和v P o r t S t a r t F i r s t -T a s k()函数的工作正确性㊂③在执行任务上下文切换时,在软件中断服务程序中添加断点,单步执行,同时通过E WR I S C V 的m e m o r y 观察窗口查看压栈到当前任务堆栈中的内容是否与对应的寄存器内容相同;在恢复下文时,检查从下一个执行任务堆栈中恢复的寄存器内容是否与堆栈中的一致㊂验证e c l i c _m s i p_h a n d l e r ()软件中断服务函数的上下文切换正确性㊂④启动第一个任务和任务上下文切换的代码验证能正常工作,移植的F r e e R T O S 已可以实现基本的任务调度,接着再继续测试开关中断操作和临界区是否正常㊂测试开关中断需要增加另外一个外设中断,将其优先级别分别设置大于或小于m t h 阈值进行测试,代码中手动调用开关中断操作A P I ,检测中断触发是否与设计的模式一致,验证F r e e R T O S 对中断的控制㊂采用同样的方法测试进入和退出临界区㊂⑤通过F r e e R T O S 系统服务调用测试,测试系统的各项服务(如信号量㊁消息队列㊁事件标志等)是否正常,并测试在受F r e e R T O S 管理的I S R 中发信号㊁消息等操作是否正确㊂基础调试测试都通过之后,已经基本可以验证移植是否成功㊂在此基础上还可以借助额外的工具继续验证,例如通过E WR I S C V 自带的F r e e R T O S 调试插件显示的信息进行确认(如图2所示)㊂图2 E W R I S C V R T O S 调试插件T a s k 窗口4 T r a c e a l yz e r 分析工具的应用4.1 移植跟踪记录器库T r a c e a l yz e r 的跟踪记录器库是运行在嵌入式目标端的一个软件库,与F r e e R T O S 项目集成在一起,负责记录R T O S 在运行时产生的事件㊂记录的事件如果是存储在R AM 中,这种工作方式称为快照模式(S n a p s h o t );如果是通过通信端口实时发送到P C 端软件,则工作在流模式(S t r e a m i n g)㊂跟踪记录器库不依赖于处理器硬件,只需要使用一个高精度的定时器产生时间戳,为记录的事件添加时间信息㊂R I S C V 架构的处理器可以利用内核的m c y c l e 计数器来产生时间戳,m c y c l e 是一个64位的计数器,对C P U 的周期进行计数,所以频率与C P U 时钟相同,精度非常高㊂m c y c l e 由两个32位的寄存器组成,T r a c e a l y z e r 只需要使用低32位寄存器㊂在t r c H a r d w a r e P o r t .h 中定义G D 32V F 103的时间戳实现接口:#d e f i n e T R C _HW T C _T Y P E T R C _F R E E _R U N N I N G _32B I T _I N -C R#d e f i n e T R C _HWT C _C O U N T r e a d _c s r (m c yc l e )#def i n e T R C _HWT C _P E R I O D 0敬请登录网站在线投稿(t o u ga o .m e s n e t .c o m.c n )2021年第1期7#d e f i n e T R C _HWT C _D I V I S O R 4#d e f i n e T R C _HWT C _F R E Q _H Z T R A C E _C P U _C L O C K _H Z #d e f i n e T R C _I R Q _P R I O R I T Y _O R D E R 1T r a c e a l y z e r 也需要实现临界区,防止在记录事件时发生任务切换,导致产生错误㊂实现是通过关中断,可以直接使用F r e e R T O S 的关中断机制在t r c K e r n e l P o r t .h 中实现临界区的宏接口:#d e f i n e T R A C E _A L L O C _C R I T I C A L _S E C T I O N ()i n t __i r q _s t a t u s;#d e f i n e T R A C E _E N T E R _C R I T I C A L _S E C T I O N ()__i r q _st a -t u s =p o r t S E T _I N T E R R U P T _MA S K _F R OM _I S R ();#d e f i n e T R A C E _E X I T _C R I T I C A L _S E C T I O N ()po r t C L E A R _I N T E R R U P T _MA S K _F R OM _I S R (__i r q_s t a t u s );以上是将T r a c e a l yz e r 跟踪记录器库移植到一款处理器上需要做的工作㊂4.2 跟踪并分析F r e e R T O S 应用将T r a c e a l yz e r 跟踪记录器库添加到E WR I S C V 的F r e e R T O S 项目中,并进行必要的配置,工作在快照模式㊂在应用代码中创建4个任务,分别为L e d 1T a s k~L e d 3T a s k ㊁B u t t o n T a s k ,任务优先级依次递增,程序运行一段时间,将快照数据通过E WR I S C V 保存成H e x 文件并加载到P C 端的T r a c e a l yz e r 中进行分析㊂如图3所示,通过水平时间轴视图查看各个任务的执行情况:每个任务或中断占一行,从左向右为时间轴的方向,行中有色矩形为该任务或中断的一次执行实例㊂由时间轴窗口可以快速地预览整个运行过程中系统的执行情况,放大窗口的时间分辨率之后可以仔细了解任务执行时相关的内核事件和时间信息㊂图3 T r a c e a l yz e r 水平时间轴视图4.3 任务的时间量分析R T O S 的任务或者中断称为参与者(A c t o r),参与者的一次执行称为实例㊂分析任务的执行通常需要了解如下几种时间:起始和结束时间,参与者实例的开始和结束时间;执行时间,参与者实例使用的C P U 时间量,不包括抢占;响应时间,从参与者实例开始到结束的时间(更确切地说,任务的响应时间是从任务开始准备就绪时计算的,即内核将任务的调度状态设置为就绪的时间);等待时间,图4所示实例中参与者实际没有执行的时间,计算方式为[(结束时间开始时间)(执行时间)];启动时间,从任务就绪到开始执行之间的这段时间㊂图4 F r e e R T O S 分析基础实例的时间关系(场景2发生了抢占)以L e d 3T a s k 的第38个实例(如图5所示)为例,等待时间为从任务就绪到任务代码开始执行的这段时间,时长为7μs ,因为该实例未发生被抢占的情况,所以这7μs 的时间是完成任务上下文切换所需的时间㊂图5 L e d 3T a s k 任务实例38的时间量通过跟踪到的事件和记录的时间戳信息,T r a c e a l yz e r 能够生成多种视图来观测系统运行时存在的问题,例如设计缺陷导致的线程饥饿㊁死锁等,以及发现系统中不必要的延迟,帮助开发者解决系统的问题,提高嵌入式系统的实时性㊂这些问题使用传统调试手段难以发现,而且效率不高㊂5 结 语本文介绍了基于R I S C V 指令集的微控制器G D 32V F 103在I A R E W R I S C V 工具链上移植F r e e R T O S的过程,以及对移植的系统进行验证的方法㊂在此基础上移植T r a c e a l y z e r 跟踪记录器库,并通过跟踪F r e e R T O S 系统运行进一步观测系统的运行,并对任务的执行进行了分析㊂嵌入式与物联网是R I S CV 最活跃的应用市场,R I S C V 给嵌入式系统开发带来许多优势,越来越多的开发者开始尝试R I S C V ㊂以上工作对于基于R T O S 技术的R I S C V 嵌入式开发与应用会有所帮助㊂参考文献[1]芯来科技.B u m b l e b e e 内核指令架构手册[E B /O L ].[202009].h t t p s ://w w w.r i s c v m c u .c o m /qu i c k s t a r t q u i c k s t a r t i n d e x u p d f i d 8.h t m l .2626M i c r o c o n t r o l l e r s &E m b e d d e d S ys t e m s 2021年第1期w w w .m e s n e t .c o m .c n在D C A S E 2019测试集和U r b a n S o u n d 8K 测试集上,模型的识别精度如表1和表2所列,并且与一些最新的方法进行了对比㊂表1 精度比较(D C A S E 2019)模 型测试精度(D C A S E )A u d i o R e s n e t80.2%R e s N e t l i k e m o d e l [14]76.6%B a s e l i n e s ys t e m [15]62.5%表2 与其他方法的精度比较模 型测试精度(U r b a n S o u n d 8K )A u d i o R e s n e t76.4%U n s u p e r v i s e d f e a t u r e l e a r n i n g[16]73.6%B a s e l i n e s ys t e m [17]68%从表中可以看到,与其他先进的分类方法相比,本文提出的A u d i o R e s ne t 模型在分类精度上有较大提高㊂4 结 语本文针对声源目标分类中小样本训练时分类模型性能不佳的问题,使用深度学习方法对不同声源发出的声音数据进行分类,使用l o g me l 声谱图特征作为特征预提取方法,采用基于R e s n e t 网络结构的分类模型对预提取特征数据进行分类处理,建立了识别效果良好的深度学习声信号分类模型A u d i o R e s n e t ㊂该模型性能在D C A S E 2019和U r b a n S o u n d 8K 数据集上得到了验证,实现了良好的效果,在声源探测领域具有一定的工程应用价值㊂参考文献[1]I S N A R D V ,C HA S T R E S V ,V I A U DD E L MO N I ,e t a l .T h e t i m e c o u r s e o f a u d i t o r y r e c o g n i t i o n m e a s u r e d w i t h r a pi d s e q u e n c e s o f s h o r t n a t u r a l s o u n d s [J ].S c i e n t i f i c R e po r t s ,2019,9(1):8005.[2]樊新海,石文雷,张传清.基于V M D 多尺度熵和A B C S V M 的装甲车辆识别[J ].装甲兵工程学院学报,2018,32(6):6873.[3]孙国强,樊新海,石文雷.基于M F C C 和支持向量机的装甲车辆识别研究[J ].国外电子测量技术,2017,36(10):3135.[4]R U B E N G O N Z A L E ZH E R N A N D E Z F ,P A S T O RS A N C H E Z F E R N A N D E Z L ,S U A R E Z G U E R R A S ,e ta l .M a r i n e m a mm a l s o u n d c l a s s i f i c a t i o nb a s e d o n a p a r a l l e lr e c o g n i t i o n m o d e l a n d o c t a v e a n a l y s i s [J ].A p pl i e d A c o u s t i c s ,2017(119):1728.[5]S A N C H E Z F E R N A N D E Z L P ,S A N C H E Z P E R E Z L A ,C A R B A J A L H E R N A NDE Z J J ,e t a l .A i r c r a f t C l a s s i f i c a t i o na n d A c o u s t i c I m pa c t E s t i m a t i o n B a s e d o n R e a l T i m e T a k e o f f N o i s e M e a s u r e m e n t s [J ].N e u r a l P r o c e s s i n g Le t t e r s ,2013,38(2):239259.[6]陈心昭.噪声源识别技术的进展[J ].合肥工业大学学报(自然科学版),2009,32(5):609614.[7]竺乐庆,张真.基于M F C C 和GMM 的昆虫声音自动识别[J ].昆虫学报,2012,55(4):466471.[8]石文雷,樊新海,张传清.基于频谱动态特征和C S S VM 的装甲车辆识别[J ].计算机应用,2018,38(S 1):4447,72.[9]董语诗,时浏艺,丁一坤.基于HMM 的声场景分类[J ].信息化研究,2018,44(3):3947,52.[10]中兴通讯采用英特尔F P G A 在深度学习上取得性能突破[J ].单片机与嵌入式系统应用,2017,17(3):88.[11]庞悦,赵威,张雅楠,等.基于深度学习的L S T M 的交通流量预测[J ].单片机与嵌入式系统应用,2019,19(3):7275.[12]王枫,陈小平.C N N 深度学习的验证码识别及A n d r o i d 平台移植[J ].单片机与嵌入式系统应用,2019,19(7):2022,73.[13]P I R O T T A E ,M E R C HA N T N D ,T HOM P S O N P M ,e t a l .Q u a n t i f y i n g th e e f f e c t o f b o a t d i s t u r b a n c e o n b o t t l e n o s e d o l -p h i n f o r a g i n g a c t i v i t y[J ].B i o l C o n s e r v ,2015(181):8289.[14]N g u y e n T ,P e r n k o pf F .A c o u s t i c S c e n e C l a s s i f i c a t i o n w i t h M i s m a t c h e d R e c o r d i ng D e v i c e s U s i n g M i x t u r e o f E x pe r t s L a ye r [C ]//2019I E E E I n t e r n a t i o n a l C o nf e r e n c e o n M u l t i -m e d i a a n d E x po (I C M E ),2019.[15]M e s a r o s A ,H e i t t o l a T ,V i r t a n e n T.A m u l t i d e v i c e d a t a s e tf o r u r b a n a c o u s t i c s c e n e c l a s s i f i c a t i o n [J ].2018,a r X i v :1807.09840.[16]S a l a m o n J ,J a c o b y C ,B e l l o J P .A D a t a s e t a n d T a x o n o m yf o r U r b a n S o u n d R e s e a r c h [C ]//a c m I n t e r n a t i o n a l C o n f e r e n c eo n M u l t i m e d i a ,2014.[17]S A L AMO N J ,J A C O B Y C ,B E L L O J P .A D a t a s e t a n d T a x -o n o m y f o r U r b a n S o u n d R e se a r c h [C ]//p r o c e e d i n gs o f t h e a c m I n t e r n a t i o n a l C o n f e r e n c e o n M u l t i m e d i a ,2014.王鹏程(硕士研究生),主要研究方向为信息探测与处理㊂(责任编辑:薛士然 收稿日期:2020-07-20) [2]胡振波.R I S C V 架构与嵌入式开发快速入门[M ].北京:人民邮电出版社,2019.[3]何小庆.3种物联网操作系统分析与比较[J ].微纳电子与智能制造,2020(3).[4]D A V I D P A T T E R S O N ,A N D R E W W A T E R M A N.R I S CV手册:一本开源指令集的指南,2018.[5]U s i n g Fr e e R T O S o n R I S C V M i c r o c o n t r o l l e r s [E B /O L ].[202009].h t t p s ://w w w.f r e e r t o s .o r g /U s i n g Fr e e R T O S o n R I S C V.h t m l .[6]J i m C o o l i n g .R e a l t i m e O p e r a t i n g S ys t e m s B o o k 2T h e P r a c t i c e [M ].M a r k f i e l d :L i n d e n t r e e A s s o c i a t e s ,2017.(责任编辑:芦潇静 收稿日期:2020-09-10)。

ESP32 Chip Revision v3.0 用户指南说明书

ESP32 Chip Revision v3.0 User GuideVersion 1.3Espressif SystemsCopyright © 2022About This GuideThis document describes differences between chip revision v3.0 and previous ESP32 chiprevisions.Release NotesDocumentation Change NotificationEspressif provides email notifications to keep customers updated on changes totechnical documentation. Please subscribe at https:///en/subscribe .CertificationDownload certificates for Espressif products from https:///en/certificates . DateVersion Release notes 2020.01V1.0Initial release.2020.07V1.1Added item 6 to Chapter 1 Design Changes in ECO V3.2022.10v1.2Replaced “ECO” with “Chip Revision” Renamed this document as “ESP32 Chip Revision v3.0 User Guide”2022.11v1.3Added item 1 to Chapter 1 Design Changes in ECO V3.Table of Contents................................................................................. 1.Design Changes in Chip Revision v3.0 1............................................................................................... 2.Impact on Customer Projects 2..........................................................................e Case 1: Hardware and Software Upgrade 2........................................................................................e Case 2: Hardware Upgrade Only 2................................................................................................................ bel Specification 3............................................................................................................. 4.Ordering Information 41. Design Changes in Chip Revision v3.0 1.Design Changes in ChipRevision v3.0Espressif has released ESP32 chip revision v3.0 that features wafer-level changes basingon previous ESP32 chip revisions. The design changes introduced on the ESP32 chiprevision v3.0 are:1.Fixed "Due to the flash start-up time, a spurious watchdog reset occurs when ESP32 ispowered up or wakes up from Deep-sleep". Details of the issue can be found in item 3.8in ESP32 Series SoC Errata.2.PSRAM Cache Bug Fix: Fixed “When the CPU accesses the external SRAM in a certainsequence, read & write errors can occur”. Details of the issue can be found in item 3.9 inESP32 Series SoC Errata.3.Fixed “When each CPU reads certain different address spaces simultaneously, a readerror can occur”. Details of the issue can be found in item 3.10 in ESP32 Series SoCErrata.4.Optimized 32.768 KHz crystal oscillator stability. The issue was reported by client thatthere is a low probability that on chip revision v1.0 hardware, the 32.768 KHz crystaloscillator couldn’t start properly.5.Fixed Fault injection issues regarding secure boot and flash encryption are fixed.Reference: Security Advisory concerning fault injection and eFuse protections(CVE-2019-17391) & Espressif Security Advisory Concerning Fault Injection and SecureBoot (CVE-2019-15894)6.Improvement: Changed the minimum baud rate supported by the TWAI module from 25kHz to 12.5 kHz.7.Allowed Download Boot mode to be permanently disabled by programming new eFusebit UART_DOWNLOAD_DIS. When this bit is programmed to 1, Download Boot modecannot be used and booting will fail if the strapping pins are set for this mode. Softwareprograms this bit by writing to bit 27 of EFUSE_BLK0_WDATA0_REG, and reads this bitby reading bit 27 of EFUSE_BLK0_RDATA0_REG. Write disable for this bit is shared withwrite disable for the flash_crypt_cnt eFuse field.12022.11 Espressif /52. Impact on Customer Projects 2.Impact on Customer ProjectsThis section is intended to help our customers to understand the impact of using chiprevision v3.0 in a new design or replacing older version SoC with chip revision v3.0 inexisting design.e Case 1: Hardware and Software UpgradeThis is the use-case where the new project is being initiated or upgrade for hardware andsoftware in an existing project is a possible option. In such a case, the project can benefitfrom protection against fault injection attack and can also take advantage of newer secureboot mechanism and PSRAM cache bug fix with slightly enhanced PSRAM performance.1.Hardware Design Changes:Please follow the latest ESP32 Hardware Design Guidelines. For 32.768 KHz crystaloscillator stability issue optimization, please refer to Section Crystal Oscillator for moreinformation.2.Software Design Changes:1)Select Minimum configuration to Rev3: Go to menuconfig > Conponent config >ESP32-specific, and set the Minimum Supported ESP32 Revision option to “Rev3”.2)Software version: Recommend to use RSA-based secure boot from ESP-IDF v4.1and later. ESP-IDF v3.X Release version can also work with application with originalsecure boot V1.e Case 2: Hardware Upgrade OnlyThis is the use-case where customers have existing project which can allow hardwareupgrade but software needs to remain the same across hardware revisions. In this case theproject gets benefit of security to fault injection attacks, PSRAM cache bug fix and32.768KHz crystal oscillator stability issue. The PSRAM performance continues to remainthe same though.1.Hardware Design Changes:Please follow latest ESP32 Hardware Design Guidelines.2.Software Design Changes:Client can continue to use the same software and binary for deployed product. Thesame application binary will work on both chip revision v1.0 and chip revision v3.0.3. Label Specification bel SpecificationThe label of ESP32-D0WD-V3 is shown below:The label of ESP32-D0WDQ6-V3 is shown below:4. Ordering Information 4.Ordering InformationFor product ordering, please refer to: ESP Product Selector.Disclaimer and Copyright NoticeInformation in this document, including URL references, is subject to change without notice.THIS DOCUMENT IS PROVIDED AS IS WITH NO WARRANTIES WHATSOEVER,INCLUDING ANY WARRANTY OF MERCHANTABILITY , NON-INFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE.All liability, including liability for infringement of any proprietary rights, relating to use of information in this document is disclaimed. No licenses express or implied, by estoppel or otherwise, to any intellectual property rights are granted herein.The Wi-Fi Alliance Member logo is a trademark of the Wi-Fi Alliance. The Bluetooth logo is a registered trademark of Bluetooth SIG.All trade names, trademarks and registered trademarks mentioned in this document are property of their respective owners, and are hereby acknowledged. Copyright © 2022 Espressif Inc. All rights reserved.Espressif IoT Team。

GD32 MCU Tools Introduction (Apr 2014)

8

GD32F150R-EVAL 超值系列评估板

基于GD32F150R8T6的USB超值型评估板,所有的 I/O端口和外设都已引出,可完整全面的评估GD32 系列超值型产品的性能与集成外设,包括: SWD、 RTC、I2C、USART、I2S、SPI、ADC、DAC、 USB 2.0 FS、HDMI-CEC、CMP、TSI。 GD32F150R8T6评估板外扩展2.2” TFT LCD显示屏 (可选),并配备滑动条以评估触摸感测接口(TSI) 可通过第三方仿真器在此板上调试软件,支持2线 SWD接口,并支持串口ISP下载程序。 通过USB供电。

产品型号 GD32150R-EVAL GD32150R-EVAL/1 (不含LCD)

参考售价 RMB 170 RMB 125

9

GD32103B-START 入门级评估板

基于GD32F103VBT6的入门级评估板,所有管脚 均 已引出。板上提供了常用接口,包括:JTAG、 BOOT、LED、Button Key、USB Device。

参考售价 RMB 295 RMB 220

产品型号 GD32103B-EVAL GD32103B-EVAL/1 (不含LCD)

GD32103C-EVAL评估板

基于GD32F103VCT6的增强型评估板,所有的I/O端 口和外设都已引出,可完整全面的评估GD32系列 MCU产品性能与集成外设,包括:JTAG、BOOT、 RTC、CAN、I2C、I2S、USART、SDIO、EXMC、 SPI、ADC、DAC、USB 2.0 FS。 GD32F103VCT6评估板外扩NAND和3.2” TFT LCD触 摸屏(可选),可体验和评估GD32系列MCU的外部总线 扩展(EXMC)功能。 可通过第三方仿真器在此板上调试软件,支持2线 SWD及标准JTAG下载接口,并支持串口ISP下载程序。 通过USB或AC-DC供电。

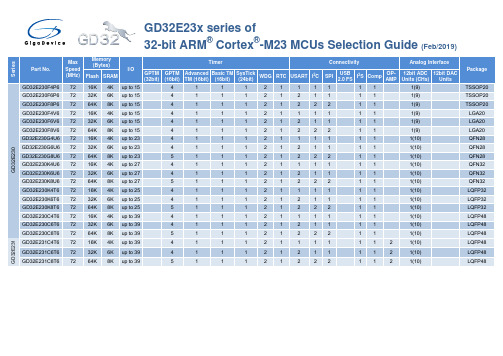

GD32_Series_of_MCUs_Selection_Guide_(Feb_2019)

GPTM (32bit)

16K 4K up to 15

Timer

GPTM (16bit)

Advanced TM (16bit)

Basic TM (16bit)

SysTick (24bit)

WDG

RTC

USART

I2C

4

1

1

1

21

1

1

Connectivity

SPI

USB 2.0 FS

I2S

Comp

OPAMP

1

11

Analog Interface

12bit ADC 12bit DAC Units (CHs) Units

1(9)

GD32E230F6P6 72 32K 6K up to 15

4

1

1

1

21

2

11

11

1(9)

GD32E230F8P6 72 64K 8K up to 15

4

1

1

1

21

2

22

11

1(9)

5

23 1

1

21

3(16)

2

GD32F303RET6 120 512K 64K up to 51 4

2

2

1

21

5

23 1

1

21

3(16)

2

GD32F303RGT6 120 1024K 96K up to 51 10

2

2

1

21

5

23 1

1

21

3(16)

2

GD32F303RIT6 120 2048K 96K up to 51 10

RISC-V处理器安全技术研究

RISC-V 处理器安全技术研究摘要:RISC-V(第五代精简指令集)安全处理器在现有的指令集架构的基础上增加了一个基于核心RISC-V技术构建的安全附加组,安全技术同架构一起开始设计,相比ARM和Intel等主流处理器架构有着得天独厚的技术优势,本文将从指令扩展、安全域、权限层级等多个方面研究RISC-V处理器安全技术。

关键词-RISC-V、安全技术1.引言国产处理器虽能够做到自主可控,但同Intel和ARM一样,其指令代码都是不公开的,其安全性、可靠性存在未知风险。

本文基于新一代开源RISC-V指令集架构,研究安全处理器内核、片上安全总线架构、TEE(Trusted execution environment)可信执行环境等内容。

虽然使用RISC-V指令集并不能保证没有任何安全漏洞和风险,但工程师可以通过深入探究分析内部细节,主动快速防御风险,而不是盲目被动升级。

在硅以外的任何层次建立现代计算的信任基础都极具挑战性,如果基本信任构建模块没有集成到处理器核心内,则无法建立可信计算,这导致了处理器架构的能力发生重大且必然的转变。

RISC-V在核心指令集架构(Instruction Set Architecture,ISA)和特权模型的定义中引入了信任的基本构建块,通过将设计中的安全性集成到核心规范中,RISC-V能够构建符合经济高效、实用且具有时间弹性的可信计算技术。

如图 1所示为RISC-V安全处理器基本架构。

图1RISC-V安全处理器基本架构2 RISC-V的安全技术为了构建安全技术,底层芯片的处理器内核需做到三个核心安全设计理念:1.安全存储重要信息;2.保证可执行代码的真实性;3.为可信应用程序的执行提供安全的环境。

存储重要信息不仅是防篡改芯片的基本功能,也是现代处理器设计的要求。

虽然物理安全对于可信计算的目标必不可少,但是防篡改芯片中模块的逻辑设计也是至关重要,它要求必须安全地处理重要信息,并防止计算机设备上可变或不可靠的攻击来访问或篡改重要信息。

STM32核心板使用说明书(Ver0.1)

51 PC10

52 PC11

53 PC12

LCD_RS LCD_RW LCD_E KEY1 KEY2

LCD 接口 LCD 接口 LCD 接口

按键

按键

8

Pins Pin Name 2 PC13-ANTI_TAMP 3 PC14-OSC32_IN 4 PC15-OSC32_OUT

5 OSC_IN/PD0

Comment 3V

104

20p 15p 22uF/6.3V 10uF/10V 100uF/10V 100uF/6.3V 绿 LED 1N4148 红 LED 2.6A 启动模式跳线 Header 13X2 D Connector 9 1602 液晶 JTAG 直流 5V 输入 0 20K 10Kx4 10K 1K 1M 100K 100 SW-SPST MAX3232CSE STM32F101RBT6 LM1117MPX-3.3 8M 32768

LCD_DB2

30 PB11/I2C2_SDA /USART3_RX

LCD_DB3

33 PB12/SPI2_NSS/I2C2_SMBAl/USART3_ LCD_DB4

CK/ TIM1_BKIN

34 PB13/SPI2_SCK/USART3_CTS/TIM1_C LCD_DB5

H1N

35 PB14/SPI2_MISO/USART3_RTS/TIM1_ LCD_DB6

第 2 章 功能说明 ............................................................. 7 2.1 电路原理图 ............................................................. 7 2.2 CPU PIN 分配(适应 STM32F103RBT6 或 STM32F103R8T6) ......................... 7 2.3 PCB 板图................................................................ 9 2.4 跳线设置 .............................................................. 10 2.5 输出口 P1,P2 PIN 定义 ................................................... 11

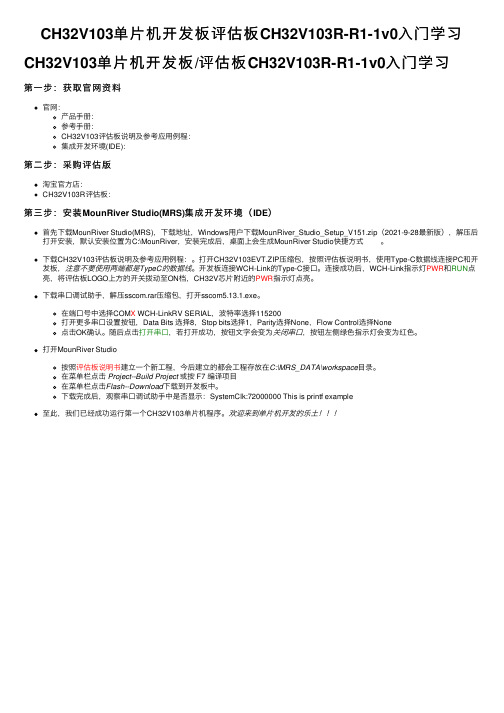

CH32V103单片机开发板评估板CH32V103R-R1-1v0入门学习

CH32V103单⽚机开发板评估板CH32V103R-R1-1v0⼊门学习CH32V103单⽚机开发板/评估板CH32V103R-R1-1v0⼊门学习第⼀步:获取官⽹资料官⽹:产品⼿册:参考⼿册:CH32V103评估板说明及参考应⽤例程:集成开发环境(IDE):第⼆步:采购评估版淘宝官⽅店:CH32V103R评估板:第三步:安装MounRiver Studio(MRS)集成开发环境(IDE)⾸先下载MounRiver Studio(MRS),下载地址,Windows⽤户下载MounRiver_Studio_Setup_V151.zip(2021-9-28最新版),解压后打开安装,默认安装位置为C:\MounRiver,安装完成后,桌⾯上会⽣成MounRiver Studio快捷⽅式。

下载CH32V103评估板说明及参考应⽤例程:。

打开CH32V103EVT.ZIP压缩包,按照评估板说明书,使⽤Type-C数据线连接PC和开发板,注意不要使⽤两端都是TypeC的数据线。

开发板连接WCH-Link的Type-C接⼝。

连接成功后,WCH-Link指⽰灯PWR和RUN点亮,将评估板LOGO上⽅的开关拨动⾄ON档,CH32V芯⽚附近的PWR指⽰灯点亮。

下载串⼝调试助⼿,解压sscom.rar压缩包,打开sscom5.13.1.exe。

在端⼝号中选择COM X WCH-LinkRV SERIAL,波特率选择115200打开更多串⼝设置按钮,Data Bits 选择8,Stop bits选择1,Parity选择None,Flow Control选择None点击OK确认。

随后点击打开串⼝,若打开成功,按钮⽂字会变为关闭串⼝,按钮左侧绿⾊指⽰灯会变为红⾊。

打开MounRiver Studio按照评估板说明书建⽴⼀个新⼯程,今后建⽴的都会⼯程存放在C:\MRS_DATA\workspace⽬录。

在菜单栏点击Project--Build Project或按 F7 编译项⽬在菜单栏点击Flash--Download下载到开发板中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

GigaDevice Semiconductor Inc.GD32VF103R-START评估板用户指南V1.1目录目录 (1)图 (3)表 (4)1.简介 (5)2.功能引脚分配 (5)3.入门指南 (5)4.硬件设计概述 (6)4.1.供电电源 (6)4.2.启动方式选择 (6)4.3.LED指示灯 (6)4.4.按键 (7)BFS (7)4.6.GD-Link (8)4.7.扩展电路 (8)4.8.MCU (9)4.9.Ardunio (9)5.例程使用指南 (10)5.1.GPIO流水灯 (10)5.1.1.DEMO目的 (10)5.1.2.DEMO执行结果 (10)5.2.GPIO按键轮询模式 (10)5.2.1.DEMO目的 (10)5.2.2.DEMO执行结果 (10)5.3.EXTI按键中断模式 (10)5.3.1.DEMO目的 (10)5.3.2.DEMO执行结果 (11)5.4.TIMER和按键触发外部中断 (11)5.4.1.DEMO目的 (11)5.4.2.DEMO执行结果 (11)BFS设备 (11)5.5.1.虚拟串口设备 (11)5.5.2.U盘设备 (12)BFS主机 (13)5.6.1.U盘主机 (13)6.版本历史 (14)图4-1 供电电源原理图 (6)图4-2 启动方式选择原理图 (6)图4-3 LED功能原理图 (6)图4-4 按键功能原理图 (7)图4-5 USBFS原理图 (7)图4-6 GD-Link原理图 (8)图4-7 扩展电路功能原理图 (8)图4-8 MCU原理图 (9)图4-9 Ardunio原理图 (9)表2-1 引脚分配 (5)表6-1 版本历史 (14)1. 简介GD32VF103R-START评估板使用GD32VF103RBT6作为主控制器。

评估板使用MiniUSB接口提供5V电源。

提供包括扩展引脚在内的及Reset, Boot, User key, LED, GD-Link, Ardunio等外设资源。

2. 功能引脚分配表2-1 引脚分配3. 入门指南评估板使用Mini USB提供5V电源。

下载程序到评估板需要使用GD-Link工具,在选择了正确的启动方式并且上电后,LEDPWR将被点亮,表明评估板供电正常。

所有例程都是基于eclipse 4.7.2创建的。

在进行调试下载前注意配置“Debug Configurations”。

4. 硬件设计概述 4.1.供电电源图 4-1 供电电源原理图4.2. 启动方式选择图 4-2 启动方式选择原理图4.3. LED 指示灯图 4-3 LED 功能原理图4.4. 按键图4-4 按键功能原理图4.5. USBFS图4-5 USBFS原理图4.6. GD-Link图 4-6 GD-Link 原理图4.7. 扩展电路图 4-7 扩展电路功能原理图4.8. MCU图 4-8 MCU 原理图4.9. Ardunio图 4-9 Ardunio 原理图5. 例程使用指南5.1. GPIO流水灯5.1.1. DEMO目的这个例程包括了GD32 MCU的以下功能:⏹学习使用GPIO控制LED⏹学习使用SysTick产生1ms 的延时GD32VF103R-START开发板上有4个LED。

LED1, LED2, LED3和LED4通过GPIO控制着。

这个例程将讲述怎么点亮LED。

5.1.2. DEMO执行结果下载程序< 01_GPIO_Running_LED >到开发板上,LED1, LED2, LED3和LED4将顺序每间隔1秒点亮然后熄灭,一直重复这个过程。

5.2. GPIO按键轮询模式5.2.1. DEMO目的这个例程包括了GD32 MCU的以下功能:⏹学习使用GPIO控制LED和按键⏹学习使用SysTick产生1ms 的延时GD32VF103R-START开发板有两个按键和四个LED。

其中,两个按键是Reset按键和User按键;LED1, LED2, LED3和LED4可通过GPIO控制。

这个例程讲述如何使用User按键控制LED1。

当按下User按键,将检测IO 端口的输入值,如果输入为高电平,将等待延时50ms。

之后,再次检测IO 端口的输入状态。

如果输入仍然为高电平,表明按键成功按下,翻转LED1的输出状态。

5.2.2. DEMO执行结果下载程序< 02_GPIO_Key_Polling_mode >到开发板上,首先,所有的灯会亮灭一次用于测试,按下User按键,LED1将会点亮,再次按下User按键,LED1将会熄灭。

5.3. EXTI按键中断模式5.3.1. DEMO目的这个例程包括了GD32 MCU的以下功能:⏹学习使用GPIO控制LED和按键⏹学习使用EXTI 产生外部中断GD32VF103R-START开发板有两个按键和四个LED。

其中,两个按键是Reset按键和User按键;LED1, LED2, LED3和LED4可通过GPIO控制。

这个例程讲述如何使用EXTI外部中断线控制LED1。

当按下User按键,将产生一个外部中断,在中断服务函数中,应用程序翻转LED1的输出状态。

5.3.2. DEMO执行结果下载程序< 03_EXTI_Key_Interrupt_mode >到开发板,首先,所有的灯会亮灭一次用于测试,然后点亮LED1,按下User按键,LED1将会点亮,再次按下User按键,LED1将会熄灭。

5.4. TIMER和按键触发外部中断5.4.1. DEMO目的这个例程包括了GD32 MCU的以下功能:⏹学习使用GPIO控制LED和按键⏹学习使用EXTI 产生外部中断⏹学习使用TIMER产生PWMGD32VF103R-START开发板有两个按键和四个LED。

其中,两个按键是Reset按键和User按键;LED1, LED2, LED3和LED4可通过GPIO控制。

这个例程讲述如何使用TIMER生成PWM产生外部中断然后在中断服务程序中翻转LED2的输出状态,以及如何使用EXTI外部中断线控制LED1。

当按下User按键,将产生一个外部中断,在中断服务函数中,应用程序翻转LED1的输出状态。

5.4.2. DEMO执行结果下载程序< 04_TIMER_Key_EXTI >到开发板,首先,LED1和LED2会闪烁一次用于测试,按下User按键,LED1将会点亮,再次按下User按键,LED1将会熄灭。

使用杜邦线连接PA6(TIMER2_CH0)和PB11,LED2的输出状态会每隔500ms翻转一下。

5.5. USBFS设备5.5.1. 虚拟串口设备DEMO目的这个例程包括了GD32 MCU的以下功能:⏹学习如何使用USBFS设备⏹学习如何实现USBFS CDC设备开发板具有一个USBFS接口。

在本例程中,开发板被USB主机枚举为一个USB虚拟串口,如下图所示,可在PC端设备管理器中看到该虚拟串口。

该例程使得USB 键盘看起来像是个串口,也可以通过USB口回传数据。

通过键盘输入某些信息,虚拟串口可以接收并显示这些信息。

DEMO执行结果将<05_USBFS\Device\CDC_ACM>例程下载到开发板中,并运行。

通过键盘输入某些数据,虚拟串口可以接收并显示这些数据。

比如通过虚拟串口的输入框输入“GigaDeviceMCU”, PC回传这些信息给虚拟串口,并得以显示。

5.5.2. U盘设备DEMO目的这个例程包括了GD32 MCU的以下功能:⏹学习如何使用USBFS⏹学习如何实现USB MSC(大容量存储)设备本DEMO主要实现了一个U盘。

U盘是现今非常普遍的可移动MSC类设备。

MSC,即Mass Storage device Class(大容量存储设备类),是一种计算机和移动设备之间的传输协议,它允许一个通用串行总线(USB)设备来访问主机的计算设备,使两者之间进行文件传输,主要包括移动硬盘、移动光驱和U盘等。

MSC类设备必须有存储介质,DEMO中使用了MCU的内部FLASH作为存储介质。

具体的MSC 类协议内容请自行查阅与参考其协议标准。

MSC类设备会使用多种传输协议与命令格式进行通信,所以在实现时需要自行选择合适的协议与命令格式。

本DEMO中选择BOT(仅批量传输)协议和所需的SCSI(小型计算机接口)命令,并和多种Window操作系统兼容。

具体的BOT协议内容与SCSI命令规格请自行查阅与参考其协议标准。

DEMO执行结果下载<05_USBFS\Device\MSC >到开发板中并运行。

当开发板连到PC后,可以在计算机的设备管理器中看到通用串行总线控制器里面多出了一个USB大容量存储设备,同时看到磁盘驱动器里面多了1个磁盘驱动器,如下所示:接着,打开资源管理器后会看到里面多了1个磁盘,如下图所示:此时,写/读/格式化操作可以像其他移动设备一样进行。

5.6. USBFS主机5.6.1. U盘主机DEMO目的这个例程包括了GD32 MCU的以下功能:⏹学习使用USBFS作为MSC主机⏹学习MSC主机和U盘之间的操作评估板包含USBFS模块,并且该模块可以被用于作为一个USB设备、一个USB主机或一个OTG设备。

本示例主要显示如何使用USBFS作为一个USB MSC主机来与外部U盘进行通信。

DEMO执行结果将OTG电缆线插入到USB接口,将< 05_USBFS\Host\MSC >工程下载到开发板中并运行。

如果一个U盘被连入,用户将会看到LED4点亮,表明U盘成功连接,并且LED2慢速闪烁,表明U盘已被成功枚举。

按下User按键将会看到LED2快速闪烁,表明主机已经识别U盘;之后再次按下User按键将会看到LED2慢速闪烁,此时表明U盘的内容已经被正确读取;然后第三次按下User按键将会向U盘写入文件;最后用户将会看到LED1和LED2同时点亮,表明MSC主机示例结束。

最后拔掉U盘,可以看到LED4熄灭。

6. 版本历史表6-1 版本历史Important NoticeThis document is the property of GigaDevice Semiconductor Inc. and its subsidiaries (the "Company"). This document, including any product of the Company described in this document (the “Product”), is owned by the Company under the intellectual property laws and treaties of the People’s Republic of China and other jurisdictions worldwide. The Company reserves all rights under such laws and treaties and does not grant any license under its patents, copyrights, trademarks, or other intellectual property rights. The names and brands of third party referred thereto (if any) are the property of their respective owner and referred to for identification purposes only.The Company makes no warranty of any kind, express or implied, with regard to this document or any Product, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. The Company does not assume any liability arising out of the application or use of any Product described in this document. Any information provided in this document is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Except for customized products which has been expressly identified in the applicable agreement, the Products are designed, developed, and/or manufactured for ordinary business, industrial, personal, and/or household applications only. The Products are not designed, intended, or authorized for use as components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, atomic energy control instruments, combustion control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or Product could cause personal injury, death, property or environmental damage ("Unintended Uses"). Customers shall take any and all actions to ensure using and selling the Products in accordance with the applicable laws and regulations. The Company is not liable, in whole or in part, and customers shall and hereby do release the Company as well as it’s suppliers and/or distributors from any claim, damage, or other liabil ity arising from or related to all Unintended Uses of the P roducts. Customers shall indemnify and hold the Company as well as it’s suppliers and/or distributors harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of the Products.Information in this document is provided solely in connection with the Products. The Company reserves the right to make changes, corrections, modifications or improvements to this document and Products and services described herein at any time, without notice.© 2019 GigaDevice – All rights reserved。