ADDA等一些芯片的verilog程序

verilog 加法

verilog 加法摘要:1.Verilog 简介2.Verilog 中的加法操作3.Verilog 中的加法实例4.Verilog 中的进位处理正文:【1.Verilog 简介】Verilog 是一种硬件描述语言,主要用于数字系统硬件的描述、模拟和验证。

它是由Phil Moorby 在1983 年发明的,最初称为"VRTL"(VHSIC 硬件描述语言)。

后来,Moorby 将其改名为Verilog,并成为了一种广泛使用的硬件描述语言。

Verilog 通常用于描述数字电路、数字信号处理、计算机体系结构等领域的硬件设计。

【2.Verilog 中的加法操作】在Verilog 中,加法操作使用"+"符号表示。

对于两个位数相同的数字,可以直接进行加法运算。

例如,对于两个4 位二进制数a 和b,可以写成:```wire [3:0] a = 4"h1010;wire [3:0] b = 4"h1101;wire [3:0] sum = a + b;```对于不同位数的数字,需要进行位扩展,使它们的位数相同,然后再进行加法运算。

例如,对于一个3 位二进制数a 和一个4 位二进制数b,可以写成:```wire [2:0] a = 3"b101;wire [3:0] b = 4"h1101;wire [5:0] sum = {a[2:0], a[1:0] + b[3:0]};```【3.Verilog 中的加法实例】下面是一个4 位二进制数的加法器的Verilog 代码实例:```module adder_4bit(input a, input b, output sum, output carry);reg [3:0] temp_sum [3:0];reg temp_carry;always @(*) begintemp_carry = a & b;temp_sum[0] = a ^ b;temp_sum[1] = a ^ b;temp_sum[2] = a ^ b;temp_sum[3] = a ^ b;endassign sum = temp_sum[3:0];assign carry = temp_carry;endmodule```【4.Verilog 中的进位处理】在Verilog 中,进位处理通常使用一个临时的进位信号(如上面代码中的temp_carry)来实现。

veriloghdl程序大全

1.简单门电路的设计二输入与非门module nand_2(y,a,b);output y;input a,b;nand(y,a,b);endmodule二输入异或门module nand_2(y,a,b);output y;input a,b;reg y;always @(a,b)begincase({a,b})2’b00:y=1;2’b01:y=1;2’b10:y=1;2’b11:y=0;default:y=’bx;endcaseendendmodule二输入三态门module eda_santai(dout,din,en); output dout;input din,en;reg dout;alwaysif (en) dout<=din;else dout<=’bz;endmodule3-8译码器的设计module yimaqi(S1,S2,S3,A,Y); input S1;wire S1;input S2;wire S2;input S3;wire S3;input [2:0]A;wire [2:0]A;output[7:0]Y;reg [7:0]Y;reg s;always@(S,S1,S2,S3)begins<=S2|S3;Y <=8'b1111_1111;else if(S)Y <=8'b1111_1111;elsecase(A)3'b000:Y<=11111110;3'b001:Y<=11111101;3'b010:Y<=11111011;3'b011:Y<=11110111;3'b100:Y<=11101111;3'b101:Y<=11011111;3'b110:Y<=10111111;3'b111:Y<=01111111;endcaseendendmodule2.8-3编码器的设计module banjiaqi(a,b,count,sum);input a;wire a;input b;wire b;output count;wire count;output sum;wire sum;assign {count,sum}=a+b;endmodule4. D触发器的设计module Dchufaqi ( Q ,CLK ,RESET ,SET ,D ,Qn ); input CLK ;wire CLK ;input RESET ;wire RESET ;input SET ;wire SET ;input D ;wire D ;output Q ;reg Q ;output Qn ;wire Qn ;assign Qn = ~Q ;always @ ( posedge CLK or negedge SET or negedge RESET ) beginif ( !RESET)Q <= 0 ;else if ( ! SET)Q <= 1;else Q <= D;endendmodule5. 1位半加法器的设计module banjiafaqi(a,b,sum,count);input a;wire a;input b;wire b;output sum;wire sum;output count;wire count;assign {count,sum}=a+b;endmodule6. 4位计数器的设计module sihisjishuqi(CLK,RESET,out);input CLK;wire CLK;input RESET;wire RESET;output[3:0] out;reg[3:0] out;always @ ( posedge CLK or negedge RESET )beginif(!RESET)out<=4'b0000;elsebeginout<=out+1;if(out==4'b1010)out<=4'b0000;endendendmodule7.分频时序逻辑电路的设计module eda_fp_even(clk_out,clk_in,rst); input clk_in;input rst;wire rst;output clk_out;reg clk_out;reg [1:0]cnt;parameter N=6;always @(posedge clk_in or negedge rst) beginif(!rst)beginclk_out<=0;cnt<=0;endelsebegincnt<=cnt+1;if(cnt==N/2-1)beginclk_out=!clk_out;cnt<=0;endendendendmodule8.7段显示译码器的设计module eda_scan_seven(clk,dig,y,rst); input clk;wire clk;input rst;wire rst;output[7:0] dig;wire[7:0] dig;output [7:0]y;wire [7:0]y;reg clkout;reg [19:0]cnt;reg [2:0]wei;reg [3:0]duan;reg [6:0]Y_r;reg [7:0]dig_r;assign y = {1'b1,(~Y_r[6:0])};assign dig =~dig_r;parameter period= 1000000;always@(posedge clk or negedge rst) beginif(!rst)cnt<=0;else begincnt<=cnt+1;if(cnt==(period>>1)-1)clkout<=#1 1'b1;else if(cnt==period-1)beginclkout<=#1 1'b0;cnt<=#1 1'b0;endendendalways@(posedge clkout or negedge rst ) beginif(!rst)wei<=0;elsewei<=wei+1;endalways @(wei) //数码管选择begincase ( wei )3'b000 :begindig_r <= 8'b0000_0001;duan <= 1;end3'b001 :begindig_r <= 8'b0000_0010;duan<= 3;end3'b010 :begindig_r <= 8'b0000_0100;duan<= 5;end3'b011 :begindig_r <= 8'b0000_1000;duan <= 7;end3'b100 :begindig_r <= 8'b0001_0000;duan<= 9;end3'b101 :begindig_r <= 8'b0010_0000;duan<= 11;end3'b110 :begindig_r <= 8'b0100_0000;duan <= 13;end3'b111 :begindig_r <= 8'b1000_0000;duan<= 15;endendcaseendalways @ ( duan ) //译码begincase ( duan )0: Y_r = 7'b0111111; // 01: Y_r = 7'b0000110; // 12: Y_r = 7'b1011011; // 23: Y_r = 7'b1001111; // 34: Y_r = 7'b1100110; // 45: Y_r = 7'b1101101; // 56: Y_r = 7'b1111101; // 67: Y_r = 7'b0100111; // 78: Y_r = 7'b1111111; // 89: Y_r = 7'b1100111; // 910: Y_r = 7'b1110111; // A11: Y_r = 7'b1111100; // b12: Y_r = 7'b0111001; // c13: Y_r = 7'b1011110; // d14: Y_r = 7'b1111001; // E15: Y_r = 7'b1110001; // Fdefault: Y_r = 7'b0000000;endcaseendendmodule9.数据选择器的设计module eda_8xuanyi (A,D0,D1,D2,D3,D4,D5,D6,D7,G,Y); input D0,D1,D2,D3,D4,D5,D6,D7,G;input [2:0]A;wire [2:0]A;output Y;reg Y;always @(A, G)beginif (G==0)Y<=0;elsecase(A)3'b000:Y=D0;3'b001:Y=D1;3'b010:Y=D2;3'b011:Y=D3;3'b100:Y=D4;3'b101:Y=D5;3'b110:Y=D6;3'b111:Y=D7;endcaseendendmodule10.数据锁存器的设计module e da_suocunqi(q,d,oen,g); output[7:0] q;//数据输出端input[7:0] d;//数据输入端input oen,g;//三态控制端reg[7:0] q;always @(*)beginif (oen)beginq<="z";endelsebeginif(g)q<=d;elseq<=q;endendendmodule11.数据寄存器的设计module eda_jicunqi(r,clk,d,y); input r,clk;input [7:0]d;wire [7:0]d;output [7:0]y;reg [7:0]y;always @ (posedge clk or negedge r) beginif(!r)y<=8'b00000000;elsey<=d;endendmodule12.顺序脉冲发生器的设计module eda_shunxu(clk,clr,q);input clk,clr;output [7:0]q;reg [7:0]q;always @ ( posedge clk or posedge clr ) beginif ( clr==1)beginq<=8'b00000000; //赋初值endelsebeginif(q==0)q<=8'b00000001;elseq<=q<<1; //给初值进行移位endendendmodule13.1位全加法器的设计module quanjiaqi(a,b,sum,count,cin); input a;wire a;input b;wire b;input cin;wire cin;output sum;wire sum;output count;wire count;assign{sum,count}=a+b+cin; endmodule15.键控Led灯的设计module eda_led(led,key);input key;output led;reg led_out;assign led<=led_out;always@(key)beginif(key)led_out<=1;else if(!key)led_out<=0;endendmodule16.双向移位寄存器的设计module eda_yiweijicunqi( left_right ,load ,clr ,clk ,DIN ,DOUT );input left_right ;wire left_right ;input load ;wire load ;input clr ;wire clr ;input clk ;wire clk ;input [3:0] DIN ;wire [3:0] DIN ;output [3:0] DOUT ;wire [3:0] DOUT ;reg [3:0] data_r;assign DOUT = data_r ;always @ (posedge clk or posedge clr or posedge load)//敏感变量,看真值表beginif(clr==1)data_r <= 0;//判断是否清零else if (load )data_r<=DIN;//判断是否装载数据//判断进行左移位还是右移位elsebeginif(left_right)data_r<=DIN<<1;elsedata_r<=DIN>>1;endendendmodule17.8-3优先编码器的设计module youxianbianma( A ,I ,GS ,EO ,EI ); input [7:0] I ;wire [7:0] I ;input EI ;wire EI ;output [2:0] A ;reg [2:0] A ;output GS ;reg GS ;output EO ;reg EO ;always @ ( I or EI )if ( EI )beginA <= 3'b111;GS <= 1;EO <= 1;endelse if (I==8'b11111111)beginA <= 3'b111;GS <= 1;EO <= 0;endelse if ( I==8'b11111110 )beginA <= 3'b111;GS <= 0;EO <= 1;endelse if ( I==8'b1111110x )beginA <= 3'b110;GS <= 0;EO <= 1;endelse if ( I==8'b111110xx )beginA <= 3'b101;GS <= 0;EO <= 1;endelse if ( I==8'b11110xxx )beginA <= 3'b100;GS <= 0;EO <= 1;endelse if ( I==8'b1110xxxx )beginA <= 3'b011;GS <= 0;EO <= 1;endelse if ( I==8'b110xxxxx )beginA <= 3'b010;GS <= 0;EO <= 1;endelse if ( I==8'b10xxxxxx )beginA <= 3'b001;GS <= 0;EO <= 1;endelse if ( I==8'b0xxxxxxx )beginA <= 3'b000;GS <= 0;EO <= 1;endendmodule18.数据分配器的设计module shujufenpeiqi(y0,y1,y2,y3,din,a); output y0,y1,y2,y3;//4??êy?Yí¨μàinput din;//êy?Yê?è?input [1:0] a;reg y0,y1,y2,y3;always @(din,a)beginy0=0;y1=0;y2=0;y3=0; //3?ê??ˉ£á?case(a)00:y0=din;01:y1=din;02:y2=din;03:y3=din;endcase end endmodule。

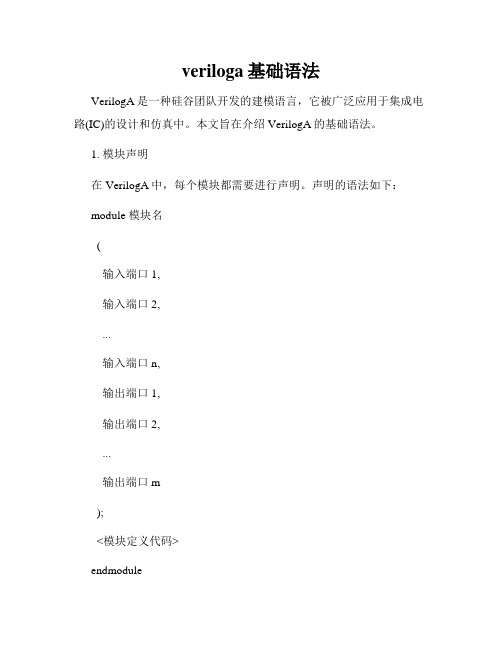

veriloga基础语法

veriloga基础语法VerilogA是一种硅谷团队开发的建模语言,它被广泛应用于集成电路(IC)的设计和仿真中。

本文旨在介绍VerilogA的基础语法。

1. 模块声明在VerilogA中,每个模块都需要进行声明。

声明的语法如下:module 模块名(输入端口1,输入端口2,...输入端口n,输出端口1,输出端口2,...输出端口m);<模块定义代码>endmodule其中,模块名可以由字母、数字和下划线组成,不能以数字开头;输入端口和输出端口可以是标量或向量。

2. 参数声明VerilogA允许在模块中声明参数,以便在实例化时进行配置。

语法如下:parameter 参数名 = 值;参数可以通过assign语句进行连接,也可以在实例化时进行配置。

3. 变量声明在VerilogA中,可以使用不同的变量类型进行声明,如实数、整数、布尔值等。

real: 实数类型,用于存储实数值。

integer: 整数类型,用于存储整数值。

boolean: 布尔类型,用于存储真/假值。

语法如下:real 变量名;integer 变量名;boolean 变量名;4. 函数和任务在VerilogA中,可以使用函数和任务来实现特定的功能。

函数是一段可重用的代码,它接收输入参数并返回一个值。

函数的语法如下:function 返回类型函数名(输入参数);<函数定义代码>return 返回值;endfunction任务是一段可重用的代码,不返回值,但可以通过参数进行输入和输出。

任务的语法如下:task 任务名(输入参数);<任务定义代码>endtask5. 运算符VerilogA支持各种常见的数学和逻辑运算符,如加减乘除、取余、与或非等。

加法运算符:+减法运算符:-乘法运算符:*除法运算符:/取余运算符:%与运算符:&&或运算符:||非运算符:!6. 控制结构在VerilogA中,可以使用if-else、for、while等控制结构来实现条件判断和循环。

verilog三位加法器代码

verilog三位加法器代码

下面是一个使用Verilog语言编写的三位加法器的代码示例: verilog.

module three_bit_adder(。

input wire a,。

input wire b,。

input wire cin,。

output wire sum,。

output wire cout.

);

assign sum = a ^ b ^ cin;

assign cout = (a & b) | (cin & (a ^ b));

endmodule.

在这个代码中,`three_bit_adder`模块定义了一个三位加法器。

它有三个输入信号 `a`、`b`和`cin`,分别代表两个加数和进位输入。

还有两个输出信号 `sum`和`cout`,分别代表和的结果和进位

输出。

在模块内部,使用`assign`语句对`sum`和`cout`进行赋值。

`sum`的值通过异或门(`^`)计算得出,即三个输入信号的异或结果。

`cout`的值通过与门(`&`)和或门(`|`)的组合计算得出,

具体逻辑为,如果两个输入信号 `a` 和 `b` 同时为1,或者进位

输入信号 `cin` 为1 且 `a` 与 `b` 不相等,则进位输出 `cout` 为1,否则为0。

这个Verilog代码实现了一个简单的三位加法器,可以用于对

三位二进制数进行加法运算。

用verilog-a写的一些电路模块的例子

用verilog-a写的一些电路模块的例子以下是几个用Verilog-A 语言编写的电路模块的例子:1. 增益电路模块````include "disciplines.vams"module gain_circuit(va, vb, vout, g);input va, vb;output vout;parameter real g=10.0;analog beginvout = g * (va - vb);endendmodule```这个例子展示了一个简单的增益电路模块,其中输入是两个电压va、vb,输出是vout,增益系数为g。

在模块中使用了Verilog-A 的`analog begin` 语句来定义电路的行为。

2. RC 低通滤波器模块````include "disciplines.vams"module rc_lowpass_filter(vin, vout, r, c);input vin;output vout;parameter real r=1.0, c=1e-6;real v1;analog begini(vin, v1) <+ (vin - v1)/(r*c);vout <+ v1;endendmodule```这个例子展示了一个基于RC 电路的低通滤波器模块,其中输入为vin,输出为vout,RC 电路的参数由r 和c 决定。

在模块中使用了Verilog-A 的`i()` 语句来定义电路的行为。

3. 三角波发生器模块````include "disciplines.vams"module triangle_wave_generator(vout, freq, amp, dc);output vout;parameter real freq=1e3, amp=1.0, dc=0.0;real t;analog begint = $abstime;vout <+ amp * (2 * (t * freq - floor(t * freq + 0.5)) - 1) + dc;endendmodule```这个例子展示了一个简单的三角波发生器模块,其中输出为vout,频率由freq 决定,幅值由amp 决定,直流分量由dc 决定。

verilog代码综合成电路

verilog代码综合成电路

标题: Verilog代码综合成电路

Verilog硬件描述语言(HDL)广泛应用于数字电路的设计和验证。

它采用硬件描述语言的文本形式来描述数字电路的行为和结构。

Verilog代码可以使用EDA工具(电子设计自动化工具)进行综合,最终生成门级模拟网表或实际的电路布局。

综合过程通常包括以下几个主要步骤:

1. 代码分析和解析

首先,EDA工具会读取Verilog源代码,对其进行语法和语义分析。

如果代码存在错误,工具会给出相应的错误信息和警告。

2. 优化和技术映射

在这个步骤中,工具会优化代码,并将其映射到目标技术库中的基本逻辑门、触发器等元件。

优化包括如逻辑简化、时序优化等。

3. 网表生成

优化后的逻辑门级描述被转换成硬件描述的数据结构,即网表(Netlist)。

网表包含了设计中每个逻辑元件、互连线路的详细信息。

4. 后续处理

网表可用于门级仿真、功耗估算、布局布线等后续工作。

一些EDA工具还会生成与FPGA或定制芯片相关的配置文件。

Verilog代码综合为我们提供了从高层次抽象硬件描述到实际电路实现的桥梁。

对于复杂的数字系统,HDL和EDA工具使得设计过程自动化、高效和可管理。

南理工电类综合实验报告FM调制解调的数字实现

《电类综合实验》仿真报告实验课题:FM调制解调的数字实现指导教师:刘光祖学生姓名:院系:电光学院专业:通信与信息系统实验时间:2016.05.09至2016.05.13一、实验背景1.FPGA简介FPGA(Field-Programmable Gate Array,现场可编程逻辑门阵列)是在PAL、GAL、CPLD等可编程逻辑器件的基础上进一步发展的产物,是专用集成电路领域一种半定制的集成数字芯片,其最大特点是现场可编程,既解决了全定制电路的不足,又克服了原有可编程逻辑器件门电路数有限的缺点。

FPGA的内部结构由CLB、RAM、DCM、IOB、Interconnect 等构成。

如下给出了FPGA的最典型的结构:FPGA开发的一般流程:1(a) 1(b)2.DE2-115开发板简介本实验中所用开发板为Altera公司的DE2-115。

如下为开发板的配置列表:•Altera Cyclone® IV 4CE115 FPGA 器件•Altera 串行配置芯片:EPCS64•USB Blaster 在线编程;也支持JTAG和AS可编程方式•2MB SRAM•两片64MB SDRAM•8MB Flash memory•SD卡插槽•4个按钮•18个滑动开关•18个红色LED•9个绿色LED•50M时钟源•24位音频编解码器,麦克风插孔•电视解码•RJ45 2G以太网接口•VGA连接器•含有USB_A和USB_B连接器的主从控制器•RS232收发器和9针连接器•PS/2鼠标和键盘连接器•红外接收器ControlPanel是开发板自带的一个工具软件,可以通过该软件提供的图形界面直接对FPGA上的各个外设进行操作。

通过该操作可以确认PC机与开发板的连接是否正确,开发板的硬件工作是否正常。

ControlPanel的安装过程如下:确保QUARTUS II 10.0 或以上版本能被成功安装;将开关RUN/PROG切换到RUN位置;将USB接线连接至USB驱动端口,供12V电源并打开开关;打开主机上的可执行文件DE2_115_ControlPanel.exe,controlPanel的用户界面如下:DE2_115_ControlPanel.exe一旦被启动,DE2_115_ControlPanel.sof程序流文件将会被自动加载;如果未连接,点击CONNECT,点sof文件将会重新加载到板子上;注意,控制面板将会占用一直到你关闭那个端口,除非你关闭USB端口,否则你不能使用QUARTUS II 来下载文件;控制面板现在可以使用了,通过设置一些LED灯ON/OFF的状态来观察DE2-115上的状态。

verilog 加法器累加位宽处理

Verilog 加法器累加位宽处理一、概述在数字电路设计中,加法器是必不可少的基本模块之一。

在Verilog中实现加法器,需要考虑到输入输出数据的位宽处理。

本文将从加法器的基本原理、Verilog实现方式以及位宽处理等方面进行探讨。

二、加法器的基本原理加法器是实现两个数字相加的电路模块,它通常由若干个全加器组成。

全加器能够实现三个输入的加法运算,包括两个加数和上一级的进位。

通过级联多个全加器,可以实现任意位数的加法运算。

加法器的位宽处理是非常重要的。

三、Verilog实现加法器在Verilog中,可以通过结构化、行为级或数据流级的描述方式实现加法器。

下面以行为级描述为例,说明Verilog中加法器的实现方式。

```verilogmodule adder(input [N-1:0] A,input [N-1:0] B,output [N-1:0] Sum);// 使用assign语句实现加法器assign Sum = A + B;endmodule```上述代码定义了一个名为adder的模块,包括两个输入端A和B,一个输出端Sum。

在模块内部通过assign语句实现加法运算,将A和B相加得到Sum。

四、位宽处理在Verilog中实现加法器时,需要考虑到输入输出数据的位宽处理。

如何处理不同位宽的数据是一个需要仔细考虑的问题。

1. 不同位宽数据的相加当两个输入数据的位宽不需要进行位宽转换,将宽度较小的数据进行扩展或者截断。

一般来说,较窄的数据需要进行扩展,以保证加法运算的精度。

2. 输出数据位宽加法器的输出数据位宽应当与输入数据的最大位宽一致,以保证结果的准确性。

若结果超出了输出位宽,则需要进行截断。

3. 考虑溢出在加法运算中,可能会出现溢出现象。

为了尽可能减小溢出的发生概率,可以在加法器的输入端增加溢出检测逻辑,并根据实际情况对溢出进行处理。

五、总结在Verilog中实现加法器,需要考虑到输入输出数据的位宽处理。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

/*AD0809 module v1.0work up to 5Msample = 25us 40khzfor normalclk = 2.5Msample = 30us 33khz*/module ad0809(clkin,adclk,eoc,st,ale,datain,oe,dataout);input clkin;input eoc;input [7:0]datain;output st;output ale;output oe;output adclk;output [7:0]dataout;reg adclk;reg [7:0]dataout;reg st;reg oe;reg ale;//frequence divider for ADparameter Div_adclk = 8'd9;//(9+1)*2=20 adclk=2.5M parameter Div_clk_state = 4'd4;//(4+1)*2=10 clk_state=5Mreg [8:0]div_cnt_ad;//frequence div cntreg [3:0]div_cnt_state;reg clk_state;always@(negedge clkin)beginif(div_cnt_ad != Div_adclk)div_cnt_ad <= div_cnt_ad + 1'b1;else begindiv_cnt_ad <= 0;adclk <= ~adclk;endif(div_cnt_state != Div_clk_state)div_cnt_state <= div_cnt_state + 1'b1;else begindiv_cnt_state <= 0;clk_state <= ~clk_state;endend/*AD convert*/reg [3:0]state;reg [7:0]delay;initial beginstate <= 4'd0;endalways@(negedge clk_state)begincase(state)4'd0:begin //clear allst <= 1'b0;oe <= 1'b0;ale <= 1'b0;delay <= 8'h00;state <= 4'd1;end4'd1:begin //ale latchale <= 1'b1;state <= 4'd2;end4'd2:begin //st rasingst <= 1'b1;state <= 4'd3;end4'd3:begin //ale fallingale <= 1'b0;state <= 4'd4;end4'd4:begin //st fallingst <= 1'b0;state <= 4'd5;end4'd5:begin//eoc delay after st; 8clock+2us = 26stata_clk delay <= delay + 1'b1;if(delay == 8'd26)state <= 4'd6;elsestate <= 4'd5;end4'd6:begin //test eoc(convete finished);if(eoc)state <= 4'd7;elsestate <= 4'd6;end4'd7:begin //out enableoe <= 1'b1;state <= 4'd8;end4'd8:begin //take datadataout <= datain;state <= 4'd9;end4'd9:begin //out unable; returnoe <= 1'b0;state <= 4'd0;enddefault:state <= 4'd0;endcaseendendmodule/*clk = 5Mhz T = 0.2usthe distance = 0.2 * 1000_000 * data *340m/s*/module chao (clk, start ,reset, trig, echo,data,success,time_out);input clk,start,reset,echo;output trig,data,success,time_out;reg trig,time_out,success;reg [31:0]data;reg [3:0]state;parameter Prepare = 4'd1;parameter Delay_trig = 4'd2;parameter Echo_raising = 4'd3;parameter Echo_falling = 4'd4;parameter Time_out = 4'd5;parameter Success = 4'd6;reg [7:0]dely; //60*0.2=12usreg [31:0]timer; //if timer is bigger than 0x1e848 (far than 4.0 m),time outalways@(negedge clk or negedge reset)beginif(!reset)beginstate <= Prepare;endelse begincase(state)Prepare:begintimer <= 32'h0000_0000;trig <= 1'b0;//success <= 1'b0;//time_out <= 1'b0;if(!start)begintrig <= 1'b1;//trig the devicedely <= 8'b0000_0000;state <= Delay_trig;endelse begin state <= Prepare; endendDelay_trig:begin //delay 12usdely <= dely + 1'b1;if(dely != 8'd60)begin //60state <= Delay_trig;endelse begintrig <= 1'b0; //end of trigstate <= Echo_raising;endendEcho_raising:begin //wait for echo rassingtimer <= timer + 1'b1;if(echo)begin timer <= 32'd0;state <= Echo_falling; endelse begin state <= Echo_raising; end/* if(timer >= 32'd2250)begin//>450ustimer <= 32'd0;state <= Prepare;endelse beginif(echo)begin timer <= 32'd0;state <= Echo_falling; endelse begin state <= Echo_raising; endend*/endEcho_falling:begin //wait for echo falling or timeout timer <= timer + 32'b1;if(timer >= 32'd120000)begin //out of 10mstate = Time_out;endelse beginif(!echo)begindata <= timer;state <= Success;endelse beginstate <= Echo_falling;endendendTime_out:begintime_out <= ~time_out;state <= Prepare;endSuccess:beginsuccess <= ~success;state <= Prepare;enddefault:beginstate <= Prepare;endendcaseend//end of ifendendmodule/*clk = 5Mhz T = 0.2usthe distance = 0.2 * 1000_000 * data *340m/s*/module chao (clk, start ,reset, trig, echo,data,success,time_out);input clk,start,reset,echo;output trig,data,success,time_out;reg trig,time_out,success;reg [31:0]data;reg [3:0]state;parameter Prepare = 4'd1;parameter Delay_trig = 4'd2;parameter Echo_raising = 4'd3;parameter Echo_falling = 4'd4;parameter Time_out = 4'd5;parameter Success = 4'd6;reg [7:0]dely; //60*0.2=12usreg [31:0]timer; //if timer is bigger than 0x1e848 (far than 4.0 m),time outalways@(negedge clk or negedge reset)beginif(!reset)beginstate <= Prepare;endelse begincase(state)Prepare:begintimer <= 32'h0000_0000;trig <= 1'b0;//success <= 1'b0;//time_out <= 1'b0;if(!start)begintrig <= 1'b1;//trig the devicedely <= 8'b0000_0000;state <= Delay_trig;endelse begin state <= Prepare; endendDelay_trig:begin //delay 12usdely <= dely + 1'b1;if(dely != 8'd60)begin //60state <= Delay_trig;endelse begintrig <= 1'b0; //end of trigstate <= Echo_raising;endendEcho_raising:begin //wait for echo rassingtimer <= timer + 1'b1;if(echo)begin timer <= 32'd0;state <= Echo_falling; endelse begin state <= Echo_raising; end/* if(timer >= 32'd2250)begin//>450ustimer <= 32'd0;state <= Prepare;endelse beginif(echo)begin timer <= 32'd0;state <= Echo_falling; endelse begin state <= Echo_raising; endend*/endEcho_falling:begin //wait for echo falling or timeout timer <= timer + 32'b1;if(timer >= 32'd120000)begin //out of 10mstate = Time_out;endelse beginif(!echo)begindata <= timer;state <= Success;endelse beginstate <= Echo_falling;endendendTime_out:begintime_out <= ~time_out;state <= Prepare;endSuccess:beginsuccess <= ~success;state <= Prepare;enddefault:beginstate <= Prepare;endendcaseend//end of ifendendmodule/*max358 modlulev1.0sclk = 25Mconvert = 0.588M2010/8/10*/module max538 (clk,databus,din,sclk,cs);/*direction*/input clk;output din;output sclk;output cs;input [15:0]databus;/*attribute*/reg din;reg sclk;reg cs;/*inner*/reg [15:0]datatemp;reg [7:0]state;reg [3:0]cnt16;reg [3:0]delay;/*state define*/ parameter Prepare = 8'd1; parameter Cs_0 = 8'd2; parameter Cs_1 = 8'd4; parameter Sclk_1 = 8'd8; parameter Sclk_0 = 8'd16; parameter Delay = 8'd32;always@(negedge clk)begin case(state)Prepare:begin//clearcs <= 1'b1;sclk <= 1'b0;cnt16 <= 4'b0000;delay <= 4'b0000;datatemp <= databus;state <= Cs_0;endcs <= 1'b0;//select the chipdin <= datatemp[15];//offer data firststate <= Sclk_1;endSclk_1:beginsclk <= 1'b1; //raising take the datadatatemp <= datatemp << 1; //shift leftstate <= Sclk_0;endSclk_0:beginsclk <= 1'b0; //fallingdin <= datatemp[15];//offer datacnt16 <= cnt16 + 4'b0001;if(cnt16[3] & cnt16[2] & cnt16[1] & cnt16[0])begin//16 state <= Delay;endelse state <= Sclk_1;endDelay:begindelay <= delay + 4'b0001;cs <= 1;if(delay[3])state <= Prepare;else state <= Delay;enddefault:state <= Prepare;endcaseendendmodulea/*adclk = 0.333Msample = 20K2011/8/9*/module tlc1549 (reset,clk50M,adclk,adcs,addata,databus);/*direction define*/input reset;input clk50M;input addata;output adclk;output adcs;output databus;/*attribute*/reg adclk;reg adcs;reg [15:0]databus;//输出数据//inner registerreg [15:0]datatmp;//暂存数据reg [3:0]cnt;//计数器统计十位reg [9:0]state;//状态热码reg [3:0]delay;//conveter delay counter parameter Adcs_1 = 10'd1;parameter Adcs_0 = 10'd2;parameter Clear = 10'd4;parameter Convert_1= 10'd8;parameter Convert_0= 10'd16;parameter Finish = 10'd32;parameter Reset = 10'd64;parameter Delay = 10'd128;parameter Waitdata = 10'd256;parameter Div = 8'd24;//div = (24+1)*2=50 fre = 50M/50 = 1M;adclk = 0.333M reg [7:0]div_cnt;//frequence div cntreg clkbuf;wire clkin;//frequence dividealways@(negedge clk50M)beginif(div_cnt != Div)div_cnt <= div_cnt + 1;elsediv_cnt <= 0;endalways@(negedge clk50M)beginif(div_cnt == 0)clkbuf <= ~clkbuf;endassign clkin = clkbuf;//ad convertalways@(negedge clkin)begincase(state)Adcs_1://stop I/O clockbeginadcs <= 1;state <= Adcs_0;endAdcs_0://enable contrlbeginadcs <= 0;state <= Clear;endClear://clear the temp databegindatatmp <= 16'h0000;cnt <= 0;delay <= 0;adclk <= 1'b1;state <= Convert_0;endConvert_0:beginadclk <= 1'b0;//falling edgedatatmp <= datatmp<<1;state <= Waitdata;endWaitdata:beginif(addata)datatmp[0] <= 1;//this is inportantstate <= Convert_1;endConvert_1:beginif(!reset) state <= Reset;else begincnt <= cnt + 1'b1;if(cnt[3] & cnt[0])begindatabus <= datatmp&16'h3fff;//take the dataadclk <= 1'b1;//rasing edgestate <= Finish;endelse beginadclk <= 1'b1;//rasing edgestate <= Convert_0;endendendFinish:beginadcs <= 1;state <= Delay;endDelay:begindelay <= delay + 1;if(delay[3] & delay[2])//1100state <= Reset;elsestate <= Delay;endReset:beginstate <= Adcs_1;enddefault:state <= Reset;endcaseendendmodule//clk为16倍波特频率。