图像缩放算法的研究与FPGA设计

基于FPGA的实时图像畸变校正系统研究

基于FPGA的实时图像畸变校正系统研究基于FPGA的实时图像畸变校正系统研究摘要:随着图像处理技术的飞速发展,图像畸变校正技术在计算机视觉和机器视觉领域中得到广泛应用。

本文以基于FPGA的实时图像畸变校正系统为研究对象,详细阐述了图像畸变的原因与分类,并提出了一种基于FPGA的实时图像畸变校正算法及其应用。

本文通过设计和搭建相应的硬件平台,实现了图像畸变校正的实时处理,证明了基于FPGA的图像畸变校正系统具有高速处理、低功耗和高精度的特点,对于实时图像畸变校正问题具有很好的应用前景。

关键词:FPGA;图像畸变;实时处理;图像校正一、引言图像畸变是指图像在采集、传输或再现过程中产生的各种形变和失真现象。

这些形变和失真可能会影响图像的准确性和可靠性,因此图像畸变校正成为了图像处理领域中重要的研究课题。

基于FPGA的实时图像畸变校正系统由于具有高度并行处理能力和快速响应的特点,被广泛应用于机器视觉、无人机遥感等领域。

二、图像畸变的原因与分类图像畸变主要由摄像机镜头失真、光学成像非理想等因素引起。

根据畸变的特性,图像畸变可分为径向畸变和切向畸变两大类。

径向畸变是指图像的边缘部分拉伸或压缩,而切向畸变则是图像的边缘部分发生扭曲。

三、基于FPGA的实时图像畸变校正算法本文设计了一种基于FPGA的实时图像畸变校正算法,主要包括以下几个步骤:1. 图像畸变参数提取:对输入的图像进行预处理,提取出径向和切向畸变的参数。

2. 校正矩阵生成:根据提取到的畸变参数,生成图像畸变校正矩阵。

3. 图像畸变校正:以每个像素为单位,通过矩阵变换将畸变图像校正为正常图像。

4. 实时显示:将校正后的图像实时显示在输出设备上。

四、硬件平台设计本文搭建了基于FPGA的实时图像畸变校正系统硬件平台。

该平台主要由FPGA芯片、图像采集模块、图像存储模块和显示模块构成。

其中,FPGA芯片负责图像畸变校正算法的实时处理,图像采集模块用于获取待校正的图像,图像存储模块用于保存畸变校正前后的图像数据,显示模块则将校正后的图像实时显示出来。

基于FPGA_的九点插值自适应图像缩放算法设计

第 38 卷第 8 期2023 年 8 月Vol.38 No.8Aug. 2023液晶与显示Chinese Journal of Liquid Crystals and Displays基于FPGA的九点插值自适应图像缩放算法设计朱明达*,辛鹏,常嘉颖(中国石油大学(北京)信息科学与工程学院,北京 102249)摘要:为了能够在现场可编程门阵列(Field Programmable Gate Array,FPGA)硬件平台上实现速度快、质量高的图像缩放,提出一种九点插值自适应缩放算法。

首先提出九点插值基本算法以减少逻辑资源用量,达到的图像缩放效果明显优于最近邻域插值算法,但略差于双线性插值算法,且图像边缘不够清晰。

为了优化九点插值基本算法对图像边缘的缩放效果,提出了九点插值与最近邻域插值算法相结合的自适应缩放算法,通过MATLAB和FPGA对以上算法分别进行软件、硬件的对比分析和实验验证。

实验结果表明,自适应九点插值算法比最近邻域、双线性插值图像缩放算法的峰值信噪比提高0.3~2.5 dB,并且硬件资源消耗量比双线性插值减少了约20%。

该算法减轻了传统算法的图像边缘模糊与图像严重失真问题,且占用FPGA资源少,有更高的应用价值。

关键词:图像缩放;现场可编程门阵列;线性插值;自适应插值中图分类号:TP391.4 文献标识码:A doi:10.37188/CJLCD.2022-0338Design of nine-point interpolation adaptive image scalingalgorithm based on FPGAZHU Ming-da*,XIN Peng,CHANG Jia-ying(College of Information Science and Engineering, China University of Petroleum (Beijing),Beijing 102249, China)Abstract: In order to realize fast and high-quality image scaling on field programmable gate array (FPGA)hardware platform, this paper proposed a nine-point interpolation adaptive scaling algorithm. Firstly, in order to reduce the amount of logical resources, a basic algorithm of nine-point interpolation is proposed, the image scaling effect achieved is obviously better than the nearest neighbor interpolation algorithm but slightly worse than the bilinear interpolation algorithm, and the edge of the image is not clear. In order to optimize the scaling effect of the basic algorithm of nine-point interpolation on the edge of the image, an adaptive scaling algorithm combining nine-point interpolation and nearest neighbor domain interpolation is proposed.The algorithm software,hardware comparative analysis and experimental verification are carried out through MATLAB and FPGA. Experimental results indicate that the peak signal to noise ratio of the adaptive nine-point interpolation algorithm is 0.3~2.5 dB higher than that of the traditional scaling algorithm on average,and the hardware resource consumption is reduced by about 20% compared with bilinear interpolation. The nine-point interpolation algorithm alleviates the problems of image edge blur and severe image distortion 文章编号:1007-2780(2023)08-1075-09收稿日期:2022-10-17;修订日期:2022-11-08.基金项目:国家自然科学基金(No.41704173);中国高校产学研创新基金(No.2020HYA08001)Supported by National Natural Science Foundation of China(No.41704173); Industry-University-ResearchInnovation Fund for Chinese Universities (No.2020HYA08001)第 38 卷液晶与显示of the traditional algorithms, and it occupies less FPGA resources and has higher application value.Key words: image scaling; field programmable gate array; linear interpolation; adaptive interpolation1 引言视频图像缩放技术目前在医疗、遥感、军事等领域有着广泛的应用[1-2],多采用FPGA进行视频图像的实时处理。

图像放大缩小的原理和应用

图像放大缩小的原理和应用1. 原理图像放大缩小是数字图像处理中的一种基础操作,其原理是通过改变图像像素的尺寸来实现。

在图像放大时,通常采用插值算法来填充空白像素;而在图像缩小时,通常采用像素平均或取样的方式来减少像素。

1.1 图像放大原理图像放大的主要原理是通过插值算法来增加图像的像素数量,从而增大图像的尺寸。

插值算法可以根据原图像的像素值,在新的像素位置上生成合适的像素值。

常用的插值算法包括最近邻插值、双线性插值和双三次插值等。

最近邻插值是一种简单的插值算法,它通过找到离新像素位置最近的像素值来进行插值。

这种算法简单快速,但会导致图像边缘的锯齿效应。

双线性插值是一种更精确的插值算法,它考虑了新像素位置附近的像素值,并进行线性插值计算。

这种算法可以有效地减少锯齿效应,但对于像素边缘仍可能存在模糊问题。

双三次插值是一种更高级的插值算法,它在双线性插值的基础上添加了更多的像素信息,通过曲线拟合来生成更精确的像素值。

这种算法可以进一步减少锯齿效应和模糊问题,但计算复杂度也相应增加。

1.2 图像缩小原理图像缩小的主要原理是通过减少图像的像素数量来缩小图像的尺寸。

常用的缩小算法包括像素平均和取样算法。

像素平均算法是一种简单的缩小算法,它将原图像中的多个像素的 RGB 值取平均,生成新的像素值。

这种算法简单快速,但会导致图像细节丢失。

取样算法是一种更精确的缩小算法,它通过从原图像中选择几个有代表性的像素进行采样,并生成新的像素值。

这种算法可以保留更多的图像细节,但计算复杂度也相应增加。

2. 应用图像放大缩小在许多领域都有广泛的应用,下面列举了几个常见的应用场景:•数字摄影:在数字摄影中,图像放大可以用于增加图像的分辨率,从而提高图像的清晰度和细节呈现。

•医学影像:在医学影像领域,图像放大可以用于放大细胞、组织或病变区域,帮助医生进行更精确的诊断。

•图像处理:在图像处理领域,图像缩小可以用于生成缩略图,帮助用户快速浏览和索引大量图像;图像放大可以用于图像重建和增强,帮助改善图像质量。

基于FPGA的视频缩放设计与实现

基于FPGA的视频缩放设计与实现

FPGA视频缩放是一种基于现场可编程门阵列(FPGA)实现的视频处理技术。

它通过对视频帧进行采样和重构,实现对视频尺寸的调整,从而满足不同的视觉需求。

本文将介绍FPGA视频缩放的设计与实现。

FPGA视频缩放的设计从以下几个方面展开:图像采集、图像处理和图像显示。

需要通过摄像头或者视频源采集视频图像,并将其传输到FPGA芯片内部。

然后,对采集到的视频图像进行处理,包括图像缩放、噪声滤波等操作。

将处理后的图像传输到显示设备,如显示器或者电视机。

在FPGA视频缩放的实现过程中,需要使用一些常用的图像处理算法和技术。

最常见的是双线性插值算法。

该算法利用附近的像素值来估计目标像素的值,以实现图像的缩放。

在此基础上,还可以使用其他的图像处理技术,如直方图均衡化、边缘检测等,以提高图像质量。

在设计FPGA视频缩放系统时,还需要考虑硬件资源和性能的问题。

FPGA芯片的资源有限,需要合理利用和分配。

视频处理过程中会涉及到大量的数据计算和存储,对FPGA芯片的性能要求较高。

需要对系统进行优化,采用并行计算和高速缓存等技术,以提高系统的性能和效率。

还需要考虑FPGA视频缩放系统的可靠性和可扩展性。

在设计过程中,需要进行模块化设计,将不同的功能模块进行划分和组合,以方便系统的测试和维护。

还应具备一定的可扩展性,以便于后期对系统进行升级和扩展。

基于fpga的数字图像处理原理及应用

基于FPGA的数字图像处理原理及应用1. 引言数字图像处理作为一项重要的技术,已经被广泛应用于多个领域,例如医疗影像、机器视觉和图像识别等。

而基于FPGA(Field-Programmable Gate Array)的图像处理系统已经成为研究的热点。

本文将介绍基于FPGA的数字图像处理原理及其应用。

2. FPGA的基本原理和特点FPGA是一种可重构的硬件设备,具有可在现场编程的特点,使其适用于不同应用的实时高性能图像处理。

FPGA拥有可配置的逻辑单元和内部存储器,可用于实现各种数字图像处理算法。

3. FPGA在数字图像处理中的应用3.1 图像滤波•FPGA可以实现图像滤波算法,例如均值滤波、中值滤波和高斯滤波等。

•FPGA的并行计算能力使得图像滤波可以以实时高性能的方式进行。

3.2 图像边缘检测•基于FPGA的图像边缘检测算法可以有效地提取图像的边缘信息,用于目标识别和图像分割等应用。

•FPGA的并行处理能力和灵活的逻辑结构使得边缘检测算法可以以高效的方式实现。

3.3 图像增强•FPGA可以用于实现图像增强算法,例如直方图均衡化和灰度级调整等。

•FPGA的硬件并行性使得图像增强算法可以在实时性要求较高的应用中得到广泛应用。

3.4 图像压缩•FPGA可以实现图像压缩算法,例如JPEG压缩算法。

•FPGA的高速并行处理能力使得图像压缩可以以实时高效的方式进行。

4. FPGA在数字图像处理中的优势•FPGA具有硬件并行处理能力,可以实现高效的图像处理算法。

•FPGA具有灵活性,可以根据不同的应用需求进行编程和配置。

•FPGA具有低功耗和低延迟的特点,适用于实时性要求较高的图像处理应用。

•FPGA具有较高的计算性能和吞吐量,可以满足高帧率的图像处理需求。

5. FPGA在数字图像处理中的应用案例5.1 医疗影像处理•基于FPGA的医疗影像处理系统可以用于实时的医学图像分析和诊断。

•FPGA的硬件并行处理能力可以提高医疗图像处理系统的性能和效率。

图像缩放原理

图像缩放原理

图像缩放原理是指通过改变图像的尺寸,使其在不改变内容的情况下适应于不同的显示设备或应用场景。

最常见的图像缩放方法有插值法、双线性插值法和双三次插值法。

插值法是最简单的图像缩放方法之一,其原理是通过已知像素点的亮度值来估计未知像素点的亮度值。

常见的插值算法有最近邻插值和双线性插值。

最近邻插值法的原理是将目标图像的坐标映射到原图像中,并找到离目标坐标最近的点的亮度值作为目标点的亮度值。

这种方法简单快速,但可能会引入锯齿状的边缘效应。

双线性插值法的原理是通过目标点周围的四个邻近点的亮度值进行加权平均,来估计目标点的亮度值。

这种方法可以平滑边缘,但会导致图像模糊。

双三次插值法是一种更高级的插值方法,其原理是通过目标点周围的16个邻近点的亮度值进行加权平均。

这种方法可以在保持图像细节的同时,减少锐化和伪影效果。

除了插值法,还有一些其他的图像缩放方法,如基于小波变换的图像缩放方法和基于域仿射变换的图像缩放方法。

这些方法都以不同的原理和算法来实现图像的缩放,以满足不同应用场景的需求。

图像缩放IP的FPGA实现

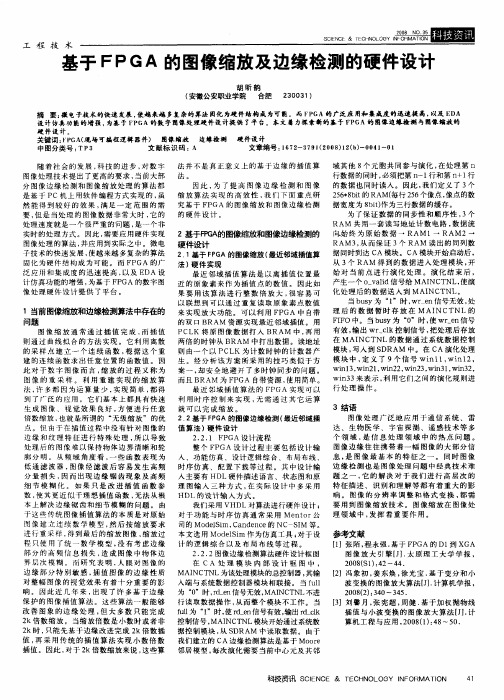

需要 。图像缩 放 I 根据 图像 显 示 的要 求 分 别 在 P可

常用 的图像插值算法有最近邻域插值、 双线性 插值和双三次插值。 最近领域插值算法十分简单, 运算速度快 , 待插

值像素将在源图像中距离其最近的像素的灰度值作 为其显示的灰度值 , 但是该算法 由于没有考虑相邻

— -

L- ・

彗

,

( 四川教育学院 网络与信息管理中心, 成都 6 13 ) 110

摘 要 : 了降低 图像 缩放 I 为 P的硬件 资源 占用率并获得 最佳 的图像 缩放 质量 , 用基 于二 次函数 的三点控 制 采

插值算 法并利 用 F G P A实现 。阐述该 I 系统架构 , P的 重点介 绍线性缓存 的读写控 制和插值 算法的优化 处理 , 相比 双三 次图像插值 算法 , I F G 该 P的 P A硬件 资源 占用仅 有其一半。 关键词 :图像缩放 ; 插值 算法; 线性缓存 ;P A FG

( ) 线 性 插 值 c双

( ) - 捅 值 d 双 E次

( )E点 斜 率 控 制 插 值 e-

图 2 不 同插值算法的缩放效果对比。2X 2 18 18放大至 26 26 5X 5

与输出图像具有同样大小的显示面积 , 从而确定待插

双三次插值算法的插值核为三次函数 , 它不仅 考虑了待插值像素周 围 1 6个源 图像像素点 的灰度 值的影响, 还考虑 了它们灰度值变化率的影响, 因此 缩放后的图像边 缘更加锐利 , 细节表现更加清 晰。 该算法常用于高质量的图像处理系统 , 在实现时需

l9 1

四川教育学院学报

基于FPGA的图像缩放及边缘检测的硬件设计

图 像 缩 放 通 常 通 过 插 值 完 成 , 插 值 而 则通 过 曲线拟 合的 方 法 实现 。它 利 用 离散 的 采 样 点 建 立 一 个 连 续 函 数 , 据 这 个 重 根 建 的连 续 函 数 求 出任 意 位 置的 函 数值 。 因 此 对 于 数 字 图像 而 言 , 放 的 过 程 又 称 为 缩 图 像 的 重 采 样 。利 用 重 建 实 现 的 缩 放 算 法 , 多都因为运算量少 , 许 实现 简单 , 得 都 到 了广 泛 的应 用 。 它们 基 本 上都 具 有快 速 生 成 图 像 、 视 觉 效果 良好 , 方便 进 行 任意 倍数缩 放 , 也就 是所 谓 的 “ 无级缩 放 的优 点 。怛 由于 在插 值过 程 中 没 有针 对 图 像的 边 缘 和 纹 理 特 征 进 行 特 殊 处理 , 以 导 致 所 处理 后 的 图 像准 以 保持 物 体 边界 清晰 和 轮 廓 分 明 。 从 频域 角 度 看 , 些 函数 表 现 为 一 { 通 滤 波 器 , 像 经 滤 波后 容 易发 生 高频 氐 图 分 量 损 失 , 而 出 现边 缘 锯 齿现 象 及 高 频 因 细 节 模 糊 化 。 如 果 只 是 改 进 插 值 函 数 参 数 , 其更 近 似 干理 想插 值 函数 , 法 从根 使 无 本 上解 决 边缘 锯 齿 和细 节 模 糊的 问题 。 由 于这 些 传统 图像 插值 算 法 的 本 质是 对原 始 图 像建 立 连 续 数 学 模 型 , 后 按 缩 放 要 求 然 进 行 重 采样 , 到最 后 的缩 放 图像 , 放过 得 缩 程 只使 用 了统 一 数 学 模 型 , 有 考 虑边 缘 没 部 分的 高 频 信息 损 失 , 成 图像 中物 体 边 造 界 层次 模 糊 。而 研 究 表 明 , 眼 对 图像 的 人

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

whole structure of scaler is designed starting、析m the analysis of scaling core.It also

brings up a new optimized algorithm···-·-window scaling algorithm on the base of research in the classical image scaling algorithm and then simplifies the calculation tlexity.In FPGA implementation,our design separates the

下面对几种平板显示技术的基本特征进行概述,以比较异同及发展前景。 1.液晶显示技术(LCD,Liquid Crystal Display) LCD有“第二半导体”的称谓,它具有低工作电压、功耗小、重量轻、厚度 薄、长寿命、无电磁辐射、不耀眼、抗干扰性好、抗震性能好、有效显示面积大、 适于大规模集成电路直接驱动、易于实现全彩色显示等优良特色。 液晶显示器件利用了液晶晶体各向异性产生光电效应的物理特性:在通电导 通后排列有序,使光线容易通过;不通电时排列混乱,阻止光线通过。液晶显示 技术经历了扭曲向歹IJ【121(TN.LCD)、超扭曲向列‘131(STN.LCD)和薄膜晶体管

design of scaler and implements its verification in FPGA.Our scaler is able to support scaling operation to images with different resolution in adjustable modes.Besides,it

本设计使用Verilog HDL对各模块进行了RTL级描述,并使用Quartus II 7.2 进行了逻辑仿真,最后使用Altera公司的FPGA芯片来进行验证。通过逻辑验 证和系统仿真,证明该scaler的设计达到了预期的目标。对于不同分辨率的图像, 均可以在显示屏上得到稳定的显示。

关键词:平板显示器、Scaler、矩形窗缩放算法、FPGA

achieves the desired objectives.For images with different resolution,they Can be

stably displayed in FPD.

Keywords:Flat panel display,Scaler,window scaling,FPGA

图像缩放内核是scaler的核心部分,它是scaler中的主要运算单元,完成图 像缩放的基本功能,它所采用的核心算法以及所使用的结构设计决定着缩放性能 的优劣,也是控制芯片成本的关键。因此,本文从缩放内核的结构入手,对scaler 的总体结构进行了设计;通过对图像缩放中常用算法的深入研究提出了一种新的

优化算法——矩形窗缩放算法,并对其计算进行分析和简化,降低了计算的复杂 度。FPGA设计中,采用列缩放与行缩放分开处理的结构,使用双口RAM作为

两次缩放间的数据缓冲区。使用这种结构的优势在于:行列缩放可以同时进行, 数据处理的可靠性高、速度快:内核结构简单明了,数据缓冲区大小合适,便于 设计。此外,本文还介绍了其他辅助模块的设计,包括DVI接口信号处理模块、 缩放参数计算与控制模块以及输出信号检测与时序滤波模块。

(1)屏幕亮度非常均匀,没有亮区和暗区,不会出现图像几何畸变和色彩 漂移现象,不受磁场影响,具有更好的环境适应能力;

(2)具有非常陡峭的阈值特性,适合于时分多路驱动; (3)具有存储效应,即使增加显示容量,也容易获得高亮度显示; (4)结构及制造工艺简单,不需要TFT那样的高精度,投资小,适合现代 化大批量生产; (5)具有记忆特性,高亮度、大屏幕、全彩色,高对比度和高分辨率,使 图像更加清晰,色彩更加鲜艳,感受更加舒适,效果更加理想; (6)色彩还原性好,灰度丰富可超过256级,色域与CRT相近,对迅速 变化的画面响应速度快,适用于显示动画和播放视频; (7)视野开阔,能提供格外亮丽、均匀平滑的画面和更大观赏角度,视角 高达160度; (8)纯平面、厚度薄、体积小,特别适合公共信息显示、壁挂式大屏幕电 视和自动监视系统。 但是PDP也有不足:显示屏上的玻璃极薄,不能承受过大或过小的气压,

size.The dissertation also presents the design of other auxiliary module,including

DVI interface signal processing module,scaling parameter computing and controlling

上海大学 硕士学位论文 图像缩放算法的研究与FPGA设计 姓名:刘婧 申请学位级别:硕士 专业:电工理论与新技术 指导教师:冉峰

20090101

上海大学硕士学位论文

摘要

Scaler是平板显示器件(FPD,Flat Panel Display)中的重要组成部分,它将 输入源图像信号转换成与显示屏固定分辨率一致的信号,并控制其显示在显示屏 上。本文在研究图像缩放算法和scaler在FPD中工作过程的基础上,采用自上 而下(Top.down)的设计方法,给出了scaler的设计及FPGA验证。该scaler支 持不同分辨率图像的缩放,且缩放模式可调,也可以以IP core的形式应用于相 关图像处理芯片中。

call be integrated in other image processing chips in the form of IP core. Image scaling core is the key part and main computing unit in scaler,which

implements the basic function of image scaling.The utilized core algorithm as well as structure determines the scaling performance and cost of chip design.Therefore,the

with FPGA chips from Altera.The dissertation introduces the building of FPGA

verification platform and testing in it,and then verifies that the design of scaler

V

上海大学硕士学位论文

AB STRACT

Scaler is one of the most important parts of FPD(Flat Panel Display),which converts the source image signal into that with the same resolution as FPD,and then

1.2平板显示技术发展现状与趋势

伴随着现代信号处理技术和大规模集成电路技术的飞速发展,显示技术正在 发生一场革命,平板显示‘1】【2】(FPD,Flat Panel Display)技术以其低功耗、小型 化、数字化、便携式、多功能越来越受人们的青睐,已可与阴极射线管显示器

(CRT,Cathode Ray Tube)相抗衡,正成为新世纪的主流显示技术。平板显示 一般是指显示器件的深度小于显示屏幕对角线1/4长度的显示技术【3】。按工作原 理的不同,平板显示器可分为液晶显示(LCD)[41、等离子体显示(PDP)【51、 电致发光显示(ELD)【6】、有机发光二极体显示(OLED)【7】【8】、场发射显示(FED) 【91、真空荧光显示(VFD)U01和发光二极管拼接显示【111等。就目前来看,LCD、 PDP及OLED成为平板显示的三大支柱。

上海大学硕士学位论文

阵列【14】(TFT-LCD)三个重要发展阶段。其中,TFT-LCD(Thin Film Transistor-LCD)是集大规模半导体集成电路技术、驱动IC技术和平板光源技术 于一体的高新技术,采用薄膜晶体管有源矩阵,在每个像素上设计有一个场效应 开关管,易于实现真彩、高分辨率,而且响应速度快、灰度高,因此成为LCD 的主要发展方向。它使LCD进入高画质、真彩图像显示的新阶段,具有高科技 含量、高附加值、高效益等特质,拥有美好的发展前景。

但LCD也有不足之处,它属于非主动发光型即被动光源,显示视角小,对 比度和亮度受环境的影响较大,响应速度较慢且工艺复杂。但是长期困扰液晶平 板显示器的三大难题:视角、色饱和度、亮度现在已经获得重大突破,液晶平板 显示技术已经步入成熟阶段。

2.等离子体显示技术(PDP,Plasma Display Panel) PDP是伴随惰性气体等离子体放电,利用行、列矩阵电极交点发光的显示器 件。其中等离子体(Plasma)是指正负电荷共存,处于电中性的放电气体的状态。 PDP分为交流和直流两种类型,采用表面放电式的AC.PDP[15】占主导地位。 与其它平板显示器件相比,PDP具备许多独特的优点,具体如下:

VI

上海大学硕士学位论文

原创性声明

本人声明:所呈交的论文是本人在导师指导下进行的研究工作。 除了文中特别加以标注和致谢的地方外,论文中不包含其他人已发表 或撰写过的研究成果。参与同一工作的其他同志对本研究所做的任何 贡献均己在论文中作了明确的说明并表示了谢意。

签名:三啦LEl期:鱼蚪

本论文使用授权说明

makes it displayed on FPD.Based on the research of image scaling algorithm and the

analysis of scaler,the dissertation chooses a top—down design topology to fulfill the