2018北京市集成电路设计大赛数字组题目二:伪码同步电路

集成电路创新大赛题目

集成电路创新大赛题目随着信息技术的不断发展,集成电路已经成为了现代电子工业的核心领域之一。

为了促进集成电路领域的创新发展,近年来,国内外各大高校和企业纷纷举办集成电路创新大赛,吸引了大批电子、计算机、通信等相关专业的优秀学生和科研人员参赛。

那么在集成电路创新大赛中,都有哪些经典的比赛题目呢?以下是其中几个经典的集成电路创新大赛题目:1、基于FPGA的数字信号处理算法设计。

FPGA是一种可编程逻辑器件,广泛应用于数字信号处理、图像处理、嵌入式系统等领域。

这个题目要求参赛者设计一种数字信号处理算法,并采用FPGA实现。

这对参赛者的硬件设计和软件调试能力都有一定的挑战性。

2、基于深度学习的图像识别系统设计。

深度学习已经成为了目前最流行的人工智能技术之一。

这个题目要求参赛者设计一种基于深度学习的图像识别系统,并采用ASIC实现。

参赛者需要具备深度学习算法的理论基础和ASIC设计的实际经验。

3、基于MEMS传感器的智能健康手环设计。

MEMS传感器是一种微型化、集成化的传感器,广泛应用于智能手机、智能手环等产品中。

这个题目要求参赛者设计一种基于MEMS传感器的智能健康手环,并实现心率、血氧、血压等多种健康监测功能。

这个题目对参赛者的硬件设计和算法实现能力都有较高的要求。

4、基于5G通信芯片的高速数据传输系统设计。

5G通信是目前最热门的通信技术之一,具有超高速率、低延迟、高可靠性等特点。

这个题目要求参赛者设计一种基于5G通信芯片的高速数据传输系统,并实现高速数据的稳定、低延迟的传输。

这个题目对参赛者的通信技术和芯片设计能力都有一定的挑战性。

总的来说,在集成电路创新大赛中,题目的难度和挑战性与时俱进,反映了当前集成电路领域的最新技术和发展趋势。

只有参赛者拥有强大的专业知识和实践能力,才能在这些比赛中脱颖而出,成为集成电路领域的未来之星。

蔡觉平老师西电Verilog-HDL上机大作业(硬件描述语言)-微电子学院

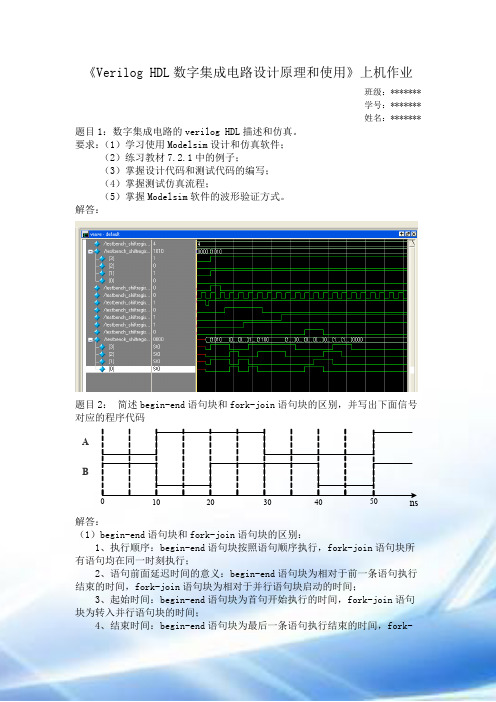

《Verilog HDL数字集成电路设计原理和使用》上机作业班级:*******学号:*******姓名:******* 题目1:数字集成电路的verilog HDL描述和仿真。

要求:(1)学习使用Modelsim设计和仿真软件;(2)练习教材7.2.1中的例子;(3)掌握设计代码和测试代码的编写;(4)掌握测试仿真流程;(5)掌握Modelsim软件的波形验证方式。

解答:题目2:简述begin-end语句块和fork-join语句块的区别,并写出下面信号对应的程序代码AB解答:(1)begin-end语句块和fork-join语句块的区别:1、执行顺序:begin-end语句块按照语句顺序执行,fork-join语句块所有语句均在同一时刻执行;2、语句前面延迟时间的意义:begin-end语句块为相对于前一条语句执行结束的时间,fork-join语句块为相对于并行语句块启动的时间;3、起始时间:begin-end语句块为首句开始执行的时间,fork-join语句块为转入并行语句块的时间;4、结束时间:begin-end语句块为最后一条语句执行结束的时间,fork-join语句块为执行时间最长的那条语句执行结束的时间;5、行为描述的意义:begin-end语句块为电路中的数据在时钟及控制信号的作用下,沿数据通道中各级寄存器之间的传送过程。

fork-join语句块为电路上电后,各电路模块同时开始工作的过程。

(2)程序代码:Begin-end语句:module initial_tb1;reg A,B;initialbeginA=0;B=1;#10 A=1;B=0;#10 B=1;#10 A=0;#10 B=0;#10 A=1;B=1;endendmoduleFrk-join语句:module wave_tb2;reg A,B;parameter T=10;initialforkA=0;B=1;#T A=1;B=0;#(2*T) B=1;#(3*T) A=0;#(4*T) B=0;#(5*T) A=1;B=1;joinendmodule题目3. 分别用阻塞和非阻塞赋值语句描述如下图所示移位寄存器的电路图。

集成电路芯片测试仪(A题)——【全国大学生电子设计大赛】

集成电路芯片测试仪(A题)一、任务设计制作一个集成电路芯片测试仪,能对常用的74系列逻辑芯片进行逻辑功能测试,以确定芯片的好坏和型号。

二、要求1.基本要求(1)通过键盘输入型号,可以对74系列的00/02/04/08/10/11/20/21/27/30十种组合逻辑芯片进行逻辑功能测试,确定其功能正确性;(2)通过键盘输入管腿特性,可以确定上述74系列的组合逻辑芯片的型号;(3)显示上述芯片的逻辑符号和逻辑表达式。

2.发挥部分将上述三项基本要求扩展到74系列时序电路:74/109/160/245等。

(1)通过键盘输入型号,可以对74系列的74/109/160/245等芯片进行逻辑功能测试,确定其功能正确性;(2)通过键盘输入管腿特性,可以确定上述74系列时序逻辑芯片的型号;(3)显示上述芯片的逻辑符号和状态转换图;(4)其它特色与创新。

1三、评分标准四、说明要求用单片机或DSP模块做成一个相对独立的整体,不能用PC机实现。

2LED显示棒(B题)一、任务设计制作一个依靠摇动能显示字符、图形的LED显示棒。

二、要求1.基本要求(1)设计一个基于LED的显示棒,LED灯必须线状排列,至少使用16只。

(2)摇动时形成的亮灯扇形区域能够让人分辨出“A”字符。

(3)摇动时形成的亮灯扇形区域能够让人分辨出“电”字。

(4)摇动时形成的亮灯扇形区域能够让人分辨出国际奥委会五环图形。

(5)用按键实现显示切换,用电池供电。

2.发挥部分(1)摇动时形成的亮灯扇形区域能够让人分辨出英文单词“Welcome”。

(2)摇动时形成的亮灯扇形区域能够让人分辨出汉字词组“美亚”。

(3)摇动时形成的亮灯扇形区域能够让人分辨出北京奥运会会徽图形。

(4)其它特色与创新。

三、评分标准3四、说明不得用LED棒专用芯片实现。

4具有实时语音播报的超声波测距测速仪(C题)一、任务设计并制作一台具有实时语音播报的超声波测距测速仪,被测物为一块面积不大于30cmX20cm的实物(可以和小车装在一起)。

2018年TI杯模拟电子系统设计邀请赛题A—数字多用表

全国大学生电子设计竞赛2018年TI杯模拟电子系统设计邀请赛数字多用表(A题)1.任务设计并制作一台具有直流电压、交流电压和电阻测量功能的数字多用表。

其中,A/D 转换器要求使用ADS112C04芯片。

2.要求⑴直流电压测量(只要求测量正极性电压)(23分)①量程(有效值):0.2V、2V;②最大显示数19999;精度:±0.05%读数±2个字;③测量速度≥2次/s;输入阻抗≥10MΩ。

⑵交流真有效值电压测量。

被测信号为正弦波或非正弦波信号,直流偏移电压为0V,频率范围:10~100Hz。

(32分)①量程:0.2V、2V;②最大显示数1999;精度:±0.8%读数±2个字;③测量速度≥2次/s;输入阻抗≥10MΩ;⑶电阻测量(23分)①电阻量程:2Ω、200kΩ;②测量速度≥2次/s;③最大读数1999;精度:±0.5%读数±2个字。

⑷具有待机模式的低功耗性能。

(12分)① 待机模式的低功耗性能:在测量过程中,若1分钟内无键按下,仪器能自动转入待机状态;再按任意键,仪器能返回工作状态。

② 待机工作状态时的功耗≤2.5mW 。

⑸ 其他。

(10分)⑹ 设计报告 (10分) 项 目主要内容 满分方案论证比较与选择,方案描述 2 理论分析与计算系统相关参数设计 4 电路与程序设计 系统组成,原理框图与各部分的电路图,系统软件与流程图2测试方案与测试结果 测试结果完整性,测试结果分析2 总分 10 3.说明⑴ 作品可采用现场提供的直流稳压电源供电。

⑵ 真有效值又称全波有效值,其值为被测信号的均方根值。

当采用数字取样方法时,先对被测信号在一个周期内进行等间隔采样,再计算出所有采集数据的均方根值,其计算公式为:式中,n 为在一个交流电压周期T 内的取样点数。

2018年江西省高考信息技术真题

B.邮崗寄送申请材料山去接岀国逮交材料C. 103D. 1042018年江西省高考技术试题第一部分倍息技术加分) 第I 卷必修模块(70分)一、选择題(本大题20小题'毎小题2分,井枷分。

每小題给出的四个选项中•只有一顼是苻合超目要求的)1,知电教馆发布通知「20悟年中小罕牛.电棘制作比軽”參赛作晶必须在3月22 H 前匕传到省幕础教育资源 金共服务半台七小明3月23 H 才看到这则適却*结果尤法上传作品•以敷倍过比赛。

这主要洋取「信息的 乩时效性«. ssm&製孚性 (1曾涸性2•下列钢能手机操作中•属于入王押能技术应用范畴的眉 A,通过AI 屮购买电影粟 B 使用翻译工具与外国人士交流C 僅询本人高易成绩I )收发电子邮件工那用年了 ”,啊烹互联倒应急中也发现*个锁屏勒索类病再变种「该类屈事通过锁屛用八于机•勒家囲门 村费解锁・对手机安全和用户財产均造成严用咸胁为r 防止情旅侵害.下列行为令理的是 ① 手机上安然杀誓软件井定期升级、査杀摘毒 ② 公共场所通过见费无线网塔进行手机支付I 融将手机连搖到公共电脑上作为u 盘使用④iS 过手机厂商的应用商城卜皱AFT 软件A.®@H ®@G ②©•D.②®4邛亂张立罐眄?这里壘社保中心戾煤枝査部”您上牛”1七号•在华西医科大学附网低院开药7北元.医保 支H 62Q 元•医保监察系统发现,您的展保卡存在违规开细的现象削嫌骗保册按將税说的进行戍卜操件 ……”.这是某电影屮的片段*受富人在5分仲内被骗走瑰万无人民「氐 假如称接到陌生人电话」寸方要求 你汇款或对丫艮行卡进行相黄撫作■下列做的是 乩楼到电话肓’丈即按照对方的要求进行?T.款 乩根据对方自报的身份逬行判断后决定是否汇款C 根据对方所说聊件的直实性涯宦层否汇款 D.接到此类电话•立即挂断不予理睬工已抑十六进制数(12B ).转换为十进制数的运算过程为L (12B )1^lxl61+2xl6^11Mi^99T M (6F )l (W 换为十进制数的结果为A. 109B. HOC. HlD. 1126. 目前有些趙市提供n 朋給算系统,对顾客所购商甜进行給惊,此类白的结n 系统屈于 A 襟件杲统B.故邺库应用泵统C.数据库管俚乘统L.编译系竦7. 小期前读明朝张居正的诗旬懺飾又逐孤鸿远,独迹还如講叶分欄时.谓到牛僻字“幣,他用Word 的浄音指南"工民嵌知沖的好为虫瞬叭 小明萩取肚信息的来源是 九啦申媒介B.纸质媒介C 事物D •专业人士乩随看技术的进步*检索方式也发生『改变:在稟校开展的*传统中戡药知识进校园"活动中,同学们借助手 机拍照,使用照片搜索的方法辨识苔种中草药材.TMfitJ 的喀称3g 态和生长周期等特性口上述新型检索 方式賦于 儿目录检嬢B.关键说检離C •图粽楡盍D ,个牲flS 检寮9.某校运动会开將式的稈序为:升国旗、壽国歌,校领导讲话'运动员入场,裁舛员代表发言,运动员代表壇言。

2018年TI杯大学生电子设计竞赛题

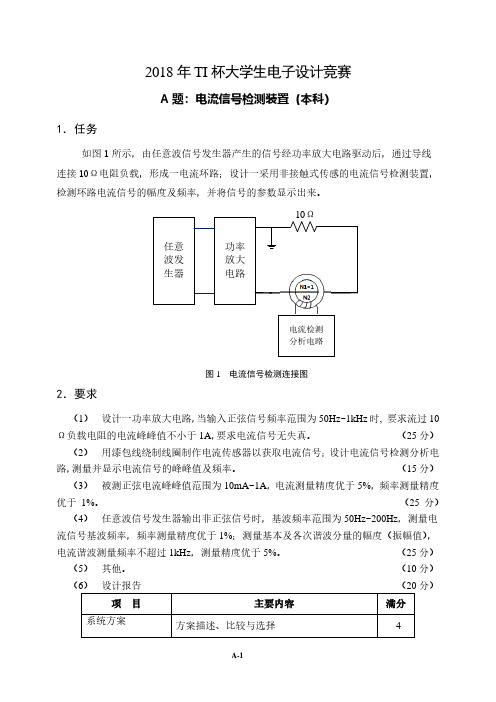

2018年TI杯大学生电子设计竞赛A题:电流信号检测装置(本科)1.任务如图1所示,由任意波信号发生器产生的信号经功率放大电路驱动后,通过导线连接10Ω电阻负载,形成一电流环路;设计一采用非接触式传感的电流信号检测装置,检测环路电流信号的幅度及频率,并将信号的参数显示出来。

图1 电流信号检测连接图2.要求(1)设计一功率放大电路,当输入正弦信号频率范围为50Hz~1kHz时, 要求流过10Ω负载电阻的电流峰峰值不小于1A,要求电流信号无失真。

(25分)(2)用漆包线绕制线圈制作电流传感器以获取电流信号;设计电流信号检测分析电路,测量并显示电流信号的峰峰值及频率。

(15分)(3)被测正弦电流峰峰值范围为10mA~1A,电流测量精度优于5%,频率测量精度优于1%。

(25分)(4)任意波信号发生器输出非正弦信号时,基波频率范围为50Hz~200Hz,测量电流信号基波频率,频率测量精度优于1%;测量基本及各次谐波分量的幅度(振幅值),电流谐波测量频率不超过1kHz,测量精度优于5%。

(25分)(5)其他。

(10分)(6)设计报告(20分)项目主要内容满分系统方案方案描述、比较与选择 4理论分析与计算电流测量方法谐波分量测量方法5 电路设计电路设计 5测试方案与测试结果测试方案测试结果完整性测试结果分析4设计报告结构及规范性摘要、报告正文结构、公式、图表的完整性和规范性2 总分203.说明(1)为提高电流传感器的灵敏度,可用用漆包线在锰芯磁环上绕制线圈,制作电流传感器。

(2)在锰芯磁环上绕N2匝导线,将流过被测电流的导线从磁环中穿过(N1=1),构成电流传感器。

2018年TI 杯大学生电子设计竞赛B 题:灭火飞行器(本科)1.任务基于四旋翼飞行器设计一个灭火飞行器(简称飞行器)。

飞行器活动区域示意图如图1所示。

在图1中,左下方的圆形区域是飞行器起飞及降落点;右侧正方形区域是灭火防区,防区中有4个用红色LED 模拟的火源(火源用单只0.5W 红色发光二极管来实现,建议LED 电流不超过25mA )。

2018年计算机考研真题及参考答案

2018年全国硕士研究生入学统一考试计算机科学与技术学科联考计算机学科专业基础综合试题一、单项选择题:第1~40小题,每小题2分,共80分。

下列每题给出的四个选项中,只有一个选项最符合试题要求。

1.若栈S1中保存整数,栈S2中保存运算符,函数F()依次执行下述各步操作:(1)从S1中依次弹出两个操作数a和b;(2)从S2中弹出一个运算符op;(3)执行相应的运算b op a;(4)将运算结果压人S1中。

假定S1中的操作数依次是5, 8, 3, 2(2在栈顶),S2中的运算符依次是*, - , +(+在栈顶)。

调用3次F()后,S1栈顶保存的值是。

A. -15B. 15C. -20D. 202. 现有队列Q与栈S,初始时Q中的元素依次是1, 2, 3, 4, 5, 6(1在队头),S为空。

若仅允许下列3种操作:①出队并输出出队元素;②出队并将出队元素人栈;③出栈并输出出栈元素,则不能得到的输出序列是。

A. 1, 2, 5, 6, 4, 3B. 2, 3, 4, 5, 6, 1C. 3, 4, 5, 6, 1, 2D. 6, 5, 4, 3, 2, 13. 设有一个12×12的对称矩阵M,将其上三角部分的元素m i, j(1≤i≤j≤12)按行优先存人C 语言的一维数组N中,元素m6, 6在N中的下标是。

A. 50B. 51C. 55D. 664. 设一棵非空完全二叉树T的所有叶结点均位于同一层,且每个非叶结点都有2个子结点。

若T有k个叶结点,则T的结点总数是。

A. 2k-1B. 2kC. k2D. 2k-15. 已知字符集{a, b, c, d, e, f},若各字符出现的次数分别为6, 3, 8, 2, 10, 4,则对应字符集中各字符的哈夫曼编码可能是。

A. 00, 1011, 01, 1010, 11, 100B. 00, 100, 110, 000, 0010, 01C. 10, 1011, 11, 0011, 00, 010D. 0011, 10, 11, 0010, 01, 0006. 已知二叉排序树如下图所示,元素之间应满足的大小关系是。

2018EDA综合实验考试题目

EDA技术实验考试题目1、用结构的描述方法设计一个多用计数器,可以选择为带计数使能、同步复位、带进位输出的增1的60进制计数器或者一百进制计数器,结果由七段数码管显示。

2、用结构的描述方法设计一个多用计数器,可以选择为带计数使能、异步复位、同步装载的可逆七位二进制计数器或者八位二进制计数器,结果山七段数码管显示。

3、设计一个正负脉宽可控的16分频的分频器。

脉宽比由七段数码管显示。

4、根据需要设计一个多用分频器,可以控制实现四种分频(正负脉宽相等)形式:第一种:4分频、第二种:8分频、第三种:10分频、第四种:16分频。

曲七段数码管显示显示当前分频系数。

5、设计一个学号显示电路,可以根据序号显示八位同学的学号(八位数字),学号由8位7段LED数码管输出显示。

6、利用状态机设计一个彩灯控制器,彩灯共有16个,每次顺序点亮相邻的四个彩灯,且保持时间越来越久,如此循环执行。

由七段数码管显示亮灯的序号。

7、设计一个9人表决电路,参加表决者为9人,同意为1,不同意为0,同意者过半则表决通过,绿指示灯亮,表决不通过则红指示灯亮。

山七段数码管显示赞成人数。

8、有16个开关,编号为0到15,编号0的优先级最高。

当某一个拨码开关为1时由数码管显示其编号(可用16进制数显示,亦可用十进制显示)9、利用状态机设计一个全自动洗衣机水位控制器。

要求:当水位超过某一上限值时,停止加水,启动洗衣机;当水位低于某一下限值时,加水,停止洗衣机;否则启动洗衣机,停止加水。

山七段数码管显示显示当前状态(用简易字母表示)。

10、根据真值表设计一位全加器,然后用结构的描述方法设计一个4位加法器。

结果由七段数码管显示。

11、设计6位二进制数到两位BCD (8421码)的转换器。

结果由共阴极数码管显示。

12、利用状态机设计一个跑马灯控制器。

一共有8个彩灯,编号为LED0~LED7,点亮方式为:每次点亮临近两个,且每个状态保持时间越来越久(比如01号亮维持10个时钟周期,23号亮维持15个时钟周期,45号亮维持20个时钟周期,67号亮维持25个时钟周期,如此循环)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

试题二伪码同步电路

设计一个伪码同步电路,实现对输入数据的伪码同步。

包括本地伪码生成电路,伪码调制电路和伪码同步判决控制电路。

题目包含基本要求和发挥部分。

题目不涉及实体硬件电路,所有功能的设计及仿真均在EDA开发环境中实现,竞赛根据总体设计框图及说明、各个模块电路设计说明、时序说明、仿真结果、资源报告、设计总结和程序源代码评定成绩。

一、任务

设计一个伪码同步电路,能够完成对输入的伪码调制信号进行同步。

同步根据伪码的自相关特性,利用匹配滤波结构完成最终同步。

伪码同步电路的基本结构如图1所示。

主要包括伪码生成模块和伪码同步两个部分。

伪码生成模块根据m序列的原理产生伪随机序列,伪码同步模块利用匹配滤波器结构完成伪码同步与捕获,通过可靠的检测策略输出调制的信息。

图1伪码同步电路的基本结构框图

二、要求

1.器件采用CycloneII EP2C35F672C6。

2.基本要求

(1)设计本地伪码发生器:

a)伪码采用m序列,由移位寄存器的初始状态和反馈异或运算确定,实

现原理见说明(1)。

b)该m序列的本原多项式为y=x5+x2+1,伪码周期为31个码片长度。

复位状态下,移位寄存器的初始值设置为00001。

c)一个码片一个采样时钟,输出伪码序列。

d)实现要求:顶层模块数图2所示,伪码序列seq_o连续输出,同时输出

伪码周期脉冲信号seq_p,该脉冲信号可由计数器产生,用于后续数据

调制使用。

rst

clk

图2

(2)设计伪码调制电路

a)实现一个伪码周期调制一个比特数据信息,调制运算为异或,数据信

息为一串规律的010101….序列。

b)调制后数据D in需按照下列要求映射为S out并输出,具体原理见说明(2)

S out={1D in=0

−1D in=1

c)实现要求:顶层模块如图3所示,data_o为调制后的输出信号,位宽为

2位,data_m为调制数据(数据序列为010101…),同时输出对应的伪

码seq_o和伪码周期脉冲seq_p。

clk

rst

图3

(3)设计伪码同步电路

a)利用(2)的输出data_o作为伪码同步电路的输入。

b)提取伪码一个周期码字作为匹配滤波器系数。

c)设计匹配滤波器(可以采用IP核实现),采用全精度输出匹配结果,具

体原理见说明(3)。

d)实现要求:顶层模块如图4所示,mf_o为匹配滤波输出,位宽为6位,

请在modelsim仿真中以十进制(decimal)波形形式显示,seq_p为伪码周

期脉冲。

clk

rst

图4

3.发挥部分

(1)要求可靠获得伪码同步判决结果,并输出原始调制数据

a)当匹配滤波输出的大于设定门限时确定为检测到同步信息,门限可设

置约为相关峰值一半。

b)连续两次检测到相关峰,确定为可靠获得同步信息。

c)利用图5所示状态机实现检测过程。

(2)根据同步判决结果输出解调数据

单次检测结果/同步结果

state0为初始状态

state1为一次检测到相关峰状态

state2为成功检测到伪码同步状态

图5 同步判决状态转移图

发挥部分实现要求:顶层模块如图6所示,要求输出状态机当前状态state_c ,位宽为2位,mf_o 为匹配滤波器的输出,flag_o 代表成功检测伪码同步的标志,data_r 是去除伪码调制后输出的数据比特。

clk

rst

图6

三、 说明

(1) m 序列

m 序列具有良好的自相关特性,一般采用移位寄存和反馈结构实现,本原多

项式y =∑c i x i

n i=0 对应的实现结构如图7所示

图7 m 序列的实现结构

(2) 伪码调制

伪码调制的原理如图8所示,调制数据比特和伪码序列进行异或运算,之后通过映射规律映射为+1或-1信号。

图8 伪码调制原理

(3) 匹配滤波器

伪码的同步是利用伪码的自相关性确定接收伪码和本地伪码间相位是否对齐,可以表示为

c (τ)=∑r(i)s(i −τ)N−1

i=0

(1)

r(i)为接收伪码,s(i −τ)为本地的伪码,当且仅当τ=0时,自相关值c (τ)达到最大值,通过检测自相关峰值获得同步标志。

FIR 滤波器的系统函数可以表示为

y (n )=∑ℎ(i)x(n −i)N−1

i=0

(2)

通过对式(1)和(2)简单分析,可得利用FIR 滤波器结构可以实现伪码的匹配接收。

四、评分标准

实验报告内容:

1. 设计思路概述

2. 总体设计框图及详细说明

3. 时序说明

4. 模块设计框图、引脚说明、相关时序

5. 代码及必要注释

6. 仿真结果

7. 结论

8. 其它需要说明的内容。