SPI协议的Verilog 实现

SPI_I2S

应用笔记487利用MAX II CPLD 实现SPI 至I 2S 的接口引言本应用笔记介绍怎样使用Altera ®MAX ®II CPLD 来实现协议转换,通过串行外设接口(SPI)控制inter-IC 声音(I 2S)总线上的音频设备数据流。

I 2S 和SPI 接口I 2S 是3线半双工串行接口,常用于通过被称为I 2S 总线的3线总线来连接系统中的音频设备。

I 2S 设备和总线使用3条线:串行数据(SDA ),承载了对应于每一个音频通道的两路时分复用音频数据;串行时钟(SCK )和字选择(WS ),控制数字音频数据在I 2S 总线上不同设备之间的传输。

I 2S 系统能够处理和串行时钟分开的串行音频数据,以消除抖动。

SPI 是4线全双工串行接口,常用于连接系统内部和外部的系统处理器(主机)和外设(从机)。

SPI 利用单独的数据输出信号线(主机输出从机输入,即MOSI )和数据输入信号线(主机输入从机输出,即MISO ) 以及时钟(SCLK )和从机选择或者片选信号(CS )来进行通信。

本设计支持SPI 接口主机对其他设备的数据流控制,包括A/D 转换器、数字信号处理器、数字滤波器、音频处理器、PC 多媒体音频转换器等 I 2S 总线设备。

有的嵌入式系统并没有为音频数据通信提供I 2S 接口,但是有SPI 接口。

您可以在和这些接口相似的环境中有效地使用本设计。

利用MAX IICPLD 实现SPI 至I 2S 的接口SPI 主机的桥接接口是SPI 从机,它有四条信号线(CS , SCLK , MISO 和MOSI )。

I 2S 总线一侧接口是I 2S 主机,它有三条信号线(I2S_ SCK , I2S_SDA 和I2S_WS )。

CLK 是主机时钟,位于I 2S 主机外部。

图1所示为采用 MAX II CPLD 来实现SPI 至I 2S 接口。

2007年12月,1.0版图1.利用MAX II CPLD实现SPI至I2S接口本设计提供协议转换功能,通过SPI 接口(更常用的4线串行接口,用于连接串行外设接口和微处理器或者主机)来控制I2S 总线(带宽相对较窄的协议,用于连接系统中的数字音频设备)上音频设备的数据流。

基于UVM的APB-SPI验证平台的设计方法与实现技术

基于UVM的APB-SPI验证平台的设计方法与实现技术基于UVM的APB-SPI验证平台的设计方法与实现技术一、引言随着数字集成电路的高度发展,可编程逻辑设备(PLD)在各种电子设备中的应用不断增加。

为确保这些 PLD 设备的功能正确性和稳定性,需要进行严格的验证工作。

本文将介绍一种基于Universal Verification Methodology(UVM)的Advanced Peripheral Bus(APB)与Serial Peripheral Interface(SPI)的验证平台设计方法与实现技术。

二、APB和SPI协议简介APB和SPI是两种常用的串行通信协议,用于连接微处理器和外设。

APB是一种低功耗和高性能的总线协议,它通过统一的地址和数据线,实现了对外围设备的读写操作。

SPI是一种简单的同步串行通信协议,每个外围设备都有一个片选线,可以通过与微处理器交互进行数据传输。

三、UVM测试平台设计方法1. 环境架构设计在设计UVM测试平台时,需要考虑到测试环境和被测设计的互动。

首先,创建一个环境类来模拟测试环境,包括实例化被测设计以及其他必要的外设模块。

然后,使用相关接口将测试环境与被测设计连接起来。

2. 驱动和监控器设计驱动和监控器是验证平台中的核心组件。

驱动负责向被测设计发送有效的数据包,并处理相关时序。

监控器负责监听被测设计发送的数据包,并进行校验。

3. 配置和注入错误为了确保被测设计的稳定性和鲁棒性,需要在测试平台中配置和注入错误。

这可以通过配置寄存器值或注入故障来实现。

例如,可以向被测设计发送错误的数据包,观察其响应是否正确。

四、UVM实现技术1. 类和对象UVM基于SystemVerilog语言实现,通过使用类和对象来描述和组织验证平台中的各个组件。

类是UVM中最基本的单位,对象是类的实例。

2. UVM构建块UVM提供了一系列的构建块,用于创建而不是定义测试平台的各个组件。

[FPGA][Verilog][SPI]简单的读写SPI接口EEPROM-93C46程序

![[FPGA][Verilog][SPI]简单的读写SPI接口EEPROM-93C46程序](https://img.taocdn.com/s3/m/1221e485ec3a87c24028c428.png)

Write19: begin mo <= 0; cs <= 0; end

Read0: cs <= 0; Read1://110+add(7bit) begin cs <= 1; mo <= 1; end Read2: mo <= 1; Read3: mo <= 0;//110 Read4: mo <= 0; Read5: mo <= 1; Read6: mo <= 1; Read7: mo <= 1; Read8: mo <= 1; Read9: mo <= 1; Read10: mo <= 1; Read11: begin mo <= 0; led[7] <= mi; end Read12: led[7] <= mi; Read13: led[6] <= mi; Read14: led[5] <= mi; Read15:

从开始读数据手册,到研究时序,到编写 Verilog 程序,到仿真调试时序,整整 花了有 3-4 天时间。 最后时序已经完全正确, 却读不出任何数据,经过一个晚上的排查才发现是开发 板上的 DI DO SK CS 标号标错了,泪奔~~ 本来我想写一个完整的 SPI 接口出来,想了几天都没有头绪,最后还是写了一个 最简单的写数据读数据的小程序,如果做成接口也勉强可以用。 程序的功能很简单,往地址 0111111 的位置写了 00001111 的数据,地址都还没 有做成接口,固定在程序里面的。 具体用了一个状态机共 53 个状态,每一个状态都是一个 SCK 信号的处理,当然 有分为三个大状态,分别为 ENWR、WRITE、READ 93C46 要首先写 ENWR 信号才能写入数据,具体还得研究数据手册 通过这次 93C46 和上次写 18B20 的经历, 我感觉到数据手册的确是相当的重要的, 需要仔细推敲,分析每一个时序图!下次要做 I2C 接口的 24C02,1、2、3 线就 都学过拉。 当然作为初学者程序是写的那是超级的烂,欢迎拍砖

FPGA实现SPI

FPGA实现SPIFPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以实现不同的数字电路功能。

SPI(Serial Peripheral Interface)是一种同步串行通信协议,常用于连接外围设备和主控制器。

在本文中,将介绍如何使用FPGA实现SPI。

1.确定硬件资源:首先,需要确定FPGA中可用的IO资源。

SPI需要至少4个IO口,分别是主设备的时钟引脚(SCK),主设备输出的数据引脚(MOSI),主设备输入的数据引脚(MISO)和片选引脚(SS)。

根据所用的FPGA型号,可以查找对应的引脚定义。

2.确定SPI时序:SPI的时序是非常重要的,不同设备可能有不同的时序规范。

一般情况下,SPI的时序包括时钟下降沿数据采样、时钟上升沿数据输出等。

SPI的时序图可以在设备的数据手册中找到。

3. 编写SPI控制器:SPI控制器可以用硬件描述语言如VHDL或Verilog编写。

控制器的功能包括生成时钟、控制数据的发送和接收、以及处理片选信号。

a.时钟生成:SPI通信需要一个时钟信号来驱动数据的传输。

可以通过计数器模块来生成控制器的时钟信号。

计数器的频率一般是SPI时钟频率的若干倍。

b. 数据发送:对于主设备(Master),要发送数据给外设,可以使用移位寄存器(Shift Register)来存储要发送的数据。

可以使用计数器生成移位寄存器的时钟信号,通过串行输入数据,并在时钟的上升沿时将数据发送到MOSI引脚。

c.数据接收:对于主设备,要接收外设发送的数据,可以使用另一个移位寄存器来接收MISO引脚传输的数据。

可以使用计数器生成移位寄存器的时钟信号,通过MISO引脚接收数据,并在时钟的下降沿时将数据存储到接收寄存器。

d.片选控制:SPI通信需要一个片选信号来选择要与主设备通信的外设。

可以通过一个时序控制器实现片选信号的生成。

在与一些外设通信时,使能片选信号,否则禁用片选信号。

【CPLD+Verilog】CPLD实现SPI接口

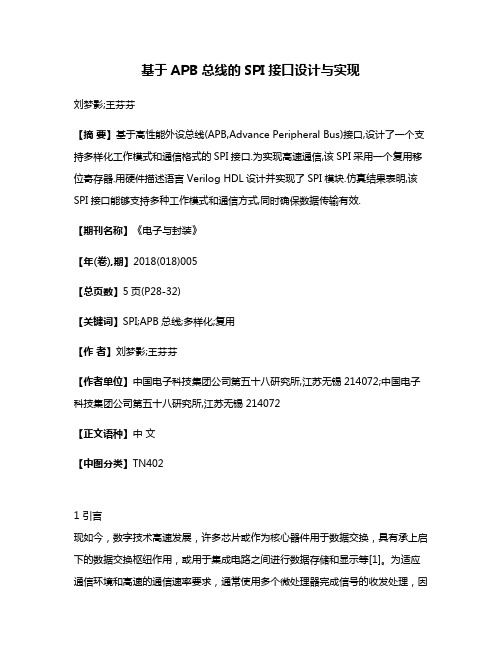

CPLD 实现SPI 接口1 实现原理CPLD 实现SPI 接口模块,通过对寄存器的操作,实现SPI 接口功能,对外部SPI 设备进行访问。

CPLD 内部SPI 模块逻辑框图如下所示。

CLK_DIVRX_SHIFT_REGSTATUS LOGICspi_clkspi_cs spi_dospi_tx_data_we_pulsereset_n spi_tx_data spi_rx_data spi_clk_div spi_rx_data_rd_pulsespi_dispi_tx_data_we_busy spi_rx_data_rd_ready spi_data_tx_we_overflow spi_data_rx_rd_nop spi_data_rx_rd_overtime cpld_clkCONTROL LOGICCOUNT LOGIC通过对主时钟分频,得到的SPI 接口时钟,其分频值可通过spi_clk_div 值设定,最小为6分频,当设置分频值低于6分频时,默认6分频。

SPI 接口的片选信号spi_cs 在写数据传输寄存器spi_tx_data 时,通过自动产生写脉冲spi_tx_data_we_pulse ,逻辑综合生成。

spi_rx_data_rd_pulse 在读取接收数据spi_rx_data 的数据时自动产生。

spi_di 和spi_do 分别由数据移位寄存器通过数据移位产生和接收。

spi_clk 由内部分频时钟和传输状态逻辑综合输出,在有数据时输出,无数据时保持高电平。

状态逻辑spi_tx_data_we_busy 信号分别表示数据正在传输,无法写入spi_tx_data 寄存器; spi_rx_data_rd_ready 信号表示数据接收完成,可读取spi_rx_data 寄存器的值。

错误状态逻辑spi_data_tx_we_overflow 信号表示在spi_tx_data 寄存器中写入了待传输值后,还未传输就又写入新的传输数据,表示写数据溢出。

基于APB总线的SPI接口设计与实现

基于APB总线的SPI接口设计与实现刘梦影;王芬芬【摘要】基于高性能外设总线(APB,Advance Peripheral Bus)接口,设计了一个支持多样化工作模式和通信格式的SPI接口.为实现高速通信,该SPI采用一个复用移位寄存器.用硬件描述语言Verilog HDL设计并实现了SPI模块.仿真结果表明,该SPI接口能够支持多种工作模式和通信方式,同时确保数据传输有效.【期刊名称】《电子与封装》【年(卷),期】2018(018)005【总页数】5页(P28-32)【关键词】SPI;APB总线;多样化;复用【作者】刘梦影;王芬芬【作者单位】中国电子科技集团公司第五十八研究所,江苏无锡214072;中国电子科技集团公司第五十八研究所,江苏无锡214072【正文语种】中文【中图分类】TN4021 引言现如今,数字技术高速发展,许多芯片或作为核心器件用于数据交换,具有承上启下的数据交换枢纽作用,或用于集成电路之间进行数据存储和显示等[1]。

为适应通信环境和高速的通信速率要求,通常使用多个微处理器完成信号的收发处理,因此需要一种高效的数据总线快速有效地完成它们之间大量的数据交换。

因此,设计一个高效快速的通信接口是至关重要的[2]。

串行外围设备接口SPI总线技术是Motorola公司推出的一种微处理器、微控制器以及外设间的串行数据接口标准[3],主要用于扩展外设和进行数据交换[4]。

SPI接口连线简单,配置灵活,传输效率高[5],因此应用广泛,很多器件如E2PROM、FLASH、实时时钟、A/D转换器等都用到了SPI接口[6]。

郭艾华[7]设计了一种可灵活配置为主/从设备,设置传输速率,支持DMA功能并适用于多种时钟模式的SPI协议IP核,但从机片选信号只可由主机输出,存在一定的局限性。

李琦、贺明等[8]以微处理器S3C2440和嵌入式Linux操作系统组成的嵌入式系统作为开发平台,设计了一款基于ARM嵌入式系统的SPI驱动程序,该设计存在两组8位移位寄存器,支持传输8位数据,但未有效地运用硬件资源。

SPI总线接口的verilog的实现

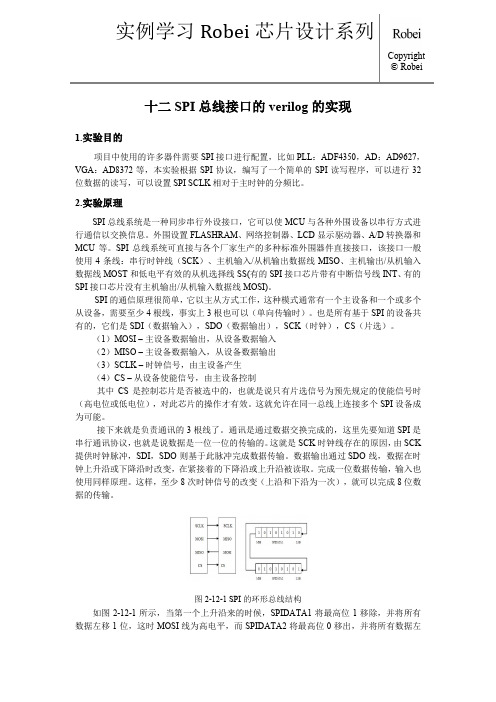

十二SPI总线接口的verilog的实现1.实验目的项目中使用的许多器件需要SPI接口进行配置,比如PLL:ADF4350,AD:AD9627,VGA:AD8372等,本实验根据SPI协议,编写了一个简单的SPI读写程序,可以进行32位数据的读写,可以设置SPI SCLK相对于主时钟的分频比。

2.实验原理SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。

外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。

SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOST和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。

SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。

也是所有基于SPI的设备共有的,它们是SDI(数据输入),SDO(数据输出),SCK(时钟),CS(片选)。

(1)MOSI –主设备数据输出,从设备数据输入(2)MISO –主设备数据输入,从设备数据输出(3)SCLK –时钟信号,由主设备产生(4)CS –从设备使能信号,由主设备控制其中CS是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时(高电位或低电位),对此芯片的操作才有效。

这就允许在同一总线上连接多个SPI设备成为可能。

接下来就是负责通讯的3根线了。

通讯是通过数据交换完成的,这里先要知道SPI是串行通讯协议,也就是说数据是一位一位的传输的。

这就是SCK时钟线存在的原因,由SCK 提供时钟脉冲,SDI,SDO则基于此脉冲完成数据传输。

数据输出通过 SDO线,数据在时钟上升沿或下降沿时改变,在紧接着的下降沿或上升沿被读取。

Verilog的spi总线

SPI串行总线接口的Verilog实现摘要:集成电路设计越来越向系统级的方向发展,并且越来越强调模块化的设计。

SPI(Serial Peripheral Bus)总线是Motorola公司提出的一个同步串行外设接口,容许CPU 与各种外围接口器件以串行方式进行通信、交换信息。

本文简述了SPI总线的特点,介绍了其4条信号线,SPI串行总线接口的典型应用。

重点描述了SPI串行总线接口在一款802.11b芯片中的位置,及该接口作为基带和射频的通讯接口所完成的功能,并给出了用硬件描述语言Verilog HDL 实现该接口的部分程序。

该实现已经在Modelsim 中完成了仿真, 并经过了FPGA 验证, 最后给出了仿真和验证的结果。

在SOC设计中,利用EDA 工具设计芯片实现系统功能已经成为支撑电子设计的通用平台.并逐步向支持系统级的设计方向发展。

而且,在设计过程中,越来越强调模块化设计。

SPI总线是Motorola公司提出的一个同步串行外设接口,具有接口线少、通讯效率高等特点。

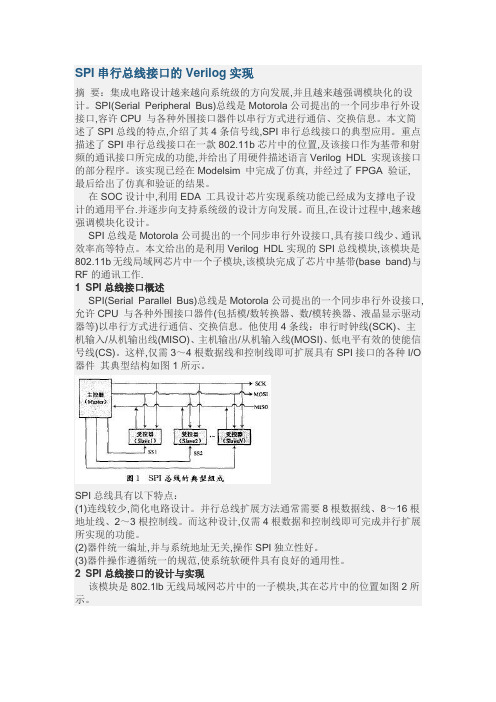

本文给出的是利用Verilog HDL实现的SPI总线模块,该模块是802.11b无线局域网芯片中一个子模块,该模块完成了芯片中基带(base band)与RF的通讯工作.1 SPI总线接口概述SPI(Serial Parallel Bus)总线是Motorola公司提出的一个同步串行外设接口,允许CPU 与各种外围接口器件(包括模/数转换器、数/模转换器、液晶显示驱动器等)以串行方式进行通信、交换信息。

他使用4条线:串行时钟线(SCK)、主机输入/从机输出线(MISO)、主机输出/从机输入线(MOSI)、低电平有效的使能信号线(CS)。

这样,仅需3~4根数据线和控制线即可扩展具有SPI接口的各种I/O 器件其典型结构如图1所示。

SPI总线具有以下特点:(1)连线较少,简化电路设计。

并行总线扩展方法通常需要8根数据线、8~16根地址线、2~3根控制线。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

// //接收数据存入 out_data

6

begin case(addr) 1'b0: begin in_buffer = in_data; busy = 1'b1; end 转入工作状态 1'b1: begin busy = 1'b0;end endcase end end else begin if(cs) begin clkcount = clkcount + 1'b1; if(clkcount >= 8'b10) // 控制 SCK 周期 begin clkcount = 0; if((count % 2) == 0) //待发数据存入缓存区,

DataPort[5]-DataPort[0] : busy、sdo 、addr、cs、wr、rd DataPort[21]-DataPort[14] :待发送 8bit 数据 DataPort[13]-DataPort[6] : 接收的 8bit 数据

3

� 总结

完成时间:12.4--12.12 前期:该阶段主要是熟悉 SPI 工作原理,进一步掌握和认识 SPI 通信协议。Chipscore 的使 用之前未曾接触, 在这一阶段, 我先通过简单编程结合开发板抓取数据进行分析达到 对其的基本掌握。 中期:在熟悉 SPI 的工作原理之后,开始尝试编写代码。写了两三次代码,效果均不理想, 很多问题在编写代码的时候没有考虑清楚,导致到了仿真阶段结果与预期有所差距, 且代码冗长复杂。参考了一些资料,效果也不是很好,特别是数据传输暂停部分, 很 多都省略了。不过借鉴别人写的代码也让我收获了不少编写的经验,有些情况下, 运 用不同的逻辑思维可以让代码更简洁、 更具有健壮性。 当然期间也遇到了一些自己无 法解决的问题,非常感谢福星学长耐心的指导,让我学到了不少知识和经验。 后期:该阶段主要是对代码进行再修改、波形仿真以及抓数据调试。 问题及分析: 小问题遇到不少,不过大多都通过 error 的提示,或者上网搜索,找到了问题的原因, 并予以解决。也有软件上的原因,比如:第一次装 ISE 的时候可能没有安装好,上板调试的 时候,cable 不能识别。经过测试分析发现 ISE 里的 drive 没有装上。考虑到这样一个问题的 出现可能还会附带有一些软件上的漏洞,重装了一遍 ISE,问题解决。 使用 chipscope 的时候,芯片配置不对连接失败,查阅该电路板的资料,重新配置,问 题解决。在 chipscope 里面有些触发信号找不到,经分析是被优化了,通过简单修改代码避 免它被优化后,问题解决。运行 chipscope 后发现 waveform 始终没反应,经过一番分析, 认 为时钟线的引脚配置有问题,重换一个时钟信号线 I/O 引脚,问题解决。解决后发现抓取的 波形没有明显的高低跳变,经分析可能是参考时钟选取不对,重选后问题解决。

� SPI—MOSI代码 (见附录)

� 仿真及分析

1

数据发送:

图 1、数据发送 如图 1 所示,传输时钟 SCK 由 busy 信号控制,在 busy 信号有效期间产生八个周期的 主从设备交换数据时钟信号,在每一个周期内完成一位数据的发送和接收。测试中,待发送 数据为 10101001 。经过数据线 SDO 发送后,在 SCK 的第一个跳边沿进行数据采样,在每 个 sck 下降沿完成一位数据的交换。由上图可知,在一个 busy 信号有效期内,sdo 发送的数 据为 10101001,与待发送数据一致。

2

ቤተ መጻሕፍቲ ባይዱ

数据接收:

图 2、数据接收 数据接收与数据发送使用同一个时钟信号 SCK 和片选信号 CS。其工作情况大致如下: 在 每个 SCK 时钟的上升沿对接收数据进行采样。由图 2 可知,在一个 busy 信号使能阶段, 采 到的数据为 10110111,即十进制 183。在 busy 信号关闭使能后,只有片选使能且处于允许 读状态,接收到的数据才会被存储,否则丢弃。 Chipscope 数据抓取

SPI 通信

� 原理

Spi 接口是一种外围串行接口,主要由四根线组成:SDI(数据输入) ,SDO(数据输出) , SCK (时钟) ,CS (片选) 。 (1)SDO主机输出 / 从机输入。 (2)SDI主机输入 / 从机输出 。 (3)SCK – 时钟信号,由主设备产生。 (4)CS – 从设备使能信号,由主设备控制。 在一个基于 SPI的设备中,至少有一个主控设备。与普通的串行通讯不同,普通的串行 通讯一次连续传送至少8位数据,而SPI 允许数据一位一位的传送,甚至允许暂停,因为SPI 的数据输入和输出线独立,所以允许同时完成数据的输入和输出。在点对点的通信中, SPI 接口不需要进行寻址操作,且为全双工通信,工作简单高效。然而SPI 接口也有缺点:没有 指定的流控制,没有应答机制确认是否接收到数据。 SPI通讯是通过数据交换完成的。在主机提供的时钟脉冲 SCK 下,SDI,SDO完成数据传 输。数据输出通过 SDO线,在 SCK 时钟上升沿或下降沿时改变,在紧接着的下降沿或上升 沿被从机读取,完成一位数据传输。输入情况同理。因此,在至少 8次时钟信号的改变(上 沿和下沿为一次) ,可以完成8位数据的传输。 SPI 总线有四种工作方式可以选择,根据外设工作要求,其输出串行同步时钟极性和相 位可以进行配置,时钟极性(CPOL )对传输协议没有重大的影响。如果 CPOL=0,串行同 步时钟的空闲状态为低电平;如果CPOL=1 ,串行同步时钟的空闲状态为高电平。时钟相位 (CPHA )能够配置用于选择两种不同的传输协议之一进行数据传输。如果 CPHA=0,在串 行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的 第二个跳变沿(上升或下降)数据被采样。SPI主\从设备时钟相位和极性应该一致。本次实 践采用第一种工作方式,具体情况将在之后的仿真波形中分析介绍。

// 发送数据

begin sdo_buffer = in_buffer[8]; in_buffer = in_buffer << 1; end if(count > 0 && count < 17) 条件满足,信号反转一次 begin sck_buffer = ~sck_buffer; end count = count + 1'b1; if(count > 17) begin count = 0; busy = 1'b0; end end end end end always@(posedge sck_buffer) begin out_buffer = out_buffer << 1; out_buffer[1] = sdi; end endmodule // 在未达到 8 个 sck 周期时,每次触发

reg[12:0] clk_cnt; reg[size:1] in_data=8'b10101001;

5

parameter size=8; parameter para=6400; parameter para_half=3200;

assign data=out_data; assign sck = sck_buffer; assign sdo = sdo_buffer; assign spi_bps=spi_bps_reg; ////////////////////////////////////////////////////////////////////////////////// ////////////// ////////////////////////////////////// ///////////// 分频模块 ////////////////////////////////////// //////////// ////////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// always@(posedge clk) begin if((clk_cnt>=0)&&(clk_cnt<para_half)) begin clk_cnt<=clk_cnt+1'b1; spi_bps_reg<=1'b0; end else if((clk_cnt>=para_half)&&(clk_cnt<para)) begin clk_cnt<=clk_cnt+1'b1; spi_bps_reg<=1'b1; end else clk_cnt<=13'd0; end ////////////////////////////////////////////////////////////////////////////////// ////////////// ////////////////////////////////////// ///////////// 发送接收模块 ////////////////////////////////////// //////////// ////////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// always@(cs or rd or busy) begin if(!busy && cs && rd) begin out_data = out_buffer; end else begin out_data = 8'b0;end end always@(posedge spi_bps) begin if(!busy) begin if(cs && wr) // 空闲状态 //片选使能且处于写状态