混合信号集成电路设计大作业2016

专用集成电路设计大作业

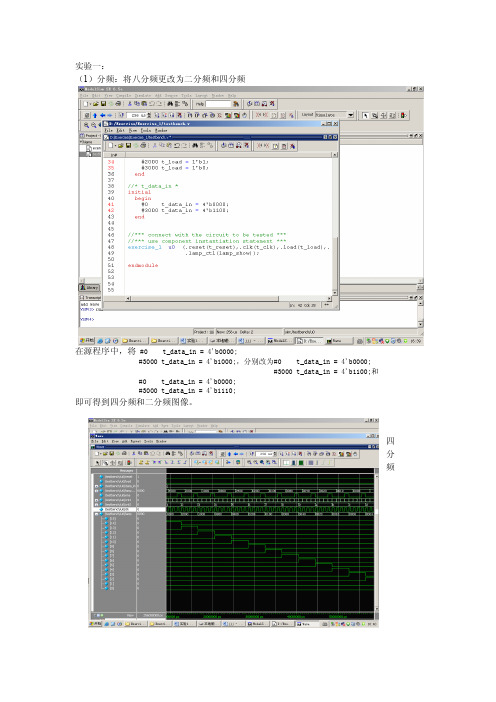

实验一:(1)分频:将八分频更改为二分频和四分频在源程序中,将#0t_data_in=4'b0000;#3000t_data_in=4'b1000;,分别改为#0t_data_in=4'b0000;#3000t_data_in=4'b1100;和#0t_data_in=4'b0000;#3000t_data_in=4'b1110;即可得到四分频和二分频图像。

四分频二分频(2)反序:改变电路使彩灯变成逆时针旋转方式:源程序改动将源程序4'b0000:lamp=16'b0000_0000_0000_0001;4'b0001:lamp=16'b0000_0000_0000_0010;4'b0010:lamp=16'b0000_0000_0000_0100;4'b0011:lamp=16'b0000_0000_0000_1000;4'b0100:lamp=16'b0000_0000_0001_0000;4'b0101:lamp=16'b0000_0000_0010_0000;4'b0110:lamp=16'b0000_0000_0100_0000;4'b0111:lamp=16'b0000_0000_1000_0000;4'b1000:lamp=16'b0000_0001_0000_0000;4'b1001:lamp=16'b0000_0010_0000_0000;4'b1010:lamp=16'b0000_0100_0000_0000;4'b1011:lamp=16'b0000_1000_0000_0000;4'b1100:lamp=16'b0001_0000_0000_0000;4'b1101:lamp=16'b0010_0000_0000_0000;4'b1110:lamp=16'b0100_0000_0000_0000;4'b1111:lamp=16'b1000_0000_0000_0000;default:lamp=16'b0000_0000_0000_0000;首尾相对应语句依次调换位置,即可得到新的源程序,执行后可观测到新的亮灯顺序为反序。

数模混合信号电路设计-第一讲

华侨大学IC设计中心

建立层次文件

1.建立config文件 2.链接顶层文件

Mixed Signal Processing & RF/Analog IC TRx architectures Signal IC Digital ASIC

Multi-band Multimode Antenna Interface

AD

90º

AD

Baseband processing

DA

TRx calibration

数模混合信号仿真华侨大学IC设计中心

3.仿真提速

A:用作信 号发生器。 仿真的时候,需要不少的激励信号,而且有着严格的时序关 系,要是用pulse电源或是别的什么电源来做的话,可要累死 人的。用verilog写模块的foundational,就 可以比较方便快 捷的构成一个信号发生器。

B:节约模拟的时间。 对于一些成熟的已经知道电路输入输出特性的电路,可以用 verilog写出其特性,这样的话,模拟的时间可以大大的缩短。 当然,还有就是verilog 的老本家--数字电路,也可以用 verilog写出foundational,节约模拟的时间。

Ch.1概述5

华侨大学IC设计中心

SIP与SOC是两项平行发展的系统集成技术, 它们都顺应了电子产品高性能、多功能、小型 化、轻量化和高可靠性的发展趋势。从发展的 历程来看,SOC与SIP是极为相似的,两者均 希望将逻辑组件、数字、模拟、无源器件整合 在一个单元中。然而就发展方向而言,两者有 很大的不同:SOC是从设计的角度出发,目的 是将一个系统整合到一块IC芯片上去;而SIP 则是由封装的角度出发,将不同功能的芯片整 合于一个电子封装结构体内。

symbo

低功耗混合信号集成电路设计

低功耗混合信号集成电路设计随着科学技术的发展,电子元器件越来越小,越来越先进。

人们的生活离不开电子元器件,无论是家电、汽车、手机、电脑等等设备都需要电子元器件。

而其中最重要的就是集成电路,而低功耗混合信号集成电路是其中的重要一环。

低功耗混合信号集成电路是指控制、通信、计算等应用领域中需要芯片实现的混合信号电路,它主要用于低功耗的数字信号处理和模拟信号处理。

低功耗混合信号集成电路广泛应用于电力、通信、信息处理、汽车、仪表、医疗、消费电子等领域。

低功耗混合信号集成电路的设计需要兼顾模拟信号和数字信号的处理,因此需要有深厚的算法功底和很好的硬件设计经验。

同时,在设计中需要考虑功耗问题,使用功耗低的设计方案才能更好地应用于各种领域,并且可以降低成本和保证可靠性。

在进行低功耗混合信号集成电路设计时,需要注意以下几点:1. 优化设计结构在进行低功耗混合信号集成电路的设计时,需要从整体结构优化入手,对于电路的架构、电路的功能和功耗消耗等方面进行优化,使用最先进的工艺和技术将功耗控制在最小的范围内。

2. 优化电路设计在进行低功耗混合信号集成电路的设计时,需要进行电路级的优化,比如,选择合适的器件和元器件,用最小的电源电压进行电路实现,灵活运用自适应电源管理等技术,以实现低功耗设计。

3. 优化模拟电路和数字电路的交互在低功耗混合信号集成电路的设计中,模拟电路和数字电路都要得到很好的处理。

因此,需要对控制、通信、计算等应用领域的信号的处理及电路结构等多方面做出精确的分析和细致的考虑,以此保证数字电路和模拟电路的交互,实现最小功耗的收益。

总之,低功耗混合信号集成电路的设计需要专业的技术、厚实的经验和细心的态度,需要在电路、器件、工艺等多个方面进行综合考虑和充分优化,才能在实现高质量、高可靠性、低功耗等方面取得很好的效果。

混合集成电路中的数字信号处理器设计

混合集成电路中的数字信号处理器设计混合集成电路(HIC,Hybrid Integrated Circuit)是指将不同性质的电子元器件或半导体器件集成在同一个芯片上的集成电路。

数字信号处理器(DSP,Digital Signal Processor)是以处理数字信号为主要任务的计算机芯片。

在现代电子设备中,混合集成电路中的数字信号处理器扮演着重要的角色,它广泛应用于音频和视频处理、图像处理、通信系统等领域。

数字信号处理器的设计在混合集成电路中具有一定的特殊性和挑战性。

本文将探讨数字信号处理器设计中的关键要素和流程,并对其应用进行简要的介绍。

首先,数字信号处理器设计的一个重要环节是架构设计。

在混合集成电路中,考虑到面积和功耗等因素,需要选择合适的架构来满足设计要求。

在架构设计中,可以采用多种不同的指令集(如RISC、CISC等)、数据通路结构以及存储器层次结构,以达到设计的性能和功耗指标。

其次,算法设计是数字信号处理器设计的核心。

根据所需的信号处理需求,需要选择合适的算法来实现相应的功能。

从离散傅立叶变换(DFT)、快速傅立叶变换(FFT)到数字滤波器设计等,都是数字信号处理中常见的算法。

在混合集成电路中设计数字信号处理器时,需要对算法进行适当的优化和改进,以满足资源限制和性能要求。

第三,运算单元设计是数字信号处理器设计中的关键环节。

运算单元包括算术逻辑单元(ALU)和乘法器等。

在混合集成电路中,需要考虑如何有效地利用有限的面积资源来设计高性能的运算单元。

这通常涉及到多级流水线、数据通路划分以及频率调度等技术。

通过合理的运算单元设计,可以实现较高的计算性能和较低的功耗。

此外,存储器设计也是数字信号处理器设计中的一个重要方面。

存储器包括指令存储器和数据存储器,用于存储运行程序和中间结果。

在混合集成电路中,存储器的容量和访问速度等因素是需要考虑的关键因素。

在设计过程中,可以采用多级缓存、片上存储器以及外部存储器等策略来满足存储器需求。

超大规模集成电路第八次作业2016秋,段成华

Assignment 81.Access relevant reference books or technical data books and give accuratedefinitions for the following timing parameters:(1)design entity,(2)signal driver,(3)transaction,(4)event,(5)time queue,(6)delta delay,(7)simulation time,(8)simulation cycle,(9)inertial time,(10)transport time.(1)design entity: In VHDL a given logic circuit represented as a design entity. Adesign entity, in return , consists of two different types of description: the interface description and one or more architectural bodies. The interface description declares the entity and describes its inputs and outputs.(2)signal driver: If a process contains one or more signal assignment statementthat schedule future values for some signal X, the VHDL simulator creates a single value holder called a signal driver.(3)transaction:A pair consisting of a value and time. The value part represents afuture value of the driver; the time part represents the time at which the value part becomes the current value of driver.(4)event: It’s a kind of signal property and presents signal jump. Such asif(clk'event and clk='1).(5)time queue: It’s used to keep some signal transactions in the simulator. Timequeue entries are represented as a two-tuple of the form(SN,V), where SN is a signal name and V is the value the signal is scheduled to assume at the scheduled time. Each time queue entry is called a signal transaction.(6)delta delay: A period of time greater than 0, but less than any standard time unitno number of delta delay added together can cause simulation time to advance.(7)simulation time: The elapsed time in standard time units during simulation.(8)simulation cycle: Every time simulation time advances, a simulation cycleoccurs, which we now define more formally. The execution of a model consists of an initialization phase followed by the repetitive execution of processes in the process network. Each repetition is said to be a simulation cycle.(9)inertial time: Example: Z <= I after 10ns; The signal propagation will takeplace if and only if input I persists at a given level for 10ns-the amount of time specified in the after clause.(10)transport time: Z <= transport I after 10ns; All changes on I will propagate toZ, regardless of how long the value of I stays at the new level.2.Construct VHDL models for 74-139 dual 2-to-4-line decoders using threedescription types, i.e., behavioral, dataflow and structural descriptions. Synthesize and simulate these models respectively in the environment of Xilinx ISE with the ModelSim simulator integrated. When simulating these models, test vector(s) are required to stimulate the units under test (UUT). Reasonable test vectors are designed and created by your own as sources added to your VHDL project.Logic schematic of 74-139:Function table of one decoder of 74-139:(1-- Company:-- Engineer:-- Create Date: 21:14:09 12/02/2016-- Design Name:-- Module Name: deceoder_beh - Behavioral -- Project Name:-- Target Devices:-- Tool versions:-- Description:-- Dependencies:-- Revision:-- Revision 0.01 - File Created-- Additional Comments:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity deceoder_beh isPort ( G1,G2 : in std_logic;A : in std_logic_vector(1 downto 0);B : in std_logic_vector(1 downto 0);Y1 : out std_logic_vector(3 downto 0);Y2 : out std_logic_vector(3 downto 0));end deceoder_beh;architecture Behavioral of deceoder_beh isbeginde1: process (A, G1)beginif G1 = '1' theny1 <= "1111"; -- sequential statementelsecase A iswhen "00" => Y1 <= "1110";when "01" => Y1 <= "1101";when "10" => Y1 <= "1011";when "11" => Y1 <= "0111";when others => Y1 <= "1111";end case;end if;end process;de2: process (B, G2)beginif G2 = '1' thenY2 <= "1111"; -- sequential statementelsecase B iswhen "00" => Y2 <= "1110";when "01" => Y2 <= "1101";when "10" => Y2 <= "1011";when "11" => Y2 <= "0111";when others => Y2 <= "1111";end case;end if;end process;end Behavioral;TestBench代码如下:-- Company:-- Engineer:-- Create Date: 22:25:59 12/02/2016-- Design Name:-- Module Name: D:/ISE11.1_example/decoder/deconder_beh_tb.vhd-- Project Name: decoder-- Target Device:-- Tool versions:-- Description:-- VHDL Test Bench Created by ISE for module: deceoder_beh-- Dependencies:-- Revision:-- Revision 0.01 - File Created-- Additional Comments:-- Notes:-- This testbench has been automatically generated using types std_logic and -- std_logic_vector for the ports of the unit under test. Xilinx recommends-- that these types always be used for the top-level I/O of a design in order-- to guarantee that the testbench will bind correctly to the post-implementation -- simulation model.LIBRARY ieee;USE ieee.std_logic_1164.ALL;USE ieee.std_logic_unsigned.all;USE ieee.numeric_std.ALL;ENTITY deconder_beh_tb ISEND deconder_beh_tb;ARCHITECTURE behavior OF deconder_beh_tb IS-- Component Declaration for the Unit Under Test (UUT)COMPONENT deceoder_behPORT(G1 : IN std_logic;G2 : IN std_logic;A : IN std_logic_vector(1 downto 0);B : IN std_logic_vector(1 downto 0);Y1 : OUT std_logic_vector(3 downto 0);Y2 : OUT std_logic_vector(3 downto 0));END COMPONENT;--Inputssignal G1 : std_logic := '0';signal G2 : std_logic := '0';signal A : std_logic_vector(1 downto 0) := (others => '0');signal B : std_logic_vector(1 downto 0) := (others => '0');--Outputssignal Y1 : std_logic_vector(3 downto 0);signal Y2 : std_logic_vector(3 downto 0);BEGIN-- Instantiate the Unit Under Test (UUT)uut: deceoder_beh PORT MAP (G1 => G1,G2 => G2,A => A,B => B,Y1 => Y1,Y2 => Y2);-- Stimulus processstim_proc: processbegin-- insert stimulus hereG1 <='1';WAIT FOR 100 ns;G1 <='0';A <= "00";B <= "00";-- --------------------------------------- ------------- Current Time: 200nsWAIT FOR 100 ns;G1 <='0';A <= "01";B <= "01";-- --------------------------------------- ------------- Current Time: 300nsWAIT FOR 100 ns;G1 <='0';A <= "10";B <= "10";-- --------------------------------------- ------------- Current Time: 400nsWAIT FOR 100 ns;G1 <='0';a <= "11";b <= "11";WAIT FOR 100 ns;end process;END;测试波形如下:可以看到当G1=0和G2=0可以正常的译码,当G1=1和G2=1,则Y1和Y2都输出”1111”。

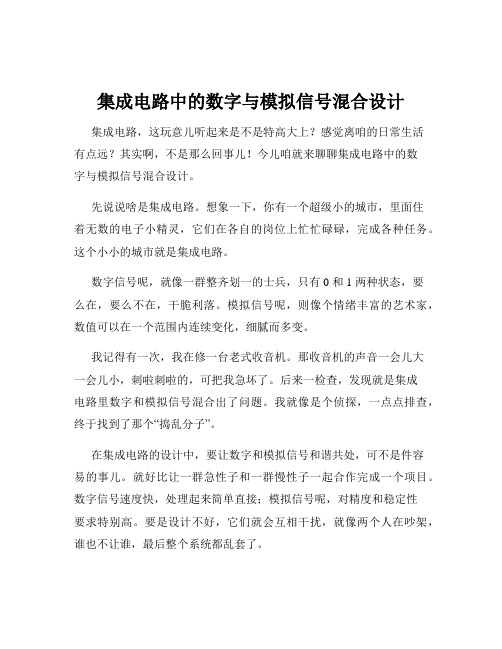

集成电路中的数字与模拟信号混合设计

集成电路中的数字与模拟信号混合设计集成电路,这玩意儿听起来是不是特高大上?感觉离咱的日常生活有点远?其实啊,不是那么回事儿!今儿咱就来聊聊集成电路中的数字与模拟信号混合设计。

先说说啥是集成电路。

想象一下,你有一个超级小的城市,里面住着无数的电子小精灵,它们在各自的岗位上忙忙碌碌,完成各种任务。

这个小小的城市就是集成电路。

数字信号呢,就像一群整齐划一的士兵,只有 0 和 1 两种状态,要么在,要么不在,干脆利落。

模拟信号呢,则像个情绪丰富的艺术家,数值可以在一个范围内连续变化,细腻而多变。

我记得有一次,我在修一台老式收音机。

那收音机的声音一会儿大一会儿小,刺啦刺啦的,可把我急坏了。

后来一检查,发现就是集成电路里数字和模拟信号混合出了问题。

我就像是个侦探,一点点排查,终于找到了那个“捣乱分子”。

在集成电路的设计中,要让数字和模拟信号和谐共处,可不是件容易的事儿。

就好比让一群急性子和一群慢性子一起合作完成一个项目。

数字信号速度快,处理起来简单直接;模拟信号呢,对精度和稳定性要求特别高。

要是设计不好,它们就会互相干扰,就像两个人在吵架,谁也不让谁,最后整个系统都乱套了。

比如说,在电源设计上,数字部分和模拟部分就得分别对待。

数字部分像个精力旺盛的小伙子,消耗能量大,电源得足够稳定和强大;模拟部分则像个娇弱的小姑娘,对电源的噪声特别敏感,稍有风吹草动,就会“发脾气”。

布线也是个大问题。

数字信号的线路就像高速公路,宽敞笔直;模拟信号的线路则像山间小道,弯曲细腻。

要是不小心把它们混在一起,那可就像是在高速公路上开着拖拉机,或者在山间小道上跑赛车,准得出乱子。

还有一个特别重要的事儿,就是屏蔽。

得给模拟信号穿上“防护服”,免得被数字信号这个“大嗓门”给吵到。

这就好比你在一个嘈杂的市场里,想要安静地看书,就得给自己围个小空间,挡住外面的吵闹声。

在实际的设计中,工程师们得像个经验丰富的大厨,把数字和模拟这两种不同的“食材”巧妙地搭配在一起,做出一道美味的“电子大餐”。

模拟与数字混合信号集成电路设计方法与技巧

模拟与数字混合信号集成电路设计方法与技巧数字混合信号集成电路(Analog Mixed-Signal Integrated Circuit,简称AMS IC)是同时包含了模拟电路和数字电路的集成电路。

它可以完成模拟信号处理和数字信号处理两种功能,广泛应用于各种领域,例如通信、消费电子、汽车电子等。

在设计AMS IC时,需要考虑到模拟电路和数字电路之间的相互影响,以及相应的设计方法和技巧。

首先,AMS IC设计需要综合考虑模拟电路和数字电路。

模拟电路主要用于接收和处理模拟信号,需要考虑到噪声、幅度范围、线性度、频率响应等因素。

数字电路主要用于处理和传输数字信号,需要考虑到时钟、功耗、面积、速度等因素。

在设计AMS IC时,需要找到一个平衡点,既能满足模拟电路的性能要求,又能满足数字电路的性能要求。

其次,AMS IC设计需要注意模拟电路和数字电路之间的相互影响。

模拟电路的性能对数字电路有直接影响,例如模拟电路的噪声和非线性度会降低数字电路的性能。

数字电路的操作也会对模拟电路产生影响,例如时钟的频率和相位会影响模拟电路的采样和重建性能。

因此,在设计AMS IC时,需要仔细分析和评估这些影响,并采取相应的措施来降低不良影响。

在AMS IC设计中,还需要考虑一些特殊技巧和方法。

首先,需要设计合适的模拟-数字界面电路,将模拟信号转换为数字信号,并将数字信号转换为模拟信号。

这些界面电路需要满足高速传输、低功耗、低噪声等要求。

其次,需要采取合适的电源和接地策略,以降低模拟电路和数字电路之间的干扰。

例如,可以采用分层供电和模拟数字分隔,减少共模噪声的影响。

此外,还需要合理选择器件和工艺,例如选择高性能模拟电路器件、互补金属氧化物半导体(CMOS)工艺等,以实现设计需求。

在实际AMS IC设计中,还需要运用一些常用的技巧和工具。

例如,可以采用模拟电路仿真工具来评估模拟电路的性能,例如SPICE。

可以采用时序分析工具来评估数字电路的性能,例如伊凡威尔科技公司的PrimeTime。

混合信号集成电路设计技术

混合信号集成电路设计技术混合信号集成电路(Mixed-Signal Integrated Circuit,简称MSIC)是一种包括模拟电路和数字电路的集成电路。

它不仅有数字信号处理的能力,还能够处理模拟信号,实现模拟与数字之间的转换。

混合信号集成电路的设计技术涉及到电路设计、信号处理、模拟与数字电路的融合等多个方面。

第一部分:混合信号电路的基本原理和分类混合信号电路是模拟与数字信号处理的结合体,它的主要功能是将模拟信号转换为数字信号进行处理。

混合信号电路广泛应用于通信、计算机、汽车电子、医疗设备等领域。

根据电路的功能和应用场景,混合信号电路可以分为多种类型,如高速数据转换器、运算放大器、滤波器、功率放大器等。

第二部分:混合信号集成电路的设计流程混合信号集成电路的设计流程包括需求分析、电路设计、模拟仿真、数字设计、布局布线、验证测试等多个环节。

首先,根据项目需求和规格要求进行需求分析,并进行电路框图设计和原理图设计。

然后,通过模拟仿真和电路参数优化,验证电路的性能和可靠性。

接下来,进行数字设计,包括逻辑设计、数字仿真和时序分析,确保数字电路的正确性。

最后,进行布局布线和物理验证,生成完整的芯片设计,并通过验证测试进行性能评估和调试。

第三部分:混合信号集成电路的关键技术混合信号集成电路的设计过程中,有一些关键技术需要掌握和应用。

其中包括模拟电路设计技术、数字电路设计技术、时钟与时序技术、辐射噪声抑制技术、功耗管理技术等。

模拟电路设计技术主要涉及到放大器设计、滤波器设计、电源管理等,需要考虑噪声、带宽、频率响应等参数。

数字电路设计技术主要包括逻辑设计、时序设计、存储器设计等。

时钟与时序技术是保证数字电路正常工作的关键,需要精确控制时钟频率和时序关系。

第四部分:混合信号集成电路设计工具和方法为了提高混合信号集成电路的设计效率和质量,需要借助相关的设计工具和方法。

常用的设计工具包括EDA工具、SPICE仿真工具、布局布线工具等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2016年《CMOS混合信号集成电路设计》大作业

1、基于TSMC 3.5V/5V 0.35um 2P4M Mixed-Signal CMOS BSIM3V3 Spice

Model,采用Hspices对图1所示的共源共栅CMOS电流镜电路,其中M1、M3的宽长比为1.5um/1um,M2、M4的沟道长度也是1um,M2、M4的沟道宽度为本人学号的最后一位(如果最后一位为0,则为10um),进行输入-输出电流仿真,并给出仿真所用的.sp文件。

(40分)(图1给出了范例波形)

图1

2、基于TSMC 3.5V/5V 0.35um 2P4M Mixed-Signal CMOS BSIM3V3 Spice

Model(模型已经在文件夹中给出),采用Hspices对所示的带隙基准源电路进行仿真验证。

管子的类型和尺寸已在图中给出。

(60分)

详细要求如下:

a.瞬态仿真,电源电压为5V,bias电压为3.8V,温度300K时,电路的瞬态特性

(保存波形图);

b.直流温度扫描仿真,电源电压5V,bias电压为3.8V,温度扫描范围从-20℃到

120℃,保存直流温度扫描下的输出电压的曲线图;

c.合理调节R4的电阻值,使零温度系数的温度点出现在80℃;

d.直流电源电压扫描仿真,温度设置为300K,扫描电源电压从4V到7V变化,

保存输出电压的曲线图;

e.给出1、2、3仿真中所用的三个.sp文件(分别以ex1.sp、ex2.sp和ex3.sp)。

(注意,在使用Hspice进行瞬态仿真的时候,电源电压要设置成PWL形式;但是在进行温度直流扫描的时候,电源电压要设置成DC形式)

备注:题1和题2中的MOS管均采用5V的器件(模型中另有3.3V的器件),电源电压为5V,bjt选用发射极面积为10的三极管。

作业用A4纸打印(封面自制),考试之前收齐交到东大楼419室。