3篇5章习题解答

第5章 习题解答

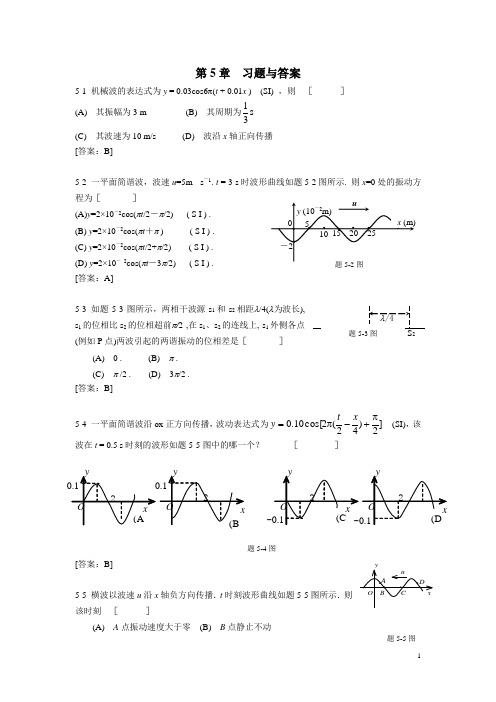

第5章 习题与答案5-1 机械波的表达式为y = 0.03cos6π(t + 0.01x ) (SI) ,则[ ] (A) 其振幅为3 m(B) 其周期为s 31(C) 其波速为10 m/s (D)波沿x 轴正向传播 [答案:B]5-2 一平面简谐波,波速u =5m · s -1. t = 3 s 时波形曲线如题5-2图所示. 则x =0处的振动方程为[ ](A)y =2×10-2cos(πt /2-π/2) ( S I ) . (B) y =2×10-2cos(πt +π ) ( S I ) . (C) y =2×10-2cos(πt /2+π/2) ( S I ) .(D) y =2×10- 2cos(πt -3π/2) ( S I ) .[答案:A]5-3 如题5-3图所示,两相干波源s 1和s 2相距λ/4(λ为波长), s 1的位相比s 2的位相超前π/2 ,在s 1、s 2的连线上, s 1外侧各点(例如P 点)两波引起的两谐振动的位相差是[ ](A) 0 . (B) π . (C) π /2 . (D) 3π/2 . [答案:B]5-4 一平面简谐波沿ox 正方向传播,波动表达式为]2)42(2cos[10.0π+-π=x t y (SI),该波在t = 0.5 s 时刻的波形如题5-5图中的哪一个? [ ][答案:B]5-5 横波以波速u 沿x 轴负方向传播.t 时刻波形曲线如题5-5图所示.则该时刻 [ ](A) A 点振动速度大于零 (B) B 点静止不动ux (m)y (10-2m)· · · · · · · 0 51015 20 25 -2题5-2图题5-4图题5-5图-(C) C 点向下运动 (D) D 点振动速度小于零 [答案:D]5-6 一平面简谐波沿x 轴正方向传播,t = 0 时刻的波形如题5-6图所示,则P 处质点的振动在t = 0时刻的旋转矢量图是[ ][答案:A]5-7 一简谐波沿x 轴正方向传播,t = T /4时的波形曲线如题5-7图所示.若振动以余弦函数表示,且此题各点振动的初相取-π 到π 之间的值,则 [ ] (A) O 点的初相为00=φ(B) 1点的初相为π-=211φ(C) 2点的初相为π=2φ (D) 3点的初相为π-=213φ [答案:D]5-8 在驻波中,两个相邻波节间各质点的振动[ ](A) 振幅相同,相位相同 (B) 振幅不同,相位相同 (C) 振幅相同,相位不同 (D) 振幅不同,相位不同 [答案:B]5-9 一平面简谐波在弹性媒质中传播,在媒质质元从平衡位置运动到最大位移处的过程中:[ ](A) 它的动能转化为势能. (B) 它的势能转化为动能.(C) 它从相邻的一段质元获得能量其能量逐渐增大. (D) 它把自己的能量传给相邻的一段质元,其能量逐渐减小. [答案:D]ωS A O ′ωSA O ′ωωSAO ′(A)(B)(C)(D)S题5-6图5-10 一横波的波动方程是))(4.0100(2sin 02.0SI x t y -=π,则振幅是__________,波长是__________,频率是__________,波的传播速度是__________。

第5章习题解答

第5章习题解答1. 解:Q235钢,m l 5.5=荷载标准值:m kN q k /5.34245.10=+= 荷载设计值:m kN q /2.46244.15.102.1=⨯+⨯=弯矩设计值:m kN ql M x ⋅=⨯⨯==69.1745.52.46818122(1)假定梁的受压翼缘设置可靠的侧向支承,可以保证梁的整体稳定由抗弯强度要求的截面模量为:3361082.77321505.11069.174mm f M W x x nx ⨯=⨯⨯==γ查型钢表选用I36a ,截面几何特性:3878cm W x =,415796cm I x =,质量m kg q /0.60= 强度验算:22326/215/44.1921087805.18/55002.16.01069.174mm N f mm N W M nx x x =<=⨯⨯⨯⨯+⨯=γ 满足要求。

挠度验算:[]2501428110157961006.25500)6.05.34(384538454533=<=⨯⨯⨯⨯+⨯=⋅=l EI l q l x kx υυ满足要求。

故选用此截面。

(2)假定梁的受压翼缘无可靠的侧向支承按整体稳定确定梁截面假定工字钢型号在I45~I63之间,均布荷载作用在梁上翼缘,自由长度m l 5.51=,由附表3-2查政体稳定系数6.0660.0>=b ϕ,所以643.0660.0282.007.1282.007.1=-=-='bbϕϕ所需毛截面抵抗矩:3361063.1263215643.01069.174mm f M W b x nx ⨯=⨯⨯='=ϕ查型钢表选用I45a ,截面几何特性:31433cm W x =,432241cm I x =,质量m kg q /4.80=强度验算:22326/215/52.11810143305.18/55002.1804.01069.174mm N f mm N W M nx x x =<=⨯⨯⨯⨯+⨯=γ满足要求。

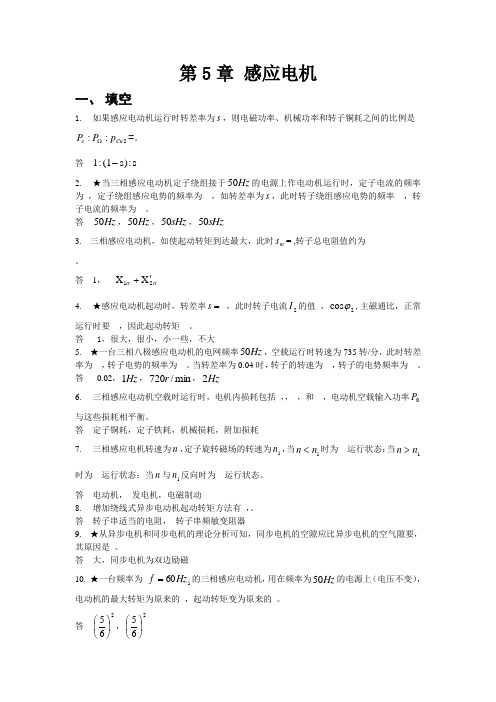

第5章感应电机习题与解答

C ;D 。

答A

6.★三相异步电动机气隙增大,其他条件不变,则空载电流( )。

A 增大 ; B 减小 ;

C 不变 ; D 不能确定。

答A

7.三相感应电动机等效电路中的附加电阻 上所消耗的电功率应等于():

A输出功率 ;B输入功率 ;

C电磁功率 ;D总机械功率 。

答D

8.与普通三相感应电动机相比,深槽、双笼型三相感应电动机正常工作时,性能差一些,主要是()。

答A

12.★设计在 电源上运行的三相感应电动机现改为在电压相同频率为 的电网上,其电动机的()。

A 减小, 减小, 增大;B 减小, 增大, 减小;

C 减小, 减小, 减小;D 增大, 增大, 增大。

答C

13.一台绕线式感应电动机,在恒定负载下,以转差率 运行,当转子边串入电阻 ,测得转差率将为()( 已折算到定子边)。

。

答1,

4.★感应电动机起动时,转差率 ,此时转子电流 的值, ,主磁通比,正常运行时要 ,因此起动转矩 。

答 1,很大,很小,小一些,不大

5.★一台三相八极感应电动机的电网频率 ,空载运行时转速为735转/分,此时转差率为,转子电势的频率为。当转差率为0.04时,转子的转速为,转子的电势频率为。

答0.02, , ,

6.三相感应电动机空载时运行时,电机内损耗包括,,,和,电动机空载输入功率 与这些损耗相平衡。

答定子铜耗,定子铁耗,机械损耗,附加损耗

7.三相感应电机转速为 ,定子旋转磁场的转速为 ,当 时为运行状态;当 时为运行状态;当 与 反向时为运行状态。

答电动机,发电机,电磁制动

8.增加绕线式异步电动机起动转矩方法有 ,。

A4极, ; B6极, ;

第5章思考题和习题解答

第五章 电气设备的选择5-1 电气设备选择的一般原则是什么?答:电气设备的选择应遵循以下3项原则:(1) 按工作环境及正常工作条件选择电气设备a 根据电气装置所处的位置,使用环境和工作条件,选择电气设备型号;b 按工作电压选择电气设备的额定电压;c 按最大负荷电流选择电气设备和额定电流。

(2) 按短路条件校验电气设备的动稳定和热稳定 (3) 开关电器断流能力校验5-2 高压断路器如何选择? 答:(1)根据使用环境和安装条件来选择设备的型号。

(2)在正常条件下,按电气设备的额定电压应不低于其所在线路的额定电压选择额定电压,电气设备的额定电流应不小于实际通过它的最大负荷电流选择额定电流。

(3)动稳定校验(3)max shi i ≥ 式中,(3)sh i 为冲击电流有效值,max i 为电气设备的额定峰值电流。

(4)热稳定校验2(3)2th th ima I t I t ∞≥式中,th I 为电气设备在th t 内允许通过的短时耐热电流有效值;th t 为电气设备的短时耐热时间。

(5)开关电器流能力校验对具有分断能力的高压开关设备需校验其分断能力。

设备的额定短路分断电流不小于安装地点最大三相短路电流,即(3).max cs K I I ≥5-3跌落式熔断器如何校验其断流能力?答:跌落式熔断器需校验分断能力上下限值,应使被保护线路的三相短路的冲击电流小于其上限值,而两相短路电流大于其下限值。

5-4电压互感器为什么不校验动稳定,而电流互感器却要校验?答:电压互感器的一、二次侧均有熔断器保护,所以不需要校验短路动稳定和热稳定。

而电流互感器没有。

5-5 电流互感器按哪些条件选择?变比又如何选择?二次绕组的负荷怎样计算? 答:(1)电流互感器按型号、额定电压、变比、准确度选择。

( 2)电流互感器一次侧额定电流有20,30,40,50,75,100,150,200,400,600,800,1000,1200,1500,2000(A )等多种规格,二次侧额定电流均为5A ,一般情况下,计量用的电流互感器变比的选择应使其一次额定电流不小于线路中的计算电流。

第5章点的合成运动习题解答080814讲课稿

第 5 章点的合成运动习题解答0 8 08 1 4第五章点的合成运动本章要点一、绝对运动、相对运动和牵连运动一个动点,两个参照系:定系,动系;三种运动:绝对运动、相对运动和牵连运动,包括三种速度:绝对速度、相对速度和牵连速度;三种加速度:绝对加速度、相对加速度和牵连加速度;牵连点:动参考系上瞬时与动点相重合的那一点称为动参考系上的牵连点。

二、速度合成定理动点的绝对速度,等于它在该瞬时的牵连速度与相对速度的矢量和,即V a V e V r解题要领1定系一般总是取地面,相对定系运动的物体为动系,动点不能在动系上.2牵连速度是牵连点的速度•3速度合成定理中的三个速度向量,涉及大小方向共六个因素,能且只能存在两个未知数方能求解,因此,至少有一个速度向量的大小方向皆为已知的.4作速度平行四边形时,注意作图次序:一定要先画大小方向皆为已知的速度向量,然后再根据已知条件画上其余两个速度向量,特别注意,绝对速度处于平行四边形的对角线位置.5用解三角形的方法解速度合成图.三、加速度合成定理1牵连运动为平移时的加速度合成定理当牵连运动为平移时,动点的绝对加速度等于牵连加速度与相对加速度的矢量和,即a a a e a r ,当点作曲线运动时,其加速度等于切向加速度和法向加速度的矢量和,因此上式还可进一步写成a;a a a e n t na e a r a r其中a;dv;,n aa2V a tdV e n,a e ,a e2Ve a t,a r dV r,a n2v■ ?a, e, r依次dt a dt e dt r为绝对轨迹、牵连轨迹和相对轨迹的曲率半径。

解题要领1牵连运动为平移时的加速度合成定理只对“牵连运动为平移时”成立,因此,判定牵连运动是否为平移至关重要.2牵连运动为平移时的加速度合成定理涉及的三个加速度,每一加速度都可能有切向和法向加速度。

但是,法向加速度只与速度有关,因此,可以通过速度分析予以求解,从而在此处是作为已知的。

概率论第五章习题解答

概率论第五章习题解答第一篇:概率论第五章习题解答第五章习题解答1.设随机变量X的方差为2,则根据车比雪夫不等式有估计P{X-E(X)≥2}≤ 1/2.P{X-E(X)≥2}≤D(X)22=122.随机变量X和Y的数学期望分别为-2和2,方差分别为1和4,相关系数为-0.5,则根据车比雪夫不等式有估计P{X+Y≥6}≤1/12.P{X+Y≥6}=P{(X+Y)-[E(X)+E(Y)]≥6}≤D(X)62=1123.电站供应一万户用电.设用电高峰时,每户用电的概率为0.9,利用中心极限定理,(1)计算同时用电的户数在9030户以上的概率;(2)若每户用电200 w,电站至少应具有多大发电量才能以0.95的概率保证供电?解:⑴ 设X表示用电户数,则X~B(10000,0.9),n=10000,p=0.9,np=9000,npq=900由中心定理得X~N(9000,900)近似P{X>9030}=1-P{X≤9030}⎧X-90009030-9000⎫=1-P⎨≤⎬900900⎩⎭=1-Φ(1)=1-0.8413=0.1587⑵ 设发电量为Y,依题意P{200X≤Y}=0.95⎧X-9000Y-9000⎫⎪⎪200即 P⎨≤⎬=0.95900900⎪⎪⎩⎭-9000200Φ()=0.95900Y-9000200≈1.65900Y=1809900 4.某车间有150台同类型的机器,每台机器出现故障的概率都是0.02,设各台机器的工作是相互独立的,求机器出现故障的台数不少于2的概率.解:设X表示机器出故障的台数,则X:B(150,0.02)Ynp=3,npq=2.94 由中心定理得X~N(3,2.94)近似P{X≥2}=1-P{X<2}2-3⎫⎧X-3=1-P⎨<⎬2.942.94⎩⎭=1-P{X<-0.58 32}=Φ(0.5832)=0.7201 5.用一种对某种疾病的治愈率为80%的新药给100个患该病的病人同时服用,求治愈人数不少于90的概率.解:设X表示治愈人数,则X:B(100,0.8)其中n=100,p=0.8,np=80,npq=16P{X≥90}=1-P{X<90}⎧X-8090-80⎫=1-P⎨<⎬1616⎩⎭=1-Φ(2.5)=0.0062 6.设某集成电路出厂时一级品率为0.7,装配一台仪器需要100只一级品集成电路,问购置多少只才能以99.9%的概率保证装该仪器是够用(不能因一级品不够而影响工作).解:设购置n台,其中一级品数为X,X:B(n,0.7)p=0.7,np=0.7n,npq=0.21nP{X≥100}=1-P{X<100}⎧X-0.7n100-0.7n⎫=1-P⎨<⎬0.21n0.21n⎩⎭10 0-0.7n=1-Φ()0.21n=0.999故Φ(-100-0.7n0.21n)=0.999有-100-0.7n0.21n=3.1⇒n=121(舍)或n=1707.分别用切比雪夫不等式与隶莫弗—拉普拉斯中心极限定理确定:当掷一枚硬币时,需要掷多少次才能保证出现正面的频率在0.4~0.6之间的概率不小于90%.解:设掷n次,其中正面出现的次数为X,X:B(n,p),p=⑴由切贝雪夫不等式,要使得P⎨0.4<12⎧⎩X⎫<0.6⎬≥0.9成立n⎭D(X)X⎧X⎫⎧XX⎫25⎧⎫n由于P⎨0.4< <0.6⎬=P⎨-p<0.1⎬=P⎨-E()<0.1⎬≥1-=1-2nnnn0.1n⎩⎭⎩⎭⎩⎭只要1-25X⎧⎫<0.6⎬≥0.9成立≥0.9,就有P⎨0.4<nn⎩⎭从而⇒n≥250⑵中心极限定理,要使得P⎨0.4<⎧⎩X⎫<0.6⎬≥0.9成立n⎭由于X:N(0.5n,0.25n)近似X⎧0.4n-0.5nX-0.5n0.6n-0.5n⎫⎧⎫P⎨0.4<<0.6⎬=P{0.4n<X<0.6n} =P⎨<<⎬n0.25n0.25n0.25n⎩⎭⎩⎭X-0.5n⎧-0.1n=P⎨<<0.25n⎩0.25n所以Φ(0.1n⎫0.1n-0.1n0.1n=Φ()-Φ()=2Φ()-1>0.9⎬0.25n⎭0.25n0.25n0.25 n0.1n0.25n)>0.95查表0.1n0.25n>1.65⇒n≥688.某螺丝钉厂的废品率为0.01,今取500个装成一盒.问废品不超过5个的概率是多少?解:设X表示废品数,则X:B(500,0.01) p=0.01,np=5,npq=4.955-5⎫⎧X-5P{X≤5}=P⎨≤⎬=Φ(0)=0.54.95⎭⎩4.95第二篇:概率论第一章习题解答1.写出下列随机试验的样本空间:1)记录一个小班一次数学考试的平均分数(以百分制记分);2)一个口袋中有5个外形相同的球,编号分别为1、2、3、4、5,从中同时取出3个球;3)某人射击一个目标,若击中目标,射击就停止,记录射击的次数;4)在单位圆内任意取一点,记录它的坐标.解:1)设小班共有n 个学生,每个学生的成绩为0到100的整数,分别记为x1,x2,Λxn,则全班平均分为x=∑xi=1nin,于是样本空间为12100niS={0,,Λ,}={|i=0,1,2,3,Λ100n}nnnn32)所有的组合数共有C5=10种,S={123,124,125,134,135,145,234,235,245,345} 3)至少射击一次,S={1,2,3,Λ}4)单位圆中的坐标(x,y)满足x2+y2<1,S={(x,y)|x2+y2<1}2.已知A⊂B,P(A)=0.3,P(B)=0.5,求P(A),P(AB),P(AB)和P(AB).解 P(A)=1-P(A)=1-0.3=0.7 P(AB)=P(A)=0.3(因为A⊂B)P(AB)=P(B-A)=P(B)-P(A)=0.2P(AB)=P(B)=0.5(因为A⊂B,则B⊂A)3.设有10件产品,其中6件正品,4件次品,从中任取3件,求下列事件的概率:1)只有一件次品; 2)最多1件次品; 3)至少1件次品.12C4C 解 1)设A表示只有一件次品,P(A)=36.C102)设B为最多1件次品,则表示所取到的产品中或者没有次品,或者只有一件次312C6C4C品,P(B)=3+36.C10C103)设C表示至少1件次品,它的对立事件为没有一件次品,3C6P(C)=1-P(C)=1-3C104.盒子里有10个球,分别标有从1到10的标号,任选3球,记录其号码.(1)求最小号码为5的概率.(2)求最大号码为5的概率.解1)若最小号码为5,则其余的2个球必从6,7,8,9,10号这5个球中取得。

习题答案:第5章拉深

第5章拉深一、填空1.拉深系数m是筒形直径和坯料直径的比值,m越小,则变形程度越大。

(5-1)2.拉深过程中,变形区是坯料的凸缘部分,其它部分是传力区。

(5-1)3.拉深中,产生起皱现象是因为该区域内受较大压应力的作用,导致材料失稳而引起的。

(5-1)4.影响拉深坯料起皱的主要因素有:材料相对厚度,拉深系数和拉深模工作部分的几何形状和尺寸。

(5-1)5.防止圆筒形件拉深起皱的方法通常是采用压料装置,并采用适当的压边力。

(5-1) 6.利用拉深模将一定形状的平面坯料或空心件制成开口件的冲压工序叫做拉深。

(5-1)7.拉深件的壁厚是不均匀的,下部壁厚略有变薄,上部分却有所增厚。

(5-1)8.板料的相对厚度t/D越小,则抗失稳能力越小,越容易起皱。

(5-1)9.一般情况下,拉深件的尺寸精度应在 IT13级以下,不宜高出 IT11 级。

(5-2)10.实践证明,拉深件的平均厚度与坯料厚度相差不大,由于塑性变形前后体积不变,因此,可以按坯料面积等于拉深件表面积原则确定坯料尺寸。

(5-3)11.拉深件的毛坯尺寸确定依据是等面积法。

(5-3)12.确定拉深件坯料形状和尺寸的原则是久里金法则。

(5-3)13.影响极限拉深系数的因素有:材料的组织与力学性能、板料的相对厚度、拉深工作条件等。

(5-4)14.有凸缘拉深件多次拉深必须遵循一个原则,即第一次拉深成有凸缘的工序件时,其凸缘的外径应等于成品零件的尺寸,在以后的拉深工序中仅仅使已拉深成形的工序件的直筒部分参与变形,逐步减少其直径并增加其高度,而第一次拉深时已成形的凸缘外径必须保持不变。

即在以后的拉深工序中不再收缩。

(5-4)15.为了提高工艺稳定性,提高零件质量,必须采用稍大于极限值的拉深系数。

(5-4)16.窄凸缘圆筒形状零件的拉深,为了使凸缘容易成形,在拉深窄凸缘圆筒零件的最后两道工序可采用锥形凹模和锥形压料圈进行拉深。

(5-4)17.压料力的作用为:防止拉深过程中坯料起皱(5-5)18.目前采用的压料装置有弹性压料和刚性压料装置。

西方经济学第五章练习题(含答案)

西方经济学第五章练习题(含答案)西方经济学(本第五章厂商均衡理论综合练习题参考答案一、名词解释题1.完全竞争是指竞争不受任何阻碍和干扰的市场结构。

2.完全垄断是指整个行业中只有一个生产者的市场结构。

3.价格歧视,也叫差别定价,即垄断者在同一时间,对同一产品的不同的消费者收取不同的价格。

4.一级价格歧视,也称完全价格歧视是指厂商按每一单位产品消费者愿意支付的最高价格,确定单位产品的价格。

5.二级价格歧视是指厂商按照消费者不同的购买量段收取不同的价格,购买量越小,厂商索价越高,购买量越大,厂商索价越低。

6.三级价格歧视,是指厂商把对同一种产品在不同的消费群,不同市场上分别收取不同的价格。

7.垄断竞争是指许多厂商生产和销售有差别的同类产品,市场中既有竞争因素又有垄断因素存在的市场结构。

8.寡头垄断是指少数几个厂商控制着整个市场中的生产和销售的市场结构。

二、单项选择题1.B9.D2.A10.A3.B11.A4.C12.C5.C13.A6.A14.A7.C15.D8.C16.C三、多项选择题1.ABC2.BD3.ABCD4.ABD5.AB6.ABE7.ABD8.ACDE9..ABD10.BDE11.ABD四、判断分析题1.×8.×2.√9.×3.×10.√4.×11.×5.×12.√6.√13.√7.×14.×五、计算题1.已知一垄断企业成本函数为:TC=5Q2+20Q+1000,产品的需求函数为:Q=140-P,求:(1)利润最大化时的产量、价格和利润,(2)厂商是否从事生产?解:(1)利润最大化的原则是:MR=MC因为TR=P·Q=[140-Q]·Q=140Q-Q2所以MR=140-2QMC=10Q+20所以140-2Q=10Q+20Q=10P=130(2)最大利润=TR-TC=-400(3)因为经济利润-400,出现了亏损,是否生产要看价格与平均变动成本的关系。

5章 化学平衡原理习题及全解答

第5章 化学平衡原理习题及全解答1. 写出下列反应的标准平衡常数表达式。

(1) CH 4(g) + 2O 2(g) == CO 2(g) + 2H 2O(l) (2) PbI 2(s) == Pb 2+(aq) + 2I -(aq)(3) BaSO 4(s) + 2C(s) == BaS(s) + 2CO(g) (4) Cl 2(g) + H 2O(l) == HCl(aq) + HClO(aq) (5) ZnS(s) + 2H +(aq) == Zn 2+(aq) + H 2S(g) (6) CN -(aq) + H 2O(l) == HCN(aq) + OH -(aq)答: (1) 224242θCO CO θθθ22CH O CH O /(/)(/)pp p p K p p p p p p==(相对压力)(2) 2+-2+-θθθ22Pb I Pb I (/)(/)c K c c c c c c == (相对浓度)(3) θθ2CO (/)p K p p = (4) 2θθHCl HClO Cl /(/)K c c p p =(5) 2++2θθ2H S Zn H (/)/K c p p c = (6) --θHCN OH CN /K c c c =2. 填空题(1) 对于反应:C(s)+CO(g)==2CO(g),=172.5 kJ ⋅mol -1,填写下表:532定量的惰性气体,反应将 移动。

(3) 对化学反应而言,r m G ∆是 的判据,r m G ∆是 的标志,若r m G ∆ =r mG ∆,则反应物和生成物都处于 状态。

动。

(3) 反应方向;反应进行倾向性;平衡。

3. 氧化亚银遇热分解:2Ag 2O(s) == 4Ag(s) + O 2(g)。

已知Ag 2O 的f m H ∆ =-31.1kJ ⋅mol -1,f m G ∆=-11.2 kJ·mol -1。

求:(1) 在298K 时Ag 2O —Ag 体系的2O p =?(2) Ag 2O 的热分解温度是多少(在分解温度,2O p =100kPa)?解: (1) -1r m Bf m 62.2 kJ mol H H ν∆=∆=⋅∑ ,-1r m B f m 22.4 kJ mol G G ν∆=∆=⋅∑2θθO /p K p p=,根据r m ln ()/K G T RT =-∆ ,当T =298 K 时, 3ln 22.410/(8.314298)9.04K =-⨯⨯=- 41.210K -=⨯P (o 2) =Pa 12k 100102.14=⨯⨯=⨯- p K p(2) 在分解温度,2O p =100 kPa , 1.0K = ,r m ()G T ∆=0根据Gibbs 方程:r m r m r m ()G T H T S ∆=∆-∆ ,r m r m/T H S =∆∆ 根据r m H ∆ 、r m S ∆ 随温度变化不大,故:-1r m r m ()(298)62.2 kJ mol H T H ∆≈∆=⋅ -1-1r m r m r m r m(298)(298)()(298)0.134 kJ mol K 298H G S T S ∆-∆∆≈∆==⋅⋅r mr m/465 K T H S =∆∆分解=或者:根据van ’t Hoff 方程:22r m 211112()ln ()K T H T T K T RT T ∆-=,412(298) 1.210, ()1K K T -=⨯=分解 ,解得:465 K T =分解。

化学工程基础课后习题及答案

化学工程基础课后习题及答案化学工程基础课后习题及答案【篇一:化工基础第5章习题答案】xt>5.2气体的吸收1.空气和co2的混合气体中,co2的体积分数为20%,求其摩尔分数y和摩尔比y各为多少?解因摩尔分数=体积分数,y?0.2摩尔分数摩尔比 y?y0.20.25 1?y1?0.22. 20℃的l00g水中溶解lgnh3, nh3在溶液中的组成用摩尔分数x、浓度c及摩尔比x表示时,各为多少?解摩尔分数x?1/17=0.01051/17?100/18浓度c的计算20℃,溶液的密度用水的密度?s?998.2kg/m3代替。

溶液中nh3的量为 n?1?10?3/17kmol 溶液的体积v?101?10?3/998.2 m3n1?10?3/17溶液中nh3的浓度c?==0.581kmol/m3 ?3v101?10/998.299.82c?sx??0.010?5.0kmol582/m3 或ms18nh3与水的摩尔比的计算 x?1/170.0106100/18x0.0105??0.0106 1?x1?0.0105或 x?3.进入吸收器的混合气体中,nh3的体积分数为10%,吸收率为90%,求离开吸收器时nh3的组成,以摩尔比y和摩尔分数y表示。

吸收率的定义为y被吸收的溶质量y1?y21?2原料气中溶质量 y1 y1解原料气中nh3的摩尔分数y?0.1 摩尔比 y1?y10.10.111 1?y11?0.1吸收器出口混合气中nh3的摩尔比为y2?(1??)y1?(1?0.9)?0.111?0.0111摩尔分数 y2?y20.0111=?0.01098 1?y21?0.01114.l00g水中溶解lg nh3,查得20℃时溶液上方nh3的平衡分压为798pa。

此稀溶液的气液相平衡关系服从亨利定律,试求亨利系数e(单位为kpa)、溶解度系数h[单位为kmol/(m3?kpa)]和相平衡常数m。

总压为100kpa。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

nn

=Q Q

+

AQ n

n

=Q

+

AQ n

题3.5.6 根据图题3.5.6所示电路及A、B、C波形,画出触发器Q端的波 形。(设触发触器初态为“0”)。

图题 3.5.6

n

解:如果 D = Q ,则是一个计数触发器(翻转触发器),加了异或门后,只有当异或

n

门输出高电平时,才满足 D = Q ,所以画出的波形图如图所示。

=

J 0 Q0n

+

K 0 Q0n

= Q2n Q0n

+ Q1n Q0n

依次设定初态,计算出次态如下:

初态设定从 Q2nQ1nQ0n = 000 开始,→001→010→011→100→001

164

图题 3.5.2

解:由基本RS触发器构成消除机械弹跳时的原理可以用波形加以说明。 当机械开关S从上端打到下端时,触点已离开了上端,但下端有一个接触和 非接触的过程,决定于触点的弹性好坏。波形说明开关离开上端,在下端弹 跳几下的情况。

由于 S D变高电平RD变低电平后 , RD再次变高电平时 触发器的输

题3.5.5 试写出图题3.5.5各触发器的次态逻辑函数表达式。

166

(a)

(b)

(c)

(d)

解:(a)电路: Qn+1

=

n

AQ

图题 3.5.5

(b)电路: Qn+1

=

n

Q

+

AQn

=

n

A+Q

(c)电路: Qn+1 = AQnQn + AQ nQ n = AQ n

(d)电路: Qn+1

=

n

JQ

+

KQ n

出处于保持功能。所以虽然机械开关有弹跳,但触发器的输出状态是稳定的。 题3.5.3 在钟控(电平控制)RS触发器(教材图3.5.5(a)所示)中,

S、R、CP端加入如图题3.5.3所示波形,试画出Q端的波形(设初态为“0”)。

165

图题 3.5.3

解:在钟控RS触发器(即同步RS)中,在R=S=1时, Q = Q = 1,而如若RS 同时变为“0”后, Q, Q 的状态将不能确定,现在RS同时为1后不同时为“0”,

题3.5.9 图题3.5.9所示电路为CMOS JK 触发器构成的双相时钟电路, 试画出电路在CP作用下,QA和QB的波形(设初态Q为“0”态)。

图题3.5.9

解:JK触发器本身接成了计数型触发器,所以只要先画出 Q, Q 的波形,就

不难画出 QA与QB 的波形了。其波形如图所示。

CP

Q

Q

QA

QB

170

图题 3.5.15

清除

CR

题表2.5.15真值表

输入

输

Ai Bi Z1 ( ) Z 2 ( )

出

Z3( )

0 ××

1

00

1

01

174

1

10

1

11

解:

清除 输 入

Cr

Ai

Bi

0

××

1

0

0

1

0

1

1

1

0

1

1

1

Z1(A>B) 0 0

0 1 0

输 Z2(A<B) 0 0

1 0 0

出 Z3(A=B) 1 保持

(4)边沿触发器虽然在上升沿或下降边沿接收数据,并完成翻转,但 数据必须在边沿到达前有效,(如上升沿触发时,数据必须比上升沿早到的 最短时间,这时间由组成触发器的电路结构决定)。

(5)触发器的逻辑功能描述有:真值表描述、次态逻辑函数描述、状 态转换图描述、卡诺图描述、时序图描述等几种。

176

(6)触发器由各种逻辑门电路组成,因此其输入和输出电气特性应该 和同一工艺的门电路一样。

167

题3.5.7 设图题3.5.7中各个边沿触发器初始状态皆为“0”状态,试画 出连续六个时钟周期作用下,各触发器Q端的波形。

图题 3.5.7

解:F1是D触发器,上升沿触发,其波形为

F2是D触发器接成的计数触发器,下降沿触发,所以有波形为: F3是D触发器,上升沿触发,其波形为:

F4是JK触发器,下降沿触发,由于JK=1,所以是计数触发器,其波形

图题 3.5.11

解:这是一个分频电路,其波形为:

题3.5.12 试用一个CMOS D触发器,一个“与”门及二个“或非”门构成一

个JK触发器。 解: 这是将 D 功能触发器转换为 JK 功能触发器的一个功能转换电路,

转换的的基本思路如图所示:

因为 D 触发器的特性方程为: Q n+1 = D ,而 JK 触发器的特性方程为

1J1 = Q0n ,1K1 = Q2n Q0n

1J 2 = Q1nQ0n ,1K 2 ="1"

触发器驱动方程代入各自的特性方程求得状态方程:

Q n&

K 2Q2n

=

Q2n Q1n Q0n

Q n+1 1

=

J1 Q1n

+ K1Q1n

= Q1nQ0n

+ Q2nQ1n Q0n

Q n+1 0

0 0 保持

题3.5.16 试绘画出D触发器、JK触发器、T触发器的状态转换图(也称 状态转移图);

解:D 触发器具有二个逻辑功能,即置“0”,和置“1”。 其状态转换图为:

JK 触发器具有 4 种功能,置“0”、置“1”、保持和翻转, 其状态转换图为:

T 触发器具有 2 种功能,保持和翻转功能,其状态转换图为:

题3.5.18 简述同步和异步时序逻辑电路的一般分析方法。 解:分析一个时序逻辑电路,其目的是分析电路的逻辑功能,其方法通 常为:写出各个触发器的驱动方程、特性方程和输出方程,将驱动方程代入 特性方程求出状态方程,然后依次设定触发器的初始状态,求出次态和电路 输出状态。画出状态转换图和列出状态转换真直表,最后得出电路的功能结 论。 题3.5.19 解释时序逻辑电路的自启动概念。解决自启动主要有哪几种 方法,各有什么优缺点? 解:时序电路的自启动是指:当电路状态进入该电路可能有的状态中的 任何一个状态时,在时钟脉冲CP的作用下,电路都会进入主循环状态,进而 一直在主循环状态下工作。 解决自启动的主要方法有:(1)用直接置位和复位端将状态不在主循 环的状态置成主循环中的一个状态,进而在主循环中工作。这种情况只有在 无效态比较少的情况下适用,它简单。(2)重新设计,将无效态在设计时 就规定进入主循环中有效态,这样可以规定无效态进入有效循环的路径,但 线路比较复杂,它适用于无效状比较多的情况下。 题3.5.20 已知某同步时序电路如图题3.5.20所示,试问:

都是高电平时, Q和Q 强制为低电平,只有在RD和SD都为高电平同时变为 低电平时, Q和Q 的状态难以确定(即, Q和Q 哪一个为高电平无法明确 决定,但是一高一个低的状态是稳定的)。根据提供的波形图,画出, Q和Q

的波形如图所示。

题3.5.2 图题3.5.2是应用基本RS触发器消除机械弹跳的逻辑电路,试 说明其工作原理并体会触发器的保持功能。

图题 3.5.20

(1)计数器的模是多少?采用什么编码方式进行计数? (2)电路能否自启动? (3)若计数脉冲频率fCP为700Hz时,从Q2端、Q0端输出时的频率各为多 少?

177

(4)试用Multisim软件绘出6个CP脉冲作用下CP、Q0、Q1、Q2波形图。 解:要回答上述问题,应该对电路进行分析。分析计数器电路有多种方法, 列表法:以 CP 为顺序,依次列出触发器的初态、输入,和次态,可以得出 结论。但在异步计数器时,要注意有无 CP 脉冲。

所以有如下波形。

题3.5.4 试写出图题3.5.4各触发器的次态逻辑函数表达式。

图题 3.5.4

解:(a)电路: Qn+1

=

n

JQ

+ KQn

=

n

AQ

+

AQ n

=

A ⊕Qn;

(b)电路: Qn+1

n

=TQ

+ TQn

=

n

Q

;

(c)电路: Qn+1

=

S

+

RQn

=

n

Q

;

(d)电路: Qn+1 = D = Qn ;

168

为:

F5是JK触发器,下降沿触发,由于J=Q、K= Q ,所以是触发器,其波

形为:

F6是JK触发器,下降沿触发,由于J=“1”、K= Q ,所以触发器翻转

成“1”态后,一直保持在“1”态,其波形为:

F7是JK触发器,下降沿触发,由于J=“Q”、K=“1”,所以触发器 翻转成“1”态后,一直保持在“1”态,其波形为:

写出各触发器的状态方程,依次设定初态,用计算方法求得次态,得 出结论。同样注意状方程有效必须有 CP 脉冲。

写出各触发器的状态方程后,用填卡诺图的方法,得出结论。下面用 写出各触发器状态方程后,依次设定初态计算法为例:

(a) 是一个同步计数器,各触发器驱动方程

1J 0 = Q2nQ1n ,1K 0 ="1"

A

CP

QA QB QB 题3.5.14 由维阻D触发器和负边沿JK触发器构成的电路及CP、 RD 和 D 的波形如图题2.4.14所示,试画出Q1和Q2的波形。

173

图题 3.5.14

解:该题请注意维阻D是上升沿触发,而JK触发器是下降沿触发后画出的波 形如下:

CP

Rd

D Q Q

题3.5.15 图题3.5.15给出了JK触发器和门电路构成的串行数据比较器 (输入为两路串行数据Ai和Bi,输出为比较结果),清零后送入数据进行比 较。试分析后在Z1、Z2、Z3输出端标明三种比较结果(A>B或A<B或A和B相 等(A=B))。并填写题表3.5.15真值表的输出栏。