实验一 Xilinx-ISE13软件使用

Lab1 ISE 工具入门

电子基础实验B-EDA实验1

姓名:周林峰学号:222012615220018

实验名称:熟悉实验环境

一、实验目的

1. ISE 工具的使用流程,从最开始的源文件输入到最后的二进制文件的生成。

2. 7 段数码管显示原理

3.拨码开关控制LED 按钮控制7 段数码管的数字电路的实现

二、实验环境

1. Xilinx ISE Design Suite 13.4(FPGA 开发工具)

2. Digilent Adept 编程调试工具

三、实验内容

四、 实验感想

安装程序花了不少时间,与上学期的fpga 实验相比,程序的编写都是用VHDL 语言,且内容接近,但是在设置方面多了不少新的东西,很多新的地方需要学习。

ISE软件使用说明(两篇)

引言:概述:ISE软件是由Xilinx公司开发的一款集成电路设计工具,使用该软件可以进行数字电路设计、仿真、验证以及实现等多个阶段的工作。

在设计阶段,ISE软件提供了丰富的组件库和设计工具,方便用户进行电路原理图的绘制和逻辑设计。

在验证阶段,ISE软件可以进行功能仿真和时序仿真,以确保设计的正确性和稳定性。

在实现阶段,ISE软件提供了先进的布局与布线工具,能够将设计转化为实际的电路板。

正文内容:1.安装与启动1.1ISE软件安装包1.2安装ISE软件1.3启动ISE软件2.项目管理2.1创建新项目2.2导入已有项目2.3添加设计文件2.4设定项目属性2.5保存和备份项目3.设计流程3.1电路原理图设计3.1.1组件选择3.1.2连接元件3.1.3设置元件属性3.2逻辑设计3.2.1设计约束3.2.2逻辑优化3.2.3时序约束3.3约束文件编辑3.3.1约束规则3.3.2约束语法3.3.3约束检查3.4时序仿真3.4.1创建仿真波形3.4.2设定初始状态3.4.3运行仿真3.5功能仿真3.5.1设置输入信号3.5.2运行仿真3.5.3分析仿真结果4.仿真与验证4.1时序分析4.1.1设定时钟4.1.2时序路径分析4.1.3时序优化4.2时序约束验证4.2.1满足约束4.2.2修复时序错误4.3灵敏度分析4.3.1设定输入敏感性4.3.2分析敏感性4.4逻辑分析4.4.1切换敏感性4.4.2分析逻辑状态5.布局与布线5.1物理约束5.1.1面积约束5.1.2信号完整性约束5.1.3电源与接地约束5.2布局5.2.1网表导入5.2.2管理物理资源5.2.3进行布局布线5.3时序优化5.3.1满足时序约束5.3.2缩短信号传输路径5.3.3优化时钟分配5.4布线5.4.1管理布线资源5.4.2进行布线5.4.3路由与优化5.5设计规约检查5.5.1检查布局布线规约5.5.2修复设计规约错误总结:引言概述:ISE软件是一款功能强大的集成开发环境工具,广泛应用于数字电路设计和实现。

Xilinx ISE使用流程1

Xilinx ISE使用流程(从新建项目到仿真执行)最近在忙着做毕业设计(计算机专业,非电子专业),从小就喜欢电子技术,但由于之前没有接触过FPGA,所以特意跑书店买了一本《Xilinx FPGA数字设计》一书,这本书同时用VHDL和Verilog HDL两种语言讲解,使用的示例非常简洁明了,是一本非常适合入门的图。

我在学习VHDL的时候,发现网上资料很少,所有决定把自己所学的知识和心得分享给广大网友,以便初学FPGA的同学们可以快速掌握Xilinx ISE工具的应用。

注意:阅读本篇文章需要数字电路和C语言等语言基础,本篇文章的代码示例出自《Xilinx FPGA数字设计》,请大家尊重版权。

我使用的Xilinx版本为ISE 14.2。

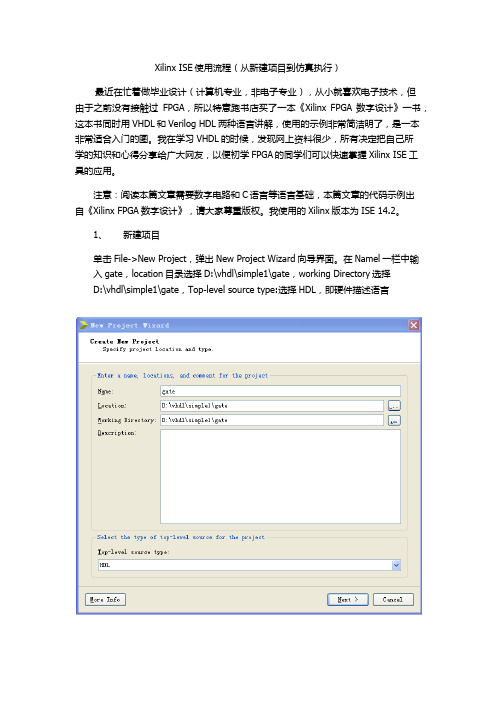

1、新建项目单击File->New Project,弹出New Project Wizard向导界面。

在Namel一栏中输入gate,location目录选择D:\vhdl\simple1\gate,working Directory选择D:\vhdl\simple1\gate,Top-level source type:选择HDL,即硬件描述语言单击Next,选择芯片型号和封装等,其中,芯片大家可以选择自己喜欢的,Synthesis Tool(综合工具)选择XST (VHDL/Verilog),Simluator(仿真工具)选择ISim (VHDL/Verilog),当然你也可以选择Modesim工具,Preferred Language(偏好语言)选择VHDL,VHDL Source Analysis Standard(VHDL语言分析标准)选择VHDL-200X单击Next,进入Project Summary页面,单击Finish,这一节我就不截图了。

进入程序主界面,我们可以看到一个空视图(Empty View),如下图:接下来我们要添加源代码了,在Hierarchy(层级)面板中选中XC6SLX16-3CSG324节点,右键单击New Source菜单,弹出New Source wizard向导界面,选中VHDL Module树节点,在右侧的File name输入gate。

Xilinx ISE Design Suite 13.4 软件使用流程(EDK和SDK部分)

Xilinx ISE Design Suite 13.4 软件使用流程(EDK与SDK部分)ISE的全称为Integrated Software Environment,即“集成软件环境”,是Xilinx公司的硬件设计工具。

相对容易使用的、首屈一指的PLD设计环境!ISE将先进的技术与灵活性、易使用性的图形界面结合在一起,不管您的经验如何,都让您在最短的时间,以最少的努力,达到最佳的硬件设计。

EDK=Embedded Development Kit,嵌入式开发套件。

EDK是xilinx公司开发嵌入式系统的工具。

比起xilinx的ISE,二者不同在于,如果仅仅是使用xilinx的fpga做逻辑设计,只需要ISE开发环境。

但是如果要使用powerpc或者microblaze处理器,从硬件到软件设计的整个嵌入式系统设计,就需要EDK。

SDK(Software Development Kit, 即软件开发工具包)一般是一些被软件工程师用于为特定的软件包、软件框架、硬件平台、操作系统等建立应用软件的开发工具的集合。

我是一个刚刚接触Xinlinx公司开发的fpga。

在对软件使用中遇到很多问题,在网上很难找到完全匹配的教程。

特别是在EDK的使用过程中,网上流传的教程都是基于老版本的。

步骤上有一些差异,对初学者来说往往不知所云,官网上的英文资料也存在一定的理解问题。

因此在此介绍一些EDK的使用步骤。

在老版本的EDK中。

硬件逻辑和软件工程是在一个EDK软件中的。

而版本比较新一点的,需要EDK硬件工程部分和SDK软件工程部分结合使用。

以下为具体的使用步骤,在解说的过程中不免出现错误。

还希望朋友们给以宝贵的意见。

1.首先点击电脑中的Xilinx Platform Studio 快捷方式,打开EDK软件。

如果桌面上没有快捷方式,也可以在开始——所有程序----Xilinx ISE Design Suite 13.4——EDK——Xilinx Platform Studio。

ISE软件使用说明

ISE软件使用说明ISE(Integrated Software Environment)软件是由赛灵思公司(Xilinx Inc.)开发的一款用于设计和开发数字电路的软件工具。

该软件提供了一个集成的环境,用于设计、模拟和验证数字电路。

本文将介绍ISE软件的安装和基本使用方法,以帮助用户快速上手。

一、安装ISE软件2.根据安装程序的提示,选择安装的目标文件夹和所需的组件。

3.等待安装程序完成安装。

二、打开ISE软件打开ISE软件后,会出现一个欢迎界面,用户可以选择新建项目、打开已有项目或者直接进入ISE工具链。

三、创建新项目1. 点击“New Project”按钮,进入新项目设置页面。

2.输入项目的名称和路径,选择项目类型和芯片系列。

3. 点击“Next”按钮,进入项目配置页面。

4.在此页面中,用户可以添加需要使用的源文件、约束文件和IP核等。

5. 点击“Next”按钮,进入总结页面。

6. 点击“Finish”按钮,完成项目创建。

四、设计源文件在ISE软件中,用户可以使用HDL(硬件描述语言)进行设计源文件的编写。

ISE软件支持的HDL语言有VHDL和Verilog。

1. 在项目视图中,右键点击“Source”文件夹,选择“New Source”。

2.在弹出的对话框中,选择源文件类型和语言。

3. 输入文件的名称和路径,点击“Finish”按钮。

五、添加约束文件约束文件用于定义电路的时序、引脚映射等信息,以确保电路的正常工作。

1. 在项目视图中,右键点击“Constraints”文件夹,选择“New Source”。

2.在弹出的对话框中,选择约束文件类型。

3. 输入文件的名称和路径,点击“Finish”按钮。

六、综合与实现在进行综合和实现之前,需要根据设计需求进行一些设置和配置。

1. 在项目视图中,右键点击项目名称,选择“Properties”。

2.在弹出的对话框中,选择“SYNTHESIS”或“IMPLEMENTATION”选项卡。

FPGA实验课件--ISE的使用与设计流程

分频器,100MHZ1HZ

高等教育出版社

基于verilog语言的ISE设计流程 --创建一个新的设计文件

3位计数器

高等教育出版社

基于verilog语言的ISE设计流程 --对该设计进行行为仿真

选中Simulation选项

选中counter.v,点击鼠标右键 选中New Source…

高等教育出版社 测试代码

ISE13.3集成开发环境介绍 --主界面介绍

工作区子窗口 源文件窗口

处理子窗口

高等教育出版社 脚本子窗口

基于verilog语言的ISE设计流程

--一个数字系统的设计原理

计数器

外部50MHz时钟

1Hz时钟

分频器生成 电路

3位的计 数器

LED灯显示计数值

top.v divider.v clk reset 分频器 1HZ counter.v 3位计数器 out[2:0]

选择Implement Design, 并展开

第三步: 布局和布线 ”Place & Route” 高等教育出版社

基于verilog语言的ISE设计流程 --查看布局布线后结果

选择Place & Route, 并展开 选择View/Edit Routed Design(FPGA Editor)

高等教育出版社

工程名

器件名字

生成了空的工程框架

高等教育出版社

基于verilog语言的ISE设计流程 --创建一个新的设计文件

选中器件名字,点击鼠标右键 选中New Source…

高等教育出版社

基于verilog语言的ISE设计流程 --创建一个新的设计文件

块存储器映像文件 在线逻辑分析仪Chipscope定义和连接文件

XilinxISE软件使用过程新(含PROM下载)

Xilinx ISE 13.4软件使用方法本章将以实现一个如图所示的4为加法器为例,来介绍Xilinx ISE13.4开发流程,并且最终下载到实验板BASYS2中运行。

4位加法器C0C 1A0A1A2A B0B1B2B3S0S 1S2S331.建立工程运行Xilinx ISE Design Suite 13.4,初始界面如图F2所示所示F1软件初始状态表软件初始状态表选择File->New Project ,该对话框显示用向导新建工程所需的步骤。

,该对话框显示用向导新建工程所需的步骤。

在Name 栏中输入工程名称(注意:以下所有不能含有中文字符或空格),如“test”。

在Location 栏中选择想要存放的工程位置,如“E:“E:\code\Xilinx\\code\Xilinx\\code\Xilinx\test”test”。

顶层语言选项栏中选择“HDL”语言。

设置向导最终设置效果如图F2所示所示F2路径信息设置表路径信息设置表点击“Next”,进入芯片型号选择界面。

进入芯片型号选择界面。

在本界面中,在本界面中,根据BASYS2实验板上的芯片型号进行相关设置,设置效果如图F3所示。

所示。

F3芯片信息选择表芯片信息选择表点击“Next Next””,出现如图F4所示工程信息汇总表格。

所示工程信息汇总表格。

F4工程信息汇总表工程信息汇总表点击“Finish”完成设置。

完成设置。

2新建V erilog文件在F5所示界面中,如图所示的区域内右击鼠标,选择“New Source”,出现F6对话框。

对话框。

F5在File name栏中键入verilog文件的名称,如“test”。

F6Next””,在本界面中将设置加法器的输入输出引脚数量,如图F1所示点击“Next的加法器共有A、B、C0、S和C1,5组引脚,其中A、B和S为4位总线形式,所示。

因此设置结果如图F7所示。

F7点击“Next”,出现V erilog 新建信息汇总表。

实验一 ISE软件的基本操作与应用

实验一ISE软件的基本操作与应用一、实验目的:1、通过一个1位全加器的设计,熟悉ISE软件的基本应用。

2、掌握VHDL设计输入方法和测试基准波形文件输入方法。

3、熟悉ModelSim软件的基本应用,掌握功能仿真过程。

二、实验步骤:1、启动ISE集成开发环境,新建一个工程。

2、为工程添加设计源文件。

3、对源文件进行语法检查,并改正错误之处。

4、输入测试基准波形文件。

5、进行仿真,记录仿真结果。

6、检查仿真结果的正确性。

7、若仿真结果不正确,说明设计有错误(非语法错误,而是设计的功能不正确)。

修改设计源文件,重新仿真直至得到正确的结果。

三、实验原理:全加器的真值表输入输出cin ain bin sum cout0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1cinainbinsumcout半加器程序:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity my_banjq isPort ( a : in STD_LOGIC;b : in STD_LOGIC;co : out STD_LOGIC;so : out STD_LOGIC); end my_banjq;architecture Behavioral of my_banjq is beginco <=a and b;so <=a xor b;end Behavioral;或门程序:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity my_or isPort ( a : in STD_LOGIC;b : in STD_LOGIC;c : out STD_LOGIC);end my_or;architecture Behavioral of my_or isbeginc <= a or b;end Behavioral;全加器程序:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity my_fadder isPort ( ain : in STD_LOGIC;bin : in STD_LOGIC;cin : in STD_LOGIC;cout : out STD_LOGIC;sum : out STD_LOGIC);architecture Behavioral of my_fadder iscomponent my_banjqport(a,b: in std_logic;co,so: out std_logic);end component;component my_orport(a,b: in std_logic;c: out std_logic);end component;signal s1,s2,s3:std_logic;beginu1:my_banjq port map(a=>ain,b=>bin,co=>s1,so=>s2);u2:my_banjq port map(a=>s2,b=>cin,co=>s3,so=>sum);u3:my_or port map(a=>s1,b=>s3,c=>cout);end Behavioral;五、实验记录波形功能仿真波形时序仿真波形六、实验心得总的来说,这次实验还是很简单的,但是却花了大量的时间才完成。

实验一 ISE应用流程实验

实验一ISE应用基础实验ISE是指集成综合环境,本章通过一系列的实验,使学习者对ISE这一工具的应用有较为深刻的认识,并对FPGA的仿真与设计环境有深入的了解,为进一步的工作奠定基础。

ISE9.1 使用流程实验1. 实验背景知识:了解FPGA的实验、项目研发与设计流程,了解ISE软件在FPGA的项目设计的作用、组成部分和基本操作步骤。

2. ISE9.1 窗口图1-1 sources窗口在sources窗口“sources for”后有下拉菜单,编译时选择“Synthesis/Implementation”,仿真时选择“Behavioral Simulation”。

3. 实验目的(1)熟悉ISE9.1开发环境,掌握工程的生成方法;(2)熟悉SEED-XDTK XUPV2Pro实验与仿真设计的环境;(3)了解PicoBlaze 8-bit嵌入式微控制器特点。

4. 实验内容(1)创建工程;(2)添加HDL资源文件;(3)配置一个应用程序完成设计;(4)设计的仿真及实现。

5. 实验准备(1)将光盘下03. Examples of Program 实验程序目录下的01. ISE9.1文件夹拷贝到E:盘根目录下;(2)将USB下载电缆与计算机及XUPV2Pro板的J8连接好;(3)将RS232串口线一端与计算机连接好,另一端与板卡的J11相连接;(4)启动计算机后,将XUPV2Pro 板的电源开关SW11 打开到ON 上。

观察XUPV2Pro 板上的+2.5V,+3.3V,+1.5V 的电源指示灯是否均亮,若有不亮的,请断开电源,检查电源。

6.实验步骤(1)创建工程1)双击桌面Xilinx ISE9.1 快捷方式打开ISE 工程管理器(Project Navigator)。

2)打开Project Navigator 后,选择File → New Project ,弹出新建工程对话框;图1-2 ISE 工程管理器3)在工程路径中单击“…”按钮,将工程指定到如下目录,单击确定。

XIlinx公司ISE软件使用中文说明

十分钟学会ISE声明本系列文档、软件的版权为Digital Power Studio工作组所有。

Digital Power Studio工作组保留所有权利。

欢迎转载,但请保留这段版权声明;请勿用于商业用途。

Copyright (c) 2004, Digital Power Studio. All rights reserved.HistoryRevision Date Issuer NotesRelease1.0 Mar 3, 2005 Badfish First目录概述 (4)实验目的 (4)软件准备 (5)流程介绍 (5)新建项目: (5)编写和导入代码文件 (8)调用Modsim进行仿真 (11)约束文件 (13)综合与实现 (15)下载 (16)十分钟学会ISE 概述这个文档主要帮助大家熟悉利用ISE进行Xilinx公司FPGA代码开发的基本流程。

主要是帮助初学者了解和初步掌握ISE的使用,不需要FPGA的开发基础,所以对每个步骤并不进行深入的讨论。

本文介绍的内容从新建project一直到下载到硬件观察现象为止,涵盖整个开发过程。

考虑到我们的开发一般以Verilog HDL或VHDL为主,在本文中未介绍原理图输入工具和IP核使用工具等。

这同时是出于为了使文章脉络更清晰,让大家更快地学会ISE的考虑。

关于这些专用工具,可以参看HELP或者其他文档。

为了有个更直观的理解,我们需要一个实验平台,在本文中,采用的是Digital Power Studio工作组FPGA SPARK1.1综合开发平台的Xilinx标准型开发系统。

如图1所示(图中为Altera子板,只需改成Xilinx的即可)。

在该开发系统中,所采用的芯片是SPARTAN II系列的XC2S200。

可以参看/solution/fpgaspark.htm中对该系统的介绍。

图1 FPGA SPARK1.1 外观图实验目的在如上系统中右边有一个128×64带背光的点阵型液晶。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一 Xilinx_ISE 软件使用与计数器相关实验一、实验目的1.1了解并掌握采用可编程逻辑器件实现数字电路与系统的方法;1.2学习并掌握采用Xilinx_ISE 软件开发可编程器件的过程1.3学习使用verilog HDL描述数字逻辑电路与系统的方法;1.4掌握分层次、分模块的电路设计方法,熟悉使用可编程器件实现数字系统的一般步骤。

二、实验条件PC机Xilinx ISE13.1 软件USB下载线Digilent Adept软件(2.0或更新版)Xilinx大学计划开发板Basys2三、预习要求阅读实验原理及参考资料,了解使用Xilinx ISE13.1 软件开发Xilinx 可编程器件,设计实现所需电子系统的流程。

四、实验原理4.1 可编程器件开发流程4.2 Xilinx ISE13.1 软件概要介绍ISE 简要介绍Xilinx 是全球领先的可编程逻辑完整解决方案的供应商,研发、制造并销售应用范围广泛的高级集成电路、软件设计工具以及定义系统级功能的IP(Intellectual Property)核,长期以来一直推动着FPGA技术的发展。

Xilinx的开发工具也在不断地升级,目前的ISE Project Navigator 13.x 集成了FPGA 开发需要的所有功能,其主要特点有:•包含了Xilinx新型SmartCompile技术,可以将实现时间缩减 2.5 倍,能在最短的时间内提供最高的性能,提供了一个功能强大的设计收敛环境;•全面支持Virtex-5 系列器件(业界首款65nm FPGA);•集成式的时序收敛环境有助于快速、轻松地识别FPGA 设计的瓶颈;•可以节省一个或多个速度等级的成本,并可在逻辑设计中实现最低的总成本。

ISE Project Navigator 13.x的主要功能包括设计输入、综合、仿真、实现和下载,涵盖了FPGA 开发的全过程,从功能上讲,其工作流程无需借助任何第三方EDA 软件。

•设计输入:ISE 提供的设计输入工具包括用于HDL 代码输入和查看报告的ISE 文本编辑器(The ISE Text Editor),用于原理图编辑的工具ECS(The Engineering Capture System),用于生成IP Core 的Core Generator,用于状态机设计的StateCAD 以及用于约束文件编辑的Constraint Editor等。

•综合:ISE 的综合工具不但包含了Xilinx 自身提供的综合工具XST,同时还可以内嵌Mentor Graphics公司的LeonardoSpectrum 和Synplicity公司的Synplify,实现无缝链接。

•仿真:ISE 本身自带了一个具有图形化波形编辑功能的仿真工具HDL Bencher,同时又提供了使用Model Tech 公司的Modelsim进行仿真的接口。

•实现:此功能包括了翻译、映射、布局布线等,还具备时序分析、管脚指定以及增量设计等高级功能。

•下载:下载功能包括了BitGen,用于将布局布线后的设计文件转换为位流文件,还包括了ImPACT,功能是进行设备配置和通信,控制将程序烧写到FPGA 芯片中去。

•使用ISE 进行FPGA 设计的各个过程可能涉及到的设计工具如表4-1 所示。

4.3 使用Xilinx ISE13.1 软件开发可编程器件的流程介绍4.3.1 新建工程(1)开启ISE13.1软件: 开始→程序→Xilinx ISE Design Suite 13.1→ISE Design Tools→Project Navigator,会出现ISE13.1 的画面.(2)在ISE13.1 软件环境下,开启一个新的工程: File New Project.[Project Name] : lab1_4bitsLEDs[Project Location]: E:\Training\training_demo\Verilog\lab1_4bitsLEDs (依使用者设定的目录). [Top-Level Module Type] : HDL( 代表最上层的设计模块是以HDL方式实现的模块.图 4.3.1:创建新的工程(3)单击next,下一个画面就是设定硬件FPGA的参数---请对照实验板芯片系列进行选择![FPGA系列(Device Family)]:Spartan3E( 请看板子的FPGA FPGA的编号)[FPGA名称(Device)] : XC3S100E(请参考开发板的FPGA FPGA的编号)[FPGA包装(Package)]:CP132(请参考开发板的FPGA FPGA的编号)[FPGA速度等级(Speed)]: -4 ( FPGA 速度等级)[综合工具(Synthesis Tool)]:XST (VHDL/Verilog)[仿真器(Simulator)] : Isim(VHDL/Verilog)图 4.3.2:FPGA参数设置(4)点击next. 此时出现此项目所有设定的信息,若需重新设定,则可back. 若无误,则按finish图 4.3.3:工程设计信息4.3.2 创建新的Verilog源4.3.2.1 创建一个新的Verilog源文件(1)此时出现一个项目的框架,可以允许使用者开始进行项目的设计.(2)创建新的设计文件: Project New Source;选择Verilog Module,并设定文件名称为led图 4.3.4:选择源文件类型(3)点击next,出现New Source Wizard,设定此设计的输出输入信号.Clk : input (50m时钟输入信号).Reset : input (当Reset = ‘0’ 时,清除内部计数器)Led_out : Output (跑马灯输出信号),勾上Bus,MSB = 3 ,LSB = 0.图 4.3.5:定义模块(8)按next,再按finish;此时项目加入此模块之后,在Sourcees的窗口中会出现led.v 的编辑窗口.(9)在Project Navigator右边的工作区可以看到LED.v的文件内容,此时可以修改或改变设计内容,在修改完成之后,利用File Save来储存文件.(10)在撰写LED.v 内容之时,可以參考ISE所附的语言模板Language Template. 在本实验中我们需要了解计数器模块,点击软件界面上方的语言模板的快捷键,然后选择“Verilog _ Synthesis Constructs _ Coding Examples _ Counters”,然后选择所需的计数器类型以做参考。

实验代码如下:本实验中,时钟晶振为50m,为了能肉眼看到计数器的led灯闪烁,那么可以将计数器的高四位led_out[26:23]传递给led输出,频率变化大概在几赫兹。

如果需要加快或降低led灯的闪烁频率,则可以相应加大或减小计数器的位数。

4.3.2.2 编译检错并查看电路(1)双击Synthesize - xst进行编译纠错,以确认设计的正确与否。

(2)点开综合选项,双击View RTL Schematic,并选择Start with a schematic of the top-level block选项图4.3.6 选择RTL电路(3)点击OK,出现设计的整个电路模块图图 4.3.7 电路模块顶层模块(4)直接双击电路顶层,查看内部电路模块图 4.3.8 内部电路(5)如果需要查看设计内部具体有哪些实际资源组成,则可以点开综合选项,双击“view technology schematic”图 4.3.9 选择technology电路(6)点击OK,出现设计顶层图 4.3.10 顶层电路(7)直接双击顶层电路,则可以看到设计的内部电路是由哪些资源组成的。

图 4.3.11 内部电路(8)在Processes的窗口中,直接以鼠标双击Generate Programming File 的选项.此时ISE 会自动执行并产生可以下载的.bit 类型文件,此步骤是最直接验证设计工作的正确性与否.---可以等待仿真验证后再执行。

(9)若在每一个步骤后都出现绿色的打勾,代表程序成功跑完而没有错误和警告。

若有黄色的警告,一般可以忽略。

若有一个程序都出现红色打叉[X]的符号,代表有错误,可以依显示结果来侦错. ---可以等待仿真验证后再执行。

图 4.3.12:成功执行4.3.3 设计仿真在实际烧录FGPA之前,为了验证设计的正确性,可以先利用测试模板(Testbench)来验证设计的正确性。

在这里请注意一下,为了加快仿真进程,仿真时将counter的低4位传给led_out 以提高频率,更快地看到输出仿真结果。

这时,将代码led.v的第37行使能,第38行不使能,然后保存。

(1) 点击led HDL文件,创建一个新的测试平台源文件: Project New Source.在源文件向导里, 点击Verilog Test Fixture 作为源文件类型, 输入文件名称为test.图 4.3.13:选择源文件(2) 一直点击next,直到点击finish,自动生成test.v的测试模板,在此基础上编辑输入激励:时钟周期设定为10ns,复位信号为高持续500ns后,再将复位信号置低。

图 4.3.14:编辑输入激励(3) 保存test.v。

选择sources for Simulation图 4.3.15:选择仿真进程(4) 双击Simulate Behavioral Model ,ISE仿真器打开并开始仿真, ,将图形界面缩小到合适的界面,其仿真结果如图所示:图 4.3.16:仿真结果(5) 我们也可以查看设计的内部信号。

添加内部信号的步骤是: 在Isim的Instances and Processes窗口中点选test,然后点击UUT,在object窗口则会出现全部信号:图4.3.17:选择内部信号(6)拖动counter到仿真波形里,点击restart按钮,再点击run all按钮,运行一段时间后点击暂停,就可以看到内部信号仿真图。

为了查看方便,将二进制数改为10进制无符号数的形式,选择counter信号,点击右键选择radix扩展栏中的Unsigned Decimal,由图可知counter信号是在正确计数的。

图 4.3.18:添加了内部信号的仿真结果(7)关闭Isim仿真器并保存。

4.3.4 创建约束(1)设定I/O 脚的位置,可以利用LED.UCF 来设定I/O 脚的位置,以得到正确的输出文件. Project New Source. 设定输入的文件格式为Implementation Constraints File, 文件名称为led(自动储存为led.UCF)图 4.3.19:选择源文件(2)一直点击next,最后按finish(3)选择source for Implementation选项(4)点选Sourcees窗口内的led.ucf,点击processess窗口里的user constraints,双击edit constraints(txt),输入后储存文件. 其中,“LOC”代表管脚定义,相关管脚定义请参考实验板使用手册Basys2_rm.pdf或参照表4.3.1;“IOSTANDARD”代表电平标准,实验中设定为LVCMOS33;“SLEW”代表信号的翻转速率,有fast和slow之分,默认是slow,时钟信号clk 变化比较快可设定为fast。