基于FPGA的VHDL语言温度控制

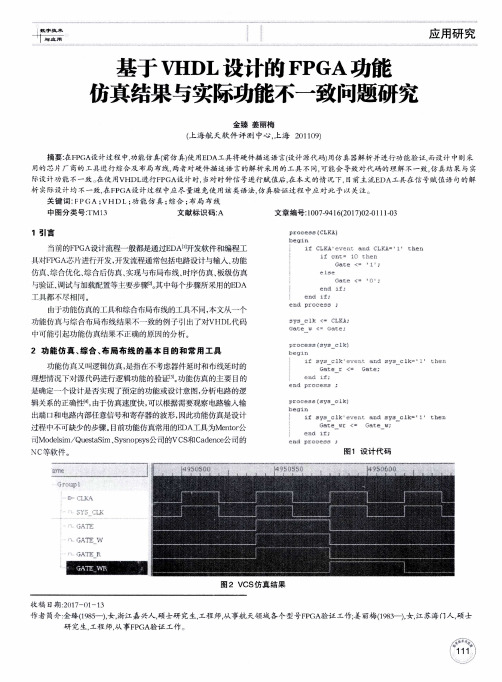

基于VHDL设计的FPGA功能仿真结果与实际功能不一致问题研究

图5 Ga t e — r 综 合 结 果

即 表 。 网表 文 件主 要 记 录 的是 所 用 工 艺 库 门级 单 元 之 间 的互 连 关 导致该时钟产生的信号用赋值后的时钟进行延时处理 时, 第一个节 系( 即门级结构) 。 而布 局布线则是对 表 中的每一个门级单元在器 拍 的延迟未起作用 , 仿真的信号 比实际信号在该处提前一个时钟周

n

一

0

窖

功能仿真 义叫逻辑仿真 , 是指在不考虑器 件延I t 寸 和布线延时的 理 想情 况下对源代码进行逻 辑功 能的验证l 3 】 。 功能仿真 的主要 目的 是确定一个设计是否实现了预定的功能或设计意 图, 分析 电路的逻 謇

A

L C d n 魏 矗 n e ~ , . l 。 f I ,

,

3 s

—

c lk <幸 CLKA;

s

G a te ;

一

G x e

l 0 e 一 ;

Gate

G 一

孽

C

2 功能仿真 、 综合 、 布局 布 线 的基 本 目的 和 常用 工具

≈

14

乞 肇

<

£ e

‘

; ,

i

k r

,都是通过E DA t I 开发软件和编程工 具; t C F P GA; 片进行开 发, 开发流程通常包括 电路设计与输入 、 功能

仿真、 综合优化 、 综合后仿真 、 实现与布局布线、 时序仿真 、 板级仿真

: r具都 小 尽相 同 。

j 验证 、 凋试 ! - - 5 J J 1 1 载配置等主要步骤 。 其 中每 个步骤所采用的E D A 触 e 0诺 p i b n K C 叫 _ L 1 w啦妇 f c 1 ; l e d n量 瞎1 : 畦 ; 巍 硅 哇 ; 3 0 r n e

基于vhdl的vivado使用流程

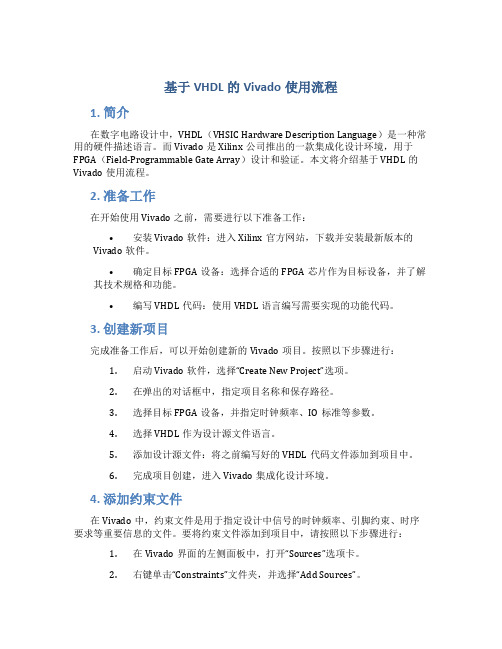

基于VHDL的Vivado使用流程1. 简介在数字电路设计中,VHDL(VHSIC Hardware Description Language)是一种常用的硬件描述语言。

而Vivado是Xilinx公司推出的一款集成化设计环境,用于FPGA(Field-Programmable Gate Array)设计和验证。

本文将介绍基于VHDL的Vivado使用流程。

2. 准备工作在开始使用Vivado之前,需要进行以下准备工作:•安装Vivado软件:进入Xilinx官方网站,下载并安装最新版本的Vivado软件。

•确定目标FPGA设备:选择合适的FPGA芯片作为目标设备,并了解其技术规格和功能。

•编写VHDL代码:使用VHDL语言编写需要实现的功能代码。

3. 创建新项目完成准备工作后,可以开始创建新的Vivado项目。

按照以下步骤进行:1.启动Vivado软件,选择“Create New Project”选项。

2.在弹出的对话框中,指定项目名称和保存路径。

3.选择目标FPGA设备,并指定时钟频率、IO标准等参数。

4.选择VHDL作为设计源文件语言。

5.添加设计源文件:将之前编写好的VHDL代码文件添加到项目中。

6.完成项目创建,进入Vivado集成化设计环境。

4. 添加约束文件在Vivado中,约束文件是用于指定设计中信号的时钟频率、引脚约束、时序要求等重要信息的文件。

要将约束文件添加到项目中,请按照以下步骤进行:1.在Vivado界面的左侧面板中,打开“Sources”选项卡。

2.右键单击“Constraints”文件夹,并选择“Add Sources”。

3.在弹出的对话框中,选择约束文件并添加到项目中。

4.在Vivado界面的左侧面板中,打开“Constraints”选项卡,确认约束文件已成功添加。

5. 进行综合和实现在Vivado中,综合是将HDL(硬件描述语言)代码和约束文件结合起来,生成逻辑网表的过程。

fpga设计中vhdl语言简介

fpga设计中vhdl语言简介

VHDL是一种硬件描述语言(HDL),旨在帮助工程师和设计师进行复杂电路和系统的设计和仿真。

VHDL语言是由美国国防部发起的,现在已经成为全球应用最广泛的HDL之一。

VHDL语言的基础包括三个部分:实体(entity)、体(architecture)和过程(process)。

实体定义组件的接口,在其内部,architecture结构体提供了具体的实现。

过程是编写复杂操作的基本方式,类似于C语言中的函数。

VHDL语言的数据类型包括标准逻辑类型,如布尔、位和字符类型,以及更复杂的数据类型,如数组和记录类型。

此外,VHDL也支持自定义数据类型。

在FPGA设计中,VHDL语言的主要作用是设计和实现可编程逻辑电路。

VHDL语言描述的电路可以在硬件上运行,也可以使用仿真器进行验证和测试。

总体而言,VHDL语言是一种强大的硬件描述语言,对于设计和实现复杂的电路和系统非常有用。

在FPGA设计中,VHDL语言是必不可少的一部分。

基于FPGA的测控系统设计与实现

基于FPGA的测控系统设计与实现一、引言随着科技的发展,现代工程领域对于高精度、高速度、高可靠性的测控设备的需求也越来越大。

其中,基于FPGA的测控系统具有极高的灵活性和可扩展性,能够满足不同领域的测控需求。

本文将介绍基于FPGA的测控系统设计与实现,主要包括系统架构、硬件设计、软件编程等方面。

二、系统架构设计基于FPGA的测控系统一般由FPGA芯片、外设模块、存储设备和通信接口等部分组成。

其中,FPGA芯片作为核心部分,负责控制整个系统的运行。

外设模块提供不同功能的接口,如模拟采集、数字转换、时钟输入、GPIO等。

存储设备用于存储测量数据和程序代码。

在系统架构设计时,需要根据实际需求选择适合的外设模块和通信接口,以及合适的存储设备。

此外,还需要考虑不同模块之间的数据传输和控制信号,确定系统的总体布局和数据流图。

三、硬件设计基于FPGA的测控系统的硬件设计主要包括电路原理图设计、PCB设计和硬件调试等部分。

在电路原理图设计时,需要根据系统架构设计绘制不同模块的电路图,并考虑电路参数的选择和优化。

在PCB设计时,需要将电路原理图转化为布局图和线路图,并按照标准的PCB设计流程进行布线、加强电路抗干扰性、防止电磁辐射等操作。

在硬件调试过程中,需要用示波器、万用表等工具对电路进行调试和测试,确保电路稳定运行。

四、软件编程基于FPGA的测控系统的软件编程主要包括FPGA芯片的Verilog/VHDL编程、上位机程序的编写等内容。

在FPGA芯片的Verilog/VHDL编程中,需要根据不同外设模块的接口来编写对应的硬件描述语言代码,如时钟控制、数据输入输出、状态控制等。

在上位机程序编写中,需要使用不同编程语言(如C/C++、Python等)来编写程序,实现与FPGA芯片的通信、测控算法的实现、数据可视化等功能。

五、系统应用与实现基于FPGA的测控系统应用广泛,如测量、控制、自动化、通信等领域。

在实际应用中,需要根据具体的应用场景和需求来设计相应的测控系统,并进行相关智能算法的设计和调试。

FPGA开发技术及VHDL语言

FPGA与CPLD的辨别和分类

④ CPLD的速度比FPGA快,并且具有较大的 时间可预测性。 ⑤ CPLD保密性好,FPGA保密性差。 ⑥一般情况下,CPLD的功耗要比FPGA大,且 集成度越高越明显。

FPGA与DSP的选择

DSP(digital singnal processor)是一种独 特的微处理器,有自己的完整指令系统,是以 数字信号来处理大量信息的器件。一个数字信 号处理器在一块不大的芯片内包括有控制单元 、运算单元、各种寄存器以及一定数量的存储 单元等等,在其外围还可以连接若干存储器 , 并可以与一定数量的外部设备互相通信, 有软、硬件的全面功能,本身就是一个微型计 算机。

FPGA技术与VHDL设计

南阳理工学院 计算机科学与技术系 通信工程教研室 路新华 Tel:62076343 Email:ieluxinhua@

课程学习内容

是什么 能做什么 怎么做 学习方法是什么 达到什么目标

一、是什么——概念

EDA:电子设计自动化 Electronic Design Automation

(

说明: (3)在RTL仿真阶段,应该建立一个测试台。此测

试台可以在整个FPGA流程中进行仿真验证(RTL级

、功能级、时序门级)。测试台不但提供测试激励

与接收响应信息,而且可以测试HDL仿真流程中的

关键功能(如运算部件输出值的正确性等)。

说明:

(

4)在功能级仿真阶段,一般验证综合后是

否仍与RTL级仿真结果相同。 (5)在门级仿真阶段,由于已经针对具体的 FPGA厂家技术进行了功能级仿真,因此可以 通过布局布线得到标准延格式下的时序信息 进行门级仿真。

一般地说,利用EDA技术进行电子系统设计,归纳起来主要 有以下4个应用领域:

基于FPGA智能温度传感器监控报警系统的设计

基于FPGA智能温度传感器监控报警系统的设计概述本文将详细介绍基于FPGA智能温度传感器监控报警系统的设计。

该系统由FPGA、温度传感器和报警器等组成,可以实时采集环境温度数据并进行处理,同时还可以根据设定的报警阈值进行温度报警。

该系统具有实时性、准确性和灵敏度高等优点,在工业、仓储等领域有广泛应用价值。

设计方案系统硬件设计智能温度传感器智能温度传感器采用DS18B20数字温度传感器,其精度高、体积小、响应速度快、使用方便等优点,能够满足系统的需要。

传感器输出数字量信号,可通过FPGA进行处理并转化为模拟量信号。

FPGAFPGA是本系统的核心部件,负责实现数字信号处理和温度阈值报警功能。

我们选用Xilinx Spartan-6系列FPGA,其具有高速、低功耗、可编程等特点,同时还有丰富的外设资源可以扩展。

报警器为了保证报警的及时和可靠性,我们使用了声光报警器,其能够在温度超出设定阈值时及时报警。

系统软件设计VHDL设计我们采用了VHDL语言对系统进行设计,通过其高级抽象、可移植性强等特点,实现了可适应性强、代码简洁的设计。

其中,数字信号处理主要包含数据的采集、过滤和频率变换等部分;温度阈值报警主要包含数据的计算和闸门控制等。

界面设计为了让用户更加便捷地使用该系统,我们设计了简洁明了的界面,包括温度值显示、报警阈值设置和报警状态等。

系统实现硬件实现按照上述设计方案,我们完成了硬件电路的设计,其中智能温度传感器采用了标准接口,与FPGA连接顺畅稳定。

报警器也能有良好的响应效果。

软件实现通过VHDL语言,我们完成了数字信号处理和温度报警部分的代码编写,在模拟器中进行了仿真和调试,并进行了综合和布局。

最终在FPGA平台上进行了验证,并与界面进行了充分交互。

结果分析经过系统实现,我们完成了一个基于FPGA智能温度传感器监控报警系统的设计。

在实际测试中,该系统具有所需的准确性、灵敏度和实时性等特点,能够实时采集环境温度并进行温度阈值报警。

《VHDL语言程序设计》课程教学大纲

《VHDL语言程序设计》课程教学大纲课程简介课程简介:本课程为软件工程专业嵌入式专业方向的专业课,是开发基于FPGA/CPLD嵌入式系统的必备基础。

主要内容包括FPGA/CPLD目标器件的结构和工作原理、EDA技术和工作流程、VHDL基础知识、VHDL实用方法和设计深入、原理图输入法、LPM宏功能模块实用方法、状态机设计以及EDA优化设计。

目的是为后续课程的学习和嵌入式系统的设计作必须的基础准备。

课程大纲一、课程的性质与任务:本课程是软件工程专业的专业方向课程。

教学任务主要包括使学生了解EDA技术的工作流程,正确使用开发平台,掌握以VHDL为代表的硬件描述语言的基本知识、编程实用方法和工程设计方法,掌握原理图设计法、状态机设计法,能够正确使用IP Core和LPM等宏功能模块。

本课程是软件工程专业嵌入式专业方向的第一门专业方向课,是后续课程的必备基础,具有较重要的地位。

二、课程的目的与基本要求:本课程涉及到的学科基础知识面广,要求软硬件兼备,需要较好的学科基础。

通过本课程的学习,最终达到能够设计基于FPGA/CPLD的ASIC,并能进行EDA优化的目的。

三、面向专业:软件工程四、先修课程:《计算系统基础》五、本课程与其它课程的联系:本课程的先行课程是计算系统基础。

服务的主要后续课程包括基于FPGA的嵌入式软件开发、基于ARM的嵌入式软件开发等。

六、教学内容安排、要求、学时分配及作业:第一章概述(2学时)1.1 EDA技术及其发展(C)1.2 硬件描述语言硬件描述语言种类、自顶向下设计方法、EDA工程设计流程。

(A)1.3 面向FPGA/CPLD的开发流程设计输入、分析综合、布局布线、仿真、下载和硬件测试。

(A)1.4 IP Core 及EDA技术发展趋势。

(C)第二章 FPGA硬件特性与编程技术(8学时)2.1 PLD发展历程及其分类(c)2.2 低密度PLD工作原理PROM、PLA、PAL、GAL。

《VHDL语言程序设计》课程教学大纲

GDOU-B-11-213《VHDL语言程序设计》课程教学大纲课程简介课程简介:本课程为软件工程专业嵌入式专业方向的专业课,是开发基于FPGA/CPLD嵌入式系统的必备基础。

主要内容包括FPGA/CPLD目标器件的结构和工作原理、EDA技术和工作流程、VHDL基础知识、VHDL实用方法和设计深入、原理图输入法、LPM宏功能模块实用方法、状态机设计以及EDA优化设计。

目的是为后续课程的学习和嵌入式系统的设计作必须的基础准备。

课程大纲一、课程的性质与任务:本课程是软件工程专业的专业方向课程。

教学任务主要包括使学生了解EDA技术的工作流程,正确使用开发平台,掌握以VHDL为代表的硬件描述语言的基本知识、编程实用方法和工程设计方法,掌握原理图设计法、状态机设计法,能够正确使用IP Core和LPM等宏功能模块。

本课程是软件工程专业嵌入式专业方向的第一门专业方向课,是后续课程的必备基础,具有较重要的地位。

二、课程的目的与基本要求:本课程涉及到的学科基础知识面广,要求软硬件兼备,需要较好的学科基础。

通过本课程的学习,最终达到能够设计基于FPGA/CPLD的ASIC,并能进行EDA优化的目的。

三、面向专业:软件工程四、先修课程:《计算系统基础》五、本课程与其它课程的联系:本课程的先行课程是计算系统基础。

服务的主要后续课程包括基于FPGA的嵌入式软件开发、基于ARM的嵌入式软件开发等。

六、教学内容安排、要求、学时分配及作业:第一章概述(2学时)1.1 EDA技术及其发展(C)1.2 硬件描述语言硬件描述语言种类、自顶向下设计方法、EDA工程设计流程。

(A)1.3 面向FPGA/CPLD的开发流程设计输入、分析综合、布局布线、仿真、下载和硬件测试。

(A)1.4 IP Core 及EDA技术发展趋势。

(C)第二章 FPGA硬件特性与编程技术(8学时)2.1 PLD发展历程及其分类(c)2.2 低密度PLD工作原理PROM、PLA、PAL、GAL。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的恒温控制系统孵化器是一种最新的孵化禽蛋的机器,通过人工制造适合禽蛋孵化的恒温环境,来以较小的经济投入孵化禽蛋,通过调查,市面上的孵化器多数是以模拟电路的方式制造恒温环境,如下图这种模拟电路控制在实际应用中很难做到恒温控制,温度会在最终归的预设值附近上下浮动,影响禽蛋的孵化。

而且,孵化器的温度设置也是模拟电路,这样是完全达不到精准的温度设置。

通过学习FPGA,我设想运用数字电路来对禽蛋孵化器内部温度进行控制,来实现可控,可调,温度恒定的禽蛋孵化器。

具体的设计框架如下通过前向温度采集电路,采集当前孵化器内部的温度信号,将采集到的模拟信号通过ADC0809模数转换芯片,转变为FPGA可控的数字信号,FPGA芯片根据输入的当前实际温度,控制输出合理的数字信号,再由DAC0832转换为模拟信号,输入到后向加热执行电路,以此来完成对整个孵化器的温度控制。

整个系统中,带有温度传感器的前向温度采集电路作为系统的反馈环节,实时反映当前环境的具体温度,具体的电路图如下。

前向温度采集电路图此电路设计以AD590作为温度触感器,通过添加相应的调节电阻,让温度与输出电压保持一个相对线性的关系其中: W1R 为调零电阻2w R 为调满度电阻最终得到的温度与输出电压的关系式为: 0U 5T 100 模数转换芯片采用的是ADC0809,具体的连接电路图如下IN0—IN7管角中任选一路作为前向温度采集电路的输入,VCC与VREF同时接+5V电压,_VREF与GND接地,OUT1—OUT8数据输出端连接FPGA,START,OE,EOC,ADDA-C均连接FPGA,根据ADC0809的工作时序图,由FPGA给出相应的信号控制ADC0809。

数模转换部分采用的是DAC0832,具体连接图如下DI0-DI7分别于FPGA的8位数据输出端相连,因为DAC0832工作在连续的负反馈电路中,故采用直通的工作方式,将WR1与WR2直接与地相连,ILE与CS,Xfer引脚均接至FPGA,有FPGA发送控制信号来控制DAC0832的工作。

输出引脚Iout1与Iout2连接一个流压转换器,将输出的电流信号转换为需要的电压信号,并进行适当的放大。

最后输出到孵化器的加热电路。

FPGA模块控制ADC0809的工作状态,并接收来自ADC0809的数字信号,与键盘输入的预设信号进行比较后,将控制信息传送给DAC0832,经由数模转换器转换后加在发热装置两端,对整个孵化器内部温度进行控制。

整个的FPGA模块分为以下几个部分;分频模块:由于外界的时钟源一般都较高,而ADC0809以及键盘扫描模块需要的时钟频率较低,故需要对外界时钟源进行分频,这里外界输入时钟源为20MHz,对其进行64分频。

波形仿真图如下:从波形图可以看出,clk每经过64个脉冲,clk1跳转一次。

分频模块工作正常;统计报告图如下:分频模块的VHDL 文件见附录1.键盘模块:键盘模块的脉冲输入来自分频模块。

其中,输入端口为两位二进制数,分别接两个按键,来对预设温度进行加减调控。

输出有两个端口,xianshi 端口作为保留端口,存储着当前预设温度的数值,可外接显示设备。

zhi 端口为信息传送端口,其存储值为当前预设温度值经由采集电路温度—电压公式换算后的十进制数值。

换算公式如下: 0U 5T 100 例:38摄氏度对应的ADC0809输出数据为5*38*256/100/5,得到十进制值为97;波形仿真图如下:图(1)图(2)图中,shuru(1)为温度减按键,shuru(0)为温度加按键,相应的预设温度对应相应的ADC0809输出值,由图2得,当预设温度为38摄氏度时,对应换算后的ADC0809输出数据为97,与计算相符。

键盘输入模块工作正常。

统计报告图如下:键盘模块的VHDL文件见附录2.ADC0809控制模块:经查阅资料,DAC0832需采用直通式,故,将DAC0832的控制语句直接写在了ADC0809的控制语句块内。

ile为输出到ADC0832的输入锁存允许信号,cont 为ADC0832WR1,WR2,CS等引脚。

Wendu为预设温度的输入引脚。

din为ADC0809转换后的输出信号,dout为受FPGA控制的输出到DAC0832的控制信号。

clk8为来自为频器的时钟信号。

根据ADC0809的时序图,总结出相应的状态转移图,一次来编写控制ADC0809的VHDL语言文件,状态转移图如下:具体波形仿真图如下:波形仿真建立在预设温度为38摄氏度的条件下。

前面提到,38摄氏度对应的ADC0809输出值为97,VHDL程序中设定,当ADC0809输入值大于或等于97时(当前温度大于或等于预设温度),FPGA输出到DAC0832的控制信号为0,即停止加热。

当ADC0809输入值小于92(即36摄氏度,与设定温度相差大于两度)时,FPGA 输出到DAC0832的控制信号为255,即以最大功率加热。

当ADC0809输入值小于92时,将会细分为5个阶段,即以逐次递减的功率加热。

由图可知,ADC0809工作正常。

统计报告图如下:ADC0809模块的VHDL仿真文件见附录3.最后,将三个模块运用元件例化语句连接在一块,并进行电路观察,生成相应的逻辑电路,如下图:总体波形仿真如下图波形分析:刚开始,FPGAjia置1,预设温度逐渐增加,如下图当温度到达38摄氏度后停止增加,即将38摄氏度作为预设温度,随后,观察FPGAin与FPGAout。

当预设温度为38摄氏度时,输入为97时,对应输出为0,当为92时,对应输出为5,当为96时,对应输出为1,当输入不在92-97之间,输入大于97时,输出为0,输入小与92时,输出为255.观察上图波形仿真,完全符合程序设计。

后面给FPGAjian置1,预设温度会随之降低。

统计报告图如下:总体的VHDL程序见附录4.附录1:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;entity fenpin isport(clk :in std_logic; --外部输入时钟源clk1: out std_logic);end fenpin; --分频后的时钟源architecture b of fenpin issignal count : std_logic_vector(7 downto 0); --信号定义signal clk2 : std_logic;beginprocess(clk)beginif(clk'event and clk='1') then --计数脉冲上升沿if(count="01000000") thencount<=(others=>'0');clk2<=not clk2; --当达到64个脉冲时count置0,clk2取反elsecount<=count+1; --未达到64脉冲时继续计数;end if;end if;clk1<=clk2; ——将产生的分频信号给输出端口end process;end b;附录2:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity jianpan isport(clk:in std_logic; --分频后的时钟输入shuru:in std_logic_vector(1 downto 0); --输入端,按键加0位,按键减1位zhi :out integer; --预设温度转化为ADC0809输出值xianshi :out integer); --当前预设温度end entity;architecture beha of jianpan issignal x:integer range 0 to 200; --定义信号beginprocess(clk)beginif(clk'event and clk='1') thencase shuru is --检测是否有输入when "01"=>x<=x+1; --按键加按下,温度+1when "10"=>if(x=0)then x<=0; --按键减按下,判断温度是否为0 else x<=x-1; --若为0,则依旧为0,否则,温度-1 end if;when others=>x<=x; --其他按键情况,温度不变end case;end if;xianshi<=x; --将温度赋给显示输出端zhi<=x*5*256/100/5; --将温度转化后赋给输出端end process;end beha;附录3:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity ADC0809 isport(din :in std_logic_vector(7 downto 0); --ADC0809输出的采样数据clk8 :in std_logic; --时钟信号eoc :in std_logic; --ADC0809转换结束指示,高电平有效ale :out std_logic; --ADC0809地址锁存次信号ile: out std_logic; --DAC0832数据锁存允许cont: out std_logic; --DAC0832控制信号(WR1,WR2,CS,Xfer)start :out std_logic; --ADC0809转换启动信号oe :out std_logic; --ADC0809数据输出允许信号wendu:in integer; --温度显示adda :out std_logic; --ADC0809信号通道控制位addb :out std_logic; --ADC0809信号通道控制位addc :out std_logic; --ADC0809信号通道控制位lock0 :out std_logic; --ADC0809观察数据锁存时钟dout :out std_logic_vector(7 downto 0)); --输出到DAC0832的8位数据end ADC0809;architecture beha of ADC0809 istype states is(st0,st1,st2,st3,st4); --定义ADC0809工作状态signal current_state,next_state:states:=st0; --定义信号signal regl :std_logic_vector(7 downto 0);signal shuchu :std_logic_vector(7 downto 0);signal lock :std_logic;signal count :std_logic_vector(7 downto 0);beginadda<='1'; --地址输入001,选择IN1 addb<='0';addc<='0';dout<=shuchu; -将处理后的数据传输到输出端口lock0<=lock; --数据传输ile<='1'; --DAC0832的控制信号cont<='0';com:process(current_state,eoc) --状态转移begincase current_state iswhen st0=>ale<='0';start<='0';lock<='0';oe<='0';next_state<=st1;when st1=>ale<='1';start<='1';lock<='0';oe<='0';next_state<=st2;when st2=>ale<='0';start<='0';lock<='0';oe<='0';next_state<=st1;if(eoc='1')then next_state<=st3;else next_state<=st2;end if;when st3=>ale<='0';start<='0';lock<='0';oe<='1';next_state<=st4;when st4=>ale<='0';start<='0';lock<='1';oe<='1';next_state<=st0;when others=>next_state<=st0;end case;end process com;reg:process(clk8)beginif(clk8'event and clk8='1')then current_state<=next_state; --在时钟上升沿改变状态end if;end process reg;latch1:process(lock)beginif lock='1'and lock'event then regl<=din; --将输入数据赋给中间变量end if;end process latch1;kongzhi:process(regl)beginif(regl<wendu) then --判断输入数据与预设温度的大小case wendu-regl is --判断输入数据与预设温度的when "00000101"=>shuchu<="00000101"; --差值为5时输出控制信号5when "00000100"=>shuchu<="00000100"; --差值为4时输出控制信号4when "00000011"=>shuchu<="00000011"; --差值为3时输出控制信号3when "00000010"=>shuchu<="00000010"; --差值为2时输出控制信号2when "00000001"=>shuchu<="00000001"; --差值为1时输出控制信号1when others=>shuchu<="11111111"; --差值大于5时输出255end case;else shuchu<="00000000"; --当前温度大于预设温度,输出0 end if;end process kongzhi;end beha;附录4:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity FPGA isport(clkin:in std_logic; --定义外部时钟端口FPGAeoc:in std_logic;FPGAin :in std_logic_vector(7 downto 0);FPGAout:out std_logic_vector(7 downto 0);FPGAale :out std_logic;FPGAjia :in std_logic;FPGAjian :in std_logic;FPGAwendu:out integer;FPGAile: out std_logic;FPGAcont: out std_logic;FPGAstart :out std_logic;FPGAoe :out std_logic;FPGAadda :out std_logic;FPGAaddb :out std_logic;FPGAaddc :out std_logic);end entity;architecture beha of FPGA iscomponent ADC0809 is --元件例化声明port(din :in std_logic_vector(7 downto 0);clk8 :in std_logic;eoc :in std_logic;ale :out std_logic;ile: out std_logic;cont: out std_logic;start :out std_logic;wendu:in integer;oe :out std_logic;adda :out std_logic;addb :out std_logic;addc :out std_logic;lock0 :out std_logic;dout :out std_logic_vector(7 downto 0));end component;component fenpin is --元件例化声明port(clk :in std_logic;clk1: out std_logic);end component;component jianpan isport(clk:in std_logic;shuru:in std_logic_vector(1 downto 0);zhi :out integer;xianshi:out integer);end component;signal c:std_logic; --定义中间变量signal n:integer;beginU0:fenpin port map(clk=>clkin,clk1=>c); --元件例化U1:ADC0809 port map(clk8=>c,wendu=>n,din=>FPGAin,eoc=>FPGAeoc,dout=>FPGAout,ale=>FPGAale,ile=>FP GAile,cont=>FPGAcont,start=>FPGAstart,oe=>FPGAoe,adda=>FPGAadda,addb=>FPGAaddb,addc=> FPGAaddc);U2:jianpan port map(clk=>c,shuru(1)=>FPGAjian,shuru(0)=>FPGAjia,zhi=>n,xianshi=>FPGAwendu);end beha;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;entity fenpin isport(clk :in std_logic; --外部输入时钟源clk1: out std_logic);end fenpin; --分频后的时钟源architecture b of fenpin issignal count : std_logic_vector(7 downto 0); --信号定义signal clk2 : std_logic;beginprocess(clk)beginif(clk'event and clk='1') then --计数脉冲上升沿if(count="01000000") thencount<=(others=>'0');clk2<=not clk2; -当达到64个脉冲时count置0,clk2取反elsecount<=count+1; --未达到64脉冲时继续计数;end if;end if;clk1<=clk2; ——将产生的分频信号给输出端口end process;end b;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity jianpan isport(clk:in std_logic; --分频后的时钟输入shuru:in std_logic_vector(1 downto 0); --输入端,按键加0位,按键减1位zhi :out integer; --预设温度转化为ADC0809输出值xianshi :out integer); --当前预设温度end entity;architecture beha of jianpan issignal x:integer range 0 to 200; --定义信号beginprocess(clk)beginif(clk'event and clk='1') thencase shuru is --检测是否有输入when "01"=>x<=x+1; --按键加按下,温度+1 when "10"=>if(x=0)then x<=0; --按键减按下,判断温度是否为0 else x<=x-1; --若为0,则依旧为0,否则,温度-1 end if;when others=>x<=x; --其他按键情况,温度不变end case;end if;xianshi<=x; --将温度赋给显示输出端zhi<=x*5*256/100/5; --将温度转化后赋给输出端end process;end beha;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity ADC0809 isport(din :in std_logic_vector(7 downto 0); --ADC0809输出的采样数据clk8 :in std_logic; --时钟信号eoc :in std_logic; --ADC0809转换结束指示,高电平有效ale :out std_logic; --ADC0809地址锁存次信号ile: out std_logic; --DAC0832数据锁存允许cont: out std_logic; --DAC0832控制信号(WR1,WR2,CS,Xfer)start :out std_logic; --ADC0809转换启动信号oe :out std_logic; --ADC0809数据输出允许信号wendu:in integer; --温度显示adda :out std_logic; --ADC0809信号通道控制位addb :out std_logic; --ADC0809信号通道控制位addc :out std_logic; --ADC0809信号通道控制位lock0 :out std_logic; --ADC0809观察数据锁存时钟dout :out std_logic_vector(7 downto 0)); --输出到DAC0832的8位数据end ADC0809;architecture beha of ADC0809 istype states is(st0,st1,st2,st3,st4); --定义ADC0809工作状态signal current_state,next_state:states:=st0; --定义信号signal regl :std_logic_vector(7 downto 0);signal shuchu :std_logic_vector(7 downto 0);signal lock :std_logic;signal count :std_logic_vector(7 downto 0);beginadda<='1'; --地址输入001,选择IN1 addb<='0';addc<='0';dout<=shuchu; --将处理后的数据传输到输出端口lock0<=lock; --数据传输ile<='1'; --DAC0832的控制信号cont<='0';com:process(current_state,eoc) --状态转移begincase current_state iswhen st0=>ale<='0';start<='0';lock<='0';oe<='0';next_state<=st1;when st1=>ale<='1';start<='1';lock<='0';oe<='0';next_state<=st2;when st2=>ale<='0';start<='0';lock<='0';oe<='0';next_state<=st1;if(eoc='1')then next_state<=st3;else next_state<=st2;end if;when st3=>ale<='0';start<='0';lock<='0';oe<='1';next_state<=st4;when st4=>ale<='0';start<='0';lock<='1';oe<='1';next_state<=st0;when others=>next_state<=st0;end case;end process com;reg:process(clk8)beginif(clk8'event and clk8='1')then current_state<=next_state; --在时钟上升沿改变状态end if;end process reg;latch1:process(lock)beginif lock='1'and lock'event then regl<=din; --将输入数据赋给中间变量end if;end process latch1;kongzhi:process(regl)beginif(regl<wendu) then --判断输入数据与预设温度的大小case wendu-regl is --判断输入数据与预设温度的when "00000101"=>shuchu<="00000101"; --差值为5时输出控制信号5when "00000100"=>shuchu<="00000100"; --差值为4时输出控制信号4when "00000011"=>shuchu<="00000011"; --差值为3时输出控制信号3when "00000010"=>shuchu<="00000010"; --差值为2时输出控制信号2when "00000001"=>shuchu<="00000001"; --差值为1时输出控制信号1when others=>shuchu<="11111111"; --差值大于5时输出255end case;else shuchu<="00000000"; --当前温度大于预设温度,输出0 end if;end process kongzhi;end beha;。