数字系统设计与PLD应用答案

数字系统设计hdl课后答案

数字系统设计hdl课后答案【篇一:数字系统设计与verilog hdl】ss=txt>(复习)eda(electronic design automation)就是以计算机为工作平台,以eda软件工具为开发环境,以pld器件或者asic专用集成电路为目标器件设计实现电路系统的一种技术。

1.电子cad(computer aided design)2.电子cae(computer aided engineering)3.eda(electronic design automation)eda技术及其发展p2eda技术的应用范畴1.3 数字系统设计的流程基于fpga/cpld的数字系统设计流程1. 原理图输入(schematic diagrams )2、硬件描述语言 (hdl文本输入)设计输入硬件描述语言与软件编程语言有本质的区别综合(synthesis)将较高层次的设计描述自动转化为较低层次描述的过程◆行为综合:从算法表示、行为描述转换到寄存器传输级(rtl)◆逻辑综合:rtl级描述转换到逻辑门级(包括触发器)◆版图综合或结构综合:从逻辑门表示转换到版图表示,或转换到pld器件的配置网表表示综合器是能自动实现上述转换的软件工具,是能将原理图或hdl语言描述的电路功能转化为具体电路网表的工具适配适配器也称为结构综合器,它的功能是将由综合器产生的网表文件配置于指定的目标器件中,并产生最终的可下载文件对cpld器件而言,产生熔丝图文件,即jedec文件;对fpga器件则产生bitstream位流数据文件p8仿真(simulation)功能仿真(function simulation)时序仿真(timing simulation)仿真是对所设计电路的功能的验证p9编程(program)把适配后生成的编程文件装入到pld器件中的过程,或称为下载。

通常将对基于eeprom工艺的非易失结构pld器件的下载称为编程(program),将基于sram工艺结构的pld器件的下载称为配置(configure)。

数字电路与系统设计课后习题答案

将下列各式写成按权展开式:()10=3×102+5×101+2×100+6×10-1()2=1×22+1×20+1×2-1+1×2-3()8=5×81+54×80+6×8-1()16=1×162+3×161+10×160+4×16-1+15×16-2按十进制0~17的次序,列表填写出相应的二进制、八进制、十六进制数。

解:略二进制数00000000~和0000000000~11分别可以代表多少个数?解:分别代表28=256和210=1024个数。

将下列个数分别转换成十进制数:(00)2,(1750)8,(3E8)16解:(00)2=(1000)10(1750)8=(1000)10(3E8)16=(1000)10将下列各数分别转换为二进制数:(210)8,(136)10,(88)16解:结果都为:()2将下列个数分别转换成八进制数:(111111)2,(63)10,(3F)16解:结果都为(77)8将下列个数分别转换成十六进制数:()2,(377)8,(255)10解:结果都为(FF)16转换下列各数,要求转换后保持原精度:解:()10=()10——小数点后至少取10位(0010 1011 0010)2421BCD=()2()余3循环BCD码=()2用下列代码表示(123)10,()2:解:(1)8421BCD码:(123)10=(0001 0010 0011)8421BCD()2=()10=(0001 0101)8421BCD(2)余3 BCD码(123)10=(0100 0101 0110)余3BCD()2=()10=(0100 1000)余3BCD已知A=(1011010)2,B=(101111)2,C=(1010100)2,D=(110)2(1)按二进制运算规律求A+B,A-B,C×D,C÷D,(2)将A、B、C、D转换成十进制数后,求A+B,A-B,C×D,C÷D,并将结果与(1)进行比较。

数字系统设计与PLD应用答案

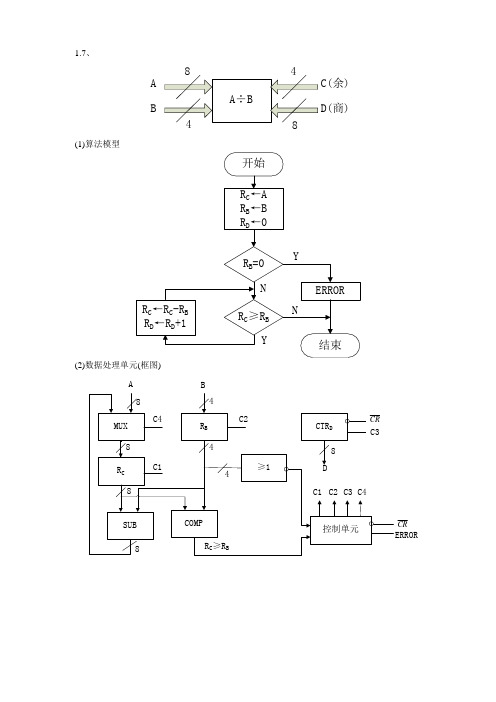

A BC(余)D(商)(1)算法模型(2)数据处理单元(框图)A B CR流水线操作结构:T S1=18*100+(256-1)*100=2.73*104(ns) 顺序算法结构:T S2=256*18*100=4.608*105(ns) 显然流水线操作时间短。

(若系统输入数据流的待处理数据元素为m 个,每一元素运算共计L 段,每段历经时间为Δ,则流水线操作算法结构共需运算时间为:T=L ·Δ+(m-1) Δ而顺序算法(或并行算法)结构所需运行时间为:m ·L ·Δ) 2.30、(1).DFF 状态编码A —000B —001C —010D —011E —100001101100010---XQ 1Q 0Q 201001101100100---XQ 1Q 0Q 20100110110000---Q 1Q 0Q 201D 2D 1D 0ZZ输出:XSETOU DOUT COUT BOUT AOUT QQ Q QQ QQQ QQQ Q QQ Q1212121212=====(2)“一对一”状态分配Q Q Q Q QE D C B A 4321-----次态表:激励方程:XZ XZ ZXX Z QQ D Q D QQ D QD Q Q QD 43413212142+==+==++=输出:X SETOU DOUT COUT BOUT AOUT Q Q Q Q Q=====3.2、试给出一位全减器的算法描述和数据流描述x—被减数y—减数bi—低位向本位的借位d—差bo—本位向高位的借位LIBRARY IEEE;USE IEEE.Std_Logic_1164.ALL;ENTITY full_sub ISPORT(x, y,bi : IN Std_Logic;d,bo : OUT Std_Logic);END full_sub;算法描述:ARICHITECTURE alg_fs OF full_sub ISBIGINPROCESS(x,y,bi)BEGINIF (x=…0‟ AND y=…0‟ AND bi=…0‟ OR x=…1‟ AND y=…0‟AND bi=…1‟ OR x=…1‟ AND y=…1‟ AND bi=…0‟ ) THENbo<=…0'; d<=…0‟;ELSIF (x=…1‟ AND y=…0‟ AND bi=…0‟ ) THENbo<=…0'; d<=…1‟;ELSIF (x=…0‟ AND y=…1‟ AND bi=…1‟ ) THENbo<=…1'; d<=…0‟;ELSEbo<=…1'; d<=…1‟;END IF;END PROCESS c1;END alg_fs;数据流描述:(d=x⊕y⊕bi bo=x’y+x’bi+ybi)ARICHITECTURE dataflow_fs OF full_sub ISBEGINd<=x XOR y XOR bi;bo<=(NOT x AND y) OR (NOT x AND bi)OR (y AND bi);END dataflow_ha;3.4、(1).十进制-BCD码编码器,输入、输出均为低电平有效。

数字PID控制算法答案共103页

1

0

、

倚

南

窗

以

寄

傲

,

审

容

膝

之

易

安

。

56、书不仅是生活,而且是现在、过 去和未 来文化 生活的 源泉。 ——库 法耶夫 57、生命不可能有两次,但许多人连一 次也不 善于度 过。— —吕凯 特 58、问渠哪得清如许,为有源头活水来 。—— 朱熹 59、我的努力求学没有得到别的好处, 只不过 是愈来 愈发觉 自己的 无知。 ——笛 卡儿

数字PID控制算法答案

6

、

露

凝

无

游

氛

,

天

高

风

景

澈

。

7、翩翩新 来燕,双双入我庐 ,先巢故尚在,相 将还旧居。8、吁嗟身后

名

,

于

我

若

浮

烟

。

9、 陶渊 明( 约 365年 —427年 ),字 元亮, (又 一说名 潜,字 渊明 )号五 柳先生 ,私 谥“靖 节”, 东晋 末期南 朝宋初 期诗 人、文 学家、 辞赋 家、散

文 家 。汉 族 ,东 晋 浔阳 柴桑 人 (今 江西 九江 ) 。曾 做过 几 年小 官, 后辞 官 回家 ,从 此 隐居 ,田 园生 活 是陶 渊明 诗 的主 要题 材, 相 关作 品有 《饮 酒 》 、 《 归 园 田 居 》 、 《 桃花 源 记 》 、 《 五 柳先 生 传 》 、 《 归 去来 兮 辞 》 等 。

拉

60、生活的道路一旦选定,就要勇敢地 走到底 ,决不 回头。 ——左

XXXXPLD习题集(含参考答案)数字系统设计

XXXXPLD习题集(含参考答案)数字系统设计第1章练习1.1名词解释可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程逻辑器件可编程采用HDL描述,自顶向下,开放标准,完整的设计库1.3。

什么是自顶向下的设计方法?(P4)1.4数字系统的实现是什么?每种方法的优缺点是什么?74LS系列/4000系列常规逻辑门的设计:设计困难,调试复杂。

采用可编程器件设计,如可编程逻辑器件/可编程门阵列。

HDL描述,设计难度小,调试和仿真方便,开发成本低,但单位成本高,适合应用专用集成电路设计的小批量应用:设计掩膜成本高,适合1.5大批量应用什么是IP复用技术?知识产权检查在EDA技术应用和发展中的意义是什么?(P5)IP是一种可重用的功能设计,可以节省设计时间,缩短开发周期,避免重复劳动,为大规模的片上系统设计提供开发基础和平台。

1.6用硬件描述语言设计数字电路有什么优点?的优点:可用于描述行为级、RTL级和门级电路,也可用于功能模拟时序分析,而不管过程如何。

1.8基于现场可编程门阵列/可编程逻辑器件的数字系统设计过程涉及哪些步骤?(P8图1.7)1.9什么是合成?什么是常见的综合工具?HDL?RTL?门的高度?1991.10年的功能模拟和计时模拟有什么不同?功能模拟不考虑器件延迟,但时序分析必须考虑不同器件中物理信号的延迟。

1.11数字逻辑设计描述分为几个层次并具有什么特征1.12,为什么任何组合逻辑电路都可以用通用“与”阵列或阵列组合来实现可以表示为布尔代数方程。

EDA 数字系统设计与PLD应用

6、 EDA设计工具与设计流程 、 设计工具与设计流程 设计工具 设计流程

8

设计准备

• 在对可编程逻辑器件的芯片进行设计之前,首先 要进行方案论证、系统设计和器件选择等设计准 备工作。设计者首先要根据任务要求,如系统所 完成的功能及复杂程度,对工作速度和器件本身 的资源、成本及连线的可行性等方面进行权衡, 选择合适的设计方案和合适的器件类型。 • 数字系统设计有多种方法,如模块设计法、自顶 向下设计法和自底向上设计法等。 • 自顶向下设计法是目前最常用的设计方法,采用 功能分割的方法从顶向下逐次进行划分。在设计 过程中采用层次化和模块化将使系统设计变得简 洁和方便。 • 描述器件总功能的模块放在最上层,称为顶层设 计;描述器件某一部分功能的模块放在下层,称 为底层设计;底层模块还可以再向下分层,这种 分层关系类似于软件设计中的主程序和子程序的 关系。 • 层次化设计的优点一是支持模块化,底层模块可 以反复被调用,多个底层模块也可以由多个设计 者同时进行设计,因而提高了设计效率;其次是 模块化设计比较自由,它既适合于自顶向下的设 计,也适合于自底向上的设计。 9

4

第一章、EDA技术概论 第一章、EDA技术概论

3、EDA技术的发展历程 EDA技术的发展历程

20 70 、 的 PCB 、 、 的 PC 、 的

1、CAD EDA 技 术 发 展 的 个 阶 段 3、EDA 3 2、CAE

CAE 20 80

、、、 技术 来自 PLD 发、 程RT Mentor Graphics、Valid Daisy

11

(4)布局和布线 • 布局和布线工作是在设计检验通过以后由软件自 动完成的,它能以最优的方式对逻辑元件布局, 并准确地实现元件间的互连。 (5)生成编程数据文件 • 设计处理的最后一步是产生可供器件编程使用的 数据文件。对CPLD来说,是产生熔线图文件, 即JEDEC文件(电子器件工程联合会制定的标 准格式,简称JED文件);对于FPGA来说,是 生成位流数据文件(Bitstream Generation), 简称BG文件

eda技术实用教程-veriloghdl答案

eda技术实用教程-veriloghdl答案【篇一:eda技术与vhdl程序开发基础教程课后答案】eda的英文全称是electronic design automation2.eda系统设计自动化eda阶段三个发展阶段3. eda技术的应用可概括为4.目前比较流行的主流厂家的eda软件有、5.常用的设计输入方式有原理图输入、文本输入、状态机输入6.常用的硬件描述语言有7.逻辑综合后生成的网表文件为 edif8.布局布线主要完成9.10.常用的第三方eda工具软件有synplify/synplify pro、leonardo spectrum1.8.2选择1.eda技术发展历程的正确描述为(a)a cad-cae-edab eda-cad-caec eda-cae-cadd cae-cad-eda2.altera的第四代eda集成开发环境为(c)a modelsimb mux+plus iic quartus iid ise3.下列eda工具中,支持状态图输入方式的是(b)a quartus iib isec ispdesignexpertd syplify pro4.下列几种仿真中考虑了物理模型参数的仿真是(a)a 时序仿真b 功能仿真c 行为仿真d 逻辑仿真5.下列描述eda工程设计流程正确的是(c)a输入-综合-布线-下载-仿真b布线-仿真-下载-输入-综合c输入-综合-布线-仿真-下载d输入-仿真-综合-布线-下载6.下列编程语言中不属于硬件描述语言的是(d)a vhdlb verilogc abeld php1.8.3问答1.结合本章学习的知识,简述什么是eda技术?谈谈自己对eda技术的认识?答:eda(electronic design automation)工程是现代电子信息工程领域中一门发展迅速的新技术。

2.简要介绍eda技术的发展历程?答:现代eda技术是20世纪90年代初从计算机辅助设计、辅助制造和辅助测试等工程概念发展而来的。

数字PID控制算法答案PPT103页

6、最大的骄傲于最大的自卑都表示心灵的最软弱无力。——斯宾诺莎 7、自知之明是最难得的知识。——西班牙 8、勇气通往天堂,怯懦通往地狱。——塞内加 9、有时候读书是一种巧妙地避开思考的方法。——赫尔普斯 10、阅读一切好书如同和过去最杰出的人谈话。——笛卡儿

Thank you

数字PID控制算法答案

36、“不可能”这个字(法语是一个字 ),只 在愚人 的字典 中找得 到。--拿 破仑。 37、不要生气要争气,不要看破要突 破,不 要嫉妒 要欣赏 ,不要 托延要 积极, 不要心 动要行 动。 38、勤奋,机会,乐观是成功的三要 素。(注 意:传 统观念 认为勤 奋和机 会是成 功的要 素,但 是经过 统计学 和成功 人士的 分析得 出,乐 观是成 功的第 三要素 。

数字系统设计和PLD应用

算法设计的几种方法

跟踪法: 就是按照已确定的系统功能,由控制要求,逐步细化,逐步具体化。从而导 出系统算法; 归纳法: 归纳法 就是先把比较抽象的设计要求具体化,而后再进行一般规律的归纳,由此 导出系统算法; 分解法: 分解法 即把一个比较复杂的系统,分解(划分)成一系列简单的运算,来完成系 统的复杂运算; 解析法: 解析法 对一些难以划分(分解)的计算过程,则可以用数学分析的方法对其进行 数值近似,转换成多项式,或者某种迭代过程,从而导出算法; 综合法: 综合法 就是把上述四种方法组合起来运用,综合的考虑,逐步导出系统的算法。

输入电路 控制电路 ……… 输出电路

受控电路1

受控电路n

时基电路

脉冲与数字电路课程的回顾

布尔函数--数字系统数学基础(卡诺 图) 数字电路设计的基本方法

组合电路设计 问题 逻辑关系 真值表 化简 逻辑图 时序电路设计 列出原始状态转移图和表 状态优化 状态分 配 触发器选型 求解方程式 逻辑图

使用中、小规模器件设计电路(74、54 系列)

判别块: 符号为菱形,块内 给出判别变量和判别条 件。判别条件满足与否, 决定系统下一步将进行 不同的后续操作。

00

A1 A0

.

10

01

F D0

F

D1

F D2

Cp

CNT M=3

D0 D1 D2 D3

MUX

F

条件块:

条件块为一带横杠的矩 形块。条件块总是源于判别 块的一个分支,仅当该分支 条件满足时,条件块中标明 的操作才被执行,而且是立 即被执行。

算法就是对这种有规律、有序分解的一 种描述。 任何一个系统都可以用算法模型进行描 述。

算法模型的特征: 含有若干子运算。 这些子运算实现对数据或信息的传输、存 储或加工处理; 具有相应的控制序列。 控制子运算按一定规律有序地进行。 用算法流程图来描述上述运算过程。

现代数字系统设计_习题集(含答案)

14.任Verilog HDL的端口声明语句中,用()关键字声明端口为双向端口

A:inout B:INOUT C:BUFFER D:buffer

15.IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为()。

A:8´b1111_1110 B:3´o276 C:3´d170 D:2´h3E

31.将设计的系统按照EDA开发软件要求的某种形式表示出来,并送入计算机的过程,称为()。

A:设计的输入B:设计的输出C:仿真D:综合

32.不属于PLD基本结构部分的是()。

A:与门阵列B:输入缓存C:与非门阵列D:或门阵列

C:原理图输入设计方法一般是一种自底向上的设计方法;

D:原理图输入设计方法也可进行层次化设计。

35.一般把EDA技术的发展分为()个阶段。

A:2 B:3 C:4 D:5

36.设a = 4´b1010,b=4´b0001,c= 4´b1xz0则下列式子的值为1的是()

A:a > b B:a <= c C:13 - a < b d:13 – (a>b)

A:查找表(LUT)C:PAL可编程B:ROM可编程D:与或阵列可编程

25.设计输入完成之后,应立即对文件进行()。

A:编译B:编辑C:功能仿真D:时序仿真

26.VHDL是在()年正式推出的。

A:1983 B:1985 C:1987 D:1989

27.基于EDA软件的FPGA / CPLD设计流程为:原理图/HDL文本输入→()→综合→适配→()→编程下载→硬件测试。①功能仿真②时序仿真③逻辑综合④配置⑤引脚锁定

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

A BC(余)D(商)(1)算法模型(2)数据处理单元(框图)A B CR2.17、流水线操作结构:T S1=18*100+(256-1)*100=2.73*104(ns) 顺序算法结构:T S2=256*18*100=4.608*105(ns) 显然流水线操作时间短。

(若系统输入数据流的待处理数据元素为m 个,每一元素运算共计L 段,每段历经时间为Δ,则流水线操作算法结构共需运算时间为:T=L ·Δ+(m-1) Δ而顺序算法(或并行算法)结构所需运行时间为:m ·L ·Δ) 2.30、(1).DFF 状态编码A —000B —001C —010D —011E —100001101100010---XQ 1Q 0Q 201001101100100---XQ 1Q 0Q 20100110110000---Q 1Q 0Q 201D 2D 1D 0ZZ输出:XSETOUDOUT COUT BOUT AOUT QQ Q QQ QQQ QQQ Q Q Q Q 01212121212=====(2)“一对一”状态分配Q Q Q Q QE D C B A 4321-----次态表:激励方程:XZ XZ ZXX Z QQ D Q D QQ D QD Q Q QD 43413212142+==+==++=输出:X SETOU DOUT COUT BOUT AOUT Q Q Q Q Q4321=====3.2、试给出一位全减器的算法描述和数据流描述LIBRARY IEEE;USE IEEE.Std_Logic_1164.ALL; ENTITY full_sub ISPORT(x, y,bi : IN Std_Logic;d,bo : OUT Std_Logic); END full_sub; 算法描述:ARICHITECTURE alg_fs OF full_sub IS BIGINPROCESS(x,y,bi) BEGINIF (x=‘0’ AND y=‘0’ AND bi=‘0’ OR x=‘1’ AND y=‘0’AND bi=‘1’ OR x=‘1’ AND y=‘1’ AND bi=‘0’ ) THENbo<=‘0'; d<=‘0’;ELSIF (x=‘1’ AND y=‘0’ AND bi=‘0’ ) THENbo<=‘0'; d<=‘1’;ELSIF (x=‘0’ AND y=‘1’ AND bi=‘1’ ) THENbo<=‘1'; d<=‘0’;ELSEbo<=‘1'; d<=‘1’;END IF;END PROCESS c1;END alg_fs;数据流描述:(d=x⊕y⊕bi bo=x’y+x’bi+ybi)ARICHITECTURE dataflow_fs OF full_sub ISBEGINd<=x XOR y XOR bi;bo<=(NOT x AND y) OR (NOT x AND bi)OR (y AND bi);END dataflow_ha;3.4、(1).十进制-BCD码编码器,输入、输出均为低电平有效。

LIBRARY IEEE;USE IEEE.Std_Logic_1164.ALL;ENTITY encoder ISPORT(a : IN Std_Logic_Vector(9 DOWNTO 0)b : OUT Std_Logic_Vector(3 DOWNTO 0));END encoder;ARCHITECTURE beh_encoder OF encoder ISBEGINWITH a SELECTb<= “0110” WHEN “0111111111”,“0111” WHEN “1011111111”,“1000” WHEN “1101111111”,“1001” WHEN “1110111111”,“1010” WHEN “1111011111”,“1011” WHEN “1111101111”,“1100” WHEN “1111110111”,“1101” WHEN “1111111011”,“1110” WHEN “1111111101”,“1111” WHEN “1111111110”,“0000” WHEN OTHERS;END beh_encoder;补充:优先编码器ENTITY encoder ISPORT(a : IN Std_Logic_Vector(9 DOWNTO 0)b : OUT Std_Logic_Vector(3 DOWNTO 0)); END encoder;ARCHITECTURE beh_encoder OF encoder IS BEGINWITH a SELECTb<= “0110” WHEN “0XXXXXXXXX”, “0111” WHEN “10XXXXXXXX”, “1000” WHEN “110XXXXXXX”, “1001” WHEN “1110XXXXXX”, “1010” WHEN “11110XXXXX”, “1011” WHEN “111110XXXX”, “1100” WHEN “1111110XXX”, “1101” WHEN “11111110XX”,“1110” WHEN “111111110X”, “1111” WHEN “1111111110”, “0000” WHEN OTHERS; END beh_encoder;(2).时钟RS 触发器。

QS CP RQLIBRARY IEEE;USE IEEE.Std_Logic_1164.ALL; ENTITY clk_rs_ff ISPORT(r,s,cp:IN Std_Logic; q,nq : BUFFER Std_Logic); END clk_rs_ff ;ARCHITECTURE beh_clkrsff OF clk_rs_ff IS BEGINASSERT NOT(r=‘1‘ AND s=‘1')REPORT"Control error" SEVERITY Error; PROCESS(r,s,cp) BEGINIF cp=‘1’ THENq<= s OR (NOT r AND q);nq<= NOT( s OR (NOT r AND q)); END IF; END PROCESS; END beh_clkrsff;(3).带复位端、置位端、延迟为15ns 的响应CP 下降沿的JK 触发器。

QQS CP J KENTITY jk_ff ISGENERIC (tpd:Time:=15 ns);FORT (r,s,j,k,cp:IN Std_Logic; q,nq:BUFFEER Std_Logic); END jk_ff;ARCHITECTURE beh_jkff OF jk_ff ISBEGINASSERT NOT(r='0‘ AND s='0')REPORT "Control error" SEVERITY Error;PROCESS(r,s,cp)BEGINIF r=‘0’ THENq<=‘0’ AFTER tpd; nq<=‘1’ AFTER tpd;ELSIF s=‘0’ THENq<=‘1’ AFTER tpd; nq<=‘0’ AFTER tpd;ELSIF (cp’Event AND cp=‘0‘) THENq<=j AND nq OR NOT k AND q AFTER tpd;nq<=NOT( j AND nq OR NOT k AND q) AFTER tpd;END IF;END PROCESS;END beh_jkff;(4).集成计数器74161。

LIBRARY IEEE;USE IEEE.Std_Logic_1164.ALL;USE IEEE.Std_Logic_Unsigned.ALL;ENTITY counter16 ISPORT (cr, ld, cp, ctt, ctp : IN Std_Logic;d : IN Std_Logic_Vector(3 DOWNTO 0);q : BUFFER Std_Logic_Vector(3 DOWNTO 0);co :OUT Bit);END counter16;ARCHITECTURE behav_ctr16 OF counter16 ISBEGINPROCESS (cr,cp)IF cr=‘0’ THENq<=“0000”;ELSIF (cp’Event AND cp=‘1’) THENIF ld=‘0’ THENq<=d;ELSIF (ctt=‘1’ AND ctp=‘1’) THENIF q=“1111” THENq<=“0000”;ELSEq<=q+“0001”;END IF;END IF;END IF;END PROCESS;co<=‘1’ WHEN (q=“1111” AND ctt=‘1’) ELSE ‘0’;END beh_ctr16;(5).集成移位寄存器74194。

LIBRARY IEEE;USE IEEE.Std_Logic_1164.ALL;ENTITY srg ISPORT(cr, cp : IN Std_Logic;d : IN Std_Logic_Vector(3 DOWNTO 0);sl, sr: IN Std_Logic;m: IN Std_Logic_Vector(1 DOWNTO 0);q: BUFFER Std_Logic_Vector(3 DOWNTO 0));END srg;ARCHITECTURE behav_srg OF srg ISPROCESS(cr, cp)BEGINIF cr=‘0' THENq<=“0000”; --异步复位ELSIF(cp’Event AND cp=‘1’) THENCASE m ISWHEN "01"=> q<=sr & q(3 DOWNTO 1); --右移WHEN "10"=> q<=q(2 DOWNTO 0) & sl; --左移WHEN "11"=> q<=d; --并行输入(同步预置)WHEN OTHERS=>NULL; --空操作,即保持END CASE;END IF;END PROCESS;END behav_srg;3.6、(2).由D触发器构成的异步二进制模8计数器Q0Q1Q2CPkLIBRARY IEEE;USE IEEE.Std_Logic_1164.ALL;ENTITY asyn_ctr8 ISPORT(cp : IN Bit;q : BUFFER Std_Logic_Vector( 2DOWNTO 0));END ctr8;ARCHITECTURE struct_ctr8 OF asyn_ctr8 ISCOMPONENT d_ff PORT (clk,d : IN Std_Logic; q,nq :OUT Std_Logic);END COMPONENT;SIGNAL nq0,nq1,nq2 : Std_Logic;BEGINff0: d_ff PORT MAP(cp,nq0,q(0),nq0);ff1: d_ff PORT MAP(q(0),nq1,q(1),nq1);ff2: d_ff PORT MAP(q(1),nq2,q(2),nq2);END struct_ctr8;4.3、一位全减器:输入为x(被减数)、y(减数)、bi(低位借位)、d(差)和bo(本位向高位的借位) (1).PROM实现:(2).PLA实现:d boxybid bo Xybi4.10、QQQQD QQQ Q Q Q Z Q Q Q Q D Q QQ Q Q Q Q Q Z QQQ Q D Q nn n nn n n nn n nn n n n 1201212121220121110121121212010+==+=+==++=+==+++状态转换图:000/01001/11011/00111/11110/10100/01010/00101/00Q 2Q 1Q 0/Z 2Z 1。