基于VerilogHDL简单CPU设计

基于RISC-VISA(RV32I)的CPU芯片设计

基于RISC-VISA(RV32I)的CPU芯片设计基于RISC-VISA(RV32I)的CPU芯片设计摘要:本文基于RISC-VISA(RV32I)指令集架构,探讨了CPU 芯片的设计问题。

首先详细介绍了RISC-VISA的指令集架构,分析了其与传统RISC和CISC指令集的异同点。

然后从CPU的整体设计、数据通路和控制模块等角度,分别进行了阐述和分析。

在具体实现方面,本文着重讲解了CPU的时序设计和Verilog HDL的实现。

最后通过仿真实验,验证了CPU的设计正确性和性能优势。

关键词:RISC-VISA、CPU芯片设计、指令集架构、数据通路、控制模块、时序设计、Verilog HDL1.引言随着信息技术的快速发展,CPU芯片作为计算机体系结构的核心,其性能和功耗问题越来越受到关注。

在此背景下,RISC-VISA(RV32I)指令集架构的提出,为CPU的设计与实现带来了新的思路和机遇。

本文基于RISC-VISA指令集架构,对CPU芯片的设计问题进行了探究和分析,旨在为读者提供实用的设计和实现方法。

2.RISC-VISA指令集架构RISC-VISA(Reduced Instruction Set Computing-VariableInstruction Set Architecture)是一种基于精简指令集(RISC)架构的新型指令集架构。

它的主要特点是指令集精简、可扩展性强、开放式设计和简洁明了的编码格式。

与传统的CISC(Complex Instruction Set Computing)指令集相比,RISC-VISA指令集具有更高的性能、更低的功耗和更强的可移植性。

3.CPU芯片的设计(1)整体设计CPU芯片的整体设计包括模块划分、总线设计、存储器设计等方面。

在模块划分方面,本文采用了经典的五级流水线结构,包括取指、译码、执行、访存和写回五个阶段。

在总线设计方面,本文采用了AMBA总线协议,以保证CPU与外部器件之间的高速数据传输。

MIPS架构多周期CPU的设计

MIPS架构多周期CPU的设计蔡晓燕;袁春风;张泽生【摘要】针对教育部最新提出的计算机专业系统结构课程设置要求,分析利用VerilogHDL代码完成多周期CPU设计的具体过程和方案,以南京大学计算机科学与技术系为例,总结将其应用在教学上的效果。

提出在计算机专业本科教学阶段可进行计算机组成与设计相关实践课程教学的观点。

【期刊名称】《计算机教育》【年(卷),期】2014(000)017【总页数】4页(P93-96)【关键词】MIPS架构;多周期;数据通路;状态图【作者】蔡晓燕;袁春风;张泽生【作者单位】南京大学计算机科学与技术系江苏南京 210046;南京大学计算机科学与技术系江苏南京 210046;南京大学计算机科学与技术系江苏南京210046【正文语种】中文【中图分类】G642近年来,教育部计算机专业教学指导委员会组织了对该专业学生能力培养和实践教学体系的研究。

研究指出,教学必须树立系统观,培养学生的系统眼光。

使学生学会在不同层面把握不同层次的系统,并全面考虑系统各部分与外界的逻辑与联系,能够完成一定规模的系统设计[1]。

研究还指出,有了计算机系统基础和计算机组成与设计课程的基础,学生将更容易从计算机系统整体角度理解操作系统、编译原理等后续课程[1]。

研究确定以MIPS为模型机进行讲解,讲透原理,强化实践。

MIPS架构的微处理器是最简单的体系结构之一,作为一种开放的架构,用户可自行开发MIPS内核,并在其中添加指令。

MIPS架构被国际上许多著名大学用于计算机系统结构的本科生和研究生教学。

CPU结构由其所能够执行的指令决定,MIPS 32位架构是一种采用RISC(精简指令集)的处理器架构,它指令长度固定,采用load/store数据模型,算术和逻辑运算采用三目操作数的形式,带有32个通用寄存器[2-3]。

自2007年起开始,南京大学计算机科学与技术系开始探索用Verilog HDL代码实现MIPS架构多周期CPU设计。

单周期CPU及其Verilog_HDL实现概要共94页文档

36、自己的鞋子,自己知道紧在哪里。——西班牙

37、我们唯一不会改正的缺点是软弱。——拉罗什福科

xiexie! 38、我这个人走得很慢,但是我从不后退。——亚伯拉罕·林肯

39、勿问成功的秘诀为何,且尽全力做你应该做的事吧。——美华纳

40、学而不思则罔,思而不学则殆。——孔子

单周期CPU及其Verilog_HDL实现概 要

1、纪律是管理关系的形式。——阿法 纳西耶 夫 2、改革如果不讲纪律,就难以成功。

3、道德行为训练,不是通过语言影响 ,而是 让儿童 练习良 好道德 行为, 克服懒 惰、轻 率、不 守纪律 、颓废 等不良 行为。 4、学校没有纪律便如磨房里没有水。 ——夸 美纽斯

5、教导儿童服从真理、服从集体,养 成儿童 自觉的 纪律性 ,这是 儿童道 德教育 最重要 的部分 。—— 陈鹤琴

谢谢!

自己动手写CPUOpenMIPS教学版讲解主要内容

指令wishbone接口 OpenMIPS 数据wishbone接口

iwishbone

dwishbone

m0

WB_CONMAX

s0

s1

s2

s3

SDRAM Controller

UART Controller

GPIO Controller

FLASH Controller

•《自己动手写CPU》OpenMIPS教 学版讲解主要内容

四 OpenMIPS教学版的文件组织

asm_test

包括所有的测试例程,其组织方式是参照《10天实现 处理器——OpenMIPS成长记》一文,按照“天”来组织, 比如Day2文件夹中存放的是《10天实现处理器—— OpenMIPS成长记》一文中第二天对应的测试例程,当 然所有的测试例程都可以在最终的OpenMIPS中进行测 试

•《自己动手写CPU》OpenMIPS教 学版讲解主要内容

四 OpenMIPS教学版的文件组织

rtl

所有OpenMIPS的源代码文件在该文件夹下,包括

流水线文件iu.vhd 除法模块div.vhd 寄存器文件Reg 顶层文件OpenMIPS.vhd 宏定义文件stdlib.vhd

•《自己动手写CPU》OpenMIPS教 学版讲解主要内容

一 OpenMIPS项目简介

OpenMIPS是采用具有哈佛结构的32位标量处理器,兼容 MIPS32体系结构,这样可以使用现有的MIPS编译环境。

具有以下特点:

五级整数流水线,分别是:取指、译码、执行、访存、 回写

哈佛结构,分开的指令、数据接口

32个32位整数寄存器

大端模式

向量化异常处理,支持精确异常处理

•《自己动手写CPU》OpenMIPS教 学版讲解主要内容

第5章单周期CPU及其Verilog HDL设计

op 6 bits

rs 5 bits

rt 5 bits

rd 5 bits

sa 5 bits

funct 6 bits

I Format

31

(rs, rt: Register Numbers, imm: Immediate)

26 25 21 20 16 15 0

时钟上升沿(0到 1的变化) 一个周期

Clock

下降沿

指令1

指令2

指令3

指令4

在时钟上升沿保存指令的结果和下一条指令的地址

c

5.1 执行指令所需的硬件电路

• 指令的执行过程

取指令 执行指令

—读取指令

程序计数器的值作为地址从存储器中 取指令 形 成 下 一 条 指 令 地 址

—分析指令 —按指令规定内容执行指令 —检查有无中断请求

c

取指部件(Instruction Fetch Unit)

• 每条指令都有的公共操作

– 取指令: M[PC] – 更新PC:PC ← PC + 4

转移(Branch and Jump)时,PC内容再次被更新为 “转移目标地址 ” 下地址 逻辑

Next Address Logic Address Instruction Word

rs rt P C a do Inst mem

we rna

rnb qa wn Regfile d clk qb b ALU

rd

a

aluc z r

clock

c

Sll指令 (Shift Left Logical)

sll rd, rt, sa ; rd <-- rt << sa

电子科技大学CPU设计:《单周期CPU的设计与实现》-实验指导书

电子科技大学计算机科学与工程学院单周期CPU的设计与实现实验指导书[计算机组成原理实验]张建2013-12-13目录前言 (1)1.1 实验内容 (2)1.2实验要求 (2)2. 实验环境 (3)2.1 硬件平台 (3)2.2 软件平台 (3)2.3 实验主要仪器设备连接框图 (4)3. 实验原理 (5)3.1 概述 (5)3.2 单周期CPU的总体电路 (5)3.3 MIPS指令格式 (6)3.4 数据路径设计 (7)3.4.1 下一条指令地址的选择 (7)3.4.2 ALU的输入端 (8)3.4.3寄存器堆的输入端 (8)4. 基本功能部件的设计与实现 (10)4.1 32位2选1选择器的设计与实现 (10)4.2 32位4选1选择器的设计与实现 (18)4.3 5位2选1选择器的设计与实现 (19)4.4 带有异步清零的32位D触发器的设计与实现 (19)4.5 移位器的设计 (20)4.6 32位加/减法器的设计与实现 (20)5.运算器(ALU)的设计与实现 (21)6.寄存器堆(Register File)的设计与实现 (24)7.控制器(Control Unit)的设计与实现 (27)8. CPU的封装 (30)9. 测试 (32)9.1 指令存储器及测试程序 (32)9.2 数据存储器及测试数据 (33)9.3 仿真测试 (33)9.4 下载到开发板验证 (35)附件: (39)BTN_Anti_Jitter模块 (39)Hex7seg_decode模块 (39)前言《计算机组成原理》是计算机科学专业的一门重要专业基础课。

在该课程中的理论学习中系统地阐述了计算机各组成部件的工作原理、逻辑实现和设计方法及将各部件连接成整机的方法,计算机硬件与底层软件的接口,培养了学生对计算机硬件系统的分析、开发与设计的基本技能能力。

本实验开设的目的是让学生通过设计一个单周期的CPU,加深对计算机各组成部件功能的理解和掌握,更好地理解计算机的基本工作原理,培养和锻炼学生掌握计算机硬件设计的基本方法和技能。

VerilogHDL数字系统设计——原理、实例及仿真作者康磊第8-13章第11章

4

冯· 诺依曼结构的处理器使用同一个存储器,经由同一个 总线传输,具有以下特点: (1) 结构上由运算器、控制器、存储器和输入/输出设备 组成。 (2) 存储器是按地址访问的,每个地址是唯一的。 (3) 指令和数据都是以二进制形式存储的。 (4) 指令按顺序执行,即一般按照指令在存储器存放的顺 序执行,程序的分支由转移指令实现。

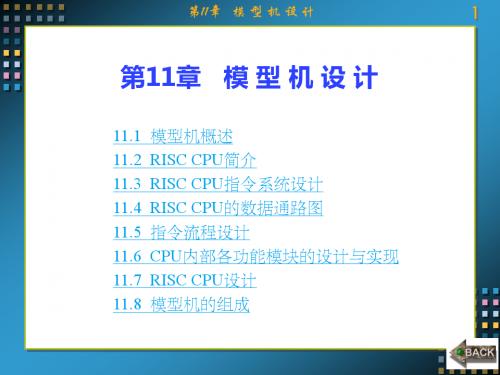

第11章 模 型 机 设 计

2

教材其余课件及动画素材请查阅在线教务辅导网 在线教务辅导网:

QQ址:

第11章 模 型 机 设 计

3

11.1 模 型 机 概 述

第11章 模 型 机 设 计

1

第11章 模 型 机 设 计

11.1 11.2 11.3 11.4 11.5 11.6 11.7 11.8 模型机概述 RISC CPU简介 RISC CPU指令系统设计 RISC CPU的数据通路图 指令流程设计 CPU内部各功能模块的设计与实现 RISC CPU设计 模型机的组成

(5) 以运算器为中心,在输入输出设备与存储器之间的数

据传送都途经运算器。运算器、存储器、输入输出设备的操 作以及它们之间的联系都由控制器集中控制。

第11章 模 型 机 设 计

5

哈佛结构使用两个独立的存储器模块,分别存储指令和 数据,并具有一条独立的地址总线和一条独立的数据总线, 具有以下特点: (1) 每个存储模块都不允许指令和数据并存,以便实现并 行处理。

CPU是计算机系统中最为重要的组成部分,它在计算机

系统中负责信息的处理和控制,因而被人们称为计算机的大 脑。CPU和外围设备构成计算机。模型机是一个简单的计算 机硬件系统,可以实现计算机的基本功能。 计算机的体系结构可分为两种类型:冯· 诺依曼结构和哈 佛结构。大多数CPU采用冯· 诺依曼结构。

基于硬件描述语言的简易CPU设计

基于硬件描述语言的简易CPU设计肖海燕;杨建波【摘要】Based on FPGA, the hardware description language Verilog and the top-to-down design method of modularization are adopted to achieve the design of a simple CPU logic controller, in which the software design and simulation are conducted for each module of CPU, and then each module is synthesized. The principle analysis is performed for the key function modules of CPU. The time-sequence simulation diagrams are given by means of compilation and adaptation with software MAX+plus II. The water lamp controlled by simple instructions was implemented by using the hardware device. The complete design of simple CPU based on Verilog was accomplished. This design has a strong flexibility and reliability. The CPU can achieve more functions as long as extending or amending the instructions appropriately.%基于可编程逻辑器件FPGA,利用Verilog硬件描述语言,采用自顶向下和模块化的设计方法,先将CPU的每个模块进行软件设计与仿真,再将每个模块综合起来,设计并验证了一种简单CPU逻辑控制器.对CPU关键功能模块进行了原理分析,并通过Max+-PlusⅡ软件编译适配,给出了时序仿真图.同时在硬件上实现了简单指令控制的流水灯实例,完成了完整的Verilog硬件描述语言的简易CPU设计.该设计具有很强的灵活性与可靠性,只要适当扩展或修改指令集就可以使CPU实现更多的功能.【期刊名称】《现代电子技术》【年(卷),期】2011(034)022【总页数】4页(P178-181)【关键词】FPGA;Verilog;CPU;时序仿真【作者】肖海燕;杨建波【作者单位】湖北师范学院物理与电子科学学院,湖北黄石435002;湖北师范学院物理与电子科学学院,湖北黄石435002【正文语种】中文【中图分类】TN710-34;TP2820 引言随着系统级FPGA 及系统芯片的出现,软、硬件协调设计和系统设计变得越来越重要。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于VerilogHDL的简单CPU设计

摘要:本文实现了一个基于veriloghdl的简单cpu,系统由运算器、控制器、译码器、存储器、指令计数器五大模块构成。

在对各个模块时序仿真实验的基础上,系统整体功能测试成功。

系统具有良好的稳定性和灵活性,指令集易扩展。

关键词:veriloghdl;cpu;时序仿真

中图分类号:tp334

1 引言

veriloghdl【1】是一种硬件描述语言(hdl:hardwarediscriptionlanguage),是一种以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

由于verilog接近c语言的语言规则,适合进行fpga的开发和教学工作,得到了广泛的应用。

本文基于对cpu的研究,设计并实现了一个基于verilog的简单cpu,并成功进行了仿真实验。

2 cpu的功能和结构

2.1 cpu的功能

本cpu模型由五大部分组成,分别是运算器、控制器、译码器、存储器、指令计数器。

实现了一个简单指令集,包括停机指令,加,减,与,加载,存储等指令。

同时能进行数据的存储和管理【2】。

2.2 cpu的结构

图2.2.1 cpu的架构图

cpu的整体结构如上面两个图所示,各个模块协调工作,共同完成cpu的每一次任务。

指令格式为“op+0+opd1+opd2”其中op为3位操作码,0为固定位(或者说是没用的一位),opd1,opd2为6位操作数的地址(之前已经写入内存)。

寻址方式固定为立即数寻址。

3 cpu主要模块的实现

3.1 运算器模块alu

算术逻辑运算单元alu。

根据输入的6种不同操作码分别实现相应的加、减、与、加载,存储,停机等6种基本操作运算。

利用这几种基本运算可以实现很多种其它运算以及逻辑判断等操作:(1)hlt停机操作。

该操作将空一个指令周期,即6个时钟周期;(2)add相加。

该操作将取存储器中的两个数据相加;(3)and相与。

该操作将存储器中的两个数据相与;(4)sub相减。

该操作将存储器中的两个数据相减;(5)lda读数据。

该操作将指令中给出地址的数据放入累加器;(6)sta写数据。

该操作将数据写入内存。

3.2 控制器模块control

控制器模块【4】对整个cpu的工作进行控制,决定本次任务要执行什么样的操作。

s0,s1,s2,s3,s4,s5分别控制指令运行中的各个步骤,其中s0有效时取指令,s1有效时译码,s2有效时从内存中读数据,s3有效时启动alu进行运算,s4有效时写数据入内存,s5有效时pc

加1。

即这几个输出控制一条指令的整个执行过程。

addsel是用于决定数据的地址来自哪里,为1时从存储器中取数,为0时地址来与pc.add_en,sub_en,and_en,pass_en为使能信号控制所进行的操作。

由输入的opcode决定。

3.3 译码器encoder和存储器memory

译码器能够将代码特定的含义翻译出来,将操作数和操作码分离开来,以完成不同的工作。

存储器主要实现:从存储器中读出数据,和将数据写入内存的功能。

wr为写控制端,有效时,把数据写入指定的存储器单元。

rd为读控制端,当有效时,从指定存储单元读数据。

addr为写入或者读出数据的地址。

drout和grout为把数据读出写入到dr,gr的端口。

4 系统仿真测试

4.1 系统仿真方案

系统测试代码如下:

lda001010001011

把10和11地址数据加载到gr和dr中

add001010001011

把10和11地址里面的数字相加送到gr

sta001100

把gr里面的值存入12地址

sub001010001011

把10和11地址里面的数字相减送到gr

sta001101

把gr的值存入13地址

and001010001011

把10和11地址里面的数字相与送到gr

sta001110

把gr的值存入14地址

halt停止一个周期

lda001100001101

把12和13地址数据加载到gr和dr中

lda001110

把14地址里面的内容加载到gr

4.2 测试结果

经过时序仿真,我们观察内存中121314这三个地址中数据的变化即可得出指令是否正确执行。

测试结果是正确的,系统仿真成功。

5 结束语

veriloghdl作为fpga开发的优势越来越被人们接纳,本文实现了一个简单地cpu模型,并进行了成功的仿真实验。

系统具有良好的稳定性和灵活性,指令集易扩展。

参考文献:

[1]潘松,黄继业.eda技术实用教程[m].北京:科学出版社.

[2]王爱英.计算机组成与结构[m].北京:清华大学出版.

[3]肖海燕,杨建波.基于硬件描述语言的简单cpu[j].现代电子技术,2011(22):178-181.

[4]周宁宁,刘胜.基于fpga技术的cpu模型机的设计与实现[j].南京邮电学院学报,2003(1):77-80.

作者简介:刘明达(1991.09.11-),男,山东,本科在读,fpga 开发、密码学;刘晓洁(1992.2-),广东揭东,本科在读,密码学。

作者单位:武汉大学计算机学院,武汉 430072。