16位加法器设计报告

数字设计 组合逻辑电路 BCD加法器课程设计报告

使用芯片 74x283、 74x157 及与、 或、 非门器件设计一个电路, 实现 16 位 BCD 加法运算。 画出电路逻辑图,并用 Verilog HDL 进行仿真。 注: 74x283 是 4 位二进制先行进位加法器,输入端有:Cin、A[3:0]、B[3:0]; 输出端有: Cout、S[3:0]; 其功能大致可以表示为:{Cout,S}=A+B+Cin 74x157 为多路复用器,输入端有:S、A[3:0]、B[3:0];输出端有:Y[3:0]; 其功能为:Y=S’·A+S·B

此次课程设计是本人第一次独立完成的一个比较完整的项目它集筛选提出问题需求分析提出设计方案可行性分析确定设计方案实现仿真检验等于一体是对人综和素质的检验和锻炼

电 子 科 技 大 学

数 字 电 路 课 程 设 计 报 告

姓名:

张华博

学号:2011091010004

选课号:

132

指导老师:

张刚

组合逻辑电路课程设计

总结: 此次课程设计是本人第一次独立完成的一个比较完整的“项目” ,它集筛选(提出) 问题、需求分析、提出设计方案、可行性分析、确定设计方案、实现、仿真检验等于一体, 是对人综和素质的检验和锻炼;学习关于电子设计的相关课程(电路分析、模拟电路、数字 设计)已经有一年半的时间了,期间就只是做题和简单的仿真,觉得不过如此,挺简单的。 但纸上得来终觉浅, 虽然这只是一个很简单的设计, 真正要动手的时候才发现不知该如何下 手,几经辗转才了解电子设计的诸多流程。 设计完成后,就要开始进行仿真了。要用到 quartus II 软件,就需要自学软件操作,上 网搜教程掌握基本操作,翻课本找程序学习 Verilog HDL;虽然有些困难,总是出现这样那 样的问题,但,是问题总有解决的办法,通过学习,看着问题一个一个的被解决掉,这才发 现自主学习是多么快乐的一件事, 每解决一个问题, 就会增加一份成就感! 这比让老师逼着、 管着去学效果要好的多,并且经过这次课程设计之后,我比以前更喜欢数字设计这门课了! 总的来说,这次课程设计使我受益匪浅,使我分析问题的思路更清晰、目的更明确、 解决方法更娴熟。虽然仿真程序还可简化改进,但是鉴于下午就要交报告,时间有点仓促, 所以在此就不再赘言,课下我会略加改进。

EDA-16位加法计数器的设计

EDA-16位加法计数器的设计北京理工大学用程序输入方法设计一个16位二进制加法计数器学院:机械xxxx学院专业班级:10机械电子工程x班姓名:陈xx学号: 10xxxxxx指导教师:xxx 老师目录摘要 (1)1 绪论 (2)2 计数器的工作原理 (3)3 设计原理 (4)4 电路系统的功能仿真 (4)6 个人小结 (23)参考文献 (24)摘要计数器是数字系统中使用较多的一种时序逻辑器件。

计数器的基本功能是统计时钟脉冲的个数,即对脉冲实现计数操作。

计数器也可以作为分频、定时、脉冲节拍产生器和脉冲序列产生器使用。

计数器的种类很多,按构成计数器中的各触发器是否使用一个时钟脉冲源来分,可分为同步计数器和异步计数器;按进位体制的不同,可分为二进制计数器、十进制计数器和任意进制计数器;按计数过程中数字增减趋势的不同,可分为加法计数器、减法计数器和可逆计数器;还有可预制数和可编计数器等等。

本次课程设计将利用众多集成电路软件软件中的Quartus II软件,使用VHDL语言编程完成论文《用程序输入方法设计一个16位二进制加法计数器》,调试结果表明,所设计的计数器正确实现了计数功能。

关键词:二进制;加法计数器;VHDL语言1 绪论现代电子设计技术的核心已日趋转向基于计算机的电子设计自动化,即EDA(Electronic Design Automation)技术。

EDA技术就是依赖功能强大的计算机,在集成电路软件平台上,对以硬件描述语言HDL(Hardware Description Language)为系统逻辑描述手段完成的设计文件,自动完成逻辑编译、化简、分割、综合、布局布线以及逻辑优化和仿真测试,直至实现既定的电子线路系统功能。

现在对EDA的概念或范畴用得很宽。

包括在机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域,都有EDA的应用。

目前EDA技术已在各大公司、企事业单位和科研教学部门广泛使用。

16位超前进位加法器实验报告

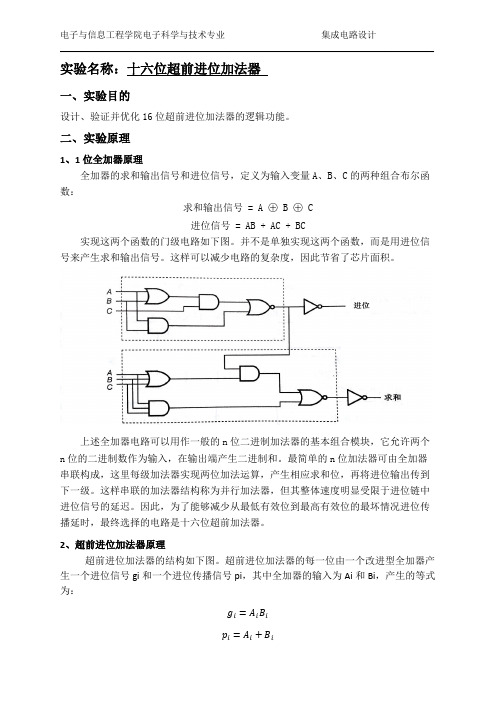

实验名称:十六位超前进位加法器一、实验目的设计、验证并优化16位超前进位加法器的逻辑功能。

二、实验原理1、1位全加器原理全加器的求和输出信号和进位信号,定义为输入变量A、B、C的两种组合布尔函数:求和输出信号 = A ⊕ B ⊕ C进位信号 = AB + AC + BC实现这两个函数的门级电路如下图。

并不是单独实现这两个函数,而是用进位信号来产生求和输出信号。

这样可以减少电路的复杂度,因此节省了芯片面积。

上述全加器电路可以用作一般的n位二进制加法器的基本组合模块,它允许两个n 位的二进制数作为输入,在输出端产生二进制和。

最简单的n位加法器可由全加器串联构成,这里每级加法器实现两位加法运算,产生相应求和位,再将进位输出传到下一级。

这样串联的加法器结构称为并行加法器,但其整体速度明显受限于进位链中进位信号的延迟。

因此,为了能够减少从最低有效位到最高有效位的最坏情况进位传播延时,最终选择的电路是十六位超前加法器。

2、超前进位加法器原理超前进位加法器的结构如下图。

超前进位加法器的每一位由一个改进型全加器产生一个进位信号gi和一个进位传播信号pi,其中全加器的输入为Ai和Bi,产生的等式为:改进的全加器的进位输出可由一个进位信号和一个进位传输信号计算得出,因此进位信号可改写为:式中可以看出,当gi = 1(Ai = Bi = 1)时,产生进位;当pi = 1(Ai =1或Bi = 1)时,传输进位输入,这两种情况都使得进位输出是1。

近似可以得到i+2和i+3级的进位输出如下:下图为一个四位超前进位加法器的结构图。

信号经过pi和gi产生一级时延,经过计算C产生一级时延,则A,B输入一旦产生,首先经过两级时延算出第1轮进位值C’不过这个值是不正确的。

C’再次送入加法器,进行第2轮2级时延的计算,算出第2轮进位值C,这一次是正确的进位值。

这里的4个4位超前进位加法器仍是串行的,所以一次计算经过4级加法器,一级加法器有2级时延,因此1次计算一共经过8级时延,相比串行加法器里的16级时延,速度提高很多。

模可变16位加法计数器

《EDA设计》报告题目:模可变16位加法计数器设计专业班级:学生姓名:指导教师:武汉理工大学信息工程学院2014 年 1 月 6 日课程设计任务书学生姓名:专业班级:指导教师:工作单位:信息工程学院题目: 模可变16位加法计数器设计初始条件:可用仪器: PC机(Quartus II软件)硬件:EDA-IV型实验箱。

要求完成的主要任务:(1)设计任务设计一个模可变16位加法计数器。

(2)设计指导设计可变16位加法计数器,可通过3个选择位M2、M1、M0实现最多8种不同模式的计数方式,例如可构成5、10、16、46、100、128、200、256进制,共8种计数模式。

(3)时间安排:2013.12.23 课程设计任务布置、选题、查阅资料2013.12.24 设计,软件编程、仿真和调试2013.12.29 实验室检查仿真结果,验证设计的可行性和正确性2013.12.30 设计的硬件调试2014.01.05 机房检查设计成果,提交设计说明书及答辩指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (I)Abstract........................................................... I I1 绪论 (1)2 Quartus II简介 (2)3 计数器的工作原理 (3)4 设计原理 (4)4.1 整体设计原理 (4)4.2 单元模块的设计 (5)4.3 顶层模块(整体电子线路系统)的设计 (8)5 电路系统的功能仿真 (10)6 硬件调试 (12)7 个人小结 (14)参考文献 (15)摘要计数器是数字电子技术中应用的最多的时序逻辑电路。

计数器不仅能用于对时钟脉冲计数,还可以用于分频、定时、产生节拍脉冲和脉冲序列以及进行数字运算等。

但是并无法显示计算结果,一般都是要通过外接LCD 或LED屏才能显示。

计数器的种类按照计数器中的触发器是否同时翻转分类,可将计数器分为同步计数器和异步计数器两种,如果按照计数过程中数字增减分类,又可将计数器分为加法计数器、减法计数器和可逆计数器,随时钟信号不断增加的为加法计数器,不断减少的为减法计数器,可增可减的叫做可逆计数器,另外还有很多种分类不一一列举,但是最常用的是第一种分类,因为这种分类可以使人一目了然,知道这个计数器到底是什么触发方式,以便于设计者进行电路的设计。

用单片机语言设计16位加法计算器实验报告

湖北第二师范学院计算机学院09计应单片机课程设计实验报告课程设计名称:电子计算器课程设计单位:10计应(1)班课设小组成员:徐凡(1060310039)凡平(1060310058)彭浩(1060310045)桂银(1060310010)潘光卉(1060300033)完成时间:2012年04月02日至2012年04月 24 日单片机课程设计实验报告课程设计题目:简易计算器作品功能描述:当通过输入键盘数字时,能够在显示器上显示输出的数值,并且通过想实现的简单运算功能,实现计算器的加、减、乘、除和清零,并将结果显示出来。

小组成员工作分工:徐凡:程序主框架的构造和主要功能函数的设计。

凡平:原理图的设计和硬件的焊接。

彭浩:基本功能函数的设计(“+,-,*,/”)。

桂银:程序流程图的设计和键盘扫描程序的实现。

潘光卉:编写文档和功能测试。

硬件电路设计:本设计中我们用的是AT89C52芯片,LCD1602 (PROTEUS中为LM016L)就是那个液晶屏,因为可以显示2行16个字符,故叫做LCD1602.11.0592M或12M晶振(CRYSTAL),两者均可,但要涉及到串口需选用12MKEYPAD-SMALLCALC就是那个4X4键盘电容20~30PF(CAP),接最小电路电容10PF主要接复位电路RESPACK-8排阻,为20K的,一个引脚接正极,另8个引脚接I/O口接RES电阻10K,接复位电路实物照片:硬件原理图原理说明:1,上电后,屏幕初始化;2,计算。

按下数字键,屏幕显示要运行的第一个数字,再按下符号键,然后再按下数字键,屏幕显示要运算的第二个数字,最后按下“=”号键,屏幕上显示出计算结果。

3,如果要再次计算,可以按下“ON/C”键清零,或者继续按下数字键,即可重新计算。

键盘使用说明如下:按键功能说明:Array“+”实现两个数的相加“-”实现两个数的相减“×”实现两个数的乘积“÷”实现两个数商的运算“ON/C”计算器显示的清零和接通电源程序控制流程图:软件设计:在程序设计方法上,模块化程序设计是单片机应用中最常用的程序设计方法。

16位超前加法器实验报告

16位超前加法器设计实验一、实验分析:四位超前进位加法器HDL程序:module add4_head ( a, b, ci, s, pp, gg);input[3:0] a;input[3:0] b;input ci;output[3:0] s;output pp;output gg;wire[3:0] p;wire[3:0] g;wire[2:0] c;assign p[0] = a[0] ^ b[0];assign p[1] = a[1] ^ b[1];assign p[2] = a[2] ^ b[2];assign p[3] = a[3] ^ b[3];assign g[0] = a[0] & b[0];assign g[1] = a[1] & b[1];assign g[2] = a[2] & b[2];assign g[3] = a[3] & b[3];assign c[0] = (p[0] & ci) | g[0];assign c[1] = (p[1] & c[0]) | g[1];assign c[2] = (p[2] & c[1]) | g[2];assign pp = p[3] & p[2] & p[1] & p[0];assign gg = g[3] | (p[3] & (g[2] | p[2] & (g[1] | p[1] & g[0])));assign s[0] = p[0] ^ ci;assign s[1] = p[1] ^ c[0];assign s[2] = p[2] ^ c[1];assign s[3] = p[3] ^ c[2];endmodulep表示进位否决信号(pass),如果p为0就否决调前一级的进位输入。

否决的意思就是即使前一级有进位,本级也不会向后一级产生进位输出。

16位超前进位加法器

16位超前进位加法器设计目录摘要 (1)1需求分析1.1加法器的发展........................................................................ 错误!未定义书签。

1.2几种串行加法器性能比较 (3)1.2.1串行进位加法器 (3)1.2.1超前进位加法器 (3)2主要内容 (4)2.1设计原理 (6)2.2设计思路 (4)3 设计思想 (5)4 实现方法 (6)4.1顶层方案图的设计与实现 (6).4.1.1顶层方案的整体设计 (6)4.1.2元器件选择和引脚锁定 (7)4.2功能模块的设计与实现 (8)4.2.1设计描述 (8)4.2.2创建RTL代码并得到电路图....................................................... .94.3功能仿真 (11)4.4编程与下载 (12)4.5硬件仿真结果 (12)5小结 (13)参考文献 (13)附录 (14)摘要:加法运算是最重要最基本的运算,所有的其他基本算术运算乘除等都最终可以用加法运算来表示在不同的场合对加法器的要求不同,要的要求速度快有的要求面积小超前进位加法器相比于串行进位加法器是一种快速加法运算器,根据用户的要求追求速度与面积的平衡。

关键词:超前进位加法器串行进位加法器速度面积1需求分析1.1 加法器的发展加法运算是最基本的运算,所有其他基本算术运算都是以加法运算为基础。

但因为加法运算存在进位问题,使得某一位计算结果的得出和所有低于他的位相关,因此,为了减少进位传输所耗的时间提高计算速度人们设计了多种类型的加法器。

如跳跃进位加法器,进位选择加法器,超前进位加法器等他们都是利用各位之间的状态来预先产生高位进位信号从而减少进位从低位到高位的传递时间1.2 几种加法器的性能比较1.2.1串行进位加法器串行进位加法器的每一位加和值都依赖于上一位进位信号,即进位信号是串行的经过加法器的每一位。

16位加法器电路设计

16位加法器电路设计

加法器电路是计算机中常见的数字电路,用于将两个二进制数相加并得出和。

16位加法器电路设计是指设计一个能处理16位二进制数相加的电路。

在设计16位加法器电路时,需要考虑以下几个关键方面:

1. 选择合适的器件:需要选择适合的逻辑门和触发器等数字电路器件。

常用的器件包括AND门、OR门、XOR门、全加器等。

2. 划分模块:将16位加法器电路划分为若干个小模块,简化设计过程。

常见的模块包括单位加法器和级联器。

3. 单位加法器设计:单位加法器是实现加法运算的基本单元。

在16位加法器电路中,每一位均由一个单位加法器完成。

单位加法器由两个输入(被加数位和加数位)和两个输出(和位和进位位)组成。

4. 级联器设计:级联器用于连接多个单位加法器,将进位位从低位传递到高位。

在16位加法器电路中,需要将每一位的进位位和前一位的进位位相连。

5. 测试和验证:设计完成后,需要进行测试和验证,确保16位加法器电路的正确性和性能。

通过以上步骤设计完成的16位加法器电路能够实现对16位二进制数的相加操作。

在实际应用中,可以将多个16位加法器电路级联以实现更大位数的加法运算。

设计一个高效可靠的16位加法器电路是数字电路设计的重要任务之一,对于计算机的性能和功能具有重要影响。

通过仔细考虑各个方面的设计和实施,可以实现一个满足要求的16位加法器电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Brent Kung树结构的16位加法器的设计仿真及优化1.利用Hspice软件设计具体电路结构

1.1 Brent Kung树结构加法器设计简介

Brent Kung树结构加法器是一种超前进位加法器,即进位提前被计算出来,送给加和电路,减小了进位顺序传递的延时,实现此加法器减小了设计的复杂度。

提高了设计的效率。

具体电路实现需要4个模块电路设计。

数据A和B通过缓冲器输入进来,然后经过进位生成和进位产生电路模块生成P和G信号。

P与G信号经过点操作模块生成相应的进位值,最后加和生成SUM。

电路结构采用动态逻辑结构,逻辑结构由NMOS下拉网络实现,构成PDN的过程和静态CMOS完全一样,晶体管的数目明显少于静态情况。

动态逻辑同时具有较快的开关速度。

动态逻辑同时在功耗方面有明显的优势。

1.2 Brent Kung树结构加法器电路设计

进位生成和进位传播模块均采用动态逻辑进行设计,具体实现公式为Pi=ai+bi,Gi=ai&bi;具体电路实现如下:

图1 进位传播和进位产生信号的动态实现

图中的反相器为对称的,p生成电路的逻辑努力为2/3,g生成电路的逻辑努力为1。

点计算模块具体生成对应的进位传播和进位产生Gi j和Pi j;其对应的具体公式为:Gi j=Gi k+Pi k*Gk-1 j。

采用动态逻辑减小复杂度具体电路结构如下:

图2点模块电路产生信号的动态实现

求和电路利用多米诺实现求和即利用选择电路实现电路结构,在此电路中求和的两种条件计算为:Si0为ai与bi的同或,Si1为ai与bi的异或,具体电路结构如下:

图5动态逻辑实现和选择电路

电路中利用两个时钟,由clk产生clkd是由下面的电路实现的,传输门总是导通,时钟路径的延时可以通过这些器件的尺寸来调整。

因为延时必须有一个严格的界限,即第二个门的所有输入必须在clkd的上升沿之前完成翻转,因此可能需要使clk进过多个以下的延时电路才能满足时序要求。

时钟延时利用反向器的缓冲器和传输门来实现。

正向二进制树结构不足以产生全部的进位位,因此Brent Kung树结构采用了一个反二进制树来实现其它的进位位,这一结构组合中间的结果以产生其余的进位位,Brent Kung树结构可以产生所有进位位的表达式。

,采用Brent Kung树的结构可以实现正确的16位加法器。

具体树结构如下所示:

图4 16位Brent-Kung树结构。