实验五 含异步清零和同步使能4位加法计数器的VHDL设计

EDA-设计含异步清零和同步时钟使能的加法计数器

专业班级:学号:姓名:EDA 技术实验报告实验项目名称:设计含异步清零和同步时钟使能的加法计数器实验日期:2012.6.5 实验成绩:实验评定标准:一、实验目的学习计数器的设计,仿真和硬件测试,进一步熟悉VHDL设计技术。

二、实验器材Quartus2软件、电脑一台三、实验内容(实验过程)<一> 实验内容一:在quartus 2上对例5进行编辑、编译、综合、适配、仿真。

说明例中各语句的作用,详细描述各事例的功能特点,给出其所有信号的时序仿真模型。

<二> 实验内容二:自己选择合适的电路模式,然后进行引脚锁定以及硬件下载测试,引脚锁定后进行编译、下载、硬件测试实验。

将实验过程和实验结果写进实验报告。

<三> 详细内容如下:1.进行文本编辑2.编译,综合,仿真四、实验程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all; entity cnt10 isport ( clk,rst,en: in std_logic ;cq: out std_logic_vector(3 downto 0); cout:out std_logic);end cnt10;architecture behav of cnt10 isbeginprocess(clk,rst,en)variable cqi:std_logic_vector(3 downto 0); beginif rst='1' then cqi:=(others =>'0');elsif clk'event and clk='1' thenif en='1' thenif cqi<9 then cqi :=cqi+1;else cqi:=(others =>'0');end if;end if;end if;if cqi=9 then cout<='1';else cout<='0';end if;cq<=cqi;end process;end behav;五、实验仿真、结果及分析:<一>实验仿真:<二> 结果和分析:当rst清零端为1时,计数器清零。

实验五 含异步清零和同步使能4位加法计数器的VHDL设计

实验五含异步清零和同步使能4位加法计数器的VHDL设计一、实验目的1掌握计数器的VHDL设计方法;2掌握异步复位和同步复位和使能的概念;3掌握寄存器性能的分析方法(即分析芯片所能达到的最高时钟频率)。

二、实验内容1异步复位4位加法计数器的设计;2同步复位4位加法计数器的设计。

3异步清0和同步时钟使能的4位加法计数器三、实验原理复位:给计数器一个初值叫复位,如果所给初值为0,则称复位为清零。

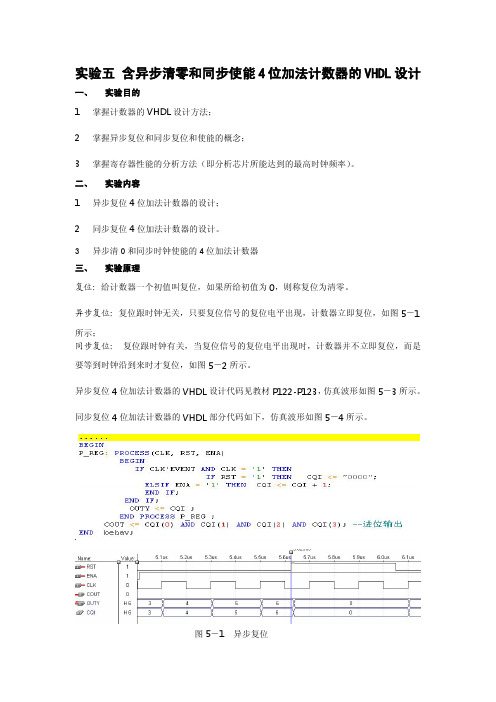

异步复位:复位跟时钟无关,只要复位信号的复位电平出现,计数器立即复位,如图5-1所示;同步复位:复位跟时钟有关,当复位信号的复位电平出现时,计数器并不立即复位,而是要等到时钟沿到来时才复位,如图5-2所示。

异步复位4位加法计数器的VHDL设计代码见教材P122-P123,仿真波形如图5-3所示。

同步复位4位加法计数器的VHDL部分代码如下,仿真波形如图5-4所示。

.图5-1异步复位图5-2同步复位图5-3异步复位计数器仿真波形图5-4同步复位计数器仿真波形四、实验步骤(一)异步复位4位加法计数器的设计1建立一个设计工程,工程名为CNT4B;2打开文本编辑器,建立一个VHDL设计文件,其VHDL代码见教材P164中的例6-20,文件名存为CNT4B.VHD。

注意文件的扩展名要选为.vhd,而且要求工程名、文件名和设计实体名必须相同。

3选器件:ACEX1K,EP1K30TC144-3(旧)或Cyclone,EP3C40Q240C8目标芯片。

4编译;5建立波形文件,然后保存,其文件名必须与工程名一致;【波形设置:①设置仿真时间为10us:②设置输入信号的波形:时钟周期设置为200ns,其他输入信号的波形设置参看图6-3。

】6仿真,观察输出波形是否正确;7时序分析:分析芯片所能达到的最高时钟频率。

【打开时序分析器,然后执行菜单命令:analysis/register performance/start,可以看到最高时钟频率为100.00MHZ】(二)同步复位4位加法计数器的设计8建立一个设计工程,工程名为CNT4B_SYS;9打开文本编辑器,建立一个VHDL设计文件,其VHDL代码参看异步计数器代码和实验原理中的参考代码,文件名存为CNT4B_SYS.VHD。

设计含异步使能清0和同步时钟使能的加法计数器

综合课程设计实验设计含异步使能清0和同步时钟使能的加法计数器1.实验目的1.计数器的设计2.QUARTUS 2中SIGNALTAP 2实时测试技术3.FPGA配置芯片的使用4.继续熟悉实验的软硬件平台2.实验步骤与结果1.设计含异步使能清0和同步时钟使能的加法计数器源代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT10 ISPORT(CLK,RST,EN:IN STD_LOGIC;CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);COUT: OUT STD_LOGIC);END CNT10;ARCHITECTURE BEHAV OF CNT10 ISBEGINPROCESS(CLK,RST,EN )VARIABLE CQI :STD:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINIF RST=’1’ THEN CQI:=(OTHERS=>’0’); --复位信号ELSIF CLK’EVENT AND CLK=’1’ THENIF EN=’1’ THEN --使能信号IF CQI<9 THEN CQI:=CQI+1;ELSE CQI:=(O THERS=>’0’);END IF;END IF;IF CQI=9 THEN COUT<=’1’; --进位ELSE COUT<=’0’;END IF;CQ<=CQI;END PROCESS;END BEHAV;实验结果:键2低电平时允许计数,键1高电平时允许计数,数码管最后一位正确计数0到9,当有进位时,发光管D1显示进位信号。

2.使用嵌入式逻辑分析仪SIGNALTAP2 进行实时测试按如图设置SIGNALTAP 2获得实验波形:可以看到CQ的波形为锯齿状的3.将计数器设计文件烧到实验板上FPGA的配置器件EPCS1中,实现掉电保护实验结果:掉电重启以后实验板上程序的功能正常。

含异步清规和同步使能的加法计数器

实验三含异步清零和同步使能的加法计数器一、实验目的1、了解二进制计数器的工作原理。

2、进一步熟悉QUARTUSII软件的使用方法和VHDL输入。

3、时钟在编程过程中的作用。

二、实验原理二进制计数器中应用最多、功能最全的计数器之一,含异步清零和同步使能的加法计数器的具体工作过程如下:在时钟上升沿的情况下,检测使能端是否允许计数,如果允许计数(定义使能端高电平有效)则开始计数,否则一直检测使能端信号。

在计数过程中再检测复位信号是否有效(低电平有效),当复位信号起作用时,使计数值清零,继续进行检测和计数。

其工作时序如图3-1所示:图3-1 计数器的工作时序三、实验内容本实验要求完成的任务是在时钟信号的作用下,通过使能端和复位信号来完成加法计数器的计数。

实验中时钟信号使用数字时钟源模块的1HZ信号,用一位拨动开关K1表示使能端信号,用复位开关S1表示复位信号,用LED模块的LED1~LED11来表示计数的二进制结果。

实验LED亮表示对应的位为‘1’,LED灭表示对应的位为‘0’。

通过输入不同的值模拟计数器的工作时序,观察计数的结果。

实验箱中的拨动开关、与FPGA的接口电路,LED灯与FPGA的接口电路以及拨动开关、LED与FPGA的管脚连接在实验一中都做了详细说明,这里不在赘述。

数字时钟信号模块的电路原理如图3-2所示,表3-1是其时钟输出与FPGA的管脚连接表。

图3-2 数字时钟信号模块电路原理表3-1 数字时钟输出与FPGA的管脚连接表按键开关模块的电路原理如图3-3所示,表3-2是按键开关的输出与FPGA的管脚连接表。

图3-3 按键开关模块电路原理信号名称FPGA I/O名称核心板接口管脚号功能说明S[0] Pin_AF5 JP1_91 ‘S1’SwitchS[1]Pin_AH6 JP1_93 ‘S2’SwitchS[2]Pin_AH7 JP1_95 ‘S3’SwitchS[3]Pin_AH8 JP1_97 ‘S4’SwitchS[4]Pin_AG10 JP1_99 ‘S5’SwitchS[5]Pin_AG11 JP1_101 ‘S6’SwitchS[6]Pin_AH14 JP1_90 ‘S7’SwitchS[7] Pin_AG7 JP1_92 ‘S8’SwitchS[8]Pin_AG8 JP1_94 ‘S9’SwitchS[9]Pin_AF9 JP1_96 ‘S10’SwitchS[10]Pin_AH10 JP1_98 ‘S11’SwitchS[11] Pin_AH11 JP1_100 ‘S12’Switch表3-2 按键开关与FPGA的管脚连接表四、实验步骤1、打开QUARTUSII软件,新建一个工程。

含异步清0和同步时钟使能的4位加法计数器 EDA技术与Verilog HDL实验报告

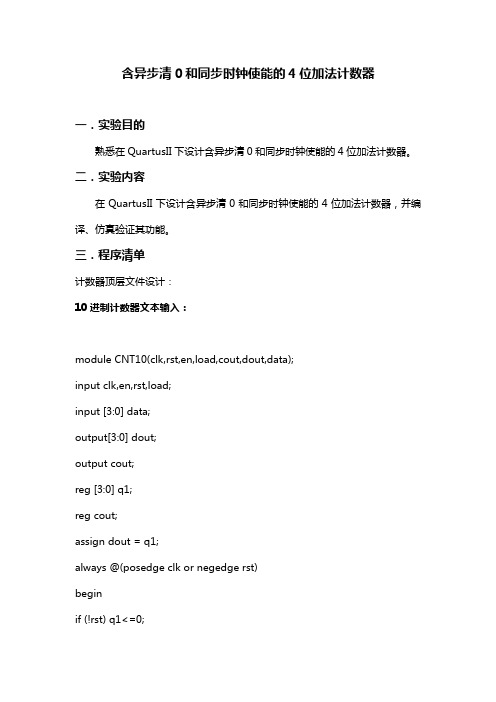

含异步清0和同步时钟使能的4位加法计数器一.实验目的熟悉在QuartusII下设计含异步清0和同步时钟使能的4位加法计数器。

二.实验内容在QuartusII下设计含异步清0和同步时钟使能的4位加法计数器,并编译、仿真验证其功能。

三.程序清单计数器顶层文件设计:10进制计数器文本输入:module CNT10(clk,rst,en,load,cout,dout,data);input clk,en,rst,load;input [3:0] data;output[3:0] dout;output cout;reg [3:0] q1;reg cout;assign dout = q1;always @(posedge clk or negedge rst)beginif (!rst) q1<=0;else if(en)beginif (!load) q1<=data;else if(q1<9) q1<=q1+1;else q1<=4'b0000;endendalways @(q1)if (q1==4'h9) cout= 1'b1;else cout= 1'b0;endmodule60位计数器文本输入:module CNT60(CLK,EN,RST,LOAD,COUT1,COUT2,DOUT1,DOUT2,DATA);input CLK,EN,RST,LOAD;input [3:0] DATA;output[3:0] DOUT1;output[2:0] DOUT2;output COUT1;output COUT2;reg [3:0] Q1;reg [2:0] Q2;reg COUT1;reg COUT2;assign DOUT1 = Q1;assign DOUT2 = Q2;always @(negedge CLK or negedge RST) beginif(!RST) Q1<=0;else if (EN) beginif (!LOAD) Q1<=DATA;else if (Q1<9) Q1<=Q1+1;else Q1<=4'b0000;endendalways @(Q1)if (Q1==4'h9) COUT1=1'b1;elseCOUT1=1'b0;always @(negedge COUT1 or negedge RST)beginif(!RST) Q2<=0;else if (EN) beginif (!LOAD) Q2<=DATA;else if (Q2<5) Q2<=Q2+1;else Q2<=4'b0000;endendalways @(Q2)if ((Q1==4'h9)&&(Q2==3'h5)) COUT2=1'b1;elseCOUT2=1'b0;endmodule60位计数器图形输入:四.实验步骤1、新建一个名称为CNT10的工程,并在该文件夹中新建一个CNT10.v的文件。

4位加法计数器的VHDL描述

0

十进制整数

35

十进制整数

10E3

十进制整数

16#D9#

十六进制整数

8#720#

八进制整数

2#11010010# 二进制整数

1.3 4位加法计数器的另一种表达方式

【例5-2】 LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL ; USE IEEE.STD_LOGIC_UNSIGNED.ALL ; ENTITY CNT4 IS PORT ( CLK : IN STD_LOGIC ; Q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ) ; END ; ARCHITECTURE bhv OF CNT4 IS

BEGIN PROCESS (CLK)

BEGIN IF CLK'EVENT AND CLK = '1' THEN Q <= Q + 1 ; END IF;

END PROCESS ; END bhv;

4位加法计数器的VHDL描述

1.2 整数、自然数和正整数数据类型

整数常量的书写方式示例如下:

1

十进制整数

1.3 4位加法计数器的另一种表达方式 4位加法计数器由两大部分组成:

图5-1 4位加法计数器RTL电路

4位加法计数器的VHDL描述

1.3 4位加法计数器的另一种表达方式

图5-2 4位加法计数器工作时序

4位加法计数器的VHDL描述

1.3 4位加法计数器的另一种表达方式

数据类型: 整数类型INTEGER、自然数类型、正整数类型POSITIVE。

EDA技术实用教程

4位加法计数器的VHDL描述

1.1 4位加法计数器

含异步清零和同步时钟使能的4位加法器

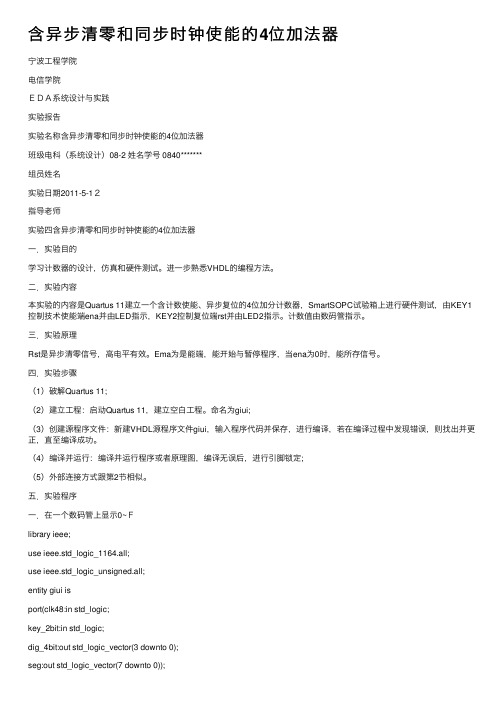

含异步清零和同步时钟使能的4位加法器宁波⼯程学院电信学院EDA系统设计与实践实验报告实验名称含异步清零和同步时钟使能的4位加法器班级电科(系统设计)08-2 姓名学号 0840*******组员姓名实验⽇期2011-5-12指导⽼师实验四含异步清零和同步时钟使能的4位加法器⼀.实验⽬的学习计数器的设计,仿真和硬件测试。

进⼀步熟悉VHDL的编程⽅法。

⼆.实验内容本实验的内容是Quartus 11建⽴⼀个含计数使能、异步复位的4位加分计数器,SmartSOPC试验箱上进⾏硬件测试,由KEY1控制技术使能端ena并由LED指⽰,KEY2控制复位端rst并由LED2指⽰。

计数值由数码管指⽰。

三.实验原理Rst是异步清零信号,⾼电平有效。

Ema为是能端,能开始与暂停程序,当ena为0时,能所存信号。

四.实验步骤(1)破解Quartus 11;(2)建⽴⼯程:启动Quartus 11,建⽴空⽩⼯程。

命名为giui;(3)创建源程序⽂件:新建VHDL源程序⽂件giui,输⼊程序代码并保存,进⾏编译,若在编译过程中发现错误,则找出并更正,直⾄编译成功。

(4)编译并运⾏:编译并运⾏程序或者原理图,编译⽆误后,进⾏引脚锁定;(5)外部连接⽅式跟第2节相似。

五.实验程序⼀.在⼀个数码管上显⽰0~Flibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity giui isport(clk48:in std_logic;key_2bit:in std_logic;dig_4bit:out std_logic_vector(3 downto 0);seg:out std_logic_vector(7 downto 0));end giui;architecture m1 of giui issignal num1:std_logic_vector(3 downto 0);signal cnt:std_logic_vector(23 downto 0);signal t: std_logic;signal q:std_logic;beginfre:process(clk48,cnt)beginif clk48'event and clk48='1' thencnt<=cnt+1;end if;q<=cnt(23);end process fre;coun:process(q)beginif q'event and q='1' thenif t='1' then num1<="0000";elsenum1<=num1+1;end if;end if;end process;SEG<= "11000000" when num1="0000" else "11111001" when num1="0001" else "10100100" when num1="0010" else"10110000" when num1="0011" else"10011001" when num1="0100" else"10010010" when num1="0101" else"10000010" when num1="0110" else"11111000" when num1="0111" else"10000000" when num1="1000" else"10010000" when num1="1001" else"10001000" when num1="1010" else"10000011" when num1="1011" else"01000110" when num1="1100" else"10100001" when num1="1101" else"10000110" when num1="1110" else"11111111";dig_4bit<="1110" when t='1' else"1111" when t='0';end m1;⼆.4位加法器Library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity sun_adder isport(clk:in std_logic;key:in std_logic;led1:out std_logic;dig:out std_logic_vector(3 downto 0);seg:out std_logic_vector(7 downto 0)); end sun_adder;architecture a of sun_adder issignal tmp:std_logic_vector(23 downto 0); signal tmp1:std_logic_vector(10 downto 0); signal address,pp:std_logic_vector(3 downto 0); signal p:std_logic_vector(1 downto 0);signal tt,t,q,q1: std_logic;signal num1,num2,num3,num4:std_logic_vector(3 downto 0);beginprocess(clk)beginif clk'event and clk='1' then tmp<=tmp+1;tmp1<=tmp1+1;end if;end process;q<=tmp(23);q1<=tmp1(10);process(q1)beginif q1'event and q1='1' then case p iswhen "00"=>pp<="1110";when "01"=>pp<="1101";when "10"=>pp<="1011";when others=>pp<="0111";end case;dig<=pp;case pp iswhen "1110"=>address<=num1;when "1101"=>address<=num2;when "1011"=>address<=num3;when others=>address<=num4;end case;p<=p+1;end if;end process;process(key)beginIf key'event and key='1' thent<= not t;end if;end process;process(q)beginif q'event and q='1' thenif t='1' then num1<="0000";num2<="0000";num3<="0000";num4<="0000";else num1<=num1+1;if num1="1001" then num1<="0000";tt<='1';if num2="1001" then num2<="0000";if num3="1001" then num3<="0000";if num4="1001" then num4<="0000";else num4<=num4+1; end if;else num3<=num3+1; end if;else num2<=num2+1; `1212212345123451233123`12341234123412341312end if; else num1<=num1+1;tt<='0'; end if; end if;end if;end process;seg<= "11000000" when address="0000" else"11111001" when address="0001" else"10100100" when address="0010" else"10110000" when address="0011" else"10011001" when address="0100" else"10010010" when address="0101" else"10000010" when address="0110" else "11111000" when address="0111" else "10000000" when address="1000" else "10010000" when address="1001" else "11111111";led1<='0' when tt='1' else'1' when tt='0';end a;六.实验现象。

VHDL4位计数器的设计

*******bcd译码器******library ieee;use ieee.std_logic_1164.all;entity decoder isport(bcd: in std_logic_vector(3 downto 0);y: out std_logic_vector(7 downto 0));end entity;architecture rtl of decoder isbeginprocess (bcd)begincase bcd iswhen "0000" => y<="11000000"; --0: h g f e d c b a when "0001" => y<="11111001"; --1when "0010" => y<="10100100"; --2when "0011" => y<="10110000"; --3when "0100" => y<="10011001"; --4when "0101" => y<="10010010"; --5when "0110" => y<="10000010"; --6when "0111" => y<="11111000"; --7when "1000" => y<="10000000"; --8when "1001" => y<="10010000"; --9when others => y<="11111111";end case;end process;end rtl;***********多路选择控制************library ieee;use ieee.std_logic_1164.all;entity mux isport (input_a:in std_logic_vector(3 downto 0); input_b:in std_logic_vector(3 downto 0);input_c:in std_logic_vector(3 downto 0);input_d:in std_logic_vector(3 downto 0);sel:in std_logic_vector(1 downto 0);y:out std_logic_vector(3 downto 0));end entity mux;architecture rtl of mux isbeginprocess(sel)isbeginif(sel="00")theny<=input_a;elsif(sel="01")theny<=input_b;elsif(sel="10")theny<=input_c;elsey<=input_d;end if;end process;end rtl;************分频************library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity clk4ms isport (clk:in std_logic;y:buffer std_logic);end entity clk4ms ;architecture rtl of clk4ms issignal a:STD_LOGIC_VECTOR(17 DOWNTO 0); beginprocess(clk)isbeginif(clk'event and clk='1')thenif(a="10111011100000000") thena<="000000000000000000";y<=not y;elsea<=a+'1';end if;end if;end process;end rtl;************计数器************library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt isport (clk,clr,en:in std_logic;a:out std_logic_vector(3 downto 0);b:out std_logic_vector(3 downto 0);c:out std_logic_vector(3 downto 0);d:out std_logic_vector(3 downto 0));end entity cnt ;architecture rtl of cnt issignal dout_0,dout_10,dout_100,dout_1000:std_logic_vector(3 downto 0); beginprocess(clr,clk,en)isbegina<=dout_0;b<=dout_10;c<=dout_100;d<=dout_1000;if clr='1' thendout_0<="0000";dout_10<="0000";dout_100<="0000";dout_1000<="0000";elsif(en='1')thenif(clk'event and clk='1')thenif(dout_0="1001")then ---计数dout_0<="0000";elsedout_0<=dout_0+'1';end if;elsif(clk'event and clk='1' and dout_0="1001")thenif(dout_10="1001") then ---计数dout_10<="0000";elsedout_10<=dout_10+'1';end if;elsif(clk'event and clk='1' and dout_0="1001" and dout_10="1001")thenif(dout_100="1001") then ---计数dout_100<="0000";elsedout_100<=dout_100+'1';end if;elsif(clk'event and clk='1' and dout_0="1001" and dout_10="1001" and dout_100="1001")thenif(dout_1000="1001") then ---计数dout_1000<="0000";elsedout_1000<=dout_1000+'1';end if;end if;end if;end process;end rtl;************位选************LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY wei ISPORT(clk4ms:IN STD_LOGIC;q:BUFFER STD_LOGIC_VECTOR(1 DOWNTO 0);d:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END ENTITY wei;ARCHITECTURE rtl OF wei ISBEGINPROCESS(clk4ms) ISBEGINIF(clk4ms 'EVENT AND clk4ms='1') THEN IF(q="11") THENq<="00";ELSEq<=q+'1';END IF;IF(q="00") THENd<="1000";ELSIF(q="01") THENd<="0100";ELSIF(q="10") THENd<="0010";ELSEd<="0001";END IF;END IF;END PROCESS;END ARCHITECTURE rtl;**********总程序*********LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY ZONG ISPORT( clr :IN STD_LOGIC;clk :IN STD_LOGIC;CLK4M:IN STD_LOGIC;en:IN STD_LOGIC;Y:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END ZONG ;ARCHITECTURE a OF ZONG ISCOMPONENT cnt isport (clk,clr,en:in std_logic;a:out std_logic_vector(3 downto 0);b:out std_logic_vector(3 downto 0);c:out std_logic_vector(3 downto 0);d:out std_logic_vector(3 downto 0));END COMPONENT;COMPONENT MUX isport (input_a:in std_logic_vector(3 downto 0); input_b:in std_logic_vector(3 downto 0);input_c:in std_logic_vector(3 downto 0);input_d:in std_logic_vector(3 downto 0);sel:in std_logic_vector(1 downto 0);y:out std_logic_vector(3 downto 0));end COMPONENT;COMPONENT DECODER isport(bcd:in std_logic_vector(3 downto 0);y: out std_logic_vector(7 downto 0));end COMPONENT;COMPONENT WEI isport(clk4ms:in std_logic;d:out std_logic_vector(3 downto 0));end COMPONENT;COMPONENT CLK4MS isport(clk:in std_logic;y:out std_logic);end COMPONENT;SIGNAL aa,bb,cc,dd:STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL mm:STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL ss:STD_LOGIC;signal ww:STD_LOGIC_VECTOR(1 DOWNTO 0);BEGINu1 : cnt PORT MAP(clk,clr,en,aa,bb,cc,dd);u2 : mux PORT MAP(aa,bb,cc,dd,ww,mm);u3 :decoder PORT MAP(mm,y);u4 : wei PORT MAP(ss,ww,dig);u5 : clk4ms PORT MAP(clk4m,ss);END a;。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验五含异步清零和同步使能4位加法计数器的VHDL设计一、实验目的

1掌握计数器的VHDL设计方法;

2掌握异步复位和同步复位和使能的概念;

3掌握寄存器性能的分析方法(即分析芯片所能达到的最高时钟频率)。

二、实验内容

1异步复位4位加法计数器的设计;

2同步复位4位加法计数器的设计。

3异步清0和同步时钟使能的4位加法计数器

三、实验原理

复位:给计数器一个初值叫复位,如果所给初值为0,则称复位为清零。

异步复位:复位跟时钟无关,只要复位信号的复位电平出现,计数器立即复位,如图5-1

所示;

同步复位:复位跟时钟有关,当复位信号的复位电平出现时,计数器并不立即复位,而是要等到时钟沿到来时才复位,如图5-2所示。

异步复位4位加法计数器的VHDL设计代码见教材P122-P123,仿真波形如图5-3所示。

同步复位4位加法计数器的VHDL部分代码如下,仿真波形如图5-4所示。

.

图5-1异步复位

图5-2同步复位

图5-3异步复位计数器仿真波形

图5-4同步复位计数器仿真波形

四、实验步骤

(一)异步复位4位加法计数器的设计

1建立一个设计工程,工程名为CNT4B;

2打开文本编辑器,建立一个VHDL设计文件,其VHDL代码见教材P164中的例6-20,文件名存为CNT4B.VHD。

注意文件的扩展名要选为.vhd,而且要求工程名、文件名和设计实体名必须相同。

3选器件:ACEX1K,EP1K30TC144-3(旧)或Cyclone,EP3C40Q240C8目标芯片。

4编译;

5建立波形文件,然后保存,其文件名必须与工程名一致;【波形设置:①设置仿真时间为10us:②设置输入信号的波形:时钟周期设置为200ns,其他输入信号的波形设置参看图6-3。

】

6仿真,观察输出波形是否正确;

7时序分析:分析芯片所能达到的最高时钟频率。

【打开时序分析器,然后执行菜单命令:analysis/register performance/start,可以看到最高时钟频率为100.00MHZ】

(二)同步复位4位加法计数器的设计

8建立一个设计工程,工程名为CNT4B_SYS;

9打开文本编辑器,建立一个VHDL设计文件,其VHDL代码参看异步计数器代码和实验原理中的参考代码,文件名存为CNT4B_SYS.VHD。

注意文件的扩展名要选为.vhd,而且要求工程名、文件名和设计实体名必须相同。

10选器件:ACEX1K,EP1K30TC144-3(旧)或Cyclone,EP3C40Q240C8目标芯片。

11编译;

12建立波形文件,然后保存,其文件名必须与工程名一致;【波形设置:①设置仿真时间为10us:②设置输入信号的波形:时钟周期设置为200ns,其他输入信号的波形设置参看图5-4。

】

13仿真,观察输出波形是否正确;

14时序分析:分析芯片所能达到的最高时钟频率。

【打开时序分析器,然后执行菜单命令:analysis/register performance/start,可以看到最高时钟频率为55.55MHZ】

(三)异步清0和同步时钟使能的4位加法计数器的VHDL设计

参照实验(一)、(二),完成异步清0和同步时钟使能的4位10进制加法计数器的设计。

五、思考题

1解释同步复位和异步复位的概念,同步的含义是什么?。

2在异步复位4位计数器的设计中,是否可以不定义信号CQI,而直接用输出端口信号完成加法运算,即OUTY<=OUTY+1?为什么?如果可以,需要修改什么?

3修改实验中的设计代码,用进程语句实现进位信号COUT的输出。

4设计一个1位十进制计数器(二进制是4位),要求含有异步复位和计数使能控制,有进位输出。

写出VHDL设计代码并仿真。

如何设计2位十进制计数器?

六、拓展:8位自启动环形计数器

[实验原理]

数字逻辑电路中,用来存放二进制数据或代码的电路称为寄存器。

寄存器是由具有存储功能的触发器组合构成的。

按照功能的不同,可将寄存器分为基本寄存器和移位寄存器两大类。

基本寄存器只能并行送入数据,需要时也只能并行输出,移位寄存器中的数据可以在移位脉冲作用下依次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,串行输入、并行输出。

在实际应用中,环形计数器实际上就是一个最简单的移位寄存器,它把最后一个触发器的输出值移位到前一个触发器中。

对于n位二进制代码的移位寄存器,为构成环形计数器可

将寄存器FF

n-1的输出Q

n-1

接到寄存器FF

的输入端D

,把各个寄存器相连使信号由左向右移

位,并由Q

n-1返回到Q

,在多数情况下,寄存器中只有一个信号1,只要有时钟脉冲作用,

1就在移位寄存器循环,环形计数器中各个触发器的Q端,将轮流地出现矩形脉冲。

应用DFF 设计的环形计数器电路图如图1所示。

图18位自启动环形计数器电路图。