40194四位双向移位寄存器

四位移位寄存器

摘要当前,电子信息化高速发展,电子产品成了日常生活中必不可少的一部分。

移位寄存器在大部分电子产品中是必不可少的一部分。

本论文介绍了实现并行存取的四位移位寄存器的设计过程,从电路的构思到整个电路的完成以及其版图的设计都有一个详细的描述。

所设计的寄存器在时钟脉冲的控制下,实现数据的并行输入、并行输出,串行输入并行输出等功能。

整个设计过程全部在LINUX系统下用Cadence软件进行设计的,用Cadence软件进行电路设计并仿真。

最后,利用Cadence软件进行版图的设计,电气规则的检查和LVS的对比匹配验证。

关键词:寄存器;并行存取;版图AbstractAt present, the rapid development of electronic information technology, electronics has become an indispensable part of daily life. Most of the shift register in electronic products is essential. This paper describes the realization of access to the four parallel shift register the design process, from concept to the circuit as a whole circuit of its territory and the completion of the design has a detailed description. The design of the register under the control of the clock, the parallel data input, output parallel, serial input parallel output functions. The entire design process in LINUX system with Cadence software designed and was used Cadence software for circuit design and simulation. Finally, use Cadence software to design the territory, electrical inspection rules and LVS comparison of the match to verify.Key words:register; parallel access; territory目录引言 (1)1 设计要求 (1)2 电路构思及其理论 (1)2.1 设计思路 (1)2.2 设计构思的理论依据 (2)2.2.1 寄存器描述 (2)2.2.2 移位寄存器的特点和分类 (2)3 系统电路的设计及原理说明 (2)3.1 系统框图及说明 (2)3.2 电路设计说明 (3)3.3 关键器件介绍 (4)3.3.1 边沿D触发器 (5)3.3.2 3个二输入与非门构成的选择器 (6)4 仿真验证叙述及效果分析 (6)4.1 电路仿真 (6)4.2电路仿真结果分析 (6)5 工程设计 (7)5.1 Cadence软件介绍 (7)5.2 电路设计 (7)5.3 版图设计及验证 (8)5.3.1 版图设计 (8)5.3.2 版图验证 (9)6 调试测试分析 (10)7 结束语 (10)参考文献 (11)附录 (12)引言当今电子信息化的社会,电子产品在日常生活中随处可见。

实验十四 移位寄存器及其应用

实验十四移位寄存器及其应用一、实验目的1.掌握四位双向移位寄存器的逻辑功能与使用方法。

2.了解移位寄存器的使用—实现数据的串行,并行转换和构成环形计数器。

二、实验原理1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。

既能左移又能右移的称为双向移位寄存器,只需要改变左右移的控制信号便可实现双向移位要求。

根据寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。

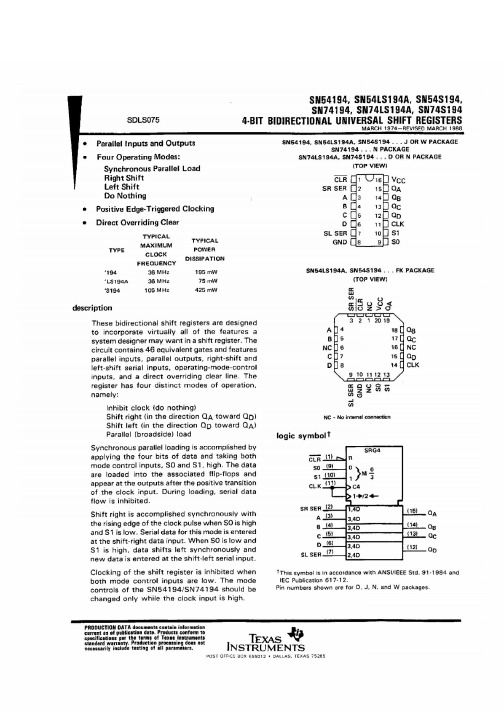

本实验选用的4位双向通用移位寄存器,型号为74LS194或CC40194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图14-1所示。

图14-1 74LS194(或CC40194)的逻辑符号及引脚排列表14-1 74LS194的功能表其中D3、D2、D1、D0为并行输入端;Q3、Q2、Q1、Q0为并行输出端;SR为右移串行输入端,SL为左移串行输入端;S1、S0为操作模式控制端;MR为无条件清零端;CP为时钟脉冲输入端。

74LS194有5种不同的操作模式:即并行送数寄存,右移(方向由Q3->Q0),左移(方向由Q0->Q3),保持及清“0”。

S1、S0和端的控制作用如表14-1所示。

2、移位寄存器应用很广,可构成移位寄存器型计数器、顺序脉冲发生器和串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。

(1)环形计数器把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,如下图所示。

图14-2 环形计数器示意图将输出端Q3与输入端SR相连后,在时钟脉冲的作用下Q0Q1Q2Q3将依次右移。

同理,将输出端Q0与输入端SL相连后,在时钟脉冲的作用下Q0Q1Q2Q3将依次左移。

(2)实现数据串、并转换○1串行/并行转换器串行/并行转换是指串行输入的数据,经过转换电路之后变成并行输出。

下面是用两片74LS194构成的七位串行/并行转换电路。

CD4000系列芯片功能

CD4000系列芯片功能CD4000系列芯片功能型号器件名称备注CD4000 双3输入端或非门+单非门 TICD4001 四2输入端或非门 HIT/NSC/TI/GOLCD4002 双4输入端或非门 NSCCD4006 18位串入/串出移位寄存器 NSCCD4007 双互补对加反相器 NSCCD4008 4位超前进位全加器 NSCCD4009 六反相缓冲/变换器 NSCCD4010 六同相缓冲/变换器 NSCCD4011 四2输入端与非门 HIT/TICD4012 双4输入端与非门 NSCCD4013 双主-从D型触发器 FSC/NSC/TOSCD4014 8位串入/并入-串出移位寄存器 NSCCD4015 双4位串入/并出移位寄存器 TICD4016 四传输门 FSC/TICD4017 十进制计数/分配器 FSC/TI/MOTCD4018 可预制1/N计数器 NSC/MOTCD4019 四与或选择器 PHICD4020 14级串行二进制计数/分频器 FSCCD4021 08位串入/并入-串出移位寄存器PHI/NSC CD4022 八进制计数/分配器 NSC/MOTCD4023 三3输入端与非门 NSC/MOT/TICD4024 7级二进制串行计数/分频器 NSC/MOT/TICD4025 三3输入端或非门 NSC/MOT/TICD4026 十进制计数/7段译码器 NSC/MOT/TICD4027 双J-K触发器 NSC/MOT/TICD4028 BCD码十进制译码器 NSC/MOT/TICD4029 可预置可逆计数器 NSC/MOT/TICD4030 四异或门 NSC/MOT/TI/GOLCD4031 64位串入/串出移位存储器 NSC/MOT/TICD4032 三串行加法器 NSC/TICD4033 十进制计数/7段译码器 NSC/TICD4034 8位通用总线寄存器 NSC/MOT/TICD4035 4位并入/串入-并出/串出移位寄存NSC/MOT/TI CD4038 三串行加法器 NSC/TICD4040 12级二进制串行计数/分频器 NSC/MOT/TICD4041 四同相/反相缓冲器 NSC/MOT/TICD4042 四锁存D型触发器 NSC/MOT/TICD4043 4三态R-S锁存触发器("1"触发) NSC/MOT/TI CD4044 四三态R-S锁存触发器("0"触发) NSC/MOT/TI CD4046 锁相环NSC/MOT/TI/PHICD4047 无稳态/单稳态多谐振荡器 NSC/MOT/TICD4048 4输入端可扩展多功能门 NSC/HIT/TICD4049 六反相缓冲/变换器 NSC/HIT/TICD4050 六同相缓冲/变换器 NSC/MOT/TICD4051 八选一模拟开关 NSC/MOT/TICD4052 双4选1模拟开关 NSC/MOT/TICD4053 三组二路模拟开关 NSC/MOT/TICD4054 液晶显示驱动器 NSC/HIT/TICD4055 BCD-7段译码/液晶驱动器 NSC/HIT/TICD4056 液晶显示驱动器 NSC/HIT/TICD4059 “N”分频计数器 NSC/TICD4060 14级二进制串行计数/分频器 NSC/TI/MOTCD4063 四位数字比较器 NSC/HIT/TICD4066 四传输门 NSC/TI/MOTCD4067 16选1模拟开关 NSC/TICD4068 八输入端与非门/与门 NSC/HIT/TICD4069 六反相器 NSC/HIT/TICD4070 四异或门 NSC/HIT/TICD4071 四2输入端或门 NSC/TICD4072 双4输入端或门 NSC/TICD4073 三3输入端与门 NSC/TICD4075 三3输入端或门 NSC/TICD4076 四D寄存器CD4077 四2输入端异或非门 HITCD4078 8输入端或非门/或门CD4081 四2输入端与门 NSC/HIT/TICD4082 双4输入端与门 NSC/HIT/TICD4085 双2路2输入端与或非门CD4086 四2输入端可扩展与或非门CD4089 二进制比例乘法器CD4093 四2输入端施密特触发器 NSC/MOT/ST CD4094 8位移位存储总线寄存器 NSC/TI/PHI CD4095 3输入端J-K触发器CD4096 3输入端J-K触发器CD4097 双路八选一模拟开关CD4098 双单稳态触发器 NSC/MOT/TICD4099 8位可寻址锁存器 NSC/MOT/STCD40100 32位左/右移位寄存器CD40101 9位奇偶较验器CD40102 8位可预置同步BCD减法计数器CD40103 8位可预置同步二进制减法计数器CD40104 4位双向移位寄存器CD40105 先入先出FI-FD寄存器CD40106 六施密特触发器 NSC\TICD40107 双2输入端与非缓冲/驱动器 HAR\TICD40108 4字×4位多通道寄存器CD40109 四低-高电平位移器CD40110 十进制加/减,计数,锁存,译码驱动 STCD40147 10-4线编码器 NSC\MOTCD40160 可预置BCD加计数器 NSC\MOTCD40161 可预置4位二进制加计数器 NSC\MOTCD40162 BCD加法计数器 NSC\MOTCD40163 4位二进制同步计数器 NSC\MOTCD40174 六锁存D型触发器 NSC\TI\MOTCD40175 四D型触发器 NSC\TI\MOTCD40181 4位算术逻辑单元/函数发生器CD40182 超前位发生器CD40192 可预置BCD加/减计数器(双时钟) NSC\TICD40193 可预置4位二进制加/减计数器 NSC\TICD40194 4位并入/串入-并出/串出移位寄存NSC\MOT CD40195 4位并入/串入-并出/串出移位寄存NSC\MOT CD40208 4×4多端口寄存器。

74LS194中文资料_数据手册_参数

74LS194是一种高速4位双向通用移位寄存器。

作为一种高速、多功能的顺序构建块,它在许多应用中都很有用。

它可以用于插入-串行、左移、右移、串行-并行、并行-串行和并行-并行数据寄存器传输。

LS194A类似于LS195A通用移位寄存器,增加了没有外部连接的移位和保持(什么也不做)modesof操作的功能。

74LS194它利用肖特基二极管夹紧工艺实现高速,并完全兼容于所有的半导体晶体管家族。

•典型的移频为36mhz•异步主复位•保持(什么也不做)模式•完全同步串行或并行数据传输•输入箝位二极管限制高速终止效果逻辑图和真值表显示了LS194A四位双向移位寄存器的功能特性。

LS194A在操作上类似于席恩半导体LS195A通用移位寄存器,用于串行或并行数据寄存器传输。

这两种设备的一些共同特征如下:所有数据和模式控制输入都是边缘触发的,只响应时钟的低到高转换(CP)。

因此,唯一的时间限制是modecontrol和所选的数据输入必须在时钟脉冲正转换之前的一个设置时间是稳定的。

寄存器是完全同步的,所有操作都在15 ns以内(通常),这使得设备对于实现高速cpu或内存缓冲寄存器特别有用。

74LS194四个并行数据输入(P0、P1、P2、P3)是d类型的输入。

当S0和S1都很高时,出现在P0、P1、P2和P3输入上的数据在时钟的下一个低到高的跃迁之后分别被传输到Q0、Q1、Q2和Q3输出。

异步主重置(MR)在低时覆盖所有其他输入条件,并强制Q输出变慢。

增加应用范围的LS194A设计的特殊逻辑特性描述如下:两个模式控制输入(S0, S1)决定设备的同步运行。

如ModeSelection表所示,数据可以从左到右(右移,Q0!)Q1,等等)或者从右向左(左移,Q3!,或者可以输入并行数据,同时加载寄存器的所有四位。

当S0和S1都很低时,74LS194现有的数据被保留在一个“什么也不做”的模式中,而不限制从高到低的时钟转换。

CD4系列芯片

CD4系列芯片2008-03-26 12:25CD系列::CD4000 双3输入端或非门+单非门 TICD4001 四2输入端或非门 HIT/NSC/TI/GOLCD4002 双4输入端或非门 NSCCD4006 18位串入/串出移位寄存器 NSCCD4007 双互补对加反相器 NSCCD4008 4位超前进位全加器 NSCCD4009 六反相缓冲/变换器 NSCCD4010 六同相缓冲/变换器 NSCCD4011 四2输入端与非门 HIT/TICD4012 双4输入端与非门 NSCCD4013 双主-从D型触发器 FSC/NSC/TOSCD4014 8位串入/并入-串出移位寄存器 NSCCD4015 双4位串入/并出移位寄存器 TICD4016 四传输门 FSC/TICD4017 十进制计数/分配器 FSC/TI/MOTCD4018 可预制1/N计数器 NSC/MOTCD4019 四与或选择器 PHICD4020 14级串行二进制计数/分频器 FSCCD4021 08位串入/并入-串出移位寄存器 PHI/NSCCD4022 八进制计数/分配器 NSC/MOTCD4023 三3输入端与非门 NSC/MOT/TICD4024 7级二进制串行计数/分频器 NSC/MOT/TICD4025 三3输入端或非门 NSC/MOT/TICD4026 十进制计数/7段译码器 NSC/MOT/TICD4027 双J-K触发器 NSC/MOT/TICD4028 BCD码十进制译码器 NSC/MOT/TICD4029 可预置可逆计数器 NSC/MOT/TICD4030 四异或门 NSC/MOT/TI/GOLCD4031 64位串入/串出移位存储器 NSC/MOT/TICD4032 三串行加法器 NSC/TICD4033 十进制计数/7段译码器 NSC/TICD4034 8位通用总线寄存器 NSC/MOT/TICD4035 4位并入/串入-并出/串出移位寄存 NSC/MOT/TI CD4038 三串行加法器 NSC/TICD4040 12级二进制串行计数/分频器 NSC/MOT/TICD4041 四同相/反相缓冲器 NSC/MOT/TICD4042 四锁存D型触发器 NSC/MOT/TICD4043 4三态R-S锁存触发器("1"触发) NSC/MOT/TI CD4044 四三态R-S锁存触发器("0"触发) NSC/MOT/TI CD4046 锁相环 NSC/MOT/TI/PHICD4047 无稳态/单稳态多谐振荡器 NSC/MOT/TICD4048 4输入端可扩展多功能门 NSC/HIT/TICD4049 六反相缓冲/变换器 NSC/HIT/TICD4050 六同相缓冲/变换器 NSC/MOT/TICD4051 八选一模拟开关 NSC/MOT/TICD4052 双4选1模拟开关 NSC/MOT/TICD4053 三组二路模拟开关 NSC/MOT/TICD4054 液晶显示驱动器 NSC/HIT/TICD4055 BCD-7段译码/液晶驱动器 NSC/HIT/TI CD4056 液晶显示驱动器 NSC/HIT/TICD4059 “N”分频计数器 NSC/TICD4060 14级二进制串行计数/分频器 NSC/TI/MOT CD4063 四位数字比较器 NSC/HIT/TICD4066 四传输门 NSC/TI/MOTCD4067 16选1模拟开关 NSC/TICD4068 八输入端与非门/与门 NSC/HIT/TICD4069 六反相器 NSC/HIT/TICD4070 四异或门 NSC/HIT/TICD4071 四2输入端或门 NSC/TICD4072 双4输入端或门 NSC/TICD4073 三3输入端与门 NSC/TICD4075 三3输入端或门 NSC/TICD4076 四D寄存器CD4077 四2输入端异或非门 HITCD4078 8输入端或非门/或门CD4081 四2输入端与门 NSC/HIT/TICD4082 双4输入端与门 NSC/HIT/TICD4085 双2路2输入端与或非门CD4086 四2输入端可扩展与或非门CD4089 二进制比例乘法器CD4093 四2输入端施密特触发器 NSC/MOT/STCD4094 8位移位存储总线寄存器 NSC/TI/PHICD4095 3输入端J-K触发器CD4096 3输入端J-K触发器CD4097 双路八选一模拟开关CD4098 双单稳态触发器 NSC/MOT/TICD4099 8位可寻址锁存器 NSC/MOT/STCD40100 32位左/右移位寄存器CD40101 9位奇偶较验器CD40102 8位可预置同步BCD减法计数器CD40103 8位可预置同步二进制减法计数器CD40104 4位双向移位寄存器CD40105 先入先出FI-FD寄存器CD40106 六施密特触发器 NSC\\TICD40107 双2输入端与非缓冲/驱动器 HAR\\TICD40108 4字×4位多通道寄存器CD40109 四低-高电平位移器CD40110 十进制加/减,计数,锁存,译码驱动 STCD40147 10-4线编码器 NSC\\MOTCD40160 可预置BCD加计数器 NSC\\MOTCD40161 可预置4位二进制加计数器 NSC\\MOTCD40162 BCD加法计数器 NSC\\MOTCD40163 4位二进制同步计数器 NSC\\MOTCD40174 六锁存D型触发器 NSC\\TI\\MOTCD40175 四D型触发器 NSC\\TI\\MOTCD40181 4位算术逻辑单元/函数发生器CD40182 超前位发生器CD40192 可预置BCD加/减计数器(双时钟) NSC\\TI CD40193 可预置4位二进制加/减计数器 NSC\\TICD40194 4位并入/串入-并出/串出移位寄存 NSC\\MOT CD40195 4位并入/串入-并出/串出移位寄存 NSC\\MOT CD40208 4×4多端口寄存器型号器件名称厂牌备注CD4501 4输入端双与门及2输入端或非门CD4502 可选通三态输出六反相/缓冲器CD4503 六同相三态缓冲器CD4504 六电压转换器CD4506 双二组2输入可扩展或非门CD4508 双4位锁存D型触发器CD4510 可预置BCD码加/减计数器CD4511 BCD锁存,7段译码,驱动器CD4512 八路数据选择器CD4513 BCD锁存,7段译码,驱动器(消隐)CD4514 4位锁存,4线-16线译码器CD4515 4位锁存,4线-16线译码器CD4516 可预置4位二进制加/减计数器CD4517 双64位静态移位寄存器CD4518 双BCD同步加计数器CD4519 四位与或选择器CD4520 双4位二进制同步加计数器CD4521 24级分频器CD4522 可预置BCD同步1/N计数器CD4526 可预置4位二进制同步1/N计数器CD4527 BCD比例乘法器CD4528 双单稳态触发器CD4529 双四路/单八路模拟开关CD4530 双5输入端优势逻辑门CD4531 12位奇偶校验器CD4532 8位优先编码器CD4536 可编程定时器CD4538 精密双单稳CD4539 双四路数据选择器CD4541 可编程序振荡/计时器CD4543 BCD七段锁存译码,驱动器CD4544 BCD七段锁存译码,驱动器CD4547 BCD七段译码/大电流驱动器CD4549 函数近似寄存器CD4551 四2通道模拟开关CD4553 三位BCD计数器CD4555 双二进制四选一译码器/分离器556 双二进制四选一译码器/分离器CD4558 BCD八段译码器CD4560 "N"BCD加法器CD4561 "9"求补器CD4573 四可编程运算放大器CD4574 四可编程电压比较器CD4575 双可编程运放/比较器CD4583 双施密特触发器CD4584 六施密特触发器CD4585 4位数值比较器CD4599 8位可寻址锁存器。

74LS194左右移位寄存器

74LS194左右移位寄存器4位移位寄存器仿真其中,3D、2D、1D、0D为并行输入端;3Q、2Q、1Q、0Q为并行输出端;R S为右移串行输入端;L S为左移串行输入端;1S、0S为操作模式控制端;R C为直接无条件清零端;CP为时钟脉冲输入端。

74LS194有5种不同操作模式:并行送数寄存;右移(方向由3Q→0Q);左移(方向由0Q→3Q);保持及清零。

1S、0S和R C端的控制作用如表3.10.1所示。

表3.10.1:输入输出功能移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或并行数据转换为串行数据等。

把移位寄存器的输出反馈到它的串行输入端,就可进行循环移位,如图3.10.2所示。

把输出端0Q 和右移串行输入端RS 相连接,设初始状态3Q2Q 1Q 0Q =1000,则在时钟脉冲作用下,3Q2Q 1Q 0Q 将依次变为0100→0010→0001→1000→……,可见,它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。

图3.10.2电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。

图3.10.2四、实验室操作实验内容:1.逻辑功能验证移位寄存器(1)将两块74LS74集成片插入IC 空插座中,按图41(a)连线,接成左移移位寄存器。

接好电源即可开始实验。

先置数据0001,然后输入移位脉冲。

置数,即把Q3、Q2、Q1、Q置成0001,按动单次脉冲,移位寄存器实现左移功能。

(2)按图42(b)连线,方法同(1)则完成右移移位功能验证。

(a)左移移位(b)右移移位图41 D触发器组成移位寄存器的实验线路图(1). 并行输入:参阅图 3.10.3,设计画出实验电路图,在THD-1型(或Dais-2B型)实验台上将实验线路搭好。

根据74LS194功能表3.10.1要求,进行并行输入实验,并填写表3.10.2。

双向移位寄存器

一、课程设计的目的与要求1.设计目的●熟悉MAXPLUS2/Quartus II软件,掌握软件的VHDL程序输入、程序编译和程序仿真操作;●学习利用VHDL语言设计双向移位寄存器电路程序。

2.设计要求根据设计正文提出的双向移位寄存器功能设置,实现电路设计。

二、设计正文●双向移位寄存器有三种输入方式:4位并行输入、1位左移串行输入、1位右移串行输入;●双向移位寄存器有一种输出方式:4位并行输出。

双向移位寄存器工作过程如下:●当1位数据从左移串行输入端输入时,首先进入内部寄存器最高位,并在并行输出口最高位输出,后由同步时钟的上跳沿触发向左移位。

●当1位数据从右移串行输入端输入时,首先进入内部寄存器最低位,并在并行输出口的最低位输出,后由同步时钟的上跳沿触发向右移位。

双向移位寄存器的输入、输出端口如下:CLR:异步清零输入端;SRSI:串行右移输入端;SLSI:串行左移输入端;A、B、C、D:4位并行输入端;QA、QB、QC、QD:4位并行输出端;S0,S1:两位控制码输入端。

双向移位寄存器的端口功能如下:当CLR=0时,4位输出端清0;当CLK=0时,4位输出端保持原来状态不变;当S=00时,4位输出端保持原来的状态不变;当S=01时,允许串行右移输入1位数据;当S=10时,允许串行左移输入1位数据;当S=11时,允许4位数据从并行端口输入。

VHDL源程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL; ——包含库和程序包entity double_dir_regt is ——定义实体为double_dir_regtport ( s: in std_logic_vector(1 downto 0);clr,clk,srsi,slsi,a,b,c,d:in std_logic;result: out std_logic_vector(3 downto 0));——设置端口参数输入控制信号s,时钟clk,并行输入abcd, end double_dir_regt; 输出result ARCHITECTURE rtl of double_dir_regt issignal result1: std_logic_vector(3 downto 0);——设置信号result1使result能作为输入使用beginresult<=result1;process (clk,clr) ——敏感信号为时钟和清零信号beginif (clr='0')thenresult1<="0000";elsif (clk'event and clk='1')thencase s iswhen "00"=> ——控制信号为00时实现保持功能result1(0)<=result1(0);result1(1)<=result1(1);result1(2)<=result1(2);result1(3)<=result1(3);when"01"=> ——控制信号为01时实现右移功能result1(3)<=srsi;result1(2)<=result1(3);result1(1)<=result1(2);result1(0)<=result1(1);when"10"=> ——控制信号为10时实现左移功能result1(0)<=slsi;result1(1)<=result1(0);result1(2)<=result1(1);result1(3)<=result1(2);when"11"=> ——控制信号为11时实现并行输入功能result1(0)<=a;result1(1)<=b;result1(2)<=c;result1(3)<=d;end case;end if; ——程序结束end process;end rtl;三、课程设计总结1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0图表1双向移位寄存器右移仿真波形图由上图1看出当s0s1=01时,寄存器执行右移功能,并可看出srsi=1100110011001100,输出结果result依次由初始状态0000,逐渐右移左端输入端口输入srsi=1100110011001100,此时result依次会出现1000:移入1;1100:移入两个1;0110:移入两个1一个0;再有以后出现的结果0011,1001,1100,0110,0011,1001,1100……..此结果符合真值表要求的右移功能。

4000系列数字电路

4000 双3输入或非门加1输入反相器Y=/A+B+C;Z=/D。

4001 四2输入或非门Y=/A+B、4002、74HC4002 双4输入或非门Y=/A+B+C+D。

4006 18位串入串出静态移位寄存器由四组移位寄存器组成,其中由两组为4位,每组有一个输出端,由最高们引出,另两组为5位,每组有两个输出端,分别在最高位和次高位引出,这四组有公共时钟输入端,这四组均有公共输入端,每组均有一个数据D输入。

4007 双互补对加反相器4008 4位二进制超前进位全加器该电路包括4对二进制加数,还有一个最低位的进位输入端;输出包括4位和输出以及这4位数的进位输出端。

功能表4009、4010 门缓冲器/电平变换器用做缓冲器驱动或高到低逻辑摆幅变换,CMOS与TTL接口;双电源供电,且应VDD≥VCC,4009为反相缓冲器/变换器,Y=/A;4010为同相缓冲器/变换器,Y=A。

4011 四2输入与非门Y=/AB。

4012双4输入与非门Y=/ABCD。

4013 双D型触发器(带预置和清除端)功能表4014 8位串入/并入—串出移位寄存器同步静态移位寄存器;串入或串出的数据都要与时钟上升沿同步,才能进入寄存器中;寄存单元是带预置端的D型主从触发器;有三个输出端,分别设在第6、7、8位寄存器上。

功能表4015、74HC4015 双4位串入—并出移位寄存器每组都有一个时钟、清除和串入端;加在DS端上得数据在时钟脉冲上升沿的作用下向右移位。

功能表4016、74 HC4016 四双向模拟开关合何一个模拟输入端可以用做输出端,反之亦然;当然CTL为地电平时各开关截止,CTL为高电平时各开关导通。

4017、74 HC4017 十进制计数/分频器该器件是具有10个译码输出的5段约翰逊计数器;每个译码输出通常处于低电平,且在时钟脉冲由低到高的转换过程中依次进入高电平;每输出在高电平维持10个时钟周期中的1个时钟周期;输出10进入低电平后进位输出由低转到高,并能与时钟允许端连接成N级,74 HC4017的典型工作频率为30MHz。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

40194四位双向移位寄存器

40194 为4 位通用移位寄存器,具有并行输入/并行输出,左移、右移等功能。

40194 的工作模式由两个模式选择输入端SELECT0 和SELECT1 确定,当处于SELECT0=SELECT1=“1”时,并行输入端在时钟上升沿并行数据输入端。

D0~D3 的数据置入4 位寄存器中并由Q 端输出。

进行左移或右移操作时,SHIFTRIGHT IN 和SHIFT LEFT IN 端上的数据在时钟上升沿分别串行移入寄存器中,当

/RESET 为低电平时,输出全零状态。

引出

S1 S0

0 0 保持不变

0 1 实行右移

1 0 实行左移

1 1 运行置数

R 清零;低电平有效

40192------十进制同步加/减计数器(有预置端,双时钟)

简要说明:

40192 为可预置BCD 可逆计数器,其内部主要由四位D 型触发器组成,与一

般计数器不同之处在于加计数器和减计数器分别由两个时钟输入端。

40192 具有复位CR、置数控制/LD、并行数据D0~D3、加计数时钟CPu、减计数时钟CP D 等输入,当CR 为高电平时,计数器置零。

当/LD 为低电平时,进行预置数操作,D0~D3 上的数据置入计数器中,计数操作由两个时钟输入控制。

当CP D=“1”时,在CPu 上跳变时计数器加1 计数;当CPu=“1”时,在CP D 上跳变计数器减1 计数。

除四个Q 输出外,40192 还有一个进位输出/CO 和一个借位输出/BO,/CO 和/BO 一般为高电平,只有在加计数模式,当计数器达到最大状态时,/CO 输出一个宽度为半个时钟周期的负脉冲,在减计数模式,当计数器全为零时,/BO 输出一个宽度为半个时钟周期的负脉冲。

引出端符号:

CR 清除端;CP D 减计数时钟输入端;CPu 加计数时钟输入端;D0~D3 并行数据输入端;Q0~Q3 计数器输出端;/BO 借位输出端;/CO 进位输出端

V DD 正电源;Vss 地

引出

真值表:

40192功能输入端PE R

0 0 置数

1 0 计数

× 1 清零。