基于FPGA二选一数据选择器

二选一数据选择器

郑州工商学院

实验报告册所属课程名称:EDA技术及应用

院部:工学院

专业:电子科学与技术

班级:1702班

学号:170508070246

姓名:刘应许

指导教师:靳世红

1.新建一个工程,为工程指定工作目录,分配工程名称以及指定是最高层设计实体名称.将设计文件加入工程中,选择目标器件,选择综合器和仿真器,结束设计.

2.输入源文件,选择源文件类型,之后出现原理图文件编辑界面,工程中出现Block1.vhd文件.

3.输入VHDL代码.

4.打开波形编辑器,输入信号节点,编辑输入信号波形,观察仿真结果.仿真完成后可查看输出波形.

5.查看电路图.

二选一数据选择器

三人表决器。

实验三4位2选1多路选择器的设计与实现

实验三 4位2选1多路选择器的设计与实现一.实验目的1.使用ISE软件设计并仿真;2.学会程序下载。

二.实验内容使用ISE软件进行4位2选1多路选择器的设计与实现。

三.实验步骤1. 编写文本文件并编译2. 软件仿真3. 进行硬件配置四.实验原理1. ISE软件是一个支持数字系统设计的开发平台。

2. 用ISE软件进行设计开发时基于相应器件型号的。

注意:软件设计时选择的器件型号是与实际下载板上的器件型号相同。

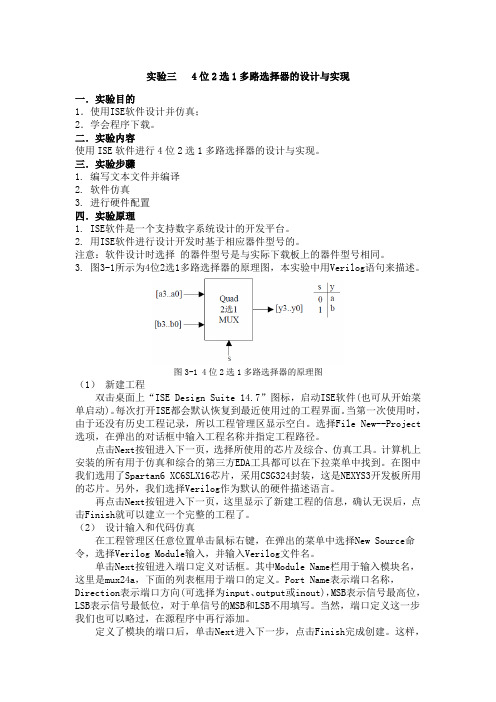

3. 图3-1所示为4位2选1多路选择器的原理图,本实验中用Verilog语句来描述。

图3-1 4位2选1多路选择器的原理图(1)新建工程双击桌面上“ISE Design Suite 14.7”图标,启动ISE软件(也可从开始菜单启动)。

每次打开ISE都会默认恢复到最近使用过的工程界面。

当第一次使用时,由于还没有历史工程记录,所以工程管理区显示空白。

选择File New--Project 选项,在弹出的对话框中输入工程名称并指定工程路径。

点击Next按钮进入下一页,选择所使用的芯片及综合、仿真工具。

计算机上安装的所有用于仿真和综合的第三方EDA工具都可以在下拉菜单中找到。

在图中我们选用了Spartan6 XC6SLX16芯片,采用CSG324封装,这是NEXYS3开发板所用的芯片。

另外,我们选择Verilog作为默认的硬件描述语言。

再点击Next按钮进入下一页,这里显示了新建工程的信息,确认无误后,点击Finish就可以建立一个完整的工程了。

(2)设计输入和代码仿真在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择New Source命令,选择Verilog Module输入,并输入Verilog文件名。

单击Next按钮进入端口定义对话框。

其中Module Name栏用于输入模块名,这里是mux24a,下面的列表框用于端口的定义。

Port Name表示端口名称,Direction表示端口方向(可选择为input、output或inout),MSB表示信号最高位,LSB表示信号最低位,对于单信号的MSB和LSB不用填写。

基于FPGA的2选1多路选择器设计

基于FPGA的2选1多路选择器设计1. 项⽬介绍 多路选择器,也叫数据选择器或多路开关,在多路数据传送过程中,能够根据需要将其中任意⼀路选出来的电路。

数据选择器⽤于控制有效数据的输出,能够通过地址选择线来选定相应的通道作为输出,提⾼了数据的传输效率。

(数据分配器⽤于数据的传输途径,在信号传输过程中能够通过地址选择线选择传输信道)。

2. 设计要求 设计⼀个2选1多路选择器,输⼊有两个单bit信号,和⼀个单bit的选择信号。

当选择信号为低电平时,将第⼀路信号输出,当选择信号为⾼电平时,将第⼆路信号输出。

3. 设计原理 该设计命名为mux2_1,第⼀路信号命名为dataa,第⼆路信号命名为datab,选择信号命名为sel,输出信号命名为odata,系统框图如下图所⽰。

根据设计要求,得真值表:dataa datab sel odata00000010010001111001101011011111 根据真值表,得到逻辑表达式: 转化为Verilog表达式为Odata = datab&sel | dataa&(~sel);4. 设计实现1module mux2_1(23input wire dataa,4input wire datab,5input wire sel,67output wire odata8 );910assign odata = (datab & sel) | (dataa & (~sel));1112endmodule5. 仿真验证1 `timescale 1ns/1ps23module mux2_1_tb();45reg dataa;6reg datab;7reg sel;89wire odata;1011 mux2_1 mux2_1_inst(12 .dataa (dataa),13 .datab (datab),14 .sel (sel),15 .odata (odata)16 );1718initial begin19 dataa = 1'b0; datab = 1'b0; sel = 1'b0; #20;20 dataa = 1'b0; datab = 1'b0; sel = 1'b1; #20;21 dataa = 1'b0; datab = 1'b1; sel = 1'b0; #20;22 dataa = 1'b0; datab = 1'b1; sel = 1'b1; #20;23 dataa = 1'b1; datab = 1'b0; sel = 1'b0; #20;24 dataa = 1'b1; datab = 1'b0; sel = 1'b1; #20;25 dataa = 1'b1; datab = 1'b1; sel = 1'b0; #20;26 dataa = 1'b1; datab = 1'b1; sel = 1'b1; #20; 27end2829endmodule参考资料: (1);。

二选一数据选择器

二选一数据选择器目录一:数据选择器的基本原理 (3)二电路逻辑功能 (2)2.1 电路逻辑图 (2)2.2真值表与表达式 (3)2.3电路设计及仿真 (3)三版图设计 (5)3.1总体版图设计及DRC验证 (5)3.1.1数据选择器版图设计步骤 (5)3.1.2版图验证 (8)3.2版图仿真 (9)四数据选择器版图LVS对比 (10)五结论及体会 (12)一:数据选择器的基本原理数据选择器是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去,实现数据选择功能的逻辑电路称为数据选择器。

它的作用相当于多个输入的单刀多掷开关,其示意图如下:图1 n位通道选择信号数据选择器除了可以实现一些组合逻辑功能以外,还可以做分时多路传输电路、函数发生器及数码比较器等。

常见的数据选择器有4选1、8选1、16选1电路。

在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器数据选择器(MUX)的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号下图所示为二选一数据选择器原理图,a,b为输入端,sel为控制端,out为输出端图1-1数据选择器原理图二电路逻辑功能2.1 电路逻辑图=+(S是数据选择控制端,S为0时选择A,为1时选S择B)Y SA SB要实现2选1选择器,逻辑电路图如下所示图2-1数据选择器逻辑电路图2.2真值表与表达式二选一数据选择器逻辑表达式为:Y SA SB =+根据逻辑表达式所列真值表如下图所示图2-2数据选择器真值表图2.3电路设计及仿真根据原理电路图并使用S-Edit 软件设计出数据选择器的电路图及对应符号图如下:S A B Y 01 1 1 1 0 1 0 1 0 0 0 0 1 1 1 1 1 0 0 0 1 1 0图2-3数据选择器符号图根据符号图并使用S-Edit软件设计出的数据选择器电路图如下所示图2-4数据选择器电路图导出的SPICE文件,如下图所示图2-5 spice文件加载包含文件,如下图所示图2-6 加载后的SPICE文件在其基础上进行仿真:下图从上到下依次为Y. S B A,结合逻辑表达式及真值表可知,电路为正确的图2-7 模拟波形仿真图三版图设计3.1总体版图设计及DRC验证3.1.1数据选择器版图设计步骤(1)新建文件夹:在电脑本地磁盘新建文件夹,文件夹名为shuju。

基于FPGA的驻波演示实验设计

基于FPGA的驻波演示实验设计作者:李维郑江来源:《西部论丛》2019年第30期摘要:将振幅相同的两列并行的相干波,传播轨迹是沿同一直线但是波的传播方向相反,进而会形成互相相交,而且不会沿着向前推进的波,广泛的在物理学中被称之为驻波。

本次实验主要中心是由拾音器收集到的模拟信号的A/D转换接入FPGA,然后对数字信号进行处理,再用VGA把所收集到的信号显示出来。

结合各种软件硬件有效的綜合,生成一个驻波的波形的演示设备。

关键词:驻波演示; FPGA; 乒乓缓存机制; VGA显示引言驻波为一种非常常见的现象,任何弦乐发声都基于驻波。

本次设计的这种驻波演示设计运用的FPGA为主控制器。

基于FPGA的驻波演示实验,该设计有着FPGA的优势。

以FPGA器件xc7a35tcpg236-1为控制核心,使用Vivado 2018.2进行软件编程进而实现声波驻波的VGA 显示。

1. 驻波演示的研究现状如今对于声波驻波的研究已经非常的成熟了,对于设计声波驻波演示的方法也非常的多,大多数物理观测的方法中最为常见的是昆特管法和示波器演示法。

昆特管是最为传统的声波中驻波的发生器,它是由两个器件构成,一个为透明的有机玻璃管,另一个为扬声器。

使一端用密闭塞子堵塞,把另一端口选择合适位置放置扬声器,启动扬声器,它发出一条入射声波到达另一边塞子处,通过反射原理声波进行反射回来,反射波与入射波相互干涉进而完成驻波的生成[1]。

2.驻波演示设计的框架次设的主要构成驻波演示实验的主要构成包括拾音器、数据选择器、A/D数模转换器、FPGA控制电路和VGA显示器所构成。

多个拾音器接收多个信号,需要将接收到的数据进行选择性的输出到后一模块。

设计出数据选择器,然后接到ADC转换芯片的内部去依次进行数据的模数转换。

已转换的数字信号经过控制系统FPGA中内部的双端口RAM读写模块把数据处理存储,并且传输到VGA接口进行处理,使用VGA显示技术把我们所要观测到的声波驻波信号显示在屏幕上。

基于FPGA实现四选一选择器的设计

基于FPGA实现四选一选择器的设计摘要本文是基于FPGA的四选一选择器的设计:基于FPGA在数据选择方面的优势,把FPGA作为选择器的控制核心;主要研究如下:软件部分——四选一选择器程序。

针对数据选择器的设计,对FPGA进行了型号选择,使用VHDL语言在型号FLEX10K/20RC208-4上编写了四选一选择器的程序,通过使能端的控制,从而达到四选一的功能。

硬件部分——使用protel画出原理图并作出PCB板。

本设计采用了单八路模拟开关CD4051,通过输入端的控制,选择一路信号,通过ADC0804模数转化,输出8路信号给FLEX10K/20RC208-4,经FLEX10K/20RC208-4处理后,接TCL7528后,将数字信号转换为模拟信号并输出。

本文通过软件和硬件的两个方面的设计,实现了四选一选择器的功能。

关键词:FPGA ;VHDL ;PROTEL ;选择器内蒙古科技大学毕业设计说明书(毕业论文)FPGA implementation based on four selected design of a selectorAbstrateThis article is based on a choice selection of four FPGA Design: FPGA-based data selection in the advantages of the FPGA as a selector control center; main research are as follows:Software parts - 4 election a choice program. Design for data selection, model selection on the FPGA, using the VHDL language in the model FLEX10K/20RC208-4 four selected to write a program selector, by enabling the client to control, so as to achieve a function of four elections.Hardware - protel schematic drawing and make a PCB board. This design uses a single eight-way analog switches CD4051, through the control input, select the way the signal, ADC0804 module through the transformation of the output signal 8 to FLEX10K/20RC208-4, by FLEX10K/20RC208-4 treatment, then TCL7528, will digital signal is converted to analog signals and output.In this paper, two aspects of hardware and software design, implementation, choose one of four selector functions.Keywords: FPGA ; VHDL ; ROTEL ; selectorI目录摘要 .............................................................................................................................................. Abstrate (I)第一章绪论 01.1 FPGA简介 01.1.1 FPGA发展现状 01.1.2 FPGA的发展趋势 (1)1.1.3 FPGA基本结构 (1)1.1.4 FPGA的特点 (3)1.1.5 FPGA选型 (4)1.1.6 FPGA设计原则 (5)1.2本论文研究的主要内容 (6)第二章FPGA芯片设计 (7)2.1 BTYG-EDA实验开发系统简介 (7)2.1.1 BTYG-EDA实验开发系统特点 (7)2.1.2 BTYG-EDA实验开发系统资源介绍 (7)2.1.3 主芯片引脚和外部硬件连接关系 (7)2.2 FLEX10K/20RC208-4 (11)2.3 本章小结 (13)第三章MAX+plus II软件和VHDL语言――软件部分 (14)3.1 MAX+plus II开发软件 (14)3.1.1 MAX+plus II功能特点 (14)3.1.2 MAX+plus II系统要求 (15)3.1.3 MAX+plus II设计流程 (15)3.2 VHDL语言简介 (18)3.2.1 VHDL基本介绍 (18)3.2.2 VHDL语言的特点 (19)3.2.3 VHDL系统优势 (20)II内蒙古科技大学毕业设计说明书(毕业论文)3.2.4 VHDL程序基本结构 (20)3.3 MAX十plus II中硬件描述语言输入的设计过程 (21)3.3.1 输入VHDL文件 (21)3.3.2 将文件指定为设计项目 (21)3.3.3 项目编译 (22)3.3.4 项目仿真 (22)3.4 程序仿真介绍及仿真图 (22)3.5本章小结 (24)第四章protel99——硬件部分 (25)4.1 protel简介 (25)4.1.1 Protel99SE的功能特点 (25)4.1.2 用Protel99SE进行电路设计的步骤 (26)4.2 四选一选择器的原理图及各元件介绍 (26)4.3 本章小结 (33)第五章总结与展望 (34)5.1 取得的成果 (34)5.2 工作展望 (34)参考文献 (35)附录A (36)附录B (37)致谢 (39)III第一章绪论1.1 FPGA简介1.1.1 FPGA发展现状当今社会是数字化的社会,是数字集成电路广泛应用的社会,数字集成电路本身在不断地进行更新换代。

(完整word版)2选1多路选择器数选器muxverilog

2 实验22。

1 实验内容题目:设计一个1位的二选一多路选择器要求:1.使用门级描述实现 2。

使用逻辑表达式实现 3。

使用if条件语句实现4。

出现正确的仿真波形,无需板子上验证。

2.2 实验步骤1.系统设计设计1位2选1选通器需要三个输入一个输出,其中中输入需要1根地址线两根数据线.设输入一位数据a,b,地址为addr,输出为Out,根据2to1选通器的特点,可得其逻辑表达式为:_______out=a·addr+b·addr(1)门级描述需要两个与门一个非门一个或门,其中所有变量均为wire类型,且需要三个wire类型中间变量储存信号.(2)逻辑表达式源代码中用assign out=sel?a:b;或 assign out=(a&sel)|(b&~sel);(3)If条件语句If语句在always语句中进行判断。

2.RTL原理图(1)门级结构(2)逻辑语句使用两种逻辑语句进行RTL分析结果略有不同,out=sel?a:b;会分析出来一个2选1选通器而out=(a&sel)|(b&~sel);分析结果与门级结构类似1)out=sel?a:b;2)out=(a&sel)|(b&~sel);(3)if语句3.重要源代码及注释(1)门级结构module mux2_1(a,b,out,addr);input a,b,addr;output out;wire naddr,a1,b1;//定义中间变量not (naddr,addr);and (b1,b,naddr);and (a1,a,addr);or (out,a1,b1);endmodule(2)逻辑语句module luoji(input a,input b,input sel,output out);assign out=(a&sel)|(b&~sel);endmodule(3)if语句module mux2_1if(a,b,sel,out);input a,b,sel;output out;reg out;always@(a or b or sel)beginif(sel) out=a;else out=b;end2。

EDA技术及应用—基于FPGA的电子系统设计:基于Verilog hdl的数字电路设计

10100

1111

15

10101

8421BC 余三码 D码

0000

0011

0001

0100

0010

0101

0011

0110

0100

0111

0101

1000

0110

1001

0111

1010

1000

1011

1001

1100

-

-

-

-

-

-

-

-

-

-

-

-

4位格雷码

0000 0001 0011 0010 0110 0111 0101 0100 1100 1101 1111 1110 1010 1011 1001 1000

4'b0011:a_to_g=7'b1111001; //显示3

4'b0100:a_to_g=7'b0110011; //显示4

4'b0101:a_to_g=7'b1011011; //显示5

4'b0110:a_to_g=7'b1011111; //显示6

4'b0111:a_to_g=7'b1110000; //显示7

4: y= {d[2:0],d[3]}; // rol

5: y= {d[3],d[3:1]}; // asr

6: y= {d[1:0],d[3:2]}; // ror2

7: y= d;

// noshift

default: y = d;

图6-2 基本门电路仿真结果

综合结果如图6-3所示。

图6-3 基本门电路综合结果

2、 三态逻辑电路

基于fpga的四选一数据选择器和一位全加器的设计

ENTITY mux21 ISPORT(A,B,S : IN BIT;Y : OUT BIT);END ENTITY mux21;ARCHITECTURE one OF mux21 ISBEGINY <= A WHEN S= '0' ELSE B;END ARCHITECTURE one;ENTITY xor2 ISport(a,b : in bit;c : out BIT);end entity xor2;ARCHITECTURE one OF xor2 ISbeginc <= '0' when a=b else '1' ;end ARCHITECTURE one;ENTITY mux41 ISPORT(A,B,C,D,S1,S2 : IN BIT;Y : OUT BIT);END ENTITY mux41;ARCHITECTURE ons OF mux41 IS COMPONENT mux21PORT(A,B,S : IN BIT;Y : OUT BIT);END COMPONENT;COMPONENT xor2port(a,b : in bit;c : out bit);END COMPONENT;SIGNAL d1,e,f : bit ;BEGINu1 : mux21 PORT MAP(A=>A,B=>B,S=>S1,Y=>e); u2 : mux21 PORT MAP(A=>C,B=>D,S=>S2,Y=>f); u3 : xor2 PORT MAP(a=>S1,b=>S2,c=>d1);u4 : mux21 PORT MAP(A=>e,B=>f,S=>d1,Y=>Y); END ARCHITECTURE ons;(四选一)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY h_adder ISPORT(A,B : IN STD_LOGIC;CO,SO : OUT STD_LOGIC);END ENTITY h_adder;ARCHITECTURE fh1 OF h_adder ISBEGINSO <= NOT(A XOR (NOT B));CO <= A AND B;END ARCHITECTURE fh1;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY or2a ISPORT(a,b : IN STD_LOGIC;c : OUT STD_LOGIC);END ENTITY or2a;ARCHITECTURE one OF or2a ISBEGINc <= a OR b;END ARCHITECTURE one;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY f_adder ISPORT(ain,bin,cin : IN STD_LOGIC;cout,sum : OUT STD_LOGIC);END ENTITY f_adder;ARCHITECTURE fd1 OF f_adder ISCOMPONENT h_adderPORT(A,B : IN STD_LOGIC;CO,SO : OUT STD_LOGIC);END COMPONENT;COMPONENT or2aPORT(a,b : IN STD_LOGIC;c : OUT STD_LOGIC);END COMPONENT;SIGNAL d,e,f : STD_LOGIC;BEGINu1 : h_adder PORT MAP(A=>ain, B=>bin, CO=>d, SO=>e); u2 : h_adder PORT MAP(A=>e, B=>cin, CO=>f, SO=>sum); u3 : or2a PORT MAP(a=>d, b=>f, c=>cout);END ARCHITECTURE fd1;LIBRARY IEEE;(一位全加器)。

2选1数据选择器的VHDL描述

2选1数据选择器的VHDL描述ENTITY mux21a ISPORT( a, b : IN BIT ;s : IN BIT;y : OUT BIT ) ;END ENTITY mux21a ;ARCHITECTURE one OF mux21a ISBEGINy <= a WHEN s = '0'ELSE b ;END ARCHITECTURE one ;译码器的设计architecture dec_behave of e1 issignal sel : std_logic_vector( 0 to 3) ;beginsel(0) <= en ; sel(1) <= a(0) ; sel(2) <= a(1) ; sel(3) <= a(2) ;with sel selecty <= "00000001" when "1000","00000010" when "1001","00000100" when "1010","00001000" when "1011","00010000" when "1100","00100000" when "1101","01000000" when "1110","10000000" when "1111","00000000" when others ;end dec_behave ;8-3优先编码器library IEEE; ……;entity encoder83 isport (ind: in std_logic_vector(7 downto 0);outd: out std_logic_vector(2 downto 0));end ;architecture behave of encoder83 isbeginprocess (ind)beginif ind (7) = ‘1' then outd<= "111";elsif ind (6) = ‘1' then outd<= "110";elsif ind (5) = ‘1' then outd<= "101"; elsif ind (4) = ‘1' then outd<= "100"; elsif ind (3 )= ‘1' then outd<= "011"; elsif ind (2) = ‘1' then outd<= "010"; elsif ind (1) = ‘1' then outd<= "001"; elsif ind (0) = ‘1' then outd<= "000"; else outd<= "000";end if;end process; end behave;。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.实验目的:

了解二选一数据选择器的原理。

熟悉Quartus II的使用,熟练掌握程序的编译,波形的仿真及下载的过程。

2实验内容:

编写二选一数据选择器的程序,并编译,下载到试验箱中查看结果。

3.实验方案(程序设计说明)

三个输入变量:a,b和s

一个输出变量:y

当s等于0时,a赋值给y;当s不等于0时,b赋值给y。

begin

process(a,b,s)

begin

if s<='0' then

y<=a;

else

y<=b;

end if;

end process;

end rtl;

管脚设置:

4.实验步骤或程序(经调试后正确的源程序)

见附件A

5.程序运行结果

6.出现的问题及解决方法

在设置输入波形时对高低电平时间及周期设置掌握不牢固。

附件A

实验步骤或程序:

程序:

entity mux2 is

port(a,b,s:in bit;

y:out bit);

end mux2;

architபைடு நூலகம்cture rtl of mux2 is