模拟集成电路ppt课件

合集下载

CMOS 模拟集成电路课件完整

反偏电压将使耗尽区变宽,从而降低了有效沟道深度。因此,需 要施加更大的栅极电压以弥补沟道深度的降低,VSB偏压会影响 MOSFET的有效阈值电压VTH。随着VSB反偏电压的增加导致VTH的增 加,这种效应称为“体效应”。这种效应也称为“衬底偏置效应” 或“背栅效应”。

VTHN VTHN0

2qsi Na Cox

VGS 1 0 1.0 VDS 2 0 5

.op .dc vds 0 5 .2 Vgs 1 3 0.5 .plot dc -I(vds) .probe

*model .MODEL MNMOS NMOS VTO=0.7 KP=110U +LAMBDA=0.04 GAMMA=0.4 PHI=0.7

.end

Systems

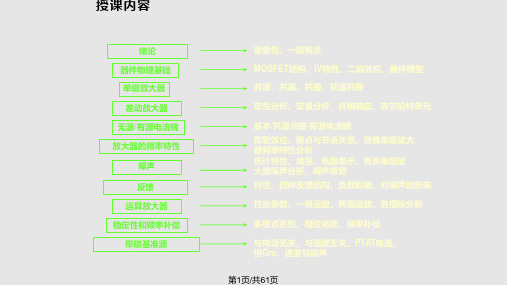

Ch13 开关电容电路

Ch14 DAC/ADC

complex Ch10 运算放大器 Ch7 频率响应

Ch11 稳定性和频 率补偿

Ch8 噪声

Ch12 比较器 Ch9 反馈

Ch3 电流源电流镜 simple Ch4 基准源 Circuits

Devices

Ch5 单级放大器 ch2 MOS器件

*Output Characteristics for NMOS M1 2 1 0 0 MNMOS w=5u l=1.0u

VGS 1 0 1.0 VDS 2 0 5

设计

属性/规范

系统/电路1

系统/电路2 系统/电路3

……

一般产品描述、想法 系统规范要求的定义

系统设计 电路模块规范定义

电路实现 电路仿真

否

是否满足系统规范

是 物理(版图)设计

物理(版图)验证

寄生参数提取及后仿真

否

是否满足系统规范

VTHN VTHN0

2qsi Na Cox

VGS 1 0 1.0 VDS 2 0 5

.op .dc vds 0 5 .2 Vgs 1 3 0.5 .plot dc -I(vds) .probe

*model .MODEL MNMOS NMOS VTO=0.7 KP=110U +LAMBDA=0.04 GAMMA=0.4 PHI=0.7

.end

Systems

Ch13 开关电容电路

Ch14 DAC/ADC

complex Ch10 运算放大器 Ch7 频率响应

Ch11 稳定性和频 率补偿

Ch8 噪声

Ch12 比较器 Ch9 反馈

Ch3 电流源电流镜 simple Ch4 基准源 Circuits

Devices

Ch5 单级放大器 ch2 MOS器件

*Output Characteristics for NMOS M1 2 1 0 0 MNMOS w=5u l=1.0u

VGS 1 0 1.0 VDS 2 0 5

设计

属性/规范

系统/电路1

系统/电路2 系统/电路3

……

一般产品描述、想法 系统规范要求的定义

系统设计 电路模块规范定义

电路实现 电路仿真

否

是否满足系统规范

是 物理(版图)设计

物理(版图)验证

寄生参数提取及后仿真

否

是否满足系统规范

《模拟集成电路基础》PPT课件

h

20

P

N

V

PN结的接触电位

(二)PN结的接触电位:

(1).内电场的建立,使PN结 中产生电位差。从而形成接 触电位V(又称为位垒)。

(2).接触电位 V决定于材 料及掺杂浓度:

硅: V=0.7 锗: V=0.2 (3).其电位差用 表示

h

21

(三)PN结的单向导电性

U

I

P

N

扩散

Q(V-U)

1.PN结加正向电压时:

第四节 二极管的应用

h

8

第一节 半导体基础知识

一1.、什半么导是体导的体特、性绝:缘体导、电半导率量导电1级0体率-2,2:为-如110:0-154s金.sc.、mc-m1-1

(1).导体:导电性能良好导量的电级物率,质为银如。1、:0-铜橡9-、胶10铝、2 s。云.c母m-、1 (2).绝缘体:几乎不导电量砷塑的级化料物,镓等质如等。。:。硅、锗、 (3).半导体:导电能力介于导体和半导体之间。

生载流子的扩散运用动下的定结向果移产动生称空

间电荷区耗尽层为(漂多移子运运动动)。

空穴 P

(2).空间电荷区产生建立了内电场 产生载流子定向运动(漂移运动)

N

•当扩散运动↑内电场↑漂移运

动↑扩散运动↓动态平衡。

(3).扩散运动产生扩散电流;漂移运动 产生漂移电流。

•动态平衡时:扩散电流=漂移电流。 PN结内总电流=0。 PN结的宽度一定 。

1.电子空穴对: 电子和空穴是成对产生的.

h

12

两种载流子——电子和空穴

外电场E 的方向

电子流

2.自由电子——载流子:

自由电子

• 在外电场作用下形成电子流(在 导带内运动),

CMOS模拟集成电路分析与设计 ppt课件

如果栅电压为负,则耗尽层变薄,栅 与衬底间电容增大。

对于大的负偏置,则电容接近于CGC。

PPT课件

24

1.2 MOS管的极间电容(1)

G

S

C1

C2 C4

C3

Cbs

反型层 耗尽层

d

L

d

p型衬底

D

Cbd

PPT课件

25

1.2 MOS管的极间电容(2)

栅与沟道之间的栅氧电容:

C2=WLCox,其中Cox为单位面积栅氧电容εox/tox;

CMOS模拟集成电路分析与设计

主讲教师:吴建辉 Tel:83795677

E-mail:wjh@

PPT课件

1

教材及参考书

教材:

吴建辉编著:“CMOS模拟集成电路分析与设 计”(第二版),电子工业出版社。

参考书:

Razavi B: Design of analog CMOS integrated circuits

11

1、有源器件

主要内容:

1.1 几何结构与工作原理 1.2 极间电容 1.3 电学特性与主要的二次效应 1.4 低频及高频小信号等效模型 1.5 有源电阻

PPT课件

12

1.1 MOS管几何结构与工作原理(1)

B p+

G

tox

S

D

G D

n+

n+

p+

n阱 p型衬底

(a)

S

B

p+

n+

W

多晶

d p+接触孔

PPT课件

3

模拟电路与模拟集成电路

分立元件音频放大电路

晶体管数 匹配性 电阻值 电容值 寄生效应影响

CMOS-模拟集成电路课件-电流源与电流镜

+ VTHN+2VOD

W/(4L)

VB

-

M4

VDD

W/L

M0

W/L

M1

IREF

Z +

VOUT IOUT=IREF

W/L +

VOD -

M3

VOD -

+

W/L

+

VOD -

M2

VOD -

例4:自偏置 增加R使得 IREFR = VOD,

VGS1 = VTHN + VOD 这样,

VB= VTHN + 2VOD

IOUT

(W (W

/ L)2 / L)1

I REF

IOUT与IREF的比值由器件尺寸的比率决定,不受工艺 和温度的影响。设计者可以通过器件的尺寸比来调整 输出电流的大小。

在λ=0的情况下 !

2024/10/19

8

• 例子:

– 在电流镜电路的实际设计中,通常采 用叉指MOS管,每个“叉指”的沟道 长度相等,复制倍数由叉指数决定, 减小由于漏源区边缘扩散所产生的误 差,以减小器件的失配造成的电流失 配。.

2024/10/19

VDD IREF

+ VOD R

-

VB = 2VOD +VTHN VOUT

IOUT=IREF

+

M0 X

VOD

M3

Y+

VGS = +

VOD

M1 VOD +VTHN M2

-

16

-

小结

• 工作在饱和区的MOS晶体管可以充当电流源 • 基本电流镜—基于电流复制 • 共源共栅电流镜—提高复制精度 • 大输出摆幅共源共栅电流源—使得输出的下限等

模拟CMOS集成电路设计课件

医学图像处理、音频处理

PPT学习交流

6

5

2、集成电路工艺

速度高, 功耗大, 集成度低

最早MOS工 艺,速度低

超高速、高频 IC

光电集成器件

主流工艺,集 成度高、功耗 低、速度快、 抗干扰性强

PPT学习交流

7

6

CMOS工艺

B

S

G

D

B

S

G

D

n+

n+

p+

p+

p 型衬底

n 型阱

n 阱CMOS工艺

B

S

G

D

20

沿沟道x点处的电荷密度为: 沟道x点的电势,以源级为参考点

电流为:

载流子为电子,电荷为负,电荷运动方向与电流 方向相反

其中: 得到:

v=μE μ为载流子的迁移率,E为电场 E=-dV(x)/dx

PPT学习交流

22

21

在整个沟道长度内积分得:

由于ID沿沟道方向是常数,因此:

电流随VGS的 增大而增加

漏极的反型层消失,出现由耗尽层

构成的夹断区。

➢电子沿沟道从源极向漏极运动,达

到夹断区边缘时,受夹断区强电场

的作用,很快漂移到漏极。 B

➢VDS的变化主要体现在夹断区上,

p+

对沟道长度和沟道内的场强影响不

大,因此可以近似认为沟道电流保

p-

持恒定。

VDS

-+

-+

VGS

G

S

D

n+

n+

夹断区

PPT学习交流

20

19

2、NMOS 管IV特性推导与分析

PPT学习交流

6

5

2、集成电路工艺

速度高, 功耗大, 集成度低

最早MOS工 艺,速度低

超高速、高频 IC

光电集成器件

主流工艺,集 成度高、功耗 低、速度快、 抗干扰性强

PPT学习交流

7

6

CMOS工艺

B

S

G

D

B

S

G

D

n+

n+

p+

p+

p 型衬底

n 型阱

n 阱CMOS工艺

B

S

G

D

20

沿沟道x点处的电荷密度为: 沟道x点的电势,以源级为参考点

电流为:

载流子为电子,电荷为负,电荷运动方向与电流 方向相反

其中: 得到:

v=μE μ为载流子的迁移率,E为电场 E=-dV(x)/dx

PPT学习交流

22

21

在整个沟道长度内积分得:

由于ID沿沟道方向是常数,因此:

电流随VGS的 增大而增加

漏极的反型层消失,出现由耗尽层

构成的夹断区。

➢电子沿沟道从源极向漏极运动,达

到夹断区边缘时,受夹断区强电场

的作用,很快漂移到漏极。 B

➢VDS的变化主要体现在夹断区上,

p+

对沟道长度和沟道内的场强影响不

大,因此可以近似认为沟道电流保

p-

持恒定。

VDS

-+

-+

VGS

G

S

D

n+

n+

夹断区

PPT学习交流

20

19

2、NMOS 管IV特性推导与分析

模拟cmos集成电路设计拉扎维MOS器件物理基础PPT课件

定义从D流 向S为正 PMOS管电流驱动能力比NMOS管差 0.8 m nwell:p=250cm2/V-s, n=550cm2/Vs 0.5 m nwell:p=100cm2/V-s, n=350cm2/V-

第23页/共61页

跨导gm

VGS对IDS的控制能力 IDS对VGS变化的灵敏度

gm ID VGS VDS cons tant

• 直流关系式-I/V特性 • 交流关系式-小信号电路中的参数

第6页/共61页

MOS管简化模型

简化模型——开关 由VG控制的一个开关

第7页/共61页

MOS管的结构

Bulk(body)

源漏在物理结构上是完全对称的,靠什么区分开?

提供载流子的端口为源,收集载流子的端口为漏

最重要的工作区域?

受VG控制的沟道区

• 小信号模型 • 信号相对于偏置工作点而言比较小、不会显著影响偏置工作点时用该模型简化计算 • 由gm、 gmb、rO等构成低频小信号模型,高频时还需加上 CGS等寄生电容、寄生电阻(接触孔电阻、 导电层电阻等)

沟道电荷的产生

当VG大到一定 程度时,表面势 使电子从源流向 沟道区 VTH定义为表面电 子浓度等于衬底 多子浓度时的VG

第12页/共61页

阈值电压

0 栅与衬底功函数差

COX

OX

TOX

常通过沟道注入把VTH0调节到合适值 工艺确定后,VTH0就固定了,设计者无法改变

第13页/共61页

I/V特性-沟道随VDS的变化

第3页/共61页

掌握器件物理知识的必要性

• 数字电路设计师一般不需要进入器件内部,只把它当开关用即可 • AIC设计师必须进入器件内部,具备器件物理知识

• MOS管是AIC的基本元件 • MOS管的电特性与器件内部的物理机制密切相关,设计时需将两者结

第23页/共61页

跨导gm

VGS对IDS的控制能力 IDS对VGS变化的灵敏度

gm ID VGS VDS cons tant

• 直流关系式-I/V特性 • 交流关系式-小信号电路中的参数

第6页/共61页

MOS管简化模型

简化模型——开关 由VG控制的一个开关

第7页/共61页

MOS管的结构

Bulk(body)

源漏在物理结构上是完全对称的,靠什么区分开?

提供载流子的端口为源,收集载流子的端口为漏

最重要的工作区域?

受VG控制的沟道区

• 小信号模型 • 信号相对于偏置工作点而言比较小、不会显著影响偏置工作点时用该模型简化计算 • 由gm、 gmb、rO等构成低频小信号模型,高频时还需加上 CGS等寄生电容、寄生电阻(接触孔电阻、 导电层电阻等)

沟道电荷的产生

当VG大到一定 程度时,表面势 使电子从源流向 沟道区 VTH定义为表面电 子浓度等于衬底 多子浓度时的VG

第12页/共61页

阈值电压

0 栅与衬底功函数差

COX

OX

TOX

常通过沟道注入把VTH0调节到合适值 工艺确定后,VTH0就固定了,设计者无法改变

第13页/共61页

I/V特性-沟道随VDS的变化

第3页/共61页

掌握器件物理知识的必要性

• 数字电路设计师一般不需要进入器件内部,只把它当开关用即可 • AIC设计师必须进入器件内部,具备器件物理知识

• MOS管是AIC的基本元件 • MOS管的电特性与器件内部的物理机制密切相关,设计时需将两者结

《模拟集成电路》课件

,以便对设计的电路进行全面的测试和评估。

PART 05

模拟集成电路的制造工艺

REPORTING

半导体材料

硅材料

硅是最常用的半导体材料,具有 稳定的物理和化学性质,成熟的 制造工艺以及低成本等优点。

化合物半导体

如砷化镓、磷化铟等化合物半导 体材料,具有高电子迁移率、宽 禁带等特点,常用于高速、高频 和高温电子器件。

《模拟集成电路》课 件

REPORTING

• 模拟集成电路概述 • 模拟集成电路的基本元件 • 模拟集成电路的分析方法 • 模拟集成电路的设计流程 • 模拟集成电路的制造工艺 • 模拟集成电路的优化与改进

目录

PART 01

模拟集成电路概述

REPORTING

定义与特点

定义

模拟集成电路是指由电阻、电容、电 感、晶体管等电子元件按一定电路拓 扑连接在一起,实现模拟信号处理功 能的集成电路。

围和失真。

信号分析方法

01

02

03

04

频域分析

将时域信号转换为频域信号, 分析信号的频率成分和频谱特

性。

时域分析

研究信号的幅度、相位、频率 和时间变化特性,分析信号的

波形和特征参数。

调制解调分析

研究信号的调制与解调过程, 分析信号的调制特性、解调失

真等。

非线性分析

研究电路的非线性效应,分析 信号的非线性失真和互调失真

音频领域

模拟集成电路在音频领域中主要用于 音频信号的放大、滤波、音效处理等 功能,如音响设备、耳机等产品中的 模拟集成电路。

模拟集成电路的发展趋势

集成度不断提高

随着半导体工艺的不断发展,模 拟集成电路的集成度不断提高, 能够实现更加复杂的模拟信号处

模拟集成电路设计.ppt

1.物理图

§3-3: 其他MOS管大信号模型的参数

17

二、MOS电容

2. 耗尽结电容:CBD, CBS

P65 上式S→D 则 CBS→ CBD

18

§3-3: 其他MOS管大信号模型的参数

3.电荷存储电容: CGD, DGS ,CGB

交叠电容: C1、C3 、C5 珊-源/漏 C1 C3 LD Weff Cox CGXO Weff

25

§3-4: MOS管的小信号模型

1. gm,gmbs , gds 在饱和区:

gm (2K'W / L) ID (1 VDS ) (2K'W / L) ID

gmbs

iD vBS

iD vSB

( iD VT

)( VT ) vSB

iD iD VT vGS

gmbs gm 2(2 F

VSB )1/ 2

(a) (b)

多个器件的表示, 从匹配角度看更好。

37

§3-7: MOS电路的SPICE模拟

三、MOS模型描述

.MODEL < 模型名> <模型类型> <模型参数>

例如: .MODEL NCH NMOS LEVEL=1 VT0=1 KP=50U GAMMA=0.5 +LAMBDA=0.01

四、分析实例

vGS

VT

n

kT q

(简化模型,适合手工计算)

第3章第7节

35

3.7 MOS电路的SPICE模拟

36

§3-7: MOS电路的SPICE模拟

一、SPICE 模拟文件的一般格式

● 标题 ● 电路描述 (器件描述和模型描述) ● 分析类型描述 ● 输出描述

§3-3: 其他MOS管大信号模型的参数

17

二、MOS电容

2. 耗尽结电容:CBD, CBS

P65 上式S→D 则 CBS→ CBD

18

§3-3: 其他MOS管大信号模型的参数

3.电荷存储电容: CGD, DGS ,CGB

交叠电容: C1、C3 、C5 珊-源/漏 C1 C3 LD Weff Cox CGXO Weff

25

§3-4: MOS管的小信号模型

1. gm,gmbs , gds 在饱和区:

gm (2K'W / L) ID (1 VDS ) (2K'W / L) ID

gmbs

iD vBS

iD vSB

( iD VT

)( VT ) vSB

iD iD VT vGS

gmbs gm 2(2 F

VSB )1/ 2

(a) (b)

多个器件的表示, 从匹配角度看更好。

37

§3-7: MOS电路的SPICE模拟

三、MOS模型描述

.MODEL < 模型名> <模型类型> <模型参数>

例如: .MODEL NCH NMOS LEVEL=1 VT0=1 KP=50U GAMMA=0.5 +LAMBDA=0.01

四、分析实例

vGS

VT

n

kT q

(简化模型,适合手工计算)

第3章第7节

35

3.7 MOS电路的SPICE模拟

36

§3-7: MOS电路的SPICE模拟

一、SPICE 模拟文件的一般格式

● 标题 ● 电路描述 (器件描述和模型描述) ● 分析类型描述 ● 输出描述

模拟集成电路设计流程.ppt

ac(交流分析)是 分析电路性能随着 运行频率变化而变

化的仿真。

既可以对频率进行 扫描也可以在某个 频率下进行对其它

变量的扫描。

2020/6/12

共88页

28

Variables菜单

包括Edit等子菜单项。可以 对变量进行添加、删除、 查找、复制等操作。变量 (variables)既可以是电 路中元器件的某一个参量, 也可以是一个表达式。变 量将在参量扫描 (parametric analysis)时 用到。

共88页

4

Cadenc软件简介

Cadence 提供了一个大型的EDA 软件包,它包括: ASIC 设计

全定制IC设计工具Virtuoso Schematic Composer 电路仿真工具Analog Design Environment FPGA 设计 PCB设计

2020/6/12

共88页

dc(直流分析)

dc(直流分析)可以在 直流条件下对

temperature,Design Variable,Component

Parameter,Model Parameter进行扫描仿真

举例:对温度的扫描(测 量温度系数)

电路随电源电压变化的 变化曲线等

2020/6/12

共88页

27

ac(交流分析)

Outputs/To be plotted/selected on schematic

schematic子菜单用来在电路原理图上选取要显示的 波形(点击连线选取节点电压,点击元件端点选取

节点电流),这个菜单比较常用

2020/6/12

共88页

31

其它有关的菜单项(3)

Outputs/Setup

化的仿真。

既可以对频率进行 扫描也可以在某个 频率下进行对其它

变量的扫描。

2020/6/12

共88页

28

Variables菜单

包括Edit等子菜单项。可以 对变量进行添加、删除、 查找、复制等操作。变量 (variables)既可以是电 路中元器件的某一个参量, 也可以是一个表达式。变 量将在参量扫描 (parametric analysis)时 用到。

共88页

4

Cadenc软件简介

Cadence 提供了一个大型的EDA 软件包,它包括: ASIC 设计

全定制IC设计工具Virtuoso Schematic Composer 电路仿真工具Analog Design Environment FPGA 设计 PCB设计

2020/6/12

共88页

dc(直流分析)

dc(直流分析)可以在 直流条件下对

temperature,Design Variable,Component

Parameter,Model Parameter进行扫描仿真

举例:对温度的扫描(测 量温度系数)

电路随电源电压变化的 变化曲线等

2020/6/12

共88页

27

ac(交流分析)

Outputs/To be plotted/selected on schematic

schematic子菜单用来在电路原理图上选取要显示的 波形(点击连线选取节点电压,点击元件端点选取

节点电流),这个菜单比较常用

2020/6/12

共88页

31

其它有关的菜单项(3)

Outputs/Setup

CMOS模拟集成电路—振荡器(课堂PPT)

A1反馈固定VDS,M3和M4跟随M5的

30.05.2020导通电阻。

13

• 4.1 环形振荡器调节(续)

▪正反馈引起的延时变化 半边电路等效: I1↑→|-1/gm3,4|↓ →( -1/gm3,4)||R1,2=R/(1-gm3,4R)↑ →fosc ↓

缺点:R1R2上的电流在控制过程中会发 生变化,输出摆幅在调节范围内变化

谐振时, Avgm1RP

接成反馈形式,谐振时,总相移等于180, 所以不能振荡

30.05.2020

10

• 3.3 交叉耦合振荡器

起振条件: 谐振时,总相移为0

gm 1RP1gm 2RP21

30.05.2020

11

• 定义

4、压控振荡器

▪中心频率 ▪调节范围ω2- ω1

▪调节线性度

▪输出摆幅

▪功耗 ▪电源与共模抑制

15

• 4.1 环形振荡器调节(续)

▪正反馈引起的延时变化(续)

为了避免消耗了额外的电压余度, 采用电流折叠结构

30.05.2020

16

• 4.1 环形振荡器调节(续)

▪插值法改变延迟

快路径导通,慢路径关断,产生最大振荡频率; 快路径关断,慢路径导通,产生最小振荡频率; Vcont落在两极中间时,产生中间振荡频率。

LC

实际(有损)并联LC回路含电阻成份

品质因数

Q L1 RS

阻抗

30.05.2020

8

• 3.1 LC振荡回路(续)

串联→并联 在较窄的频率范围内ZS=ZP

得到

LP

L11L1R2S22

L1

RP

L122

RS

Q2RS

谐振频率

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

主要原因:主要由温度变化引起,也称温漂。 温漂指标:温度每升高1度时,输出漂移电压按电压增益折算

到输入端的等效输入漂移电压值。

15

6.2.0 概述

假设 AV1 = 100, AV2 = 100, AV3 = 1 。 若第一级漂了100 uV, 则输出漂移 1 V。

漂移 10 mV+100 uV

漂移 1 V+ 10 mV

中规模集成电路(MSI)<103 大规模集成电路(LSI)<105、

Intel 奔腾4

超大规模集成电路(VLSI)>105、 (如:CPU 310万---330万)

4

6 集成电路运算放大器

6.0 概述 集成电路的工艺特点: (1)元器件具有良好的一致性和同向偏差,因而特别有 利于实现需要对称结构的电路。

2

概述

一、集成电路(integrated circuit): 在半导体制造工艺基础上,把整个电

路中的器件(电阻、电容、三极管等)制 造在一块Si 基片上,并引出相应的引线, 构成特定功能的电子电路。 如:运放、各种芯片等。

3

二、按功能分类:

模拟集成电路

数字集成电路

三、集成度:

小规模集成电路(SSI)<102

+ vo1

vo2 -

-

共模电压增益 差分式放大电路输入输出结构示意图

17

6.2.0 概述

总输出电压

vo = vod voc AVD vid AVC vic

+

+

-vid

vi1 +

-

vi2 -

差放

+

-vod

+

+ vo1

vo2 -

-

差分式放大电路输入输出结构示意图

KCMR =

AVD AVC

共模抑制比 反映抑制零漂能力的指标

(2)集成电路的芯片面积小,集成度高,所以功耗很小, 在毫瓦以下。 (3)不易制造大电阻。需要大电阻时,往往使用有源负载

(4)只能制作几十pF以下的小电容。因此,集成放大器 都采用直接耦合方式。如需大电容,只有外接。

(5)不能制造电感,如需电感,也只能外接。

5

§6.1集成电路运放中的电流源

要求:提供恒定电流IO,且有大的交流电阻 其两端电压变化时, IO保持恒定。Βιβλιοθήκη 若第二级也漂了100 uV,

则输出漂移 10 mV。 漂了 100 uV

3. 减小零漂的措施

用非线性元件进行温度补偿 调制解调方式。如“斩波稳零放大器” 采用差分式放大电路

漂移 1 V+ 10 mV

16

6.2.0 概述

4. 差分式放大电路中的一般概念

vid = vi1 vi2

差模信号 两个输入信号的差值

6 集成电路运算放大器

基本要求

1. 掌握差放的结构、原理及Q点、动态指标的计算。 2.了解差动放大器抑制零点漂移的原理。 3.了解镜像电流源、微电流源的组成及工作原理。 4.了解集成运算放大器的组成及工作原理。 5.了解集成运算放大器的主要参数。

1

6 集成电路运算放大器 6.0 概述 6.1 电流源 6.2 差分式放大电路 6.3 集成电路运算放大器 6.4 集成电路运算放大器的主要参数

VBE1 VBE2 Re2

VBE Re2

优由点于:12VBE内受很阻电小ro源,一波般动在影几响百千小欧;以上

所以IC234也. 很具IC小有2 u温A级度;补偿特性。

9

6.1.1.3多路电流源:

T1、T2、T3的基极并联。

电路用一个基准电流IREF获得了多个电流输出。

I C1

I E1

C2

19

6.2.1 基本差分式放大电路

1. 电路组成

根据输入、输出方式不同,

可分为四种工作方式:

双端输入、双端输出;

IREF Re Re1

I C2

I E2

IREF Re Re2

I C3

I E3

I REF Re Re3

10

6.1.1.4 电流源作用

镜像电流源

提供直流偏置 作为有源负载 例电流源作为有源负载:

例P315 6.6.1

放大管

11

举例:P282 集成运放

微电流源直流偏置 镜像电流源有源负载 电流源直流偏置 12

+

ro Io

-

+

ro v

_

6

6.1.1.1 镜像电流源(P258)

一、电路组成

三极管T1、T2对称

二、恒流特性

当较大(>>2)时:

VBE2 = VBE1 IE2 = IE1

IC2

=

I

C1

IREF

2

IREF

= VCC VBE VCC

R

R

结论:

无论Rc值如何, IC2电流值保持不变(前提:电源要稳定)

抑制零点漂移原理

主要指标计算

几种方式指标比较

6.2.2 FET差分式放大电路

6.2.3 差分式放大电路的传输特性

14

6.2.0 概述

1. 直接耦合放大电路

可以放大直流信号

# 为什么一般的集成运 算放大器都要采用直接 耦合方式?

2.直接耦合放大电路 的零点漂移

零漂:输入短路时,输出仍有缓慢 变化的电压产生。

7

当较小时,可用 带缓冲级的镜像电流源

增加T0,使IC更加接近IREF 三、镜像电流源特点 1 内阻ro一般在几百千欧以上

2. 电流受电源波动影响大; 3. 电流最低至mA级。 4. 具有温度补偿特性。

8

6.1.1.2微电流源(P259)

一、电路特点 (Re2 K级)

二、工作原理

IC2 IE2

6.1.2 FET电流源(P260)

(与BJT电流源比较,自学,了解)

一、 MOSFET镜像电流源: 二、 MOSFET多路电流源: 三、 JFET电流源:

13

6.2 差分式放大电路

6.2.0 概述

直接耦合放大电路

零点漂移

差分式放大电路中的一般概念

6.2.1 基本差分式放大电路

电路组成及工作原理

18

6.2.1 基本差分式放大电路

1. 电路组成

两个BJT特性一致,参数相等。

1=2=

rbe1= rbe2= rbe

VBE1=VBE2= VBE

C1

差放一般有两个输入端:

双端输入—两输入端同时加信号

单端输入—一输入端对地加信号 差放可以有两个输出端:

双端输出—从C1 和C2输出。 单端输出—从C1或C2 对地输出。

1 vic = 2 (vi1 vi2 )

共模信号

两个输入信号的算术平均值

根据以上两式可以得到

vi1 = vic

vi2 = vic

AVD AVC

= =

v od vviodc v ic

vid

差模信号输出

v2id 2

+ vi1

共+-v模+id 信号输差出放

差模电压增益 -

vi2 -

+

-vod +

到输入端的等效输入漂移电压值。

15

6.2.0 概述

假设 AV1 = 100, AV2 = 100, AV3 = 1 。 若第一级漂了100 uV, 则输出漂移 1 V。

漂移 10 mV+100 uV

漂移 1 V+ 10 mV

中规模集成电路(MSI)<103 大规模集成电路(LSI)<105、

Intel 奔腾4

超大规模集成电路(VLSI)>105、 (如:CPU 310万---330万)

4

6 集成电路运算放大器

6.0 概述 集成电路的工艺特点: (1)元器件具有良好的一致性和同向偏差,因而特别有 利于实现需要对称结构的电路。

2

概述

一、集成电路(integrated circuit): 在半导体制造工艺基础上,把整个电

路中的器件(电阻、电容、三极管等)制 造在一块Si 基片上,并引出相应的引线, 构成特定功能的电子电路。 如:运放、各种芯片等。

3

二、按功能分类:

模拟集成电路

数字集成电路

三、集成度:

小规模集成电路(SSI)<102

+ vo1

vo2 -

-

共模电压增益 差分式放大电路输入输出结构示意图

17

6.2.0 概述

总输出电压

vo = vod voc AVD vid AVC vic

+

+

-vid

vi1 +

-

vi2 -

差放

+

-vod

+

+ vo1

vo2 -

-

差分式放大电路输入输出结构示意图

KCMR =

AVD AVC

共模抑制比 反映抑制零漂能力的指标

(2)集成电路的芯片面积小,集成度高,所以功耗很小, 在毫瓦以下。 (3)不易制造大电阻。需要大电阻时,往往使用有源负载

(4)只能制作几十pF以下的小电容。因此,集成放大器 都采用直接耦合方式。如需大电容,只有外接。

(5)不能制造电感,如需电感,也只能外接。

5

§6.1集成电路运放中的电流源

要求:提供恒定电流IO,且有大的交流电阻 其两端电压变化时, IO保持恒定。Βιβλιοθήκη 若第二级也漂了100 uV,

则输出漂移 10 mV。 漂了 100 uV

3. 减小零漂的措施

用非线性元件进行温度补偿 调制解调方式。如“斩波稳零放大器” 采用差分式放大电路

漂移 1 V+ 10 mV

16

6.2.0 概述

4. 差分式放大电路中的一般概念

vid = vi1 vi2

差模信号 两个输入信号的差值

6 集成电路运算放大器

基本要求

1. 掌握差放的结构、原理及Q点、动态指标的计算。 2.了解差动放大器抑制零点漂移的原理。 3.了解镜像电流源、微电流源的组成及工作原理。 4.了解集成运算放大器的组成及工作原理。 5.了解集成运算放大器的主要参数。

1

6 集成电路运算放大器 6.0 概述 6.1 电流源 6.2 差分式放大电路 6.3 集成电路运算放大器 6.4 集成电路运算放大器的主要参数

VBE1 VBE2 Re2

VBE Re2

优由点于:12VBE内受很阻电小ro源,一波般动在影几响百千小欧;以上

所以IC234也. 很具IC小有2 u温A级度;补偿特性。

9

6.1.1.3多路电流源:

T1、T2、T3的基极并联。

电路用一个基准电流IREF获得了多个电流输出。

I C1

I E1

C2

19

6.2.1 基本差分式放大电路

1. 电路组成

根据输入、输出方式不同,

可分为四种工作方式:

双端输入、双端输出;

IREF Re Re1

I C2

I E2

IREF Re Re2

I C3

I E3

I REF Re Re3

10

6.1.1.4 电流源作用

镜像电流源

提供直流偏置 作为有源负载 例电流源作为有源负载:

例P315 6.6.1

放大管

11

举例:P282 集成运放

微电流源直流偏置 镜像电流源有源负载 电流源直流偏置 12

+

ro Io

-

+

ro v

_

6

6.1.1.1 镜像电流源(P258)

一、电路组成

三极管T1、T2对称

二、恒流特性

当较大(>>2)时:

VBE2 = VBE1 IE2 = IE1

IC2

=

I

C1

IREF

2

IREF

= VCC VBE VCC

R

R

结论:

无论Rc值如何, IC2电流值保持不变(前提:电源要稳定)

抑制零点漂移原理

主要指标计算

几种方式指标比较

6.2.2 FET差分式放大电路

6.2.3 差分式放大电路的传输特性

14

6.2.0 概述

1. 直接耦合放大电路

可以放大直流信号

# 为什么一般的集成运 算放大器都要采用直接 耦合方式?

2.直接耦合放大电路 的零点漂移

零漂:输入短路时,输出仍有缓慢 变化的电压产生。

7

当较小时,可用 带缓冲级的镜像电流源

增加T0,使IC更加接近IREF 三、镜像电流源特点 1 内阻ro一般在几百千欧以上

2. 电流受电源波动影响大; 3. 电流最低至mA级。 4. 具有温度补偿特性。

8

6.1.1.2微电流源(P259)

一、电路特点 (Re2 K级)

二、工作原理

IC2 IE2

6.1.2 FET电流源(P260)

(与BJT电流源比较,自学,了解)

一、 MOSFET镜像电流源: 二、 MOSFET多路电流源: 三、 JFET电流源:

13

6.2 差分式放大电路

6.2.0 概述

直接耦合放大电路

零点漂移

差分式放大电路中的一般概念

6.2.1 基本差分式放大电路

电路组成及工作原理

18

6.2.1 基本差分式放大电路

1. 电路组成

两个BJT特性一致,参数相等。

1=2=

rbe1= rbe2= rbe

VBE1=VBE2= VBE

C1

差放一般有两个输入端:

双端输入—两输入端同时加信号

单端输入—一输入端对地加信号 差放可以有两个输出端:

双端输出—从C1 和C2输出。 单端输出—从C1或C2 对地输出。

1 vic = 2 (vi1 vi2 )

共模信号

两个输入信号的算术平均值

根据以上两式可以得到

vi1 = vic

vi2 = vic

AVD AVC

= =

v od vviodc v ic

vid

差模信号输出

v2id 2

+ vi1

共+-v模+id 信号输差出放

差模电压增益 -

vi2 -

+

-vod +