基于VHDL的DDS设计

DDS信号源的设计与实现(电子科大)

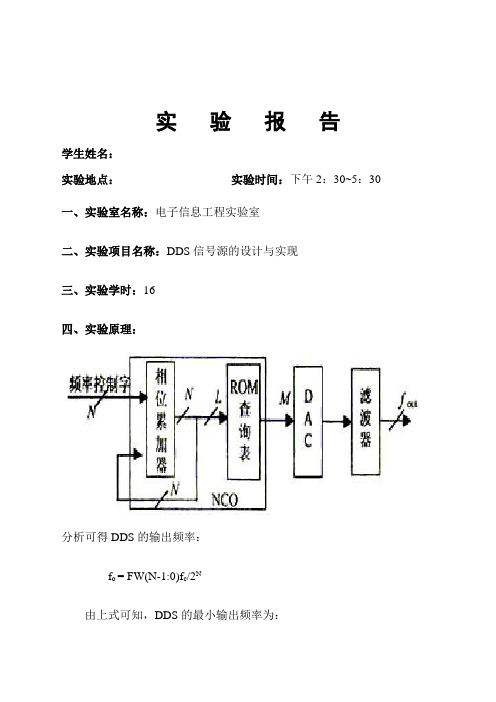

实验报告学生姓名:实验地点:实验时间:下午2:30~5:30一、实验室名称:电子信息工程实验室二、实验项目名称:DDS信号源的设计与实现三、实验学时:16四、实验原理:分析可得DDS的输出频率:f o = FW(N-1:0)f c/2N由上式可知,DDS的最小输出频率为:f omin = f c/2NDDS的频率分辨率为:f o = f c/2NDDS频率输入字的计算:FW(N-1:0) = 2N f0/f c五、实验目的:通过本实验项目,可使学生利用VHDL硬件描述语言对比较复杂的、综合性的实际电路系统进行设计、描述,利用EDA开发工具完成系统的综合、仿真,并用硬件平台完成系统的硬件实现, 着重培养学生的实际动手设计能力。

六、实验内容:1.EDA技术及VHDL2.EDA开发软件及实验箱的使用3.DDS信号源的设计与实现七、实验器材(设备、元器件):电脑,实验箱(带有EPF10K10 LC84-4芯片)八、实验步骤:① 创建新目录“D:\XX”,运行MAXPLUS II软件;② 打开Altera MAX+plus软件后,首先选择“File”中的“New”, 建立一个新的VHDL文件;③ 编辑VHDL源程序选择“Text Editor file”,再输入程序: library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity dds_nes isport (clk,swithc : in std_logic;freqin : in std_logic_vector(11 downto 0); --频率控制字宽:12位phasein : in std_logic_vector(5 downto 0); --相位字宽ampin : in std_logic_vector(7 downto 0); --加法器宽度ddsout : out integer range 0 to 255 );end dds_nes;architecture rtl of dds_nes issignal acc:std_logic_vector(11 downto 0);signal phaseadd: std_logic_vector(5 downto 0);signal romaddr: std_logic_vector(5 downto 0);signal freqw:std_logic_vector(11 downto 0);signal phasew:std_logic_vector(5 downto 0);signal romaddr_i:integer range 0 to 63;signal amp_t:std_logic_vector(15 downto 0);signal ddsout_t:integer range 0 to 255;beginprocess(clk)beginif clk'event and clk='1' thenif swithc='1' thenfreqw<=freqin;elsefreqw<=freqin+freqin;end if;phasew<=phasein;acc<=acc+freqw;end if;end process;phaseadd<=acc(11 downto 6)+phasew;romaddr<=phaseadd(5 downto 0);romaddr_i<=conv_integer(romaddr); --查找表字宽取整amp_t<=ampin*conv_std_logic_vector(ddsout_t,8);--8*8ddsout_t转为8位ddsout<=conv_integer(amp_t(15 downto 8)); --取高8位后转整process(romaddr_i)begincase romaddr_i iswhen 00 => ddsout_t<=255;when 01 => ddsout_t<=254;when 02 => ddsout_t<=252;when 03 => ddsout_t<=249;when 04 => ddsout_t<=245;when 05 => ddsout_t<=239;when 06 => ddsout_t<=233;when 07 => ddsout_t<=225;when 08 => ddsout_t<=217;when 09 => ddsout_t<=207;when 10 => ddsout_t<=197;when 11 => ddsout_t<=186;when 12 => ddsout_t<=174;when 13 => ddsout_t<=162;when 14 => ddsout_t<=150;when 15 => ddsout_t<=137;when 16 => ddsout_t<=124;when 17 => ddsout_t<=112;when 18 => ddsout_t<=99;when 19 => ddsout_t<=87;when 20 => ddsout_t<=75;when 22 => ddsout_t<=53; when 23 => ddsout_t<=43; when 24 => ddsout_t<=34; when 25 => ddsout_t<=26; when 26 => ddsout_t<=19; when 27 => ddsout_t<=13; when 28 => ddsout_t<=8; when 29 => ddsout_t<=4; when 30 => ddsout_t<=1; when 31 => ddsout_t<=0; when 32 => ddsout_t<=0; when 33 => ddsout_t<=1; when 34 => ddsout_t<=4; when 35 => ddsout_t<=8; when 36 => ddsout_t<=13; when 37 => ddsout_t<=19; when 38 => ddsout_t<=26; when 39 => ddsout_t<=34; when 40 => ddsout_t<=43; when 41 => ddsout_t<=53; when 42 => ddsout_t<=64; when 43 => ddsout_t<=75;when 45 => ddsout_t<=99;when 46 => ddsout_t<=112;when 47 => ddsout_t<=124;when 48 => ddsout_t<=137;when 49 => ddsout_t<=150;when 50 => ddsout_t<=162;when 51 => ddsout_t<=174;when 52 => ddsout_t<=186;when 53 => ddsout_t<=197;when 54 => ddsout_t<=207;when 55 => ddsout_t<=217;when 56 => ddsout_t<=225;when 57 => ddsout_t<=233;when 58 => ddsout_t<=239;when 59 => ddsout_t<=245;when 60 => ddsout_t<=249;when 61 => ddsout_t<=252;when 62 => ddsout_t<=254;when 63 => ddsout_t<=255;when others=>null;end case;end process;end rtl;④ 将源程序存为VHDL文件格式,并将VHDL文件设置为当前工程;⑤ 编译VHDL源文件,点击“MAX+plus II→Compiler→Start”进行编译,如果警告和错误不为0,要改正错误直至全部正确;⑥ 对照芯片,用导线依次对应连接好实验箱芯片的每一个接口;⑦ 确定无误后,打开试验箱与示波器电源,并运行程序,下载程序。

基于FPGA的DDS正弦波信号源设计(DDS的VHDL语言实现及其高纯谱研究

内容摘要:频率合成技术在现代电子技术中具有重要的地位。

在通信、雷达和导航等设备中,它可以作为干扰信号发生器;在测试设备中,可作为标准信号源,因此频率合成器被人们称为许多电子系统的“心脏”。

直接数字频率合成(DDS——Digital Direct Frequency Synthesis)技术是一种全新的频率合成方法,是频率合成技术的一次革命。

本文主要分析了DDS的基本原理及其输出频谱特点,并采用VHDL语言在FPGA上实现。

对于DDS的输出频谱,一个较大的缺点是:输出杂散较大。

针对这一缺点本文使用了两个方法加以解决。

首先是压缩ROM查找表,在相同ROM容量的情况下,压缩后相当于把512点查找表扩展为2048点,过采样的引入提高了DDS输出谱的纯度。

其次,采用了相位随机抖动技术,引入了M序列作为DDS采样输出的相位随机抖动,这个方法把原来的均匀查表抽样变成为伪随机非均匀抽样,使得DDS输出谱的杂散分量白化,同样使输出频谱纯度得到提高。

本文最后用频谱分析仪做了相关实验测试,在实验上验证了设计思想。

关键词:DDS FPGA VHDL M序列频谱The realization of DDS with VHDL and its high pure spectrumresearchAbstract;The frequency synthesis technology has the important status in the modernelectronic technology. In equipment such as correspondence, radar and navigation, it may work as the unwanted signal generator; In the test facility, may work as the standard signal source, therefore the frequency synthesizer is called by the people as "the heart" of many electronic systems .DDS——Digital Direct Frequency Synthesis technology is one brand-new frequency synthetic method, is a frequency synthesis technology revolution. This paper analyzes the basic principle of DDS and its output frequency spectrum characteristic, and realizes it with VHDL language on FPGA. In regard to the output frequency spectrum of DDS, a shortcoming is: The output spurious is bigger. In view of this shortcoming this article uses two methods to solve. First compress the ROM search table, in the same capacity of ROM, it is equal to expand 512 searches tables to 2,048 after the compression, the introduction of over sampling enhance the spectrum purity of DDS output. Then utilize the phase random dither technology, use the M sequence as the phase random dither of the DDS sampling output .this method causes evenly look up table sampling turn to for pseudo-random non- even sampling, it make the output spurious component of DDS change to white noise, similarly enhance purity of the output frequency spectrum to This article finally used the spectrum analyzer to do the correlation experiment test, has confirmed the design thought at the experiment.Key words:Digital Direct Frequency Synthesis FPGA VHDL M sequenceSpectrum目录一、频率合成技术概述及DDS性能特点 (3)(一)频率合成技术概述 (3)(二)DDS特点 (4)二、DDS基本原理 (5)(一)波形存储器基本原理 (5)(二)DDS基本原理 (5)(三)DDS设计中的参数选择 (7)(四)小结 (7)三、DDS的VHDL语言实现 (8)(一)EDA技术与VHDL语言 (8)(二)DDS的FPGA实现方法 (9)(三)开发平台 (9)(四)基本DDS的VHDL实现与仿真 (9)四、提高输出频谱纯度的方法与实验验证 (13)(一)DDS的频谱纯度提高方法简述 (13)(二)相位随机抖动原理与VHDL实现 (14)(三)频谱纯度提高的实验验证 (19)五、程序下载及硬件调试 (19)(一)FPGA的配置和下载 (19)(二)调试与程序固化 (20)六、结束语 (20)七、致谢 (21)参考文献 (21)附录 (22)(一)各组成模块的VHDL程序 (22)基于FPGA的DDS正弦波信号源设计一、频率合成技术概述及DDS性能特点(一)频率合成技术概述频率合成是指由一个或多个频率稳定度和精确度很高的参考信号源通过频率域的线形运算,产生具有同样稳定度和精确度的大量离散频率的过程。

基于VHDL的DDS实现及仿真

基于VHDL 的DDS 实现与仿真宜宾学院物理与电子工程学院2011级2班段艳婷110302034)摘要:本文论述了直接数字频率合成技术(DDS的信号发生器的设计与实现。

本设计以DDS芯片Cyclone n:EP2C5T144C为频率合成器,以AVR单片机ATmegal为进程控制和任务调度核心,用AD603 实现增益控制(AGC和功率放大,串行数模转换器(D/A)MAX531 实现方波占空比调节,并用LCD12864液晶显示及键盘构成幅度、频率、方波占空比均可调的函数信号发生器。

本文分析了DDS的设计原理,基于VHDI语言进行系统建模,对DDS进行参数设计,实现了可重构的IP 核,能够根据需要方便的修改参数以实现器件的通用性。

同时利用Quartus n编译平台完成一个具体DDS芯片的设计,详细阐述了基于VHDL编程的DDS设计方法步骤。

针对DDS频率转换时间短,分辨率高等优点,提出了基于FPGA芯片设计DDS系统的方案。

该方案利用Altera公司的Quartus n开发软件,完成DDS核心部分即相位累加器和RAM 查找表的设计, 可得到相位连续、频率可变的信号,并通过单片机配置FPGA勺E A2 PROM完成对DDS硬件的下载,最后完成每个模块与系统的时序仿真。

经过电路设计和模块仿真, 验证了设计的正确性。

由于FPGA勺可编程性,使得修改和优化DDS勺功能非常快捷。

直接数字频率合成信号发生器关键字:DDS,Cyclone n,Quartus n,FPGA中图分类号:TN正文:目录第一章、绪论1.1 DDS 引言1.2 直接数字合成器的概念及其发展1.3 DDS 技术在国内研究状况及其发展趋势1.4 频率合成器的种类与技术发展趋势1.5 DDS 优势1.6 课题主要研究内容和技术要求第二章、超大规模集成电路设计介绍2.1 引言2.1.1 EDA 技术的含义及其特点2.1.2 EDA 技术的主要内容2.2 大规模可编程逻辑器件2.2.1 FPGA 的介绍2.2.2 CPLD 的介绍2.2.3 FPGA 与CPLD 的区别2.3 硬件描述语言(HDL )2.3.1 VHDL 简介2.3.2 VHDL 主要特点2.3.3 VHDL 语言的优势2.4 软件开发工具第三章、DDS 工作原理和主要特点3.1 DDS 的基本工作原理3.2 DDS 的主要特点3.3 DDS 建模第四章、用VHDL 来编程实现和仿真4.1 VHDL 编程实现4.1.1 32 位加法器的VHDL 实现程序4.1.2 32 位加法器的生成模块4.1.3 32 位寄存器的VHDL 实现4.1.4 32 位寄存器的生成模块4.1.5 波形数据ROM 的VHDL 实现4.1.6 波形数据ROM 的生成模块4.1.7 整形模块设计4.2 用Quartus H进行DDS仿真421 Quartus H软件简介4.2.2用Quartus H的仿真步骤和图像4.2.3 注意事项第五章、设计相关数据处理与图像分析5.1 电路原理图5.2 仿真波形图5.3 数据验证5.4 波形毛刺儿的分析及消除第六章、结束语5.1 总结5.2 参考文献5.3 致谢5.4 附录第一章绪论1.1、DDS 引言频率合成技术是将一个(或多个)基准频率变换成另一个(或多个)合乎质量要求的所需频率的技术。

基于VHDL编程的DDS设计

Ke r s f l — r g r mma l a e a r y FPGA ) d r c i i ls n h sz ( y wo d :i d p o a a e b eg t r a ( ; ie td g t y t e ie DDS) smu a a ; i l—

g n r l u p s . h a i , e in o o c eeDDS c i s c mpe e y Qu ru e e a p r o e Att es metme a d sg fc n rt h p i o ltd b a t s I o i r meh d a d se so I mp l , t o n t p f c e DDS d sg a e n VHDL e iigr u i ei e c ie n e in b sd o dtn o t d s rb di n s

钟 蔚杰 蒋 垒 刘 耀 应 , ,

(. 放 军 电 子 工 程学 院 , 肥 20 3 ;. 放 军 西 安 通 信 学 院 , 安 7 0 0 ) 1解 合 3 0 7 2解 西 11 6

摘要 : 分析了 D S的设计原理 , D 基于 V L语言进行 系统建模 , D S进行参数设计 , 了可重构的 I HD 对 D 实现 P

( . e to i En ie rn n tt t fP 1 Elc r n c g n e ig I s i eo LA , ee 3 0 7 Ch n ; . ’ n XTY fPLA, ’ n 7 0 0 Ch n ) u H f i2 0 3 , i a 2 Xia o Xi a 1 1 6319

文献标 识码 : A

文 章编 号 : N 211(070—12 4 C 3—4320 )2 0— 0 0

基于VHDL的DDS设计

信息与通信工程学院VHDL课程设计2013年5月基于VHDL语言的DDS的设计1.设计内容DDS即直接数字频率合成,是近年来发展起来的一种新的频率合成技术,其主要优点是相对带宽很大,频率转换时间极短(可小于20 ns),频率分辨率很高,全数字化结构便于集成,输出相位连续可调,且频率、相位和幅度均可实现程控。

DDS 能够与计算机技术紧密结合在一起,克服了模拟频率合成和锁相频率合成等传统频率合成技术电路复杂、设备体积较大、成本较高的不足,因此它是一种很有发展前途的频率合成技术。

DDS 技术现已在接收机本振、信号发生器、通信系统、雷达系统等方面得到广泛应用。

数字频率合成器作为一种信号产生装置己经越来越受到人们的重视,它可以根据用户的要求产生相应的波形,具有重复性好、实时性强等优点,己经逐步取代了传统的函数发生器。

我们组本次课程设计的目的是设计基于所学课程VHDL硬件描述语言开发出一个能产生正弦波、方波、三角波、锯齿波等波形的信号源。

2.实现方案2.1 DDS原理直接数字频率合成是采用数字化技术,通过控制相位的变化速度,直接产生各种不同频率、不同波形信号的一种频率合成方法。

DDS 的基本结构如图1 所示,它主要由相位累加器、正弦ROM 表、D/A 转换器和低通滤波器构成。

图1 DDS工作原理图DDS 工作时,在时钟脉冲fc的控制下对频率控制字K 用累加器进行处理以得到相应的相位码,然后由相位码寻址波形存储器进行相位码―幅度编码变换,再经过D/A 数模变换器得到相应的阶梯波,最后经过低通滤波器对阶梯波进行平滑处理即可得到由频率控制字K 决定的频率可调的输出波形。

参考频率源一般是高稳定的晶体振荡器,用于DDS 中各部件的同步工作,因此DDS 输出的合成信号频率稳定度与晶体振荡器是相同的。

在标准频率参考源的控制下,频率控制字K可决定相应的相位增量,相位累加器则以步长K进行线性累加,相位累加器积满时就会产生一次溢出,从而完成一个周期性动作,这个动作周期即是DDS合成信号的一个周期。

基于Verilog+HDL的DDS设计与仿真

基于Verilog HDL的DDS设计与仿真直接数字频率合成技术(Direct Digital Synthesize,DDS)是继直接频率合成技术和锁相式频率合成技术之后的第三代频率合成技术。

它采用全数字技术,并从相位角度出发进行频率合成。

随着微电子技术和数字集成电路的飞速发展,以及电子工程领域的实际需要,DDS 日益显露出优于传统频率合成技术的一些性能,高分辨率、极短的频率切换时间、相位噪声低、便于集成等,逐步成为现代频率合成技术中的佼佼者。

目前,DDS的设计大多是应用HDL(Hardware Description Language)对其进行逻辑描述。

整个设计可以很容易地实现参数改变和设计移植,给设计者带来很大的方便。

Verilo g HDL就是其中一种标准化的硬件描述语言,它不仅可以进行功能描述,还可以对仿真测试矢量进行设计。

Altera公司开发的QuartusⅡ设计软件,提供了Verilog HDL的设计界面以及编译平台,并且该公司还集成了可供程序下载的FPGA器件CYCLONEⅡ系列芯片,这样大大缩短了DDS的设计周期。

1 DDS的设计原理DDS的原理图如图1所示。

DDS实现频率合成主要是通过查表的方式进行的。

正弦查询表是一个只读存储器(ROM),以相位为地址,存有1个或多个按0°~360°相位划分幅值的正弦波幅度信息。

相位累加器对频率控制字进行累加运算,若需要还可以加入相位控制字,得到的结果作为正弦波查询表的地址。

正弦查询表的输出为数字化正弦幅度值,通过D/A转换器转化为近似正弦波的阶梯波,再通过低通滤波器滤除高频成分和噪声最终得到一个纯正度很高的正弦波。

1.1 建模如图2所示正弦波y=sin(2πx),若以f量化的量化频率对其幅度值进行量化,一个周期可以得到M=f量化个幅度值。

将这些幅度值按顺序存入到ROM。

相位累加器在参考时钟的驱动下,每来1个脉冲,输出就会增加1个步长相位增量X,输出数据作为地址送入ROM 中,读出对应的幅度值形成相应的波形。

基于VHDL的DDS设计

基于VHDL的DDS设计DDS(Direct Digital Synthesizer)是一种基于数字信号处理技术的频率合成技术,通过数字化的方式生成高精度的频率信号。

在VHDL中,可以利用DDS技术实现频率可变的信号源,比如用于通信系统中的频率合成、频率测量等。

DDS技术的核心是相位累加器和查找表。

相位累加器用于累加一个固定的频率,生成一个连续不断增大的相位值,然后通过查找表将相位值转换为具体的信号数值,从而生成一个连续变化的频率信号。

下面是一个基于VHDL的DDS设计示例:```vhdllibrary ieee;use ieee.std_logic_1164.all;use ieee.numeric_std.all;entity DDS isgenericN : positive := 10; -- 相位累加器精度M : positive := 10; -- 查找表精度F : positive := 100; -- 需要生成的频率CLOCK_FREQ : positive := 50e6 -- 系统时钟频率portclk : in std_logic; -- 系统时钟reset : in std_logic; -- 同步重置信号sine_out : out std_logic -- 输出正弦波信号end DDS;architecture Behavioral of DDS issignal phase_accumulator : unsigned(N - 1 downto 0); -- 相位累加器signal sine_lut : unsigned(M - 1 downto 0); -- 正弦查找表beginprocess (clk) isvariable phase_inc : unsigned(N - 1 downto 0);variable phase_acc : unsigned(N - 1 downto 0);beginif rising_edge(clk) thenif reset = '1' thenphase_accumulator <= (others => '0'); -- 复位相位累加器elsephase_inc := conv_unsigned(F / CLOCK_FREQ * 2 ** N, N); -- 计算相位增量phase_acc := phase_accumulator + phase_inc; -- 累加相位值phase_accumulator <= phase_acc;end if;sine_lut <= conv_unsigned(2 ** (M - 1) * sin(2 * pi *to_real(phase_acc) / 2 ** N - pi / 2) + 0.5, M); -- 更新查找表中的数值sine_out <= sine_lut(M - 1); -- 输出正弦波信号end if;end process;end Behavioral;```在上面的代码中,通过定义N、M、F和CLOCK_FREQ等参数,实现了一个可配置的DDS模块。

实验DDS信号发生器的VHDL建模与设计

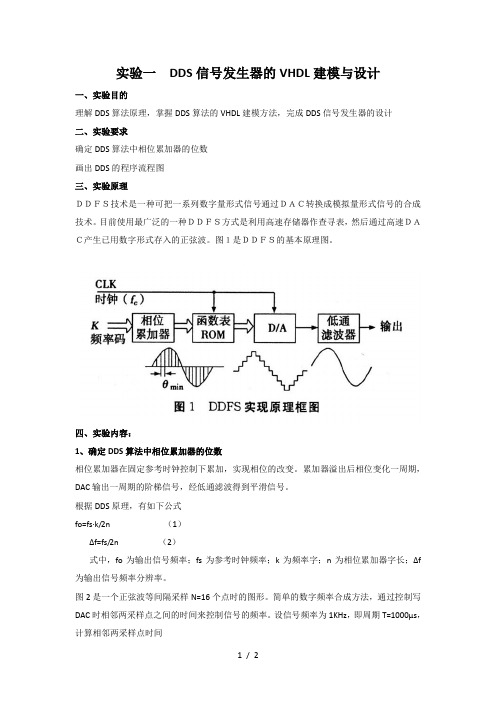

实验一DDS信号发生器的VHDL建模与设计一、实验目的理解DDS算法原理,掌握DDS算法的VHDL建模方法,完成DDS信号发生器的设计二、实验要求确定DDS算法中相位累加器的位数画出DDS的程序流程图三、实验原理DDFS技术是一种可把一系列数字量形式信号通过DAC转换成模拟量形式信号的合成技术。

目前使用最广泛的一种DDFS方式是利用高速存储器作查寻表,然后通过高速DAC产生已用数字形式存入的正弦波。

图1是DDFS的基本原理图。

四、实验内容:1、确定DDS算法中相位累加器的位数相位累加器在固定参考时钟控制下累加,实现相位的改变。

累加器溢出后相位变化一周期,DAC输出一周期的阶梯信号,经低通滤波得到平滑信号。

根据DDS原理,有如下公式fo=fs·k/2n (1)Δf=fs/2n(2)式中,fo为输出信号频率;fs为参考时钟频率;k为频率字;n为相位累加器字长;Δf 为输出信号频率分辨率。

图2是一个正弦波等间隔采样N=16个点时的图形。

简单的数字频率合成方法,通过控制写DAC时相邻两采样点之间的时间来控制信号的频率。

设信号频率为1KHz,即周期T=1000μs,计算相邻两采样点时间t=T/N=62.5μs(3)若时钟最小单位为μs,则t只能取62或63,因此每段时间会有误差Δt=0.5μs,整个周期的误差为0.5/63=0.8%。

可见,信号频率分辨率受时钟分辨率的影响较大。

若采用DDS技术,其参考时钟周期TS固定,设为56μs,相位累加器字长n取8位。

频率字K可计算如下:式(3)已得出每段数据占有的时间为62.5μs,则每经过一个参考时钟周期相位应该走过的段数为:TS/t=0.896。

由采样点数N=16=24,取频率字K的高4位表示整数部分(即为查表偏移量),低4位表示小数部分,得到K=0x0e。

这种计算方法同公式(1)等价。

可见,与简单数字频率合成技术相比,DDS技术在相位表达上具有“小数部分”,并将“小数部分”保留,累计到下一个信号周期(如图2,相位累加器以零相位开始累加,溢出后初值不再为零),若不考虑字长对小数精度的限制,任意时刻相位累加器的值均精确表达了当前时刻信号的相位。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

信息与通信工程学院VHDL课程设计2013年5月基于VHDL语言的DDS的设计1.设计内容DDS即直接数字频率合成,是近年来发展起来的一种新的频率合成技术,其主要优点是相对带宽很大,频率转换时间极短(可小于20 ns),频率分辨率很高,全数字化结构便于集成,输出相位连续可调,且频率、相位和幅度均可实现程控。

DDS 能够与计算机技术紧密结合在一起,克服了模拟频率合成和锁相频率合成等传统频率合成技术电路复杂、设备体积较大、成本较高的不足,因此它是一种很有发展前途的频率合成技术。

DDS 技术现已在接收机本振、信号发生器、通信系统、雷达系统等方面得到广泛应用。

数字频率合成器作为一种信号产生装置己经越来越受到人们的重视,它可以根据用户的要求产生相应的波形,具有重复性好、实时性强等优点,己经逐步取代了传统的函数发生器。

我们组本次课程设计的目的是设计基于所学课程VHDL硬件描述语言开发出一个能产生正弦波、方波、三角波、锯齿波等波形的信号源。

2.实现方案2.1 DDS原理直接数字频率合成是采用数字化技术,通过控制相位的变化速度,直接产生各种不同频率、不同波形信号的一种频率合成方法。

DDS 的基本结构如图1 所示,它主要由相位累加器、正弦ROM 表、D/A 转换器和低通滤波器构成。

图1 DDS工作原理图DDS 工作时,在时钟脉冲fc的控制下对频率控制字K 用累加器进行处理以得到相应的相位码,然后由相位码寻址波形存储器进行相位码―幅度编码变换,再经过D/A 数模变换器得到相应的阶梯波,最后经过低通滤波器对阶梯波进行平滑处理即可得到由频率控制字K 决定的频率可调的输出波形。

参考频率源一般是高稳定的晶体振荡器,用于DDS 中各部件的同步工作,因此DDS 输出的合成信号频率稳定度与晶体振荡器是相同的。

在标准频率参考源的控制下,频率控制字K可决定相应的相位增量,相位累加器则以步长K进行线性累加,相位累加器积满时就会产生一次溢出,从而完成一个周期性动作,这个动作周期即是DDS合成信号的一个周期。

通常N 位相位累加器的最小值为0,最大值为2N −1,故最后输出信号的频率为f0= Kfc /2N,频率分辨率的大小为Δ f= fc/2N。

实际运用中,根据实际需要所计算出的K 很难为整数,因此不可避免地会存在频率误差。

如将计算出来的K的小数部分舍去,那么最终输出信号的频率误差不超过频率分辨率Δf ;如果将K 的小数部分四舍五入,则频率误差不会超过0.5Δf 。

DDS 技术可以理解为数字信号处理中信号综合的硬件实现问题,即给定信号幅度、频率、相位参数,产生所需要的信号波形,也可以认为是给定输入时钟和频率控制字K,输出一一对应的正弦信号。

由于DDS采用了不同于传统频率合成方法的全数字结构,所以它具有直接模拟频率合成和间接频率合成方法所不具备的一些优点。

2.2 基于FPGA 的DDS 模块设计DDS 遵循奈奎斯特(Nyquist)取样定律,即最高的输出频率是时钟频率的一半(fm ax0=0.5 fc)。

在实际应用中DDS 的最高输出频率还由允许输出的杂散水平决定,一般情况下fm ax0≤0.4 fc。

在使用FPGA 设计DDS 时,要在满足系统要求和保持DDS 原有优点的基础上,尽量减少硬件复杂性,降低芯片面积和功耗,提高芯片速度。

综合以上考虑,所设计DDS 电路的电路结构如图2 所示。

图2 用FPGA实现的DDS电路功能框图2.3 采用方案上述框图中的实现方案需要ROM模块,用来存储波形的取样值.mif.文件。

相位累加器模块产生波形数据ROM 的8 位读取地址RomAdder,设计复杂程度相对高,所以我们组另辟蹊径,并没有采用ROM实现,而采用了描点法,对应于不同的相位值给定不同的波形幅度取样值。

此设计中,我们取样了64个相位点,随着相位点的变化,针对不同要求的输出波形,给定相对应的输出幅值,从而产生不同的输出波形。

通过拨码开关可以选择输出正弦波,三角波,方波等不同波形。

在FPGA工程文件中,采用Sel[3..0]l来选择,当Sel为0001时,输出正弦波;当Sel为0010时,输出方波;当Sel为0100时,输出三角波;当Sel 为1000时,输出锯齿波。

将输出端接到实验板中的DAC0832,实现数模转换后,通过示波器即可观察到相应的实验波形。

3实验仿真此次课程设计初衷是打算在示波器上观察输出波形,但是由于实验箱中的DAC0832数模转换在连接后并没有输出,但模拟端是有电压值显示。

究其原因可能是DAC0832是与CPLD相连,而不是FPGA芯片连接,实验中所给出的管脚分配不对应导致。

所以只能选择通过仿真软件示出波形。

本设计中所采用的仿真软件是Modelsim6.4版本。

图3 Modelsim软件波形仿真结果如下:case sel iswhen "0001"=> --正弦波将时间轴展宽,可以看到波形呈阶梯状,且较为明显,这是由于本设计中取样值为64点,点数较少,如果增加取样值到256点或这更多,如1024点时,波形就会呈现出较平滑的特性。

正弦波when "0010"=> --方波方波方波波形较为清晰,规整,这是由于方波本身只有高低电平,幅值只有两个,不需要多点连续变化。

when "0100"=> --三角波三角波展宽时间轴,同样会出现类似正弦波的情形,原因也是取样值较少,波形没有呈现平滑变化的特点。

when"1000"=>--锯齿波锯齿波锯齿波的产生原理同三角波,只是在到最高点后下一时刻直接返回到最低点,之后继续。

在最后的仿真波形中,通过对波形周期的抓取,T=2560ns,在一个时间轴中分别显示了三周期的正弦波、三角波、方波、锯齿波,仿真结果如下:4.心得体会本次课程设计虽然我们组在做DDS的时候采用的是一种相对简单的方案进行实现,但是在调试过程中也遇到了很多问题,比如说在实验仿真过程中,起初打算用DAC0832进行数模转换,后接到示波器上进行波形显示,在实验箱中配置完对应的管脚后,不出现波形,最开始以为是实验程序问题,反复对程序进行修正,但是不管怎么修改,示波器始终没有波形出现,由于实验中用到的DAC0832是和CPLD相连接,而不是和FPGA直接相连,所以在实验指导中管脚分配可能出现错误。

不得不放弃用示波器示出波形,转而考虑用仿真软件Modelsim去显示,经过反复调试终于正确的显示了想要的波形。

完成本课程设计的同时,收获了很多,在遇到问题不断想办法去解决的过程中才是一个真正能学习到东西的过程。

我们组在调试的过程中,相互配合,尤其在孙永昌身上我觉得可以学到很多,他那种遇到问题不放弃,始终乐观去思考、去解决的态度让我感触很深,这也正是我所欠缺的。

经过我们的努力虽然完成本次课程设计的内容,但是仍有很多不足或者可以改进的地方,比如我们所采用的描点法实现直接数字频率计,由于取样点数目只有64点,必定会导致波形不是很平滑的过渡,有些地方呈现明显的阶梯状,波形不完美。

另外由于没有使用ROM,不能对波形进行频率的调节,功能较为单一。

这些都是我们需要改进的地方,我看到了我的不足,日后会加以改进。

附录library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity test isport( clk : in std_logic;sel : in std_logic_vector (3 downto 0);pout: out integer range 255 downto 0);end;architecture dacc of test issignal q: integer range 63 downto 0;signal d: integer range 255 downto 0;--signal q1: integer range 3 downto 0;beginprocess(clk)beginif clk'event and clk='1' thenif q<63 thenq<=q+1;elseq<=0;end if;end if;end process;process(q,sel)begincase sel iswhen "0001"=> --正弦波case q iswhen 00=>d<=255; when 01=>d<=254; when 02=>d<=252;when 03=>d<=249; when 04=>d<=245; when 05=>d<=239;when 06=>d<=233; when 07=>d<=225; when 08=>d<=217;when 09=>d<=207; when 10=>d<=197; when 11=>d<=186;when 12=>d<=174; when 13=>d<=162; when 14=>d<=150;when 15=>d<=137; when 16=>d<=124; when 17=>d<=112;when 18=>d<=99; when 19=>d<=87; when 20=>d<=75;when 21=>d<=64; when 22=>d<=53; when 23=>d<=43;when 24=>d<=34; when 25=>d<=26; when 26=>d<=19;when 27=>d<=13; when 28=>d<=8; when 29=>d<=4;when 62=>d<=254; when 61=>d<=252; when 60=>d<=249;when 59=>d<=245; when 58=>d<=239; when 57=>d<=233;when 56=>d<=225; when 55=>d<=217; when 54=>d<=207;when 53=>d<=197; when 52=>d<=186; when 51=>d<=174;when 50=>d<=162; when 49=>d<=150; when 48=>d<=137;when 47=>d<=124; when 46=>d<=112; when 45=>d<=99;when 44=>d<=87; when 43=>d<=75; when 42=>d<=64;when 41=>d<=53; when 40=>d<=43; when 39=>d<=34;when 38=>d<=26; when 37=>d<=19; when 36=>d<=13;when 35=>d<=8; when 34=>d<=4; when 33=>d<=1;when 32=>d<=0;when others=>null;end case;when "0010"=> --方波case q iswhen 00=>d<=255; when 01=>d<=255; when 02=>d<=255;when 03=>d<=255; when 04=>d<=255; when 05=>d<=255;when 06=>d<=255; when 07=>d<=255; when 08=>d<=255;when 09=>d<=255; when 10=>d<=255; when 11=>d<=255;when 12=>d<=255; when 13=>d<=255; when 14=>d<=255;when 15=>d<=255; when 16=>d<=255; when 17=>d<=255;when 18=>d<=255; when 19=>d<=255; when 20=>d<=255;when 21=>d<=255; when 22=>d<=255; when 23=>d<=255;when 24=>d<=255; when 25=>d<=255; when 26=>d<=255;when 27=>d<=255; when 28=>d<=255; when 29=>d<=255;when 30=>d<=255; when 31=>d<=255; when 63=>d<=0;when 62=>d<=0; when 61=>d<=0; when 60=>d<=0;when 59=>d<=0; when 58=>d<=0; when 57=>d<=0;when 56=>d<=0; when 55=>d<=0; when 54=>d<=0;when 53=>d<=0; when 52=>d<=0; when 51=>d<=0;when 50=>d<=0; when 49=>d<=0; when 48=>d<=0;when 47=>d<=0; when 46=>d<=0; when 45=>d<=0;when 44=>d<=0; when 43=>d<=0; when 42=>d<=0;when 41=>d<=0; when 40=>d<=0; when 39=>d<=0;when 38=>d<=0; when 37=>d<=0; when 36=>d<=0;when 35=>d<=0; when 34=>d<=0; when 33=>d<=0;when 32=>d<=0;when others=>null;end case;when "0100"=> --三角波case q iswhen 03=>d<=24; when 04=>d<=32; when 05=>d<=40;when 06=>d<=48; when 07=>d<=56; when 08=>d<=64;when 09=>d<=72; when 10=>d<=80; when 11=>d<=88;when 12=>d<=96; when 13=>d<=104; when 14=>d<=112;when 15=>d<=120; when 16=>d<=128; when 17=>d<=136;when 18=>d<=144; when 19=>d<=152; when 20=>d<=160;when 21=>d<=168; when 22=>d<=176; when 23=>d<=184;when 24=>d<=192; when 25=>d<=200; when 26=>d<=208;when 27=>d<=216; when 28=>d<=224; when 29=>d<=232;when 30=>d<=240; when 31=>d<=248; when 63=>d<=8;when 62=>d<=16; when 61=>d<=24; when 60=>d<=32;when 59=>d<=40; when 58=>d<=48; when 57=>d<=56;when 56=>d<=64; when 55=>d<=72; when 54=>d<=80;when 53=>d<=88; when 52=>d<=96; when 51=>d<=104;when 50=>d<=112; when 49=>d<=120; when 48=>d<=128;when 47=>d<=136; when 46=>d<=144; when 45=>d<=152;when 44=>d<=160; when 43=>d<=168; when 42=>d<=176;when 41=>d<=184; when 40=>d<=192; when 39=>d<=200;when 38=>d<=208; when 37=>d<=216; when 36=>d<=224;when 35=>d<=232; when 34=>d<=240; when 33=>d<=248;when 32=>d<=255;when others=>null;end case;when "1000"=> --锯齿波case q iswhen 00=>d<=0; when 01=>d<=4; when 02=>d<=8;when 03=>d<=12; when 04=>d<=16; when 05=>d<=20;when 06=>d<=24; when 07=>d<=28; when 08=>d<=32;when 09=>d<=36; when 10=>d<=40; when 11=>d<=44;when 12=>d<=48; when 13=>d<=52; when 14=>d<=56;when 15=>d<=60; when 16=>d<=64; when 17=>d<=68;when 18=>d<=72; when 19=>d<=76; when 20=>d<=80;when 21=>d<=84; when 22=>d<=88; when 23=>d<=92;when 24=>d<=96; when 25=>d<=100; when 26=>d<=104;when 27=>d<=108; when 28=>d<=112; when 29=>d<=116;when 30=>d<=120; when 31=>d<=124;when 63=>d<=252;when 62=>d<=248; when 61=>d<=244; when 60=>d<=240;when 59=>d<=236; when 58=>d<=232; when 57=>d<=228;when 56=>d<=224; when 55=>d<=220; when 54=>d<=216;when 53=>d<=212; when 52=>d<=208; when 51=>d<=204;when 50=>d<=200; when 49=>d<=196; when 48=>d<=192;when 47=>d<=188; when 46=>d<=184; when 45=>d<=180;when 44=>d<=176; when 43=>d<=172; when 42=>d<=168;when 41=>d<=164; when 40=>d<=160; when 39=>d<=156;when 38=>d<=152; when 37=>d<=148; when 36=>d<=144;when 35=>d<=140; when 34=>d<=136; when 33=>d<=132;when 32=>d<=128;when others=>null;end case;when others=>null;end case;end process;pout<=d;end;- 10 -。