时钟树综合

数字后端设计实现之时钟树综合实践篇

数字后端设计实现之时钟树综合实践篇时钟树综合定义时钟树综合就是指从某个clock的root点长到各个sink点的clock buffer/inverter tree。

工具试图将某个clock所属的所有sinks做到相同长度。

从概念上,我们可以得到几个要点。

图1 时钟树CTS之前你应该先搞清楚以下几点(非常重要)•clock的root点需要定义清楚。

这个可以通过create_clock来定义。

如果是create_generated_clock,它的master clock需要定义清楚。

同时要求generate clock与master clock是可以trace通的•clock 的sinks•哪些clock是同步,哪些是异步的•分析时钟结构,大致画出其结构图。

如果时钟结构比较复杂,建议编写CTS constraint,来引导工具build tree•定义好stop pin ignore pin exclude pin floating pin等•哪些clock是需要做inter-balance的衡量时钟树的几大指标合理的时钟结构能够加速Timing收敛(时钟树综合中级篇)时钟树综合(clock tree synthesis)基础篇设置DRC参数设置max_transition max_capacitance max_fanout等参数。

对于clock的max transition的设置,应该根据clock的频率来设置。

高频率的clock,需要额外设置严格点。

指定clock inverter listset_clock_tree_references -references $cts_clock_inv_listset_clock_tree_references -references $cts_clock_inv_list -sizing_onlyset_clock_tree_references -references $cts_clock_inv_list -delay_insertion_onlyclock inverter cell list的选择往往比较有讲究。

一网打尽时钟树综合ClockSkew

一网打尽时钟树综合ClockSkewClock Skew (时钟偏移) 分为Global skew和Local skew两大类。

•Global skewGlobal skew是泛指design中任意两个寄存器latency之差的最大值。

•Local skewLocal skew是指design中两个相关寄存器latency之差的最大值。

因此,在数字后端设计实现中,我们更多的是关注local skew。

因为local skew会直接影响到我们的时序(setup和hold)。

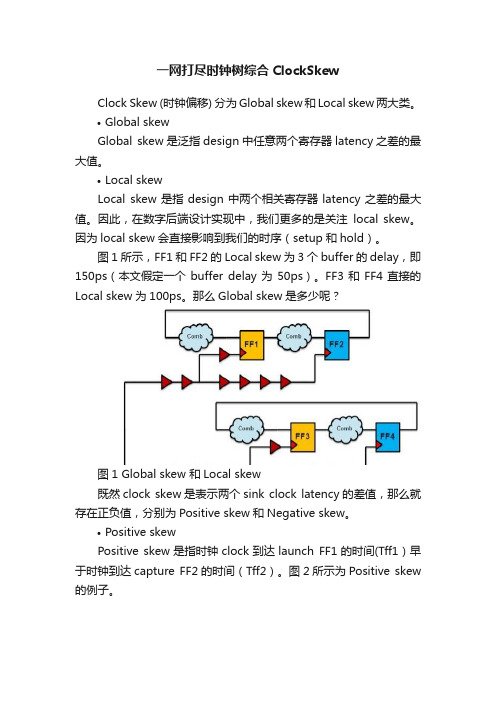

图1所示,FF1和FF2的Local skew为3个buffer的delay,即150ps(本文假定一个buffer delay为50ps)。

FF3和FF4直接的Local skew为100ps。

那么Global skew是多少呢?图1 Global skew 和Local skew既然clock skew是表示两个sink clock latency的差值,那么就存在正负值,分别为Positive skew和Negative skew。

•Positive skewPositive skew是指时钟clock到达launch FF1的时间(Tff1)早于时钟到达capture FF2的时间(Tff2)。

图2所示为Positive skew 的例子。

图2 Positive skew示意图对应的setup和hold检查波形如图3所示。

默认情况下setup检查的edge如图中绿色标识,hold检查的edge如图中红色标识。

显然在positive skew的情景下,setup检查变得宽松点,hold检查则变得更为严格。

吾爱IC社区公众号之前也推送过无数篇关于setup,hold的检查方式,如何画波形图,如何计算setup,hold time以及如何计算电路最高工作频率的分享。

如果对这些还心存疑问困惑,可以查看下面几篇文章。

听说Latch可以高效修hold违例(Timing borrowing及其应用)CRPR能补偿crosstalk吗?原来电路最高工作频率是这么算出来的(STA基础篇)秒杀数字后端实现中clock gating使能端setup violation问题数字芯片设计实现中修复setup违例的方法汇总深入浅出讲透set_multicycle_path,从此彻底掌握它Setup slack=Tclock-Tck-q(FF1)-T comb-Tsu(FF2) TskewHold slack = Tck-q(FF1) T comb-Thold(FF2)-TskewTclock=T ck-q(FF1) Tcomb Tsu(FF2)-Tskew图3 Positive skew下setup和hold check•Negative skewNegative skew是指时钟clock到达launch FF1的时间(Tff1)晚于时钟到达capture FF2的时间(Tff2)。

时钟树综合解读

同步Pins和忽略Pins

同步Pins: CTS优化达到 buffer约束(最大传 输时间/电容)和时 钟树目标(偏移,插 入延时等)) 忽略Pins: CTS加入一个小的 buffer去隔离所有 的Pins 忽略buffer约束 (最大传输时间/电 容和时钟树目标)

默认的Skew Optimization

带有SDC不确定的传播时钟

如果SDC不确定值包括抖动和时间裕量,Astro仍 能计算实际的时钟网络延时,同时模仿这些效应 调整SDC中set_clock_uncertainty 的值 通过估计偏移值减少这个值 执行相同的命令 sdc “set_propagated_clock [all_clocks]” 调节下面的时序设置项 Unset “Ignore Clock Uncertainty ” Unset “Ignore Propagated Clock ”

符合buffer约束(不符合该约束会报违规) 最大传输时间延迟 最大负载电容 最大扇出 最大buffer级数 符合时钟树目标(不会报违规) 最大偏移 根据Min/Max delay插入延迟

CTS流程

布局完成 设置时钟公共选项 综合时钟树 重新连接扫描链 使能传播时钟 Post-CTS布局优化 优化时钟偏移(CTO) 优化时序(Useful Skew CTO) 布线

时钟树综合结果

时钟buffer增加 阻塞可能会增加 非时钟树单元可能 会被移动到不理想 的位置 可能会引起新的时 序和最大tran/cap 违规

Post-CTS布局优化

Post-CTS布局优化能 优化时序和减少阻塞 执行逻辑和布局优化 去修复可能的时序 (建立时间和保持时 间)、最大电容和最 大过渡时间违规 保持时间推荐在这 里进行首次修复 Congestion Removal 能通过移动不必要的 非时钟树buffer减少 阻塞

时钟树综合(1)

时钟树综合(1)时钟树综合学习背景时钟信号是数据传输的基准,他对于同步数字系统的功能、性能、稳定性起决定性作⽤。

时钟信号通常是整个芯⽚中有最⼤扇出、通过最长距离、以最⾼速度运⾏的信号。

时钟信号必须要保证在最差的条件下,关键的时序要求能够满⾜,否则对时钟信号的任何不当的控制都可能导致紊乱情况,将错误的数据信号索存到寄存器,从⽽导致系统功能的错误。

时钟信号怎么产⽣的时钟信号源⼀般是从晶体(⽯英晶体、陶瓷晶体)产⽣的。

IC设计时通常会使⽤晶体振荡器来提供时钟源信号。

⼀般会使⽤PLL加上晶体振荡器来给芯⽚内部电路提供倍频或相位的时钟信号。

时钟信号特征时钟的周期(频率)、时钟延迟、时钟信号的不确定性是时钟的三个主要特征要素。

时钟信号延迟时钟信号延迟(latency)⼜称为插⼊延迟(insertion delay), 包括时钟源插⼊延迟和时钟⽹络插⼊延迟。

时钟源插⼊延迟是来⾃系统到当前芯⽚(当前模块)时钟根节点(clock root pin)之间的延迟,时钟⽹络插⼊延迟是时钟树的延迟。

时钟信号不确定性时钟信号的不确定性主要是有时钟信号抖动引起的,时钟抖动是先天存在的,所以在时钟树综合的时候只能考虑起影响,⽆法消除。

时钟抖动是信号实际时间与理想时间的偏差,抖动中含有确定抖动成分和随机抖动的成分【】。

时钟信号偏差时钟信号偏差是指同⼀时钟达到该时钟域内的不同寄存器之间的时间偏差,也即是skew=max(|t i−t j|)产⽣时钟偏差的原因有多种:时钟源到各个时钟端点的路径长度不同、各个端点负载不同、在时钟⽹中插⼊的缓冲器不同等。

在什么时候做时钟树综合:如下图所⽰,通常在物理设计布局完成之后布线之前进⾏时钟树综合。

在此之前所有的寄存器时钟信号是由同⼀个时钟pin驱动的,具有相同的延时的理想时钟。

已经⽣成了gatelevel 的netlist已经有⼀个初步的版图规划,每个逻辑门包括时序器件都有⼀个具体的位置。

已经基于理想时钟完成了时序优化设计。

芯片中时钟树综合质量评价指标

芯片中时钟树综合质量评价指标介绍时钟树是芯片设计中非常重要的一部分,它负责为芯片内的各个功能模块提供稳定的时钟信号。

时钟树的设计质量直接影响芯片的性能和功耗。

因此,对时钟树的综合质量进行评价是芯片设计过程中的重要任务。

时钟树的综合质量评价指标时钟树的综合质量评价指标主要包括以下几个方面:1. 时钟树延迟时钟树的延迟是指时钟信号从源端到达目的端所需的时间。

时钟树延迟的大小直接影响芯片的工作频率和时序要求。

因此,评价时钟树的综合质量时,需要考虑时钟树延迟是否满足设计要求。

2. 时钟树功耗时钟树的功耗是指时钟信号在时钟树中传输过程中所消耗的能量。

时钟树功耗的大小与时钟树的拓扑结构、电压和频率等因素有关。

评价时钟树的综合质量时,需要考虑时钟树功耗是否在可接受范围内。

3. 时钟树抖动时钟树的抖动是指时钟信号的相位或频率在传输过程中发生的变化。

时钟树抖动会导致芯片的时序偏差和时钟信号的不稳定性。

因此,评价时钟树的综合质量时,需要考虑时钟树抖动是否满足设计要求。

4. 时钟树噪声时钟树的噪声是指时钟信号中的不良成分,包括时钟信号的谐波、杂散等。

时钟树噪声会对芯片的功能模块产生干扰,影响芯片的性能和可靠性。

因此,评价时钟树的综合质量时,需要考虑时钟树噪声是否在可接受范围内。

评价指标的权重不同的芯片设计对时钟树的要求不同,因此,在评价时钟树的综合质量时,需要为不同的评价指标分配不同的权重。

一般来说,时钟树延迟和功耗是两个比较重要的指标,因为它们直接关系到芯片的性能和功耗。

而时钟树抖动和噪声相对来说可以适当放宽要求。

评价方法和工具评价时钟树的综合质量可以采用静态分析和动态仿真的方法。

静态分析是指通过对时钟树的结构和参数进行分析,预测时钟树的性能指标。

动态仿真是指通过模拟时钟信号在时钟树中的传输过程,评估时钟树的实际性能。

评价时钟树的综合质量还可以借助一些专门的工具,如PrimeTime、HSPICE等。

这些工具可以对时钟树进行详细的分析和仿真,提供时钟树的延迟、功耗、抖动和噪声等性能指标。

含有多路选择器路径的时钟树综合

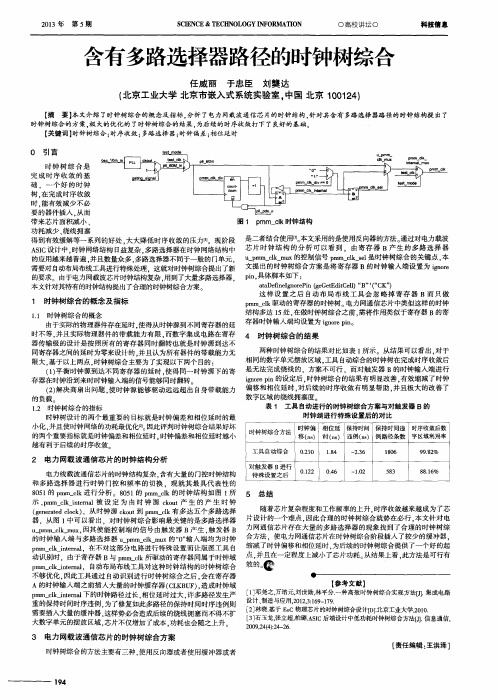

是二者结合使用日 。 本文采用 的是使用反 向器 的方法 。 通过对 电力载波 芯 片时 钟 结 构 的分 析 可 以看 到 .由寄 存 器 B产 生 的多 路 选择 器 u p mm_ e l km u x的控制信号 p m m _ c l k _ s e l 是 时钟树综合 的关键点 . 本 文提 出的时钟树综合 方案是将 寄存器 B的时钟输 入端设 置为 i g n o r e p i n . 具体脚本如下 :

【 摘 要】 本文介绍 了时钟树综合 的概念及指标 , 分析 了电力 网载波通信 芯片的时钟 结构 , 针对其含有 多路 选择器路径的 时钟 结构提 出了

时钟树 综合的方案 , 极大的优化的 了时钟树综合的结果 , 为后续的 时序收敛打下 了良好的基础 。

【 关键词 】 时钟树综合 ; 时序收敛 ; 多路选择 器; 时钟偏差 ; 相位延 时

_ _

a t a De i f n e l g n o r e P i n( g e Ge t E d i t C e l 1 )… B“( “ C K ” )

1 时钟树综合的概念及指标

1 . 1 时钟 树综合 的概念

由于实际的物理器件存在延时 . 使得从时钟源到不 同寄存器 的延 时不等 , 并且实 际物 理器件 的带 载能力有 限 . 而数字集成 电路在 寄存 器 传输级 的设计是 按照所有 的寄存器 同时翻转也就是 时钟源 到达不 同寄存器 之间的延时为零来设计 的. 并且认为所有器件 的带载 能力无 限大 , 基于以上两点 , 时钟树综合主要为 了实现 以下两个 目的: ( 1 ) 平衡 时钟源到达不 同寄存器 的延 时 , 使得 同一时钟源下 的寄 存 器在时钟沿到来时时钟输人端 的信号能够 同时翻转 ( 2 ) 解决 高扇出 问题 . 使 时钟源 能够驱动远远 超出 自身带 载能力 的负载。 1 . 2 时钟树综合 的指标 时钟树设计 的两个最 重要 的 目 标 就是时钟偏 差和相位延 时的最 小化 . 并且使 时钟 网络 的功耗最优化[ 2 1 因此评判时钟树综合结果好坏 的两个重要指标就是时钟偏差 和相位延 时 时钟偏差和相位延时越小 越有利于后续 的时序收敛

高性能芯片设计中的时钟树优化技术

高性能芯片设计中的时钟树优化技术时钟树是芯片设计中至关重要的一个组成部分,它负责传输时钟信号以保证芯片的正常工作。

在高性能芯片设计中,时钟树的优化技术尤为重要,可以提高芯片的稳定性、降低功耗,并保证芯片的高性能工作。

本文将介绍高性能芯片设计中的时钟树优化技术,并探讨其在芯片设计中的应用。

一、时钟树设计的重要性时钟信号是芯片工作的基准,它控制着各个功能模块的操作时序,因此时钟树设计的合理性直接影响着芯片的性能和功耗。

在高性能芯片设计中,要实现较高的工作频率和低功耗,时钟树的设计至关重要。

一个优秀的时钟树设计应具备以下几个方面的特点:1. 低时钟抖动:时钟抖动会导致芯片工作不稳定,降低性能。

通过合理的时钟树设计,可以减少时钟抖动,提高芯片的工作稳定性和可靠性。

2. 低功耗:时钟信号在芯片中的传输需要消耗功耗,较长的时钟路径和不优化的时钟树设计将导致大量的功耗浪费。

通过优化时钟树设计,可以降低功耗,提高芯片的能效。

3. 均衡和分布平衡:时钟信号在传输过程中,应该保持均衡和分布平衡,避免信号传输的不平衡导致时钟抖动和延迟问题。

二、时钟树优化的目标在高性能芯片设计中,时钟树优化的目标是实现如下几个方面的优化:1. 降低时钟路径的长度:时钟路径越短,芯片的工作频率越高,性能越好。

2. 降低时钟路径的延时:通过合理的时钟树设计,可以降低时钟路径的延时,提高芯片的工作速度。

3. 降低时钟树的功耗:优化时钟树设计,可以减少时钟信号传输过程中的功耗损耗,提高芯片的能效。

三、时钟树优化技术1. 时钟树综合:时钟树综合是时钟树优化的一项重要技术,通过对时钟信号的分析和综合,优化时钟树的结构,减少时钟路径的长度和延时。

时钟树综合工具可以根据设计需求自动完成时钟树的综合工作,生成一个最优的时钟树结构,提高芯片的性能和功耗。

2. 缓冲器插入:在时钟路径过长或者时钟分布不均衡时,可以通过插入合适的缓冲器来优化时钟树设计。

缓冲器可以提升时钟信号的驱动能力,减少时钟路径的延时和功耗。

Clock Tree

关于时钟树的调研在集成电路设计中,时钟信号是数据传输的基准,它对于同步数字系统的功能、性能和稳定性起着决定性的作用,所以时钟信号的特性及其分配网络尤其被人们关注。

时钟信号通常是整个芯片中有最大扇出、通过最长距离、以最高速度运行的信号。

时钟信号必须保证在最坏的条件下,关键的时序要求能得到满足。

因此有必要引入时钟树的概念。

首先,我们要明确时钟树的定义。

时钟树,即clock tree,是个由许多缓冲单元(buffer cell)平衡搭建的网状结构,它有一个源点,一般是时钟输入端(clock input port),也有可能是design内部某一个单元输出脚(cell output pin),然后就是由一级一级的缓冲单元搭建而成,具体的多少级,根据你的设置以及所使用的单元而定,目的就是使所用终点的clock skew(时钟脉冲相位差)、insertion delay(插入延迟)以及transtion最小了,满足设计要求。

一、为什么要使用时钟树和时间管理器?FPGA内部所有的同步部件(如可编程逻辑块内被配置为触发器的寄存器)都需要时钟信号来驱动。

这样的时钟信号一般是来自外部世界的,通过专用时钟输入引脚进入FPGA,接着传送到整个器件并连接到适当的寄存器。

之所以称为时钟树,是因为主时钟信号在芯片内一次又一次地进行分支(触发器可以视为在分支末端的“叶子”)。

使用这种结构是为了保证所有触发器的时钟信号尽可能一致。

如果时钟使用一条长的走线来一个接一个地驱动触发器,那么最接近时钟引脚的触发器接受的信号看上去将比位于链条的最末端所接收到的快很多,这被称为偏移,并且会带来很多问题(甚至使用时钟树时,在分支上的寄存器之间和分支本身之间也存在一定量的偏移)。

时钟树使用专门的走线,与通用可编程互连相分离。

在实际情况中,可以有多个始终引脚(不能使用的时钟引脚可以作为通用I/O 引脚),而在器件内部可以有多个时钟树。

如果在配置时不把时钟引脚直接连入内部的时钟树,也可以先用该引脚驱动一个称为时钟管理器的专用硬件功能块,由时钟管理器产生一定数量的时钟树。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

布局-----完成 电源和地网络-----预布线 估计阻塞------可接受 估计时序------可接受(~0ns) 估计最大电容/传输时间-----没有违规 高扇出网络: Reset,Scan Enable已经综合 时钟还没有综合

Starting Point Before CTS

CTS目标

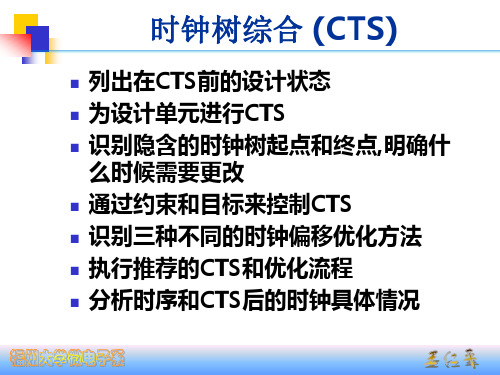

时钟树综合 (CTS)

列出在CTS前的设计状态 为设计单元进行CTS 识别隐含的时钟树起点和终点,明确什 么时候需要更改 通过约束和目标来控制CTS 识别三种不同的时钟偏移优化方法 执行推荐的CTS和优化流程 分析时序和CTS后的时钟具体情况

CTS开始时的设计状态

在CTS期间进行优化

在CTS期间进行优化

重新连接扫描链

在布局前打断扫描链,让布局集中在功能路径 在时钟树生成之后,要进行重新连接扫描链和优化扫描链, 重新连接扫描链和优化扫描链在下一个优化步骤包括修复 hold time 相同组的FFS,在打断前先’traced’ 不同的顺序:基于布局,减少布线资源

时钟树偏移分析

拥塞图分析

为了得到更准确的拥塞图,执行GlobalRoute命令进 行全局布线,再执行axgDisplayPLCongestionMap命令对拥 塞图显示方式进行设置,然后按快捷键F6在版图上显示布 线拥塞的情况如图所示,从中可知仅存在4处蓝色(溢出数 为1)区域,因此可判断拥塞在允许范围内。

Post-CTS设置:传播时钟

CTS后,Astro能计算实际的时钟网络延时而 不是使用SDC中估计的理想值 执行下面命令: sdc “set_propagated_clock [all_clocks]” 调整下面的时序设置项 set “Ignore Clock Uncertainty” Unset “Ignore Propagated Clock”

时钟树综合结果

时钟buffer增加 阻塞可能会增加 非时钟树单元可能 会被移动到不理想 的位置 可能会引起新的时 序和最大tran/cap 违规

Post-CTS布局优化

Post-CTS布局优化能 优化时序和减少阻塞 执行逻辑和布局优化 去修复可能的时序 (建立时间和保持时 间)、最大电容和最 大过渡时间违规 保持时间推荐在这 里进行首次修复 Congestion Removal 能通过移动不必要的 非时钟树buffer减少 阻塞

测试

若SDC中set_clock_uncertainty约束过高 (如0.05ns),你想放松到0.02ns,怎么实现? 同步Pin和忽略pin的区别在哪里?列出一些 隐含的同步和忽略Pin例子 全局和局部偏移优化的优缺点? 在CTS期间,产生时钟和主时钟都被当作相 同的时钟域?

测试

Post-CTS优化:根据需要反复执行

对于一个大的设计,每 次优化目标只有一个,如 修复hold时间等

Post-CTS布局优化结果

通过逻辑优化和单元重新放 置来修复时序(建立时间和保 持时间)、最大电容和最大过 渡时间违规可能会影响时钟 网络----FFS可能会被移动. 这将可能影响时钟偏移和插 入延时. 因此要分析时钟偏移和插入 延时! 如果想不影响时钟偏移和插 入延时,则需保持FFS位置固 定,执行clock->Utilities>Mark Clock Tree…

时钟树综合

建立buffer树去平衡负载达到最小时钟偏移

时钟树综合

延迟线加入去符合插入延迟目标

时钟树的起点和终点

时钟树起点是在.SDC文件 定义的时钟源: create_clock –p 2 CLOCK 时钟树终点在Astro定义 的”stop Pins” 两种类型的”stop Pins” 同步Pins:时序单元和宏 单元的Clock Pins 忽略Pins:其它

时钟延时在每一个时钟域内全部进行平衡,经过所 有的主时钟和产生时钟的clock-pin,去减少时钟 偏移到0,或尽可能小

时钟公共选项设置

默认的设置如图 时钟公共选项设置 在CTS和优化之前进 行设置

全局偏移(运行钟树

默认情况下,所有时钟域 用目标偏移为0进行综合 所有SDC定义的时钟都进 行综合, 除非在clock nets中列出时钟信号时, 其它不综合 默认情况下,在SDC中的 set_clock_uncertainty 在CTS时没有用

时钟树时序分析

使用astReportTiming命令进行时序分析得 如图所示,从中可知建立时间、保持时间、最 大电容和最大过渡时间满足要求。

时钟树偏移分析

执行命令

执行命令astSkewAnalysis得出时钟 偏移报告,如图所示,从图中可知最 长时钟路径延时为1.487ns,最短时 钟路径延时为1.409ns,全局时钟偏 移为0.078ns。

符合buffer约束(不符合该约束会报违规) 最大传输时间延迟 最大负载电容 最大扇出 最大buffer级数 符合时钟树目标(不会报违规) 最大偏移 根据Min/Max delay插入延迟

CTS流程

布局完成 设置时钟公共选项 综合时钟树 重新连接扫描链 使能传播时钟 Post-CTS布局优化 优化时钟偏移(CTO) 优化时序(Useful Skew CTO) 布线

指定非默认的偏移(例1)

若所有时钟在 SDC文件中有 set_clock_unc ertainty值为 0.2ns,你想在 CTS时用这个值 而不是默认值0, 则在Target Skew中设置0.2 所有时钟用相 同的偏移值进 行综合

指定非默认的偏移(例2)

假设其中一个时钟 (Clock2)是一个低频 时钟有2.0ns的正偏 移,因此要求Astro忽 略默认的0.2ns偏移 而用2.0ns或更大的 偏移来减少运行时间 (这个时钟要先进行 综合) 默认,一旦一个时钟 已经CTS,那么在后续 的CTS运行将不再综 合(然后余下的时钟 用0.2ns偏移进行CTS)

带有SDC不确定的传播时钟

如果SDC不确定值包括抖动和时间裕量,Astro仍 能计算实际的时钟网络延时,同时模仿这些效应 调整SDC中set_clock_uncertainty 的值 通过估计偏移值减少这个值 执行相同的命令 sdc “set_propagated_clock [all_clocks]” 调节下面的时序设置项 Unset “Ignore Clock Uncertainty ” Unset “Ignore Propagated Clock ”

同步Pins和忽略Pins

同步Pins: CTS优化达到 buffer约束(最大传 输时间/电容)和时 钟树目标(偏移,插 入延时等)) 忽略Pins: CTS加入一个小的 buffer去隔离所有 的Pins 忽略buffer约束 (最大传输时间/电 容和时钟树目标)

默认的Skew Optimization

“Useful Skew”优化

Useful Skew优化对保持时间不足不进行优化 强迫优化,使用:useful_skew_opt -buffer_sizing –hold_target -2.0 潜在的保持时间违规可通过使用post-CTS布局优化 进行修复

测试

1、在CTS前,高扇出网络已经进行综合和初 始时间树已经建立 2、CTS努力要实现的是哪两种目标 3、默认,CTS要: A.符合SDC中时间偏移约束 B.符合SDC中时间偏移和插入延时约束 C.符合最小偏移和SDC中插入时间约束 D.减少时间偏移和插入延时到0

在CTS后和运行post-CTS优化前,哪两个主 要任务必须实现? 列出运行post-CTS优化的三个优点? CTO的优点是什么以及什么时候你必须运行 它? 什么时候应该运行Useful Skew优化?

时钟树综合总结

功耗分析

执行astReportClockTreePower命令对FFT 处理器时钟树进行功耗优化分析,优化前分析功 耗为218.436mW,经过功耗优化后进行功耗分析 得出结果如图所示,从中可知功耗降为 209.479mW。

时钟树浏览

时钟树浏览

时钟树浏览

时钟树浏览

时钟树优化

在布线前执行额外的时钟树优化去进一步 减少时钟偏移和达到插入延时

插入延时和忽略约束

插入延时目标: 用这些设置去控制 最小/最大插入延时 默认在SDC的插入 延时具有优先,除非 执行axSetIntparam “acts” “ingore set_clock_latency” 1命令才忽略SDC设 置 你可以选择完全忽 略SDC或库的约束进 行CTS

导入CTS

在CTO后仍有时序违规

时钟树已经进行很好的平衡,但仍存在建立 时间违规?

“Useful Skew”优化

“Useful Skew CTO”使用流水借时间工 艺来减少或消除建立时间违规,同时在 其它地方保持平衡偏移

“Useful Skew”优化

修复建立时间违规通过利用在流水中的正偏 移进行改变时钟buffer尺寸

指定非默认的偏移(例3)

不是一个时钟,现在假设所有的时钟有不同 的不确定值,用更好的方法: 输入axSetIntparam “acts” “ingore set_clock_uncertainty” 0命令让Astro 用SDC文件中的值而不是GUI中的偏移目标 值

时钟buffer约束

最大tran/cap/fanout: 如果在多个地方指定 (库,SDC文件或Astro默 认), Astro使用最小值 最大buffer级数 用默认的初始值(20) 只有在仔细分析或基于 以住经验的基础上才需 要调整 如果设置太紧,违规可能 不能修复