双2线-4线译码器真值表与逻辑表达式(精)

4常用组合逻辑电路

RBI =0且A3 ~ A0=0时,使Ya ~ Yg=0,全灭. RBO :RBI=0,A3~A0=0时,RBO=0;否则RBO=1

多个译码器的连接

三,数据分配器

数据分配器是将一个输入数据根据需要送到多个 不同的输出通道上.

Y0 Y1 Y2n-1

数据输入

n位通道选择信号

数据输入 例: 地址 输入

00 X

&

01

& 1

B 11 10

X

B

Y3

A

1

X

01 11 X

X X

X

+UCX X

X X

Y2 10 Y X Y1 0

2,二 — 十进制编码器 将十个状态(对应于十进制的十个代码)编 制成BCD码. 十个输入 输入:Y0 Y9 输出:ABCD 列出状态表如下: 四位

2,二 — 十进制编码器

8421BCD编码表 输出 十进制数 ABCD 0 ( y0 ) 0000 1 ( y1 ) 0001 2 ( y2 ) 0010 3 ( y3 ) 0011 4 ( y4 ) 0100 5 ( y5 ) 0101 6 ( y6 ) 0110 7 ( y7 ) 0111 8 ( y8 ) 1000 9 ( y9 ) 1001 输入

&

Y2 = B A

1

Y3 = BA

EI=0 — 译码器工作

EI

EI=1—译码器被封锁

实验三-数据选择器译码器全加器

实验三:数据选择器和译码器应用1. 能力培养目标● 理解数据选择器和译码器的逻辑功能● 运用数据选择器和译码器的逻辑关系设计实际应用2. 项目任务要求(1)测试4选1数据选择器的逻辑功能,通过示波器观测每种组合下数据选择器的输出波形(2)测试2-4线译码器的逻辑功能(3)将2-4线译码器扩展组成3-8线译码器,利用两个2-4线译码器扩展组成3-8线译码器(4)利用2-4线译码器设计并实现组合逻辑电路B A F ⊕=【选做】3. 项目分析(1) 数据选择器及主流芯片数据选择器是一种多输入、单输出的组合逻辑电路,其应用主要包括通过级联进行通道扩展数据输入端的个数;或者配合门电路实现逻辑函数,组成函数发生器。

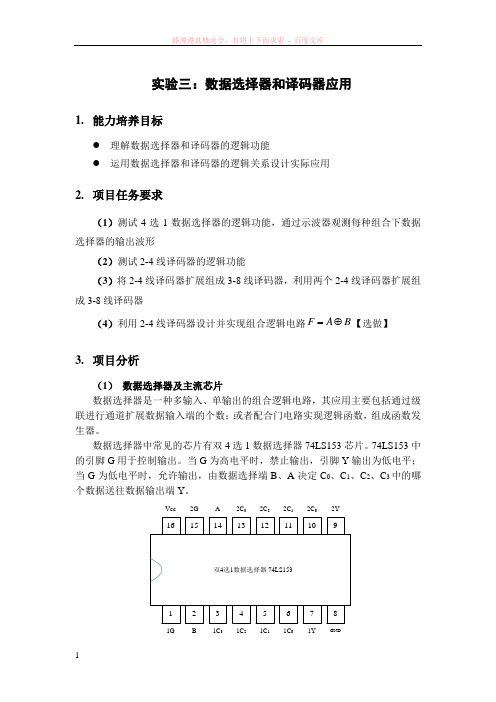

数据选择器中常见的芯片有双4选1数据选择器74LS153芯片。

74LS153中的引脚G 用于控制输出。

当G 为高电平时,禁止输出,引脚Y 输出为低电平;当G 为低电平时,允许输出,由数据选择端B 、A 决定C 0、C 1、C 2、C 3中的哪个数据送往数据输出端Y 。

14131211109161234567双4选1数据选择器 74LS153Vcc2GA2C 32C 22C 12C 01Y1GB1C 31C 21C 11C 01582YGND图2-3-1 74LS153引脚结构图 表2-3-1 4选1数据选择器真值表选择输入 数据输入 选通 输出 B A C 0 C 1 C 2 C 3 G Y X X X X X X H L L L L X X X L L L L H X X X L H L H X L X X L L L H X H X X L H H L X X L X L L H L X X H X L H H H X X X L L L H HX X X HLH(2) 译码器及主流芯片译码器中常见的芯片有双2-4线译码器74LS139,其引脚结构图和真值表分别如下:14131211109161234567双2-4线译码器 74LS139Vcc2G2A2B2Y 02Y 12Y 21Y 31G1A1B1Y 01Y 11Y 21582Y 3GND图2-3-2 74LS139引脚结构图 表2-3-2 2-4线译码器真值表输入端输出端允许G选择B AY 0(____________________0BA G Y =) Y 1(_________________1B A G Y =) Y 2(_________________2B A G Y =)Y 3(______________3B A G Y =)H X X H H H H L L L L H H H L L H H L H H L H L H H L H LH HH H H L在74LS139中,引脚G 用于控制输出。

组合电路(2译码)sk

与总线断开

数 据 A

三态门

EA

三态门

EB

三态门

EC

三态门

ED

A 0

B

Y0

Y1Y 2

C

Y3

D

A0 A1

2-4线译 码器

S

0 0

50

例题四:构成函数发生器。

译码器输出: Fi=mi 或 Fi = mi

译码器每个输出对应一个最小项,n变量译 码器的输出给出了全部最小项。

利用MSI译码器进行逻辑设计的一般步骤

余3码

0 0 0 0 0 1 1 1 1 1 0 1 1 1 1 0 0 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0

5421

0 0 0 0 0 1 1 1 1 1 0 0 0 0 1 0 0 0 0 1 0 0 1 1 0 0 0 1 1 0 0 1 0 1 0 0 1 0 1 0

1 1 ~ 1 1 1 1 1 1 1 1 1 1

逻辑表达式

F0 = A3 A2 A1A0 F1 = A3 A2 A1 A0

F8 = A3 A2 A1 A0 F9 = A3 A2 A1 A0

7442逻辑符号

译码输出

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y8 Y9

7442 A0 A1 A2 A3

b

f e

UCC 共 阳

f e

共 阴

2、7449七段译码器

配合各种七段显示器有专用的七段译 码器。这类MSI产品很多如:7448、74248、 7449、74249、7447、74247、74347等。还 有CMOS产品等。 此处仅以7449为例来介绍此类产品的 设计过程。

74138的工作原理如下图所示

74138的工作原理如下图所示:从上图可看出,74138有三个输入端:A0、A1、A2和八个输出端Q0~Q7。

当输入端A0、A1、A2的编码为000时,译码器输出为Q0=0,而Q1~Q7=1。

即Q0对应于A0、A1、A2为000状态,低电平有效。

A0、A1、A2的另外7种组合见后面的真值表。

图中S1、S2、S3为使能控制端,起到控制译码器是否能进行译码的作用。

只有S1为高电平,S2、S3均为低电平时,才能进行译码,否则不论输入羰输入为何值,每个输出端均为1。

下图是输入端A0、A1、A2为000,控制端S1=1、S1=0、S2=0的电平示意图(红色数字为端口电平),大家可按下图进行分析,也可以分析输出端另外七种组合时的输出情况。

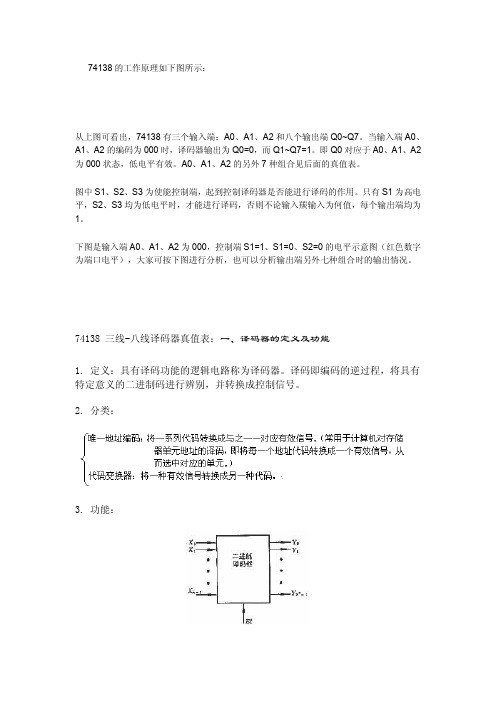

74138 三线-八线译码器真值表:一、译码器的定义及功能1. 定义:具有译码功能的逻辑电路称为译码器。

译码即编码的逆过程,将具有特定意义的二进制码进行辨别,并转换成控制信号。

2. 分类:3. 功能:二进制译码器一般原理图一个n→2n译码器结构如上图,n个输入端,2n个输出端。

它是一个多输出逻辑组合电路,对每种可能的输入条件,有且仅有一个输出信号为逻辑“1”,所以我们可以把它当作最小项产生器,一个输出就相应于提取一个最小项。

4. 译码器电路结构:首先我们先来分析两输入译码器结构,由于2输入变量A、B共有4种不同状态的组合,因而可以译出4个输出信号,所以简称为2/4线译码器。

2线-4线译码器逻辑图由图可以写出输出端逻辑表达式:根据输出逻辑表达式可以列出功能表。

由表可知,时无论A、B为何种状态,输出全为1,译码器处于非工作状态。

而当时,对应于AB 的某种状态组合,其中只有一个输出量为0,其余各输出量均为1。

例如:AB=0时,输出Y0=0,Y1~Y3=1,由此可见,译码器是通过输出端的逻辑电平来识别不同的代码。

在我们讲述的这种结构中,输出0表示有效电平,所以就叫做低电平有效。

2线-4线译码器功能表二、集成电路译码器1.74138集成译码器下图为常用的集成译码器74LS138的逻辑图和引脚图。

数字电子技术(第四版)(孙津平)章 (4)

图 3.22 例8的连接图

3. 例9

试用八选一数据选择器74LS151产生逻辑函数

解 把逻辑函数变换成最小项表达式:

八选一数据选择器的输出逻辑函数表达式为

若将式中A2、A1、A0用A、B、C来代替, D0=D1=D3= D6=1, D2=D4=D5=D7=0,画出该逻辑函数的逻辑图, 如图 3.23所示。

1. 74LS151是一种典型的集成电路数据选择器。 如图3.21所示 是74LS151的管脚排列图。 它有三个地址端A2A1A0。 可选择

D0~D7八个数据, 具有两个互补输出端W和W。 其功能如表3.12

所示。

图 3.21 74LS151 (a) 符号图; (b) 管脚图

2. 例 8 用两片74LS151连接成一个十六选一的数据选择器。 解 十六选一的数据选择器的地址输入端有四位, 最高

止工作。

图3.18 例7的连接图

3.4 数据选择器和数据分配器

3.4.1 数据选择器

数据选择器按要求从多路输入选择一路输出, 根据输入端 的个数分为四选一、 八选一等等。 其功能相当于如图3.19所示 的单刀多掷开关。

图3.19 数据选择器示意图

如图3.20所示是四选一选择器的逻辑图和符号图。 其

2. 非二进制编码器(以二-十进制编码器为例) 二-十进制编码器是指用四位二进制代码表示一位十进制数 的编码电路, 也称10线-4线编码器。四位二进制代码共有16 种组合状态, 而0~9共10个数字只用其中 10 个状态, 所以二-十进制编码方案很多。 最常见是8421 BCD码编码器,

如图3.7所示。 其中,输入信号I0~I9代表0~9共10个十进制信号, 输出信号Y0~Y3为相应二进制代码。

话铃响用1表示, 铃没响用0表示。 当优先级别高 的信号有效时, 低级别的则不起作用, 这时用×表示; 用

实验四编码器,译码器,数码管(定稿)

实验四编码器、译码器、数码管一、实验目的1.掌握编码器、译码器和七段数码管的工作原理和特点。

2.熟悉常用编码器、译码器、七段数码管的逻辑功能和他们的典型应用。

3. 熟悉“数字拨码器”(即“拨码开关”)的使用。

二、实验器材1. 数字实验箱 1台2. 集成电路:74LS139、 74LS248、 74LS145、 74LS147、 74LS148 各1片74LS138 2片3. 电阻: 200Ω 14个4. 七段显示数码管:LTS—547RF 1个三、预习要求1.复习编码器、译码器和七段数码管的工作原理和设计方法。

2. 熟悉实验中所用编码器、译码器、七段数码管集成电路的管脚排列和逻辑功能。

3. 画好实验用逻辑表。

四、实验原理和电路按照逻辑功能的不同特点,常把数字电路分成两大类:一类叫做组合逻辑电路,另一类叫做时序逻辑电路。

组合逻辑电路在任何时刻其输出信号的稳态值,仅决定于该时刻各个输人端信号的取值组合。

在这种电路中,输入信号作用以前电路的状态对输出信号无影响。

通常,组合逻辑电路由门电路组成。

(一)组合逻辑电路的分析方法:a.根据逻辑图,逐级写出函数表达式。

b.进行化简:用公式法或图形法进行化简、归纳。

必要时,画出真值表分析逻辑功能。

(二)组合逻辑电路的设计方法:从给定逻辑要求出发,求出逻辑图。

一般分以下四步进行。

a.分析要求:将问题分析清楚,理清哪些是输入变量,哪些是输出函数。

进行逻辑变量定义(即定义字母A、B、C、D ……所代表的具体事物)。

b. 根据要求的输入、输出关系,列出真值表。

c. 进行化简:变量比较少时,用图形法;变量多时,可用公式法化简。

化简后,得出逻辑式。

d. 画逻辑图:按逻辑式画出逻辑图。

进行上述四步工作,设计已基本完成,但还需选择元件——数字集成电路,进行实验论证。

值得注意的是,这些步骤的顺序并不是固定不变的,实际设计时,应根据具体情况和问题难易程度进行取舍。

(三)常用组合逻辑电路:1.编码器编码器是一种常用的组合逻辑电路,用于实现编码操作。

74138的工作原理如下图所示

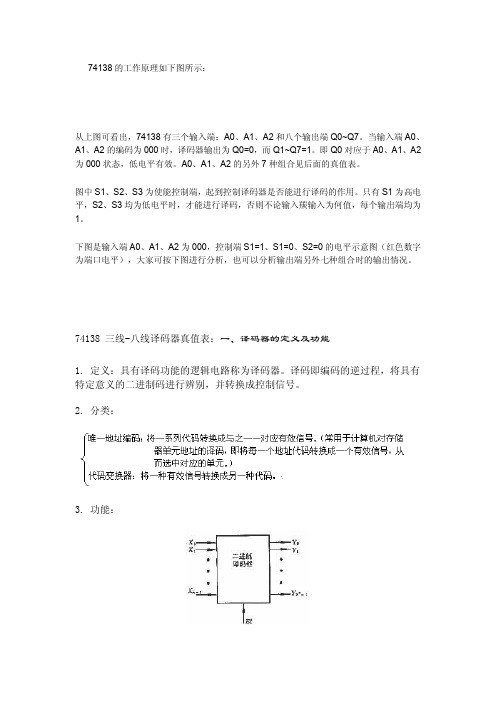

74138的工作原理如下图所示:从上图可看出,74138有三个输入端:A0、A1、A2和八个输出端Q0~Q7。

当输入端A0、A1、A2的编码为000时,译码器输出为Q0=0,而Q1~Q7=1。

即Q0对应于A0、A1、A2为000状态,低电平有效。

A0、A1、A2的另外7种组合见后面的真值表。

图中S1、S2、S3为使能控制端,起到控制译码器是否能进行译码的作用。

只有S1为高电平,S2、S3均为低电平时,才能进行译码,否则不论输入羰输入为何值,每个输出端均为1。

下图是输入端A0、A1、A2为000,控制端S1=1、S1=0、S2=0的电平示意图(红色数字为端口电平),大家可按下图进行分析,也可以分析输出端另外七种组合时的输出情况。

74138 三线-八线译码器真值表:一、译码器的定义及功能1. 定义:具有译码功能的逻辑电路称为译码器。

译码即编码的逆过程,将具有特定意义的二进制码进行辨别,并转换成控制信号。

2. 分类:3. 功能:二进制译码器一般原理图一个n→2n译码器结构如上图,n个输入端,2n个输出端。

它是一个多输出逻辑组合电路,对每种可能的输入条件,有且仅有一个输出信号为逻辑“1”,所以我们可以把它当作最小项产生器,一个输出就相应于提取一个最小项。

4. 译码器电路结构:首先我们先来分析两输入译码器结构,由于2输入变量A、B共有4种不同状态的组合,因而可以译出4个输出信号,所以简称为2/4线译码器。

2线-4线译码器逻辑图由图可以写出输出端逻辑表达式:根据输出逻辑表达式可以列出功能表。

由表可知,时无论A、B为何种状态,输出全为1,译码器处于非工作状态。

而当时,对应于AB 的某种状态组合,其中只有一个输出量为0,其余各输出量均为1。

例如:AB=0时,输出Y0=0,Y1~Y3=1,由此可见,译码器是通过输出端的逻辑电平来识别不同的代码。

在我们讲述的这种结构中,输出0表示有效电平,所以就叫做低电平有效。

2线-4线译码器功能表二、集成电路译码器1.74138集成译码器下图为常用的集成译码器74LS138的逻辑图和引脚图。

含两个2-4译码器的74HC139芯片版图

集成电路课程设计1. 目的与任务本课程设计是《集成电路分析与设计基础》的实践课程,其主要目的是使学生在熟悉集成电路制造技术、半导体器件原理和集成电路分析与设计基础上,训练综合运用已掌握的知识,利用相关软件,初步熟悉和掌握集成电路芯片系统设计→电路设计及模拟→版图设计→版图验证等正向设计方法。

2. 设计题目与要求2.1设计题目及其性能指标要求器件名称:含两个2-4译码器的74HC139芯片 要求电路性能指标:(1) 可驱动10个LSTTL 电路(相当于15pF 电容负载); (2) 输出高电平时,|I OH |≤20μA ,V OH ,min =4.4V ; (3) 输出底电平时,|I OL |≤4mA ,V OL ,man =0.4V ; (4) 输出级充放电时间t r =t f ,t pd <25ns ;(5) 工作电源5V ,常温工作,工作频率f work =30MHz ,总功耗P max =150mW 。

2.2设计要求1. 独立完成设计74HC139芯片的全过程;2. 设计时使用的工艺及设计规则: MOSIS:mhp_n12;3. 根据所用的工艺,选取合理的模型库;4. 选用以lambda(λ)为单位的设计规则;5. 全手工、层次化设计版图;6. 达到指导书提出的设计指标要求。

3. 设计方法与计算 3.1 74HC139芯片简介74HC139是包含两个2线-4线译码器的高速CMOS 数字电路集成芯片,能与TTL 集成电路芯片兼容,它的管脚图如图1所示,其逻辑真值表如表1所示:图1 74HC139芯片管脚图 表1 74HC139真值表计时只需分析其中一个2—4译码器即可,从真值表我们可以得出Cs 为片选端,当其为0时,芯片正常工作,当其为1时,芯片封锁。

A1、A0为输入端,Y0-Y3为输出端,而且是低电平有效。

2—4译码器的逻辑表达式,如下所示:01010A A C A A C Y s s ⋅⋅=++= 01011A A C A A C Y s s ⋅⋅=++=01012A A C A A C Y s s ⋅⋅=++= 01013A A C A A C Y s s ⋅⋅=++=74HC139的逻辑图如图2所示:图2 74HC139逻辑图3.2 电路设计本次设计采用的是m12_20的模型库参数进行各级电路的尺寸计算,其参数如下: NMOS: εox =3.9×8.85×10﹣12F/m μn =605.312×10﹣4㎡/Vst ox =395×10﹣10m V tn =0.81056V PMOS: εox =3.9×8.85×10﹣12F/m μp =219×10﹣4㎡/Vst ox =395×10﹣10m V tp =﹣0.971428V 3.2.1 输出级电路设计根据要求输出级电路等效电路图如图3所示,输入Vi 为前一级的输出,可认为是理想的输出,即V IL =Vss, V IH =V DD 。