除法器设计报告

现代计算机组成原理——除法器设计

数字系统组成原理和设计技术实验:除法器学号 1115108052姓名詹炳鑫班级电子2班华侨大学电子工程系一.程序LIBRARY IEEE;USE IEEE.std_logic_1164.ALL;USE IEEE.std_logic_unsigned.ALL;ENTITY devide ISPORT(reset, clock, start : IN STD_LOGIC;x : IN STD_LOGIC_VECTOR( 4 DOWNTO 0 );y : IN STD_LOGIC_VECTOR( 8 DOWNTO 0 ); done, overflow : OUT STD_LOGIC;q, r : OUT STD_LOGIC_VECTOR( 4 DOWNTO 0 ) );END devide;ARCHITECTURE behav OF devide ISSIGNAL rx : STD_LOGIC_VECTOR( 5 DOWNTO 0 ); SIGNAL ry : STD_LOGIC_VECTOR( 5 DOWNTO 0 ); SIGNAL rq : STD_LOGIC_VECTOR( 4 DOWNTO 0 );SIGNAL rmd : STD_LOGIC_VECTOR( 5 DOWNTO 0 ); SIGNAL flag_subadd : bit;SIGNAL state : integer RANGE 0 TO 6;BEGINPROCESS ( reset, clock )V ARIABLE sq : STD_LOGIC;BEGINIF reset = '0' THENrx <= ( OTHERS => '0' );ry <= ( OTHERS => '0' );rq <= ( OTHERS => '0' );state <= 0;ELSIF clock'event AND clock = '1' THENCASE STATE ISWHEN 0 =>rx( 5 DOWNTO 0 ) <= x(4) & x( 4 DOWNTO 0 ) ;ry( 5 DOWNTO 0 ) <= y(8) & y( 8 DOWNTO 4 ) ;rq( 4 DOWNTO 0 ) <= y( 3 DOWNTO 0 ) & '0';flag_subadd <= '1';done <= '0';overflow <= '0';IF start = '1' THENstate <= 1;END IF;WHEN 1 =>IF rmd(5) = '0' THENoverflow <= '1';state <= 0;done <= '1';ELSEstate <= state + 1;sq := '0';ry( 5 DOWNTO 0 ) <= rmd( 4 DOWNTO 0 ) & rq(4); rq( 4 DOWNTO 0 ) <= rq( 3 DOWNTO 0 ) & sq; flag_subadd <= '0';END IF;WHEN 5 =>IF rmd(5) = '0' THENsq := '1';flag_subadd <= '1';ELSEsq := '0';flag_subadd <= '0';END IF;ry( 5 DOWNTO 0 ) <= rmd( 4 DOWNTO 0 ) & rq(4); ry( 5 DOWNTO 0 ) <= rmd( 5 DOWNTO 0 );rq( 4 DOWNTO 0 ) <= rq( 3 DOWNTO 0 ) & sq; state <= state + 1;WHEN 6 =>IF rq(0) = '0' THENry <= rmd( 5 DOWNTO 0 );r <= rmd( 4 DOWNTO 0 );ELSEr <= ry( 4 DOWNTO 0);END IF;state <= 0;q <= rq;done <= '1' ;WHEN OTHERS =>IF rmd(5) = '0' THENsq := '1';flag_subadd <= '1';ELSEsq := '0';flag_subadd <= '0';END IF;ry( 5 DOWNTO 0 ) <= rmd( 4 DOWNTO 0 ) & rq(4);rq( 4 DOWNTO 0 ) <= rq( 3 DOWNTO 0 ) & sq;state <= state + 1;END CASE;END IF;END PROCESS;rmd <= ry + rx WHEN flag_subadd = '0' ELSEry + NOT rx + 1;END behav;-- Copyright (C) 1991-2011 Altera Corporation-- Your use of Altera Corporation's design tools, logic functions-- and other software and tools, and its AMPP partner logic-- functions, and any output files from any of the foregoing-- (including device programming or simulation files), and any-- associated documentation or information are expressly subject-- to the terms and conditions of the Altera Program License-- Subscription Agreement, Altera MegaCore Function License-- Agreement, or other applicable license agreement, including,-- without limitation, that your use is for the sole purpose of-- programming logic devices manufactured by Altera and sold by-- Altera or its authorized distributors. Please refer to the-- applicable agreement for further details.-- *************************************************************************** -- This file contains a Vhdl test bench template that is freely editable to-- suit user's needs .Comments are provided in each section to help the user-- fill out necessary details.-- *************************************************************************** -- Generated on "03/04/2014 15:45:59"-- Vhdl Test Bench template for design : devide---- Simulation tool : ModelSim-Altera (VHDL)--LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY devide_tb ISEND devide_tb;ARCHITECTURE devide_arch OF devide_tb IS-- constants-- signalsSIGNAL clock : STD_LOGIC:='0';SIGNAL done : STD_LOGIC:='0';SIGNAL overflow : STD_LOGIC:='0';SIGNAL q : STD_LOGIC_VECTOR(4 DOWNTO 0):="00000"; SIGNAL r : STD_LOGIC_VECTOR(4 DOWNTO 0):="00000"; SIGNAL reset : STD_LOGIC:='0';SIGNAL start : STD_LOGIC:='0';SIGNAL x : STD_LOGIC_VECTOR(4 DOWNTO 0); SIGNAL y : STD_LOGIC_VECTOR(8 DOWNTO 0); CONSTANT CLK_P : TIME :=10 ns;COMPONENT devidePORT (clock : IN STD_LOGIC;done : OUT STD_LOGIC;overflow : OUT STD_LOGIC;q : OUT STD_LOGIC_VECTOR(4 DOWNTO 0);r : OUT STD_LOGIC_VECTOR(4 DOWNTO 0);reset : IN STD_LOGIC;start : IN STD_LOGIC;x : IN STD_LOGIC_VECTOR(4 DOWNTO 0);y : IN STD_LOGIC_VECTOR(8 DOWNTO 0));END COMPONENT;BEGINi1 : devidePORT MAP (-- list connections between master ports and signalsclock => clock,done => done,overflow => overflow,q => q,r => r,reset => reset,start => start,x => x,y => y);PROCESSBEGINCLOCK<='0';W AIT FOR CLK_P;CLOCK<='1';W AIT FOR CLK_P;END PROCESS;reset <= '0','1' AFTER 10 ns;start <='0','1' AFTER 25 ns;x<="00000","01011"AFTER 60 ns,"00010"AFTER 120 ns;y<="000000000","010010000"AFTER 60 ns,"000001101"AFTER 120 ns; END devide_arch;二.仿真图。

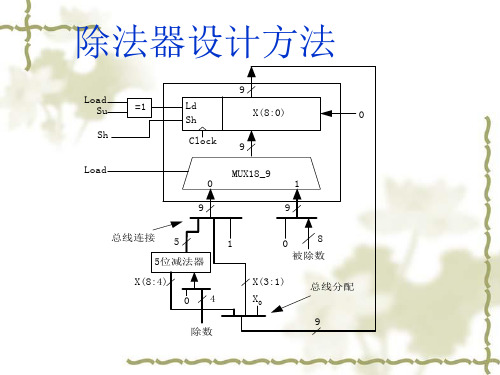

除法器设计方法

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity divider is

Port ( dividend_in : in std_logic_vector(7 downto 0); --被除数

remainder<=dividend(7 downto 4); --分离出余数

quotient<=dividend(3 downto 0); --分离出商

state_graph:process(state,st,c)

--状态控制器

begin

load<='0';overflow<='0';sh<='0';su<='0';

update:process(clk)

--同步数据更新进程

begin

if(clk='1'and clk'event) then

state<=nextstate;

if load='1' then

dividend<='0'÷nd_in;

end if;

if su='1' then

dividend(8 downto 4)<=subout;

divisor : in std_logic_vector(3 downto 0); --除数

st : in std_logic;

--除法启动控制信号

Verilog除法器设计(包含单步设计和流水线设计)

Verilog除法器设计(包含单步设计和流水线设计)1.单步设计:单步设计是最简单的一种除法器设计,其原理是将被除数和除数逐位进行比较和计算,直到得到商和余数。

首先,需要定义Verilog模块的输入和输出端口。

输入包括被除数(dividend)和除数(divisor),输出包括商(quotient)和余数(remainder)。

同时,还需要定义一些辅助信号,如计数器和比较器。

```verilogmodule Dividerinput [N-1:0] dividend,input [N-1:0] divisor,output [N-1:0] quotient,output [N-1:0] remainder```在单步设计中,使用一个循环进行逐位比较和计算,直到得到商和余数。

在每一步循环中,被除数向左移动一位,并与除数进行比较。

如果被除数大于或等于除数,则商的对应位为1,否则为0。

然后,将商的对应位赋值给商,并从被除数中减去除数的相应部分。

最后,余数更新为被除数。

```verilogreg [N-1:0] temp_dividend;reg [N-1:0] temp_remainder;reg [N-1:0] temp_quotient;integer i;temp_dividend = dividend;temp_remainder = {N{1'b0}};temp_quotient = {N{1'b0}};for (i = 0; i < N; i = i+1) begintemp_remainder = temp_dividend;if (temp_remainder >= divisor) begin temp_quotient[i] = 1'b1;temp_dividend = temp_remainder - divisor; endtemp_dividend = temp_dividend << 1;endquotient = temp_quotient;remainder = temp_dividend;endendmodule```以上就是单步设计的Verilog除法器代码。

-阵列除法器的设计1

Xxxxxxxxx课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:阵列除法器的设计院(系):xxxxxxxxx专业:xxxxxxxxx班级:xxxxxxxxx学号:xxxxxxxxxxx姓名:xxxxxxxxxxxxx指导教师:xxxxxxxxxxxx完成日期:xxxxxxxxxxxxxxx沈阳航空工业学院课程设计报告目录第1章总体设计方案 (1)1.1设计原理 (1)1.2设计思路 (3)1.3设计环境 (4)第2章详细设计方案 (7)2.1顶层方案图的设计与实现 (7)2.1.1创建顶层图形设计文件 (7)2.1.2器件的选择与引脚锁定 (8)2.1.3编译、综合、适配 (9)2.2功能模块的设计与实现 (9)2.3仿真调试 (11)第3章编程下载与硬件测试 (14)3.1编程下载 (14)3.2硬件测试及结果分析 (14)参考文献 (16)附录(电路原理图) (17)第1章总体设计方案1.1 设计原理阵列除法器是一种并行运算部件,采用大规模集成电路制造,与早期的串行除法器相比,阵列除法器不仅所需的控制线路少,而且能提供令人满意的高速运算速度。

阵列除法器有多种形式,如不恢复余数阵列除法器、补码阵列除法器等等本实验设计的是加减交替阵列除法器。

原理是利用一个可控加法/减法CAS单元所组成的流水阵列来实现的它有四个输出端和四个输入端。

当输入线P=0时,CAS作加法运算;当P=1时,CAS作减法运算。

逻辑结构图如图1.1所示。

图1.1不恢复余数阵列除法器的逻辑结构图CAS单元的输入与输出的关系可用如下一组逻辑方程来表示:S i=A i⊕(B i⊕P)⊕CC i+1=(A i+C i)·(B i⊕P)+A i C i当P=0时,就是一个全加器,如下式:S i=A i⊕B i⊕C iC i+1=A i B i+B i C i+A i C i当P=1时,则得求差公式:S i=A i⊕B i⊕C iC i+1=A i B i+B i C i+A i C i其中B i=B i⊕1。

EDA四位二进制除法器设计报告

沈阳航空航天大学课程设计(说明书)4位二进制除法器的设计班级 / 学号学生姓名指导教师常丽东沈阳航空航天大学课程名称数字逻辑课程设计院(系)计算机学院专业计算机科学与技术班级学号姓名课程设计题目4位二进制除法器的设计课程设计时间: 2011 年07 月11 日至2011 年07 月24 日课程设计的内容及要求:一、设计说明设计一个4位二进制除法器,可以存贮其商和余数。

电路原理框图如图1所示。

除法器可以利用减法器和寄存器实现。

图1 乘法器原理框图寄存器A、B、C及R分别存放被除数、除数、商及余数。

比较器用来判断“余数”和除数的大小,即比较R寄存器和B寄存器的内容来确定商,用S2表示判断的结果,R≥B,S2=1;R<B,S2=0。

计数器P用来累计运行次数,当P=4时,除法结束。

二、技术指标1.设计4位二进制除法器。

输入数据:被除数X(0000~1111);除数Y(0001~1111)。

输入命令:启动信号S1,高有效。

输出数据:商数C(0000~1111),余数R(R<Y)2.存贮其商和余数。

三、设计要求1.在选择器件时,应考虑成本。

2.根据技术指标通过分析计算确定电路形式和元器件参数。

3.主要器件:(1)74LS74双D触发器;(2)74LS194双向移位的寄存器;(3)74LS283加法器;(4)74LS163计数器;(5)74LS00、74LS04等门电路。

四、实验要求1.根据技术指标制定实验方案;验证所设计的电路。

2.进行实验数据处理和分析。

五、推荐参考资料1.谢自美. 电子线路设计·实验·测试. [M]武汉:华中理工大学出版社,2000年2.阎石. 数字电子技术基础. [M]北京:高等教育出版社,2006年3.付家才. 电子实验与实践. [M]北京:高等教育出版社,2004年六、按照要求撰写课程设计报告指导教师年月日负责教师年月日学生签字年月日成绩评定表一、设计概述要求设计一个四位二进制除法器,要求被除数的最大值位1111,最小值为0000。

计算机组成原理实验报告_3_不恢复余数阵列除法器

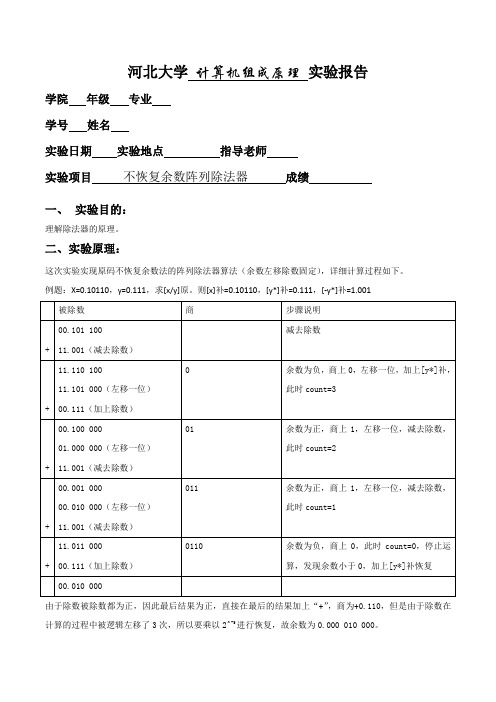

河北大学计算机组成原理实验报告学院年级专业学号姓名实验日期实验地点指导老师实验项目不恢复余数阵列除法器成绩一、实验目的:理解除法器的原理。

二、实验原理:这次实验实现原码不恢复余数法的阵列除法器算法(余数左移除数固定),详细计算过程如下。

例题:X=0.10110,y=0.111,求[x/y]原。

则[x]补=0.10110,[y*]补=0.111,[-y*]补=1.001由于除数被除数都为正,因此最后结果为正,直接在最后的结果加上“+”,商为+0.110,但是由于除数在计算的过程中被逻辑左移了3次,所以要乘以2^-5进行恢复,故余数为0.000 010 000。

原码不恢复余数法原理说明:①符号位单独处理,参加运算的是除数和被除数的绝对值的补码,除数的绝对值用y*表示;②合法的除法运算中,被除数必须小于除数,因此第一次上商肯定是r6=0,否则溢出,停止运算;③原码恢复余数法来源于手算的竖式除法。

若余数为正,表示够减,商上1,左移一位,减去[y*]补,也就是加上[-y*]补;若余数为负,表示不够减,商上0,恢复余数(加上除数),变成减去除数之前的结果,继续左移一位,加上[-y*]补。

④原码不恢复余数法建立在原码恢复余数法的基础之上,假设当前的余数为R。

当余数大于0时,下一步余数是先左移一位再减去除数,即下一步余数应该为R’=2R-y*;当余数小于0时先恢复余数,然后再左移一位再减去除数,假设当前余数为R,那么下一步余数应该为R’=2(R+y*)-y*=2R+y*。

以上两个式子将恢复余数法的步骤定量化了,也就是说,要么左移一位加上y*,要么左移一位减去y*,这就是加减交替的含义。

⑤除数和被除数具有3位尾数的合法的除法,需要逻辑移位3次,上商3+1=4次。

可以设置一个计数器count来控制循环次数,达到3次就停止。

⑥若最后一步为负,表示不够减,商上0,需要恢复余数,即加上除数,否则不需要。

接下来介绍原码不恢复余数阵列除法器①可控加法/减法(CAS)单元原理是利用一个可控加法/减法 CAS 单元所组成的流水阵列来实现的它有四个输出端和四个输入端。

高速硬件除法器设计

高速硬件除法器设计一、实验目得:了解与掌握硬件除法器得结构与工作原理,分析除法器得仿真波形与工作时序。

二、实验原理:除法器算法得思路与手写除法基本一致。

假设除法a/b,a、b就是输入得两个位数都为n得二进制数。

如果位数小于n,可以在位数较少得数得前面添加0来满足这种位数要求。

商与余数就是n位标准矢量类型得二进制数。

在过程中,算法也就是按顺序执行得,但就是综合后系统将会由组合逻辑电路组成,进程中得每一步都与系统构建得不同级别得逻辑电路相对应。

首先,从输入信号中创建变量A与B,A=a,B=b,其中a,b都就是n位二进制数。

如果A大于等于B,则商为1 ,余数为A-B,否则商为0,余数为A。

这就是算法开始得第一次循环,如果小于B,结果商位就是0,A得值不做变化并保留其值。

否则,结果商位为1,则把相减后得余数插入变量A中。

不管比较结果如何,变量A都要右移一位(左边添加0),接着开始下一次循环。

循环n次之后,n位结果赋给商,最后A剩余得值就就是余数。

三、实验任务:用VerilogHDL设计除法器。

除法器得参考程序如下:module DIV16(input CLK,input[15:0] A,B,output reg[15:0] QU,RE);reg[15:0] AT,BT,P,Q; integer i;always (posedge CLK) beginAT=A; BT=B; P=16'H0000;Q=16'H0000;for(i=15;i>=0;i=i-1)beginP={P[14:0],AT[15]};AT={AT[14:0],1'B0}; P=P-BT;if (P[15]==1) begin Q[i]=0; P=P+BT; endelse Q[i]=1;endendalways (*) begin QU=Q;RE=P; endendmodule其中A与B就是除法器输入端得两个16位数据,它们分别为被除数与除数,输出结果分成两部分:QU就是商,RE就是余数。

循环型除法器(精品)

divisor详细设计方案1.循环型除法器简介:补码除法器。

2.循环型除法器规格:八位循环型除法器。

3.实现原理首先我们看小学时代的一个公式:被除数= 除数X商+ 余数应因小学我们没学过负数,这里假定被除数与除数都是自然数。

能不能为负数呢?下面在说。

循环型触发器的原理其实也很简单就是:判断被除数有多少个除数,满足的条件是商小于除数。

如果用C语言写的话Q = 0;while(rmin << dsor){rmin = rmin –dsor;Q ++;}这里它们都是正数哈,则计算的结果:Q是商,rmin 是余数。

但是我们发现,当rmin 和dsor 大小不一样时,计算所花费的步骤将不一样,这里我们要做的是一个,时钟消耗一样的除法器。

假设被除数A,除数B,商Q=Q3 Q2 Q1 Q0,余数R都是四位二进制数真假A-Bx2^3=R >= 0 ? Q3=1 下一操作A=R Q3=0 下一操作A不变A-Bx2^2=R >= 0 ? Q2=1 下一操作A=R Q2=0 下一操作A不变A-Bx2^1=R >= 0 ? Q1=1 下一操作A=R Q1=0 下一操作A不变A-Bx2^0=R>= 0 ? Q0=1 下一操作A=R Q0=0 下一操作A不变例1:A=10,B=3;10 – 3 x 2^3 = -14 < 0 Q3=010 – 3 x 2^2 = -2 < 0 Q2=010 – 3 x 2^1 = 4 > 0 Q1=14 – 3 x 2^0 = 1 > 0 Q0=1则商Q=1100=3 余数R=1;其实就是第一步:判断Q3是否为一,Q3是第四位权重为2^3=8。

为一的话说明A至少有8个B,即A –8B >= 0,并把余数R赋给A进行下一步操作;第二步:判断Q2是否为一,Q2是第四位权重为2^2=4。

为一的话说明A至少有4个B,即A –4B >= 0,并把余数R赋给A进行下一步操作;第三步:判断Q1是否为一,Q1是第四位权重为2^1=2。

有符号位的除法器课程设计报告

有符号位的除法器课程设计报告有符号5位整数除法器设计与制作1.课程设计的性质、目的和任务创新精神和实践能力二者之中,实践能力是基础和根本。

这是由于创新基于实践、源于实践,实践出真知,实践检验真理。

实践活动是创新的源泉,也是人才成长的必由之路。

通过课程设计的锻炼,要求学生掌握电路的一般设计方法,具备初步的独立设计能力,提高综合运用所学的理论知识独立分析和解决问题的能力,培养学生的创新精神。

2. 课程设计基本要求掌握现代大规模集成数字逻辑电路的应用设计方法,进一步掌握电子仪器的正确使用方法,以及掌握利用计算机进行电子设计自动化(EDA)的基本方法。

3. 设计课题要求设计一个两个五位数相除的整数除法器。

用发光二极管显示输入数值,用7段显示器显示结果十进制结果。

除数和被除数分两次输入,在输入除数和被除数时,要求显示十进制输入数据。

采用分时显示方式进行,可参见计算器的显示功能。

4. 设计内容:有符号5位整数除法器设计与制作根据系统设计要求,系统设计采用自顶向下的设计方法。

顶层设计采用原理图设计方式,系统的整体组装设计原理图如下图所示,它由除法器输入模块、除法实现模块和显示译码模块三部分组成。

4.1除法器输入模块本除法器的被除数和除数(有符号5位整数)分两次输入,设置两个标志位A 和B,A和B的初值均为0。

当A=1,B=0时,输入为被除数;当A=1,B=1时,输入为除数。

将被除数和除数分别送至显示电路,以十进制形式显示,同时送入除法实现电路进行除法运算。

输入模块的源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY SHURU1 ISPORT(LOADA,LOADB,CLK:IN STD_LOGIC;DIN:IN STD_LOGIC_VECTOR(4DOWNTO 0);A,B:OUT STD_LOGIC_VECTOR(4 DOWNTO 0));END SHURU1;ARCHITECTURE BEHAVE OF SHURU1 ISBEGINPROCESS(LOADA,LOADB,DIN,CLK)BEGINIF( CLK'EVENT AND CLK='1') THENIF (LOADA='1'AND LOADB='0')THENA<=DIN;END IF;IF (LOADA='1' AND LOADB='1')THENB<=DIN;END IF;END IF;END PROCESS;END BEHAVE;生成模块如图(1-1)所示:如图(1-1)本模块的仿真波形如图(1-2)所示:如图(1-2)4.2 除法实现模块本模块作用是将输入的被除数和除数进行除法运算,输出商和余数。

高速硬件除法器设计

高速硬件除法器设计一、实验目得 :了解与掌握硬件除法器得结构与工作原理,分析除法器得仿真波形与工作时序。

二、实验原理 :除法器算法得思路与手写除法基本一致。

假设除法a/b,a、b 就是输入得两个位数都为 n 得二进制数。

如果位数小于n, 可以在位数较少得数得前面添加0 来满足这种位数要求。

商与余数就是n 位标准矢量类型得二进制数。

在过程中, 算法也就是按顺序执行得 , 但就是综合后系统将会由组合逻辑电路组成, 进程中得每一步都与系统构建得不同级别得逻辑电路相对应。

首先 , 从输入信号中创建变量 A 与 B,A=a,B=b, 其中 a,b 都就是 n 位二进制数。

如果 A 大于等于 B, 则商为 1 , 余数为 A-B, 否则商为 0, 余数为 A。

这就是算法开始得第一次循环, 如果小于 B, 结果商位就是 0,A得值不做变化并保留其值。

否则 , 结果商位为 1, 则把相减后得余数插入变量 A 中。

不管比较结果如何, 变量 A 都要右移一位 ( 左边添加 0),接着开始下一次循环。

循环 n 次之后 ,n 位结果赋给商 , 最后 A剩余得值就就是余数。

三、实验任务 :用VerilogHDL设计除法器。

除法器得参考程序如下:module DIV16(input CLK,input[15:0] A,B,output reg[15:0] QU,RE);reg[15:0] AT,BT,P,Q; integer i;always (posedge CLK) beginAT=A; BT=B; P=16'H0000;Q=16'H0000;for(i=15;i>=0;i=i-1)beginP={P[14:0],AT[15]};AT={AT[14:0],1'B0}; P=P-BT;if (P[15]==1) begin Q[i]=0; P=P+BT; endelse Q[i]=1;endendalways (*) begin QU=Q;RE=P; endendmodule, 输出结果分成两其中 A 与 B 就是除法器输入端得两个 16 位数据 , 它们分别为被除数与除数部分 :QU 就是商 ,RE 就是余数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

设计报告

一.设计名称

运算器的描述与模拟验证(四位原码除法器)

二.设计目的

通过用硬件描述语言(如VHDL或Verilog)描述某个运算器(如ALU、乘法器、除法器等),并进行模拟验证,加深对二进制数运算方法的理解。

三.设计平台:MaxPlusII

四.基本思想

本实验模拟了一个四位带符号二进制整数除法器,被除数为A:A3,A2,A1,A0,除数为B:B3,B2,B1,B0。

其中A3,B3为符号位,算法思想如下:

1)将二个操作数A,B都扩展成7位即:(A3和B3是符号位,不参与具体运算)A:0 0 0 A2 A1 A0

B:0 0 0 B2 B1 B0

2) 将B左移三位得Q:B2 B1 B0 0 0 0

比较A与Q,若A>=Q,商上1,A=A-Q;

否则,商上0,A=A;

B左移一位;

如此循环四次,便得到所要的结果。

五.源代码

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

------------------------------实体定义---------------------------------

entity Div is --除法器实体

port (

A:in STD_LOGIC_VECTOR(3 downto 0); --被除数

B:in STD_LOGIC_VECTOR(3 downto 0); --除数

C:out STD_LOGIC_VECTOR(3 downto 0); --商

);

end Div;

--------------------------------实体的实现-------------------------------------

architecture Div_arch of Div is

--下列信号记录计算过程中的余数的中间结果:

signal remainS0 : STD_LOGIC_VECTOR (5 downto 0);

signal remainS1 : STD_LOGIC_VECTOR (5 downto 0);

signal remainS2 : STD_LOGIC_VECTOR (5 downto 0);

signal remainS3 : STD_LOGIC_VECTOR (5 downto 0);

--运算过程中用于减余数的数:

signal diverS0 : STD_LOGIC_VECTOR (5 downto 0);

signal diverS1 : STD_LOGIC_VECTOR (5 downto 0);

signal diverS2 : STD_LOGIC_VECTOR (5 downto 0); -

signal diverS3 : STD_LOGIC_VECTOR (5 downto 0);

signal Q_TEMP : STD_LOGIC_VECTOR (3 downto 0); --保存商

signal Z0 : STD_LOGIC_VECTOR (2 downto 0); --用于扩展0

signal Z1 : STD_LOGIC_VECTOR (2 downto 0); --用于扩展0

signal ZERO : STD_LOGIC; -置被0除标志位

begin

--扩展被除数与除数:

Z0 <=(others => '0');

Z1 <=(others => '0');

diverS0 <=Z0 & B(2 downto 0);

remainS3 <=Z1& A(2 downto 0);

diver1<=diver0(4 downto 0) & '0'; --由diver0左移1位---〉0 0 B2 B1 B0 0

diver2<=diver1(4 downto 0) & '0'; --由diver0左移1位---〉0 B2 B1 B0 0 0

diver3<=diver2(4 downto 0) & '0'; --由diver0左移1位---〉B2 B1 B0 0 0 0

----------具体运算过程---------

--比较并上商:

Q_TEMP(2) <= '1' when (remainS3 >= diverS2) else '0';

Q_TEMP(1) <= '1' when (remainS2 >= diverS1) else '0';

Q_TEMP(0) <= '1' when (remainS1 >= diverS0) else '0';

--计算余数的中间结果:

remainS2 <= remainS3 - diverS2 when Q_TEMP(2) = '1' else remainS3;

remainS1 <= remainS2 - diverS1 when Q_TEMP(1) = '1' else remainS2;

remainS0 <= remainS1 - diverS0 when Q_TEMP(0) = '1' else remainS1;

Q_TEMP(3) <= A(3) xor B(3); --确定结果的符号位

ZERO <= '1' when B(2 downto 0) = Z1 else '0'; --置被0除标志位

DIVz <= '1' when ZERO = '1' else '0'; --当除数为0时设置标志

C <= (others => '0') when ZERO = '1' else Q_TEMP; --将结果赋予C

end Div_arch;

六.设计心得

1) 通过课程设计,使我对于如何编写VHDL程序有了初步了解,包括基本结构与流程,学会了使用MaxPlusII这个平台,对于除法器,特别是整数除法有了实践上的认识。

2) 在设计的起初阶段,对于MaxPlusII平台的使用花了不少时间,为此参阅了一些书籍,同时在VHDL程序的调试,模拟仿真上也画了不少时间

3)在设计的具体过程中,由于原码整数除法与教材上的小数除法不一致,参考了网上一些资料,并具体分析了一下,得出了前面的算法。