基于FPGA的交织器和解交器的实现

基于FPGA的DVB-T信道内编码和内交织的设计和实现

dg a vdobodat g( V iil ie ra cs n D B—T r t d c d t i )ae i r u e .Mayt e fo t zt n d s nmae ec a n l no n i so pi ai ei k st h n e m mi o g h

后的 A I 现。 SC实 2 D B—T信道 内码 部 分的 F GA实 现 V P

发 射端信 道 内码 部 分 主要 由 内编码 和 内交 织 ( 包

导 频 &T S P

括 比特交 织 、 号 交织 ) 符 组成 , 面分 别 介 绍 各 个模 块 下

的 FG P A实现 。

的卷积 码 , 在非 分级 传输 中 可 以根 据 给 定 的数 据 率 选 择 不 同的误码 保 护 :l 2码率 的主 卷6年 第 0 中 20 7期

图 4 比特 交织 内部 实现框 图 表 l 交织 方 案及移 位寄 存器 的 大小

维普资讯

《 国有线 电视 )0 6 0 ) 中 2 0 ( 7

CH I NA GI A L CABL TV DI T E

⑥

文章 编 号 :0 7— 0 2 20 ) 7— 6 7—0 10 7 2 ( 06 0 0 6 3

・与 ・ 开 应 发用

符 号率 的应用 往 往难 以胜 任 。下 面 用 来 实 现 D B— V T

所 示。 目前 实 现 D B—T 射 端 的 方 案 大 多 是 使 用 V 发

发 射端 的方 案是 将 数 字 上 变 频 集 成 在 一 片 F G 内 , PA 其 优点 是体 积小 , 格 低 , 时 处 理 速 度 较快 , 合 以 价 实 适

1 D B—T发射 端 V

交织/解交织器的FPGA实现

兰 兰 兰 兰 兰

l 1

8 / -

数 据 输 入

BLOCK RAM

一2

据 、 、 J 控制 榆 一

信 号 发生

读 写

写起始控制

读地 址发 生器

图 2 P A 实现 交织 器 的原 理框 图 F G

如果读、 写地址序列具有较强的规律性, 可以用在 F G P A中构造计数器的方式来直接 产生。如交织器的几个参数分别为 : -29 d 、d=【1一 /] 2 ,则可将 l 位地 n 1、I=8 i 29l 8= 8 = 1

2 交织深度固定的码段交织器实现的原理 . 2

图 3为交织器和解交织器实现的基本原理图,其中 I 表示交织深度。由图可见,共 有1 个通道 , 输入数据依次进入第 0 I 通道, 到 — l 并按照各 自通道上的延时规律输出, 交

织器和解交织器相同通道上的延时是互补的,延时之和均为 M× —) ( 1。这样经过发射机 I 交织器数据输出的先后顺序被打乱,再经过接收机解交织器又被重新恢复。 由于交织和解交织要对数据进行有规律的延时处理 ,所以输入数据首先被存入一双 口 R M 中,然后经过一定时延后被读出。此延时由双 口 R M 的读写地址来控制,因 A A

维普资讯

电信技术研究

20 年第 4 06 期

交织/ 解交织器的 F G P A实现

肖永 辉

摘要:交织和解交织是组合信道纠错 系统的一个重要环节,交织器和解交织器的实 现方法有多种 本文利用 Xl x i 公司开发的软件平台,设计比较通用的实现交织器 i n 和解 交织 器的方案 。

数字通信中常用的交织器按交织方式可分为分组交织器和随机交织器两种 ,按交织

基于FPGA的通用调制解调器的设计【文献综述】

毕业论文文献综述电子信息工程基于FPGA的通用调制解调器的设计摘要:随着电子信息技术的高速发展,当今电子系统的设计是以大规模FPGA为物理载体的系统芯片的设计,基于FPGA的片上系统可称为可编程片上系统。

以硬件描述语言为主要设计手段,借助以计算机平台的EDA工具进行的。

调制解调技术是通信系统的灵魂,其性能直接影响到整个系统的通信质量.由于数字技术的大量应用,数字调制解调技术得到了广泛的应用.随着软件无线电思想的发展,将整个系统尽可能地集成于一个芯片的设计方法已经呈现出强大的发展潜力,成为系统设计发展的主要方向.基于这种思想的调制解调器可通过基于FPGA上平台来设计实现。

关键词:FPGA;调制解调;数字调制技术;现代通信原理调制解调器概述调制解调器,是一种计算机硬件,它能把计算机的数字信号翻译成可沿普通电话线传送的脉冲信号,而这些脉冲信号又可被线路另一端的另一个调制解调器接收,并译成计算机可懂的语言。

这一简单过程完成了两台计算机间的通信。

所谓调制,就是把数字信号转换成电话线上传输的模拟信号;解调,即把模拟信号转换成数字信号。

合称调制解调器。

Fpga概述FPGA即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA的使用非常灵活,同一片FPGA通过不同的编程数据可以产生不同的电路功能。

FPGA在通信、数据处理、网络、仪器、工业控制、军事和航空航天等众多领域得到了广泛应用。

随着功耗和成本的进一步降低,FPGA还将进入更多的应用领域。

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个新概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。

基于FPGA的Turbo码交织器的设计与实现

i tr a e s h me i p e e t d,a d t e i lme tt n w t P sg v n n e l v c e s r s n e n h mpe n ai ih F GA i ie .Th i d t n u ig t e s f r e o e smt ai sn h ot e o wa

维普资讯

第2 5卷

第 4期

天

津

工

业

大

学

学

报

V 12 No 4 0. 5 .

Au u t 2 06 g s 0

20 0 6年 8月

J oURNAL oF TI ANJ N I PoL YTECHNI I I C VERS T I Y

o AX + PLUSI ndc ts t tt e c m bn d i e la e a a d a t g ss c sl w i e r rr t fM Ii ia e ha h o ie ntre v rh s m ny a v n a e u h a o bt ro ae,p o r— csigq c l e sn uik y,e s o b dfe n O o a yt e mo iid a d S n. Th r fr h ne l a e shih p a t lv l . e e oe t e i tre v rha g r ci aue ca

要组 成部 分 . 论 研 究 和仿 真 结果 表 明 J 交 织 器 在 理 , T ro 的性 能 中起 到 了关 键 作 用 . 织 器 的设 计 是 ub 码 交

T ro 设 计 中的一个 重要 方 面 , 同交织 器 对于 T r ub 码 不 u*

织器 实 际上是 一个 置换 器 , 最 大程 度 地 置 乱 输 入 信 它

线性同余交织器的FPGA实现

Ab t a t s r c :Th sc p i i eofln a on u nc n e l a e s i t o c d,t e her a ia i n e ba i rncpl i e rc gr

错 。

产 生 的线性 同余 序列 的数值 作为 码元 符号 的地址 , 对 每 组 的 个 码 元 进 行 置 换 , 后 再 顺 序 送 人 信 然 道 。 种用 线性 同余 序列对 码序 列 中的码元 进行 重 这 新 排 序的编 码方 法称 为线性 同余 交织 编码 [ 。 1 ] 对 于 同余方程 ( ) 1 来说 , c和A。 a, 的取值 不 同 , 它产 生 的线 性 同余 序列 的周期 可 能等 于或 小 于

中 图 分 类 号 : N9 1 T 1

文献标识码 : A

Re lz to o ne r Co g u nc nt r e v r wih FPG A a i a i n n Li a n r e e I e l a e t

X FU

( p r me to n o ma i n En i e rn P De a t n f I f r t g n e i g, LA n o ma i n En i e rn i e s t Z e g h u, 5 0 2 Ch n ) o I f r t g n e i g Un v r iy, h n z o 4 0 0 , i a o

,

实 际应 用 中应避 免 - 的情况 发生 。文献 [ ] <L 1

( ) L=p a … 户 , 一 的条 件是 1当 T户 :时

a 一 ( p2 p ) + 1 户1 … 忌

分几种 情况 给 出了 L 一L的条 件 :

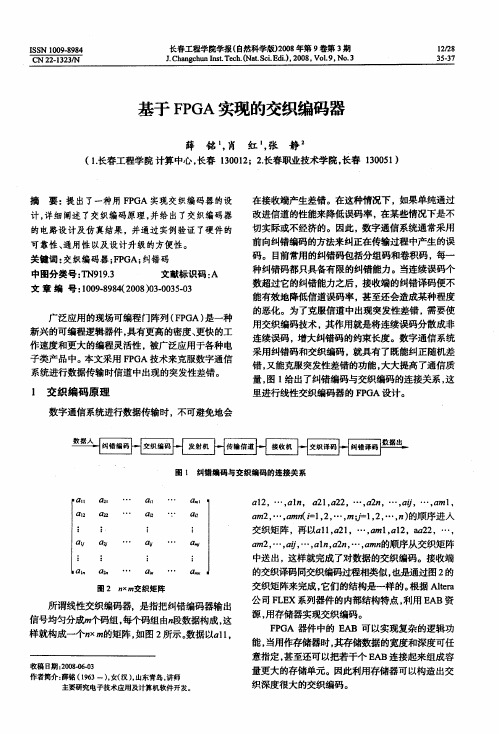

基于FPGA实现的交织编码器

时 钟输 入

双 端 口R M A

时 钟输 出

写地址产生 >

< 读地址产生

顺序地址 从存储 器 中读 出 。

图 3 交 织 编码 器 工 作 原理 方 框 图

2 交 织编 码 器 的 电 路设 计 及 仿 真 结 果

本设计采用 ‘ 序写入 , 顺 乱序读 出” 的方法。 4 图 是 4 4 织编码 器 的电路图 , x交 双端 口 RA 由“ m M l p lm p 宏 模块构 成 。 ' d' a ’

图 3是利 用双 端 口 RA 实 现的交织 编码器工 M

作原理方框图, 由图可看出, 交织编码器设计的关键

所 谓线性交 织编码 器,是指把 纠错编码 器输 出

信号均匀分成 组, 每个码组由嘏 数据构成, 这 样就构成一个r 肌 / 的矩阵 ,  ̄ 如图 2 所示。 数据 以口 l l。

能, 当用作存储器时 , 其存储数据的宽度和深度可任

意指定 , 甚至还可以把若干个 E B连接起来组成容 A 量更大的存储单元。因此利用存储器可以构造出交

中图分 类号 :N993 T 1.

文献标 识码 : A

文 章 编 号 :0 98 8( 0 8 0 .0 50 1 0 .9 4 2 0 )30 3 .3

广泛 应用 的现场可编 程 门阵列 ( P A) 一种 FG 是 新 兴的可 编程逻辑器 件 , 具有更 高的密度 、 更快 的工 作 速度 和更大 的编程灵 活性 。被广泛 应用于各种 电 子类产 品 中。本文采用 F G P A技术来 克服数字通 信

在于 ‘ / 读 写地址” 的产生 。一 般有 2种设计 ‘ / 地 ‘ 写 { 卖

数据通信中交织与解交织的FPGA实现

是很大的,从而带来较大的时延 。 因此 , 在所需的 时延容限范围内,才可以使用交织。 在本课 题 中 , 传输 的数字 信 号进行 B H3 , 对 C ( 1 交织 ( 或称 为交错 )是 在复合 差错 信道 上使用 1 编 码技 术 的一种 简单 而有效 的方 法 。这种 方法 可 2) 格式的编码与解码 。在发送端,信号源 的信 C 进入交织模块, 以将一条突发信道转换成一条独立差 错的信道, 并 号加上子帧同步码进行 B H编码 ,

收稿 日期 :2 0 -6 1. 0 1 -5 0

c mmu ia i nh sb e i r d c dt e l t h u s- r r o nc t o a e nito u e od a wi l ht eb rter D

i lyc a ne.S v rl d r ̄・e eaintemiu s t iig nr a h n 1 e ea de g n rt e a o e l q e uizn l F GA h sb e o ae n ie se nd ti Co iig P a e nc mp rda ddsu s di eal mb n n teFP h GA e ieo d vc fALnj e ip i , tet- iitrev r RA o la y h btnela e l l h a d enela e b s d i 日) tc n lg h v b e n d itrev r ae Ol A e h oo y a e e n d v lp d a du e ii l y t c esul . e eo e n sdi adgt se s c sf l n as m u y

关键词 :交织器;解 交织器;L M;地址序列 ;F GA P P 中图分类号 :T 1.2 N9 7 1 文献标识码 :A

3GPPWCDMA系统Turbo译码中交织解交织的FPGA实现方案

引言1993年C.Berrou等在总结卷积码最大后验概率译码Bahl算法、乘积码和级联码等理论基础上,创造性地提出了“Turbo 码”的编译码新概念。

Turbo码的巧妙之处在于多个子编码器通过交织器进行并行或串行级联(PCC/SCC),然后以类似内燃机引擎废气反复利用的机理进行迭代译码,从而获得具有接近Shannon极限的纠错性能。

在Turbo 码的编译码过程中,正是由于交织器的存在才真正体现了Shannon随机编码的思想精华。

在Turbo译码中反复地利用了附加信息(即外信息)在子译码器间进行多次迭代译码的结果,而这些由各级子译码器产生并反映相应信息位译码判决可信度的附加信息之所以能被相互利用,归功于插在它们之间的交织与解交织器,即它们的“置乱”作用使在同一时刻送入各子编译码器的信息序列码元几乎不相关。

虽然使用Turbo 码能获得极佳的纠错性能,但在许多实际应用场合也给我们带来了极高的编译码复杂度,尤其是Turbo译码更是需要大量的计算,庞大的缓存空间和比较长的译码延迟时间,所有这一切制约着Turbo 码在实时性要求较高的场合中的进一步广泛应用。

在第三代移动通信系统中,Turbo码已经作为一项新技术被应用于快速分组数据的差错控制。

作为其中一大难点的Turbo译码常采用以BCJR算法为基础、具有最小比特差错概率的MAP算法及其改进或简化算法,其译码原理框图如图1所示。

由于译码中需要经历L=4 ̄8次循环迭代,而交织、解交织模块更是需要在其中多次反复调用,所以如何设计一个简单有效的交织、解交织器对节省译码资源和缩短译码时间具有重要意义。

交织与解交织过程根据3GPP WCDMA移动通信系统的协议规范,Turbo 码中最为繁琐同时也是最具特色的是其内部交织器,交织过程可分为如下几个步骤:计算交织矩阵的行数R和列数C设K为输入比特长度,则行数R由以下方法决定:R=5 if 40≤K≤159R=10 if 160≤K≤200 or 481≤K≤530R=20 else而确定矩阵列数C的算法如下:if(481≤K≤530) then p = 53 and C = pelse Find minimum prime p such that (p+1)-K/R≥0,and determine C such that if (p -K/R≥0) then if(p-1-K/R≥0) then C = p -1 else C = p end if else3GPP WCDMA系统Turbo译码中交织解交织的FPGA实现方案FPGA Implementation of Interleaver and Deinrterleaver in Turbo Decoder of 3GPP WCDMA System 解放军信息工程大学通信工程系 马晓军 张水莲 齐赛摘要:本文主要介绍了在第三代移动通信WCDMA系统中Turbo/MAP译码部分交织解交织模块的FPGA实现方案。

数字视频广播系统中交织器与解交织器的FPGA实现

在发射端 ,将要发射的输入数据通过交织器 , 其顺序被打乱 ,使得数据序列 的相关性被大大减 弱, 这样做 的突出优点就是可以很好地降低突发性 错误 的危害。而在接收端通过相反 的处理把数据恢

据延迟下 , 卷积交织所需 的存储器 比矩 阵交织减少 半 , 以一般 采用 卷积 交织 。 所

摘要 : 本文首先介绍了交织解交织的基本原理 , 并针对数字视频广播 系统提 出了优化 方案, 着重 分 析 了其 工作原 理及 各组 成模 块 的具体设 计 , 采用 V r g HL编 写程序 , 后用 F G 以 实现 。 e io D l 最 PA加

关键 词 : 字视 频广播 数 交织 解 交织 FG PA

维普资讯

…

…

…

…

…

…

…

…

…

…

…

・

・

集成电s 用 … … … … … ・ n 照 … … … … … …・ ; 摩

A pplcat o i

数 字视 频 广播 系统 中交织 器 与解 交织器 的 F G P A实现

周 加铳

( 同济大学通信软件及专用集成电路设计 中心 2 09) 002

基于FPGA的Turbo译码交织器设计

硬件 实现 方案 , 交织 算法 的软 件编程和 F G 将 P A内部 的硬 件存储 块相结 合 , 有效地 降低 了译 码器 的硬件

实 现 复 杂 度 ,减 小 了译 码 延 时 ,并 且 给 出 了具 体 的 译 码 器 内 交 织 器 F G 实 现 原 理 框 图 。 PA

关 键 词 :T r o码 ; 交 织 器 ;F G ub P A;译 码 ;延 时 中 图 分 类 号 :T 1 .2 N9 17 文 献 标 识 码 :A

基 于 F G 的 T r o译 码 交 织 器 设 计 P A ub

赵 旦 峰 , 雷李 云 ,罗清 华

( 尔 滨 工 程大 学 信 息 与通 信 工 程 学 院 ,黑龙 江 哈尔 滨 1 0 0 ) 哈 501

摘 要 :介 绍 了 一种 T ro 码 交 织器 的 现 场 可 编 程 门 阵 列 (i dPormm beG t A ry P A ub 译 Fe rga a l ae r ,F G ) l a

图 1 ub ro码 译 码 结 构 图 T

T ro 译码结 构如 图 1 示 ,其 译码结构 主要包括 子译 码器 1 ub 码 所 、交织器 、子译码 器 2和解 交织 器等部 分 ,

收稿 日期 :2 0 .22 ;修回 日期 :2 0 .3 1 0 61 .6 0 70 .6

1 引言

19 9 3年 ,T ro码被提 出【 ,由于其 接近香农 极限 的优异译 码性 能 ,一直是编码界 研究 的热点 。第 三代移 动 ub l j 通信(r G n rt n G 标 准 已采用 T ro 3d e eai ,3 ) o ub 码作 为信道 编码方 案 ,并 给 出了编码 和交织 方案 【。T ro 之所 以 2 ub 码 j

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

专业设计报告基于FPGA的交织器和解交器的实现班级:08集成专业:学院:电子信息工程指导老师:目录一:交织器原理 (2)1实现原理 (2)2纠错原理 (2)二交织器的FPGA实现1 整体结构 (3)2功能分析 (3)3 模块设计 (4)( 1)计数器模块 (4).(2)选择器模块 (5)(3)ROM模块 (6)(4)RAM模块 (7)(5)顶层模块 (9)三设计总结 (14)一:交织器原理1实现原理随着通信技术的发展,对系统要求不断提高,在移动通信领域,由于数字信号在传输途中会随各种干扰,使得信号失真,因此需要利用编码技术来纠正信道中产生的随机错误。

但是,仅利用纠错编码技术,对于传输过程中突发性干扰需要借助很长的码字,这样会很复杂,同时产生很长的延时,。

交织技术作为一项改善通信系统性能的方式,将数据按照一定的规律打乱,把原来聚集的错误分散,使得突发错误变为随机错误,使得突发码字个数在纠错范围内,接收端就可以用较短的码字进行纠错。

交织的过程就是将一个数据系列按一定的条件进行位置从新排布。

其逆过程就是解交。

常用交织器主要有三种:矩阵分组式, 伪随机式, 半伪随机式。

本设计采用矩阵分组式。

矩阵分组式的原理及实现方式如下:假设发送X =(x16....x x x 321)首先将X 送入交织器,此交织器设计为按行取出的4x4的阵列存储器。

送入交织器后,从存储器按行输出,送入突发差错的信道,信道输出在送入反交织器,完成交织与反交织,即按行输入,按列输出。

→按行读出15x x11x7x314x x10x6x213x x9x5x1x12x8x40x :↓按列写入则 交织器的输出为(x0,x4 ,x8,x12,x1,x5,x9,x13,…x15) 2 纠错原理:假设信道产生两个突发性错误,第一个产生与x0到x12,连错4个,第二个产生于x9到x2,连错三个,则此收到的信号为,([x0],[x4] ,[x8],[x12],x1,x5,[x9],[x13],[x2],x6,x10,x14,x3,x7,x11,x15)(加[]的为错误信号)经过交织去交矩阵输出为([x0],x1,[x2],x3,[x4],x5,x6,x7,[x8],x9,x10,x11,[x12],[x13],x14,x15)可以看到原来的四连错和三连错变成了随机性独立差错。

二交织器的FPGA实现1 整体结构交织器总是按顺序写入数据,然后按交织地址读出数据。

解交的过程与此过程相反,按解交地址写入数据,再按顺序读出数据就可以了。

因此交织器和解交器可以按相似电路完成。

2功能分析交织器要写入数据,将数据存储起来,并读出,需要ram模块。

交织地址是固定的交织方式,可以用rom将地址存储起来,按顺序读取rom存储的ram 地址就可以完成交织。

控制部分有计数器,选择器组成,完成对ram读写的控制。

电路框图如下计数器产生顺序地址,数据选择器起地址控制作用,当需要顺序地址时,直接由计数器输到地址总线,当需要交织地址时,计数器的输出送到ROM地址总线,再将ROM读出的交织地址送出。

3 模块设计(1)计数器模块计数器的作用是,为选择器提供顺序地址,为rom提供地址 VHDL描述如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;entity countern isgeneric(n:integer:=16);port(clr,ena,clk:in std_logic;q:buffer integer range 0 to n-1;cout:out std_logic);end countern;architecture rtl of countern isbeginprocess (clk,clr)beginif clr='1'thenq<=0;elseif clk='1' and clk'event thenif ena='1' thenif q=q'high thenq<=0;else q<=q+1;end if;end if;end if;end if;if q=q'high thencout<='1';elsecout<='0';end if ;end process;end rtl;仿真波形如下:(2)选择器模块VHDL描述如下library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;entity mux2 isgeneric (n:integer:=16);port (d0:in std_logic_vector(7 downto 0);d1: in integer range 0 to n-1;sel:in std_logic;yout: out std_logic_vector(7 downto 0));end mux2;architecture if_march of mux2 isbeginprocess(d0,d1,sel)beginif(sel='1') thenyout<=conv_std_logic_vector(d1,8);elseyout<=d0;end if;end process;end if_march;选择器仿真波形如下图:(3)ROM模块library ieee;use ieee.std_logic_1164.all;entity rom_16_8 isgeneric(n:integer:=16);port(addr: in integer range 0 to n-1;clk: in std_logic;data: out std_logic_vector(7 downto 0));end rom_16_8;architecture rtl of rom_16_8 issubtype rom_word is std_logic_vector(7 downto 0);type rom_table is array(0 to 15) of rom_word;constant rom :rom_table:=rom_table'(rom_word'("00000000"),rom_word'("00000100"),rom_word'("00001000"),rom_word'("00001100"),rom_word'("00000001"),rom_word'("00000101"),rom_word'("00001001"),rom_word'("00001101"),rom_word'("00000010"),rom_word'("00000110"),rom_word'("00001010"),rom_word'("00001110"),rom_word'("00000011"),rom_word'("00000111"),rom_word'("00001011"),rom_word'("00001111"));begin process(clk)beginif clk'event and clk='1' thendata<=rom(addr);end if;end process;end rtl;ROM模块仿真波形图(4)RAM模块library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity ram_16_8 isport (ad:in std_logic_vector(7 downto 0);clk :in std_logic ;di:in std_logic_vector(7 downto 0);do:out std_logic_vector(7 downto 0);wr_en: in std_logic:='0';rd_en: in std_logic :='0');end ram_16_8;architecture rtl of ram_16_8 issubtype ram_word is std_logic_vector(7 downto 0); type ram_table is array (0 to 15) of ram_word;signal ram:ram_table:=ram_table'(ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"));begin process(clk)beginif clk'event and clk='1'thenif rd_en='1'thendo<=ram(conv_integer(ad));end if ;if wr_en='1' thenram(conv_integer(ad))<=di;end if ;end if ;end process;end rtl;(5)顶层模块library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;entity top isgeneric(n:integer:=16);port (clk: in std_logic;clr: in std_logic;ena :in std_logic;di: in std_logic_vector(7 downto 0);do : out std_logic_vector(7 downto 0));end top;architecture rtl of top iscomponent counternport(clr,ena,clk:in std_logic;q:buffer integer range 0 to n-1:=0;cout: out std_logic);end component;component rom_16_8port(addr: in integer range 0 to n-1;clk: in std_logic;data: out std_logic_vector(7 downto 0));end component;component mux2port(d0:in std_logic_vector(7 downto 0);d1: in integer range 0 to n-1;sel: in std_logic;yout:out std_logic_vector(7 downto 0)); end component;component ram_16_8port( ad:in std_logic_vector(7 downto 0); clk:in std_logic;di:in std_logic_vector(7 downto 0);do:out std_logic_vector(7 downto 0);wr_en: in std_logic:='0';rd_en:in std_logic:='0');end component;signal qs:integer range 0 to n-1:=0;signal ds:std_logic_vector(7 downto 0); signal ys:std_logic_vector(7 downto 0); signal cout: std_logic;signal wr_en:std_logic:='0';signal rd_en:std_logic:='0';signal sel:std_logic:='1';beginct:counternport map (clk=>clk,clr=>clr,ena=>ena,cout=>cout,q=>qs);rom:rom_16_8port map(clk=>clk,addr=>qs,data=>ds);mux:mux2port map (d1=>qs,d0=>ds,sel=>sel,yout=>ys);ram:ram_16_8port map(clk=>clk,do=>do,di=>di,wr_en=>wr_en,rd_en=>rd_en,ad=>ys);process(cout)beginif cout'event and cout='0' thensel <=not sel;end if ;if sel='1' thenwr_en<='1';elserd_en<='1';end if ;end process;end rtl;从图形可以看出交织器把顺序的信号12345…交织为 0 4 8 12 1 5 9 13…交织功能实现解交织器的实现其中rom,ram ,计数器都一样,只是在选择器时稍作变化。