洗衣机定时控制器课程设计参考

数电课程设计 洗衣机定时控制器

数字电子技术课程设计报告题目:洗衣机定时控制器班级:洗衣机定时控制器一、设计任务及要求:1.设计脉冲信号源(秒脉冲)2.至少能显示 1:00—12:593.具备校时功能4.附加特殊功能设计(报时功能)二、方案设计与论证:所谓数字钟,是指利用电子电路构成的计时器。

相对机械钟而言,数字钟能达到准确计时,并显示小时、分、秒,同时能对该钟进行调整。

在此基础上,还能够实现整点报时的功能。

其中有振荡器,分频器,校时电路,报时电路,计数器,译码器和显示器七部分组成。

振荡器和分频器组成标准秒信号发生器,不同进制的计数器产生计数,译码器和显示器进行显示,通过校时电路实现对时,分的校准方案一:使用 COMS 数字芯片,使用专用时钟芯片,使用十进制计数器,以及使用万用板焊接电路,分模块搭建电路,使用专用电源供电。

优点:计时准确,反应灵敏,思路简单,性能稳定,成功率高,便于调试。

缺点:驱动能力弱,走线复杂,对数电知识的利用并不充分。

方案二:使用 TTL 数字芯片,使用 74LS93 多进制计数器,用 555 定时器自建时钟模块,使用 USB 供电,使用 PCB 制板。

优点:电路驱动能力强,不必考虑输入脚悬空的问题,充分利用了模电、数电的知识,外观漂亮,供电方便。

缺点:整体布局比较麻烦,排查错误比较麻烦,时钟性能一般。

在比较两个方案的优缺点后,选择了第二个方案,进行由上而下层次化的设计,先定义和规定各个模块的结构,再对模块内部进行详细设计。

通过仿真,原理图设计,PCB 制作,分步骤调试,来解决方案二的不足。

使做出来的效果又好,又能充分利用学过的数电知识。

可以体现数电课设的真正内涵。

我们设计的电子钟,严格按照设计要求,具有整点报时,调时,调分等功能;特别是,我们的调时调分开关,都加上了消抖电路,使用了模拟电路消抖,省去了一些数字芯片,这些都是我们组,区别于其他组的地方。

设计原理及框图定时控制器实际上是一个对标准频率进行计数的计数电路,由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的 1kHZ 时间信号必须做到准确稳定。

自动洗衣机控制器ddpp课程设计

电子科技大学数字设计原理和实践课程设计报告题目:自动洗衣机控制器姓名:魏玉峰学号:29一、任务和要求设计内容:1)进行需求分析,确定总体框架;2 )画出逻辑电路图;3 )对设计电路进行仿真;设计要求:假设自动洗衣机的定时操作顺序是,洗衣10min,排水2min,脱水3mi n,然后停止。

设计出这个自动洗衣机的控制器。

设计提示:本设计有4个状态,分别为初始状、洗衣系统、排水系统、和脱水状态。

当有复位信号时,系统进入循环控制状态,依次执行操作,可从信号灯观察到所处状态。

二、设计思路的介绍分析:洗衣机开机后,自动进入循环状态,分别进行洗衣10min,排水2min,脱水3min的操作,然后回到待机状态。

任意期间输入复位信号都会重新开始进入循环控制状态。

LED旨示灯和当前操作对应,处于发光状态。

由以上要求可知,所有状态共4种,分别为初始状态、洗衣状态、排水状态、和脱水状态,即用1个74163计时器,输出的状态和上面一一对应,具体见下表:0000 待机0001 洗衣状态0010 洗衣状态0011 洗衣状态0100 洗衣状态0101 洗衣状态0110 洗衣状态0111 洗衣状态1000 洗衣状态1001 洗衣状态1010 洗衣状态1011 排水状态1100 排水状态1101 脱水状态1110 脱水状态1111 脱水状态故可根据上表分别选择输出时的74163对应输出接口三、总体方案的选择经过多次选择和比较最终选择74163,7400来完成电路实现计时功能。

将时钟信号设为1/60hz,即每分钟一个上升沿。

电路中采用16个4输入和非门,1个12输入和非门,1个2输入和非门,1个3输入和非门。

把每一个4输入和非门的四个角分别于74163的Qd、Qc、Qb、Qa相连,而每一个4输入和非门分别对应一个74163的输出状态。

当所输出状态对应了洗衣机状态时,总输出状态将产生变化,从而进行当前操作,具体电路图设计如下:Clk为时钟信号1/60hzIn put为开关按钮Clr为复位按钮Sta ndb y代表当前为待机状态Washi ng代表当前为洗衣状态Drain age代表当前为排水状态Dehydration代表当前为洗衣状态四、Verilog HDL module try3(clk,in put,clr,Sta ndby,Wash ing,Drain age, 代码Dehydratio n);in put clk;in put in put;in put clr;output Stan dby;output Washi ngoutput Drain age; wire SYNTHESIZED_WIRE_78; output Dehydrati on; wire SYNTHESIZED_WIRE_84;wire SYNTHESIZED_WIRE_114; wire SYNTHESIZED_WIRE_85;wire SYNTHESIZED_WIRE_115; wire SYNTHESIZED_WIRE_86;wire SYNTHESIZED_WIRE_2; wire SYNTHESIZED_WIRE_88;wire SYNTHESIZED_WIRE_116; wire SYNTHESIZED_WIRE_90;wire SYNTHESIZED_WIRE_117; wire SYNTHESIZED_WIRE_91;wire SYNTHESIZED_WIRE_5; wire SYNTHESIZED_WIRE_118; wire SYNTHESIZED_WIRE_6; wire SYNTHESIZED_WIRE_95;wire SYNTHESIZED_WIRE_7; wire SYNTHESIZED_WIRE_96;wire SYNTHESIZED_WIRE_8; wire SYNTHESIZED_WIRE_97;wire SYNTHESIZED_WIRE_9; wire SYNTHESIZED_WIRE_98;wire SYNTHESIZED_WIRE_10; wire SYNTHESIZED_WIRE_99;wire SYNTHESIZED_WIRE_12; wire SYNTHESIZED_WIRE_100; wire SYNTHESIZED_WIRE_13; wire SYNTHESIZED_WIRE_101; wire SYNTHESIZED_WIRE_16; wire SYNTHESIZED_WIRE_102; wire SYNTHESIZED_WIRE_17; wire SYNTHESIZED_WIRE_103; wire SYNTHESIZED_WIRE_18; wire SYNTHESIZED_WIRE_104; wire SYNTHESIZED_WIRE_23; wire SYNTHESIZED_WIRE_105; wire SYNTHESIZED_WIRE_24; wire SYNTHESIZED_WIRE_106; wire SYNTHESIZED_WIRE_25; wire SYNTHESIZED_WIRE_107; wire SYNTHESIZED_WIRE_34; wire SYNTHESIZED_WIRE_108; wire SYNTHESIZED_WIRE_36; wire SYNTHESIZED_WIRE_112; wire SYNTHESIZED_WIRE_38; wire SYNTHESIZED_WIRE_113; wire SYNTHESIZED_WIRE_39; \74163 b2v_i nst(wire SYNTHESIZED_WIRE_42; .ENT(input),wire SYNTHESIZED_WIRE_43; .CLRN(clr),wire SYNTHESIZED_WIRE_44; .CLK(clk),wire SYNTHESIZED_WIRE_51; .ENP(input),wire SYNTHESIZED_WIRE_53; .LDN(input),•QA(SYNTHESIZED_WIRE_115),•QB(SYNTHESIZED_WIRE_116),•QC(SYNTHESIZED_WIRE_117),.QD(SYNTHESIZED_WIRE_114));assign SYNTHESIZED WIRE 105 = ~(SYNTHESIZED WIRE 114 & SYNTHESIZED WIRE 115 & SYNTHESIZED_WIRE_2 & SYNTHESIZED_WIRE_116);assig n SYNTHESIZED_WIRE_2 = ~SYNTHESIZED_WIRE_117;assign SYNTHESIZED WIRE 113 = ~(SYNTHESIZED WIRE 5 & SYNTHESIZED WIRE 6 & SYNTHESIZED_WIRE_7 & SYNTHESIZED_WIRE_8);assign SYNTHESIZED WIRE 100 = ~(SYNTHESIZED WIRE 9 & SYNTHESIZED WIRE 10 & SYNTHESIZED_WIRE_117 & SYNTHESIZED_WIRE_12);assign SYNTHESIZED WIRE 102 = ~(SYNTHESIZED WIRE 13 & SYNTHESIZED WIRE 115 & SYNTHESIZED_WIRE_117 & SYNTHESIZED_WIRE_16);assign SYNTHESIZED WIRE 101 = -(SYNTHESIZED WIRE 17 & SYNTHESIZED WIRE 18 & SYNTHESIZED_WIRE_117 & SYNTHESIZED_WIRE_116);assign SYNTHESIZED WIRE 118 = ~(SYNTHESIZED WIRE 114 & SYNTHESIZED WIRE 115 & SYNTHESIZED_WIRE_23 & SYNTHESIZED_WIRE_24);assign SYNTHESIZED WIRE 103 = ~(SYNTHESIZED WIRE 25 & SYNTHESIZED WIRE 115 & SYNTHESIZED_WIRE_117 & SYNTHESIZED_WIRE_116);assign SYNTHESIZED WIRE 108 = ~(SYNTHESIZED WIRE 114 & SYNTHESIZED WIRE 115 & SYNTHESIZED_WIRE_117 & SYNTHESIZED_WIRE_116);assign SYNTHESIZED WIRE 104 = ~(SYNTHESIZED WIRE 114 & SYNTHESIZED WIRE 34 & SYNTHESIZED_WIRE_117 & SYNTHESIZED_WIRE_36);assign SYNTHESIZED WIRE 96 = ~(SYNTHESIZED WIRE 114 & SYNTHESIZED WIRE 38 & SYNTHESIZED_WIRE_39 & SYNTHESIZED_WIRE_116);assign SYNTHESIZED WIRE 95 = ~(SYNTHESIZED WIRE 114 & SYNTHESIZED WIRE 42 & SYNTHESIZED_WIRE_43 & SYNTHESIZED_WIRE_44);assig n SYNTHESIZED_WIRE_5 = ~SYNTHESIZED_WIRE_114;assig n SYNTHESIZED_WIRE_7 = ~SYNTHESIZED_WIRE_117;assig n SYNTHESIZED_WIRE_8 = ~SYNTHESIZED_WIRE_116;assig n SYNTHESIZED_WIRE_6 = ~SYNTHESIZED_WIRE_115;assig n SYNTHESIZED_WIRE_90 = ~SYNTHESIZED_WIRE_117;assig n SYNTHESIZED_WIRE_91 = ~SYNTHESIZED_WIRE_116;assign SYNTHESIZED WIRE 97 = ~(SYNTHESIZED WIRE 51 & SYNTHESIZED WIRE 115 & SYNTHESIZED_WIRE_53 & SYNTHESIZED_WIRE_116);assig n SYNTHESIZED_WIRE_88 = ~SYNTHESIZED_WIRE_114;assig n SYNTHESIZED_WIRE_84 = ~SYNTHESIZED_WIRE_114;assig n SYNTHESIZED_WIRE_86 = ~SYNTHESIZED_WIRE_117;assig n SYNTHESIZED_WIRE_85 = ~SYNTHESIZED_WIRE_115;assig n SYNTHESIZED_WIRE_51 = ~SYNTHESIZED_WIRE_114;assig n SYNTHESIZED_WIRE_53 = ~SYNTHESIZED_WIRE_117;assig n SYNTHESIZED_WIRE_9 = ~SYNTHESIZED_WIRE_114;assig n SYNTHESIZED_WIRE_12 = ~SYNTHESIZED_WIRE_116;assig n SYNTHESIZED_WIRE_10 = ~SYNTHESIZED_WIRE_115;assig n SYNTHESIZED_WIRE_13 = ~SYNTHESIZED_WIRE_114;assig n SYNTHESIZED_WIRE_16 = ~SYNTHESIZED_WIRE_116;assig n SYNTHESIZED_WIRE_17 = ~SYNTHESIZED_WIRE_114;assig n SYNTHESIZED_WIRE_18 = ~SYNTHESIZED_WIRE_115;assig n SYNTHESIZED_WIRE_25 = ~SYNTHESIZED_WIRE_114;assig n SYNTHESIZED_WIRE_43 = ~SYNTHESIZED_WIRE_117;assig n SYNTHESIZED_WIRE_44 = ~SYNTHESIZED_WIRE_116;assig n SYNTHESIZED_WIRE_42 = ~SYNTHESIZED_WIRE_115;assig n SYNTHESIZED_WIRE_23 = ~SYNTHESIZED_WIRE_117;assig n SYNTHESIZED_WIRE_112 = ~SYNTHESIZED_WIRE_116;assig n SYNTHESIZED_WIRE_24 = ~SYNTHESIZED_WIRE_116;assig n SYNTHESIZED_WIRE_39 = ~SYNTHESIZED_WIRE_117;assig n SYNTHESIZED_WIRE_38 = ~SYNTHESIZED_WIRE_115;assign SYNTHESIZED WIRE 107 = -(SYNTHESIZED WIRE 114 & SYNTHESIZED WIRE 78 & SYNTHESIZED_WIRE_117 & SYNTHESIZED_WIRE_116);assig n SYNTHESIZED_WIRE_36 = ~SYNTHESIZED_WIRE_116; assig n SYNTHESIZED_WIRE_34 = ~SYNTHESIZED_WIRE_115; assig n SYNTHESIZED_WIRE_78 = ~SYNTHESIZED_WIRE_115; assignSYNTHESIZED WIRE 98 = -(SYNTHESIZED WIRE 84 & SYNTHESIZED WIRE 85 &SYNTHESIZED_WIRE_86 & SYNTHESIZED_WIRE_116);assign SYNTHESIZED WIRE 99 = -(SYNTHESIZED WIRE 88 & SYNTHESIZED WIRE 115 & SYNTHESIZED_WIRE_90 & SYNTHESIZED_WIRE_91);assig n Washi ng = ~(SYNTHESIZED_WIRE_118 & SYNTHESIZED_WIRE_118 & SYNTHESIZED_WIRE_118 & SYNTHESIZED_WIRE_95 & SYNTHESIZED_WIRE_96 & SYNTHESIZED_WIRE_97 & SYNTHESIZED_WIRE_98 & SYNTHESIZED_WIRE_99 & SYNTHESIZED_WIRE_100 & SYNTHESIZED_WIRE_101 & SYNTHESIZED_WIRE_102 & SYNTHESIZED_WIRE_103);assig n Drai nage = ~(SYNTHESIZED_WIRE_104 & SYNTHESIZED_WIRE_105); assig n Dehydratio n = ~(SYNTHESIZED_WIRE_106 & SYNTHESIZED_WIRE_107 & SYNTHESIZED_WIRE_108);assign SYNTHESIZED WIRE 106 = ~(SYNTHESIZED WIRE 114 & SYNTHESIZED WIRE 115 & SYNTHESIZED_WIRE_117 & SYNTHESIZED_WIRE_112); assig n Sta ndby = ~SYNTHESIZED_WIRE_113; en dmodule五、仿真结果截图六、 结果分析当给入信号后,洗衣依次进入洗衣状态,排水状态,脱水状态,最后回到待 机状态,当有复位信号CLR=O 输入时,系统进入循环控制状态。

洗衣机控制器课程设计

摘要洗衣机控制器可以控制洗衣机的工作状态,同时对其状态加以显示,可以手动设置工作时间,在洗衣机工作时还可以加以控制,使其在工作和暂停之间进行进行转换。

该控制器启动后,先正转20秒,再暂停10秒,接着反转20秒,再停止,这一功能可以通过计数器的减数功能完成,用四个74LS194即可以实现分秒计数,同时用555定时器组成的多谐振荡器作脉冲产生器接入计数器来实现计数,用LED指示电机转动状态,当设置的时间到时,产生跳变脉冲,触发555定时器组成的单稳态触发器带动蜂鸣器工作,一段时间后停止响动。

本设计电路用Multisim软件进行仿真,它包含了电路原理图的图形输入、电路硬件描述语言输入方式,具有丰富的仿真分析能力。

Multisim 10是该软件比较新的版本。

本次课程设计主要要求掌握原理图的设计、仿真、安装调试。

关键词:触发器多谢振荡器仿真 MultisimABSTRACTThe washing machine controller can control the working status, and its status, can be manually set time, work in the washing machine work also can be controlled in the work and suspended between the switches. This controller is started, the first 20 seconds, then suspended for 10 seconds, then reverse 20 seconds, then stop, this function can be observed by the counter with complete functions, which can be realized 74LS194 four seconds count, and with more than composed of 555 timing for pulse generator harmonic oscillator access to count, counter LED indicator when setting, motor rotation of time, jumping, triggering pulse 555 timing single steady-state flip-flop, drive buzzer after a period of time to stop shake.This circuit design software simulation with Multisim, it contains the circuit principle diagram of graphic, circuit hardware description language input mode, has the rich simulation analysis ability. Is this software is Multisim 10 new version. This course design main requiring schematic diagram of the design, installation, commissioning and simulation.Keywords: trigger thanks oscillator Multisim simulation目录1 设计任务与要求 (1)1.1 设计任务 (1)1.2 设计要求 (1)2 原理图设计 (2)2.1 总体设计概述 (2)2.1.1 设计总体思路 (2)2.1.2 基本原理 (2)2.1.3系统设计框图 (3)2.2 单元电路设计 (3)2.2.1分、秒计数器的设计 (3)2.2.2秒脉冲发生器 (6)2.2.3循环控制电路 (7)2.2.4单稳态延时电路 (10)2.3总电路设计 (11)3 Multism软件仿真 (14)3.1 Multism软件简介 (14)3.2 Multism软件的仿真应用 (15)3.2.1秒脉冲发生电路的仿真 (15)3.2.2计数器及循环电路的仿真 (15)3.2.3单稳态延时电路的仿真 (17)4 心得体会 (18)参考文献 (19)附录 (20)实物制作 (21)1 设计任务与要求1.1 设计任务设计并制作一个电子定时器,用以控制洗衣机电机的运转,要求如下:(1).洗衣机的工作顺序;启动——>正转20s ——> 暂行10s——> 反转20s—— >暂行10 s——>停止(2). 用4个LED模拟洗衣机的动作状态:LED1~LED4右移循环点亮表示正转,LED1~LED4左移循环点亮表示反转,LED1~LED4同时闪烁点亮表示暂停,全灭为停止。

洗衣机定时控制器课程设计参考分析

NPN)或者两个或门就可以实现该功能。还有我们可以利用分计数的

端来进行外部置数,当把它们各接到一个低触发(平时保持高电平,外部给一个力就输入一个

就可以实现从0-9的数字输入。

电机正反转即停止控制电路

60秒到40

40到30秒内是第二个灯亮。在30到10秒内是第三个灯亮,然后剩下的十

20s——>,,——>时间到停止”设计一个定时器控制洗衣机的电机的运转,由其转,传反转及暂停时

60s,并且呈现周期循环,知道时间到停止为止。我们可以利用计

60s的计数,及需要一个秒计数器,并且利用洗衣机的电机工作状态转换的时间来

如此则需要为计数器设置一个合适的脉冲,设计中的秒计数器所需的脉冲必为1HZ脉冲。对于

端作为脉冲的输入,计数器的进制设置依靠其数入端D3、D2、D1、D0的置数。

:LED灯的点亮与熄灭指示显示主要是取决于192的输出低三位,根据输入与输出的 10 关系,

:利用UP端的特性,为其可控置入低电平以改变十分位和个分为的数字显示,即实现置数功能。

就可以实现置数功能的准确性,实现置数

蜂鸣器部分

当电动机的状态发生改变时即LED灯发生改变时,蜂鸣器会接受到一个脉冲,发出响声。

原理总图

仿真结果

分析与改进

问题分析

:计数器的进制设置于计数器之间的连接

:LED指示灯的状态指示

:工作后的停止设置

:分秒置数开关的设定

:清零开关的设置

.2改进措施

:减法计数器的BO平常位高电平,有借位时为低电平。利用此特性,将其连接在高位计数器的

可是做着做着就有些烦躁了。特别是在遇到问题而无法解决的时候,

Verilog课程设计_洗衣机设计电路

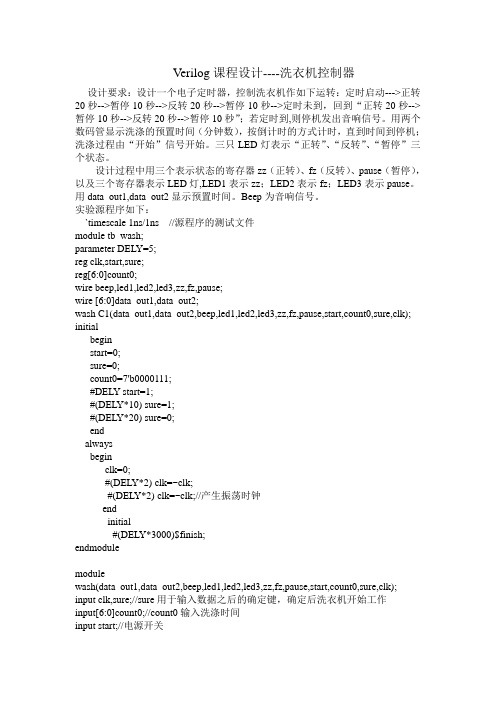

Verilog课程设计----洗衣机控制器设计要求:设计一个电子定时器,控制洗衣机作如下运转:定时启动--->正转20秒-->暂停10秒-->反转20秒-->暂停10秒-->定时未到,回到“正转20秒-->暂停10秒-->反转20秒-->暂停10秒”;若定时到,则停机发出音响信号。

用两个数码管显示洗涤的预置时间(分钟数),按倒计时的方式计时,直到时间到停机;洗涤过程由“开始”信号开始。

三只LED灯表示“正转”、“反转”、“暂停”三个状态。

设计过程中用三个表示状态的寄存器zz(正转)、fz(反转)、pause(暂停),以及三个寄存器表示LED灯,LED1表示zz;LED2表示fz;LED3表示pause。

用data_out1,data_out2显示预置时间。

Beep为音响信号。

实验源程序如下:`timescale 1ns/1ns //源程序的测试文件module tb_wash;parameter DELY=5;reg clk,start,sure;reg[6:0]count0;wire beep,led1,led2,led3,zz,fz,pause;wire [6:0]data_out1,data_out2;wash C1(data_out1,data_out2,beep,led1,led2,led3,zz,fz,pause,start,count0,sure,clk); initialbeginstart=0;sure=0;count0=7'b0000111;#DELY start=1;#(DELY*10) sure=1;#(DELY*20) sure=0;endalwaysbeginclk=0;#(DELY*2) clk=~clk;#(DELY*2) clk=~clk;//产生振荡时钟endinitial#(DELY*3000)$finish;endmodulemodulewash(data_out1,data_out2,beep,led1,led2,led3,zz,fz,pause,start,count0,sure,clk); input clk,sure;//sure用于输入数据之后的确定键,确定后洗衣机开始工作input[6:0]count0;//count0输入洗涤时间input start;//电源开关output [6:0]data_out1,data_out2;//数码管时间输出reg [6:0]data_out1,data_out2;output zz,fz,pause;reg zz,fz,pause;output led1,led2,led3;reg led1,led2,led3;reg[5:0]counts;output beep; //音响reg beep;reg[6:0]count;//计数分钟reg[3:0]countm;//计数秒wire [3:0]bcd_1;reg [3:0]bcd_2;reg signal;//用于控制音响信号initial begindata_out1=7'b0;data_out2=7'b0;counts<=6'b0;countm<=4'b0;count<=count0;bcd_2<=4'b0;zz<=0;fz<=0;pause<=0;beep<=0;led1<=0;led2<=0;led3<=0;signal<=0;endalways@(posedge clk)beginif(sure==1)beginsignal<=1;count<=count0;//对count赋初值endif((count>0)&&(start==1)&&(signal==1))beginif(counts==6'b111100)//60begincounts<=6'b1;count<=count-1;endelsebegincounts<=counts+1'b1;if(counts<=5'b10100) //20beginzz<=1;fz<=0;pause<=0;led1<=1;led2<=0;led3<=0;endelseif(counts<=6'b11110|counts>6'b110010&&counts<=6'b111011)//30 50~59 beginpause<=1;zz<=0;fz<=0;led2<=1;led1<=0; led3<=0;endelsebeginfz<=1;zz<=0;pause<=0;led3<=1;led1<=0; led2<=0;endendendif(signal==1&&count==0)//控制洗涤结束时音响响的时间beginif(countm==4'b1001)beep<=0;elsebegincountm<=countm+1;beep<=1;led2=0;pause=0;endendend//always//show the numberalways@(count)beginif(count>=7'd90)bcd_2<=4'd9;else if(count>=7'd80)bcd_2<=4'd8;else if(count>=7'd70)bcd_2<=4'd7;else if(count>=7'd60)bcd_2<=4'd6;else if(count>=7'd50)bcd_2<=4'd5;else if(count>=7'd40)bcd_2<=4'd4;else if(count>=7'd30)bcd_2<=4'd3;else if(count>=7'd20)bcd_2<=4'd2;else if(count>=7'd10)bcd_2<=4'd1;elsebcd_2<=4'd0;endassign bcd_1=count-bcd_2*4'd10; always@(bcd_1)//数码管个位的显示begincase (bcd_1)4'b0000:data_out1=7'b0111111;//04'b0001:data_out1=7'b0000110;4'b0010:data_out1=7'b1011011;4'b0011:data_out1=7'b1001111;4'b0100:data_out1=7'b1100110;4'b0101:data_out1=7'b1101101;4'b0110:data_out1=7'b1111100;4'b0111:data_out1=7'b0000111;4'b1000:data_out1=7'b1111111;4'b1001:data_out1=7'b1100111;default:data_out1=7'b0000000;endcaseendalways@(bcd_2)//数码管十位的显示begincase (bcd_2)4'b0000:data_out2=7'b0111111;//04'b0001:data_out2=7'b0000110;4'b0010:data_out2=7'b1011011;4'b0011:data_out2=7'b1001111;4'b0100:data_out2=7'b1100110;4'b0101:data_out2=7'b1101101;4'b0110:data_out2=7'b1111100;4'b0111:data_out2=7'b0000111;4'b1000:data_out2=7'b1111111;4'b1001:data_out2=7'b1100111;default:data_out2=8'b0000000;endcaseendendmodule程序编号之后在linux系统的nclaunch里面仿真出来波形如下:波形符合设计的要求。

eda技术课程设计洗衣机控制器

课程EDA技术课程设计题目洗衣机控制器专业电子信息工程姓名主要内容、基本要求、主要参考资料等主要内容:设计一个洗衣机控制器,要求洗衣机有正转、反转、暂停三种状态。

设定洗衣机的工作时间,要洗衣机在工作时间内完成:定时启动→正转20秒→暂停10秒→反转20秒→暂停10秒→定时未到回到“正转20秒→暂停10秒→……”,定时到则停止,同时发出提示音。

基本要求:1、设计一个电子定时器,控制洗衣机作如下运转:定时启动→正转20秒→暂停10秒→反转20秒→暂停10秒→定时未到回到“正转20秒→暂停10秒→……”,定时到则停止;2、若定时到,则停机发出音响信号;3、用两个数码管显示洗涤的预置时间(分钟数),按倒计时方式对洗涤过程作计时显示,直到时间到停机;洗涤过程由“开始”信号开始;4、三只LED灯表示“正转”、“反转”、“暂停”三个状态。

主要参考资料:[1] 潘松著.EDA技术实用教程(第二版). 北京:科学出版社,2005.[2] 康华光主编.电子技术基础模拟部分. 北京:高教出版社,2006.[3] 阎石主编.数字电子技术基础. 北京:高教出版社,2003.完成期限2011.3.11指导教师专业负责人2011年3月7日一、总体设计思想1.基本原理从课程设计要求来看,要求实现电机的正传、反转、暂停,需要用LED灯的状态来表示,当显示时间前20秒正传、暂停10秒、反转20秒、再暂停10秒,如此一来,周期恰好是60秒。

洗衣机控制器的设计主要是定时器的设计。

由一片FPGA和外围电路构成了电器控制部分。

FPGA接收键盘的控制命令,控制洗衣机的进水、排水、水位和洗衣机的工作状态、并控制显示工作状态以及设定直流电机速度、正反转控制、制动控制、起停控制和运动状态控制。

对芯片的编程采用模块化的VHDL (硬件描述语言)进行设计,设计分为三层实现,顶层实现整个芯片的功能。

顶层和中间层多数是由VHDL的元件例化语句实现。

中间层由无刷直流电机控制、运行模式选择、洗涤模式选择、定时器、显示控制、键盘扫描、水位控制以及对直流电机控制板进行速度设定、正反转控制、启停控制等模块组成,它们分别调用底层模块。

数字逻辑实验——洗衣机定时控制器设计报告

数字逻辑综合性实验设计报告课程名称数字逻辑实验题目名称洗衣机定时控制器班级 20150615学号 2015061506学生姓名黄伟同组班级 20150615同组学号 2015061502 同组姓名郭伟指导教师武俊鹏、孟昭林、刘书勇、赵国冬摘要关键词:预置洗涤时间;倒计时显示;发出信号提醒用户;洗衣机状态转换提示功能;甩干功能洗衣机已经进入了千家万户,其控制逻辑和功能也为人熟知,本课题要求设计一个带有洗涤时间设定并显示功能的简易洗衣机控制电路,当时间到后,报警提醒。

根据要求,该电路需要有三个基础功能:第一,能在10分钟内自行设定洗涤时间;第二,用三位数码管显示预置洗涤时间,并对洗涤过程做倒计时显示,直到时间到零;第三,当时间到达终点时,会发出信号提醒用户注意。

在实现了基础功能的基础上,我们小组又扩展添加了三个功能:第一,在洗衣机洗衣功能进行到倒数第九秒时,会有一个小灯亮起提醒用户洗衣即将结束,且洗衣结束后,该灯保持闪亮直至洗衣功能被关闭;第二,为洗衣机状态转换提示功能,每十秒让设定好的小灯闪亮一次;第三,我们增加了甩干功能,因为,用户可能只需要甩干,所以甩干功能并未与洗衣功能自动连接起来,在甩干的倒数第八秒时,设定好的一个小灯会闪亮一下,提醒用户甩干即将完成,甩干结束后,此小灯会保持闪亮直至甩干功能被关闭。

该实验用到八种芯片,即74LS192、74LS11、74LS00、74LS04、74LS08、74LS27、74LS32、7490。

主要用到了反馈预置法,实现了六十进制,结合了组合逻辑电路与时序逻辑电路,以1hz的连续脉冲控制整个电路的运转,较好实现了洗衣机定时控制器常见的功能。

目录1 需求分析........................................................................................................................................... - 5 -1.1 基本功能要求......................................................................................................................... - 5 -1.2 创新拓展功能......................................................................................................................... - 5 -1.3 设计原理.................................................................................................................................. - 6 -1.4 实验原理图 ............................................................................................................................. - 6 -2 系统设计........................................................................................................................................... - 7 -2.1 系统逻辑结构设计................................................................................................................. - 7 -2.2 系统物理结构设计............................................................................................................... - 15 -3 系统实现......................................................................................................................................... - 24 -3.1 系统实现过程....................................................................................................................... - 24 -3.2系统测试............................................................................................................................ - 26 -3.3 系统最终电路图.................................................................................................................. - 30 -3.4系统团队分工........................................................................................................................ - 35 -4 总结.................................................................................................................................................. - 37 -5 引脚图附录 .................................................................................................................................... - 38 -1 需求分析1.1 基本功能要求1)洗涤时间在10分钟内由用户自行设定。

课程设计---洗衣机控制器的设计

电子技术课程设计报告书课题名称洗衣机控制器的设计姓名学号院、系、部专业电子信息工程指导教师2010年 11 月 25日洗衣机控制器的设计1 设计目的(1) 熟悉集成电路的引脚安排。

(2)掌握各芯片的逻辑功能及使用方法。

(3)了解面包板结构及其接线方法。

(4)了解洗衣机控制器的组成及工作原理。

(5)熟悉洗衣机控制器的设计与制作。

(6)运用HVDL 语言完成洗衣机控制器的编程。

2 设计思路(1)设计洗衣机控制器电路。

(2)设计可预置时间(10-30分钟)的定时模块。

(3)设计洗衣机运作模块,控制洗衣机的进水,洗衣,放水,脱水运转。

(4)设计分频模块,为洗衣机提供‘秒’时钟。

(5)设计译码模块,完成对时间(分)的二进制译码和LED 管的动态扫描。

(6)设计电源电路和按键判别电路。

(7)设计显示电路,完成对剩余时间和工作状态的显示3 设计过程3.1 方案论证洗衣机控制器的整体框图如下(图一)所示:图 一(洗衣机控制器原理框图)FPGA 芯片 电源总控制键盘电路 译码模块洗衣机运作模块 显示电路 分频模块 时钟(1K )工作原理:1、开启电源后,洗衣机进入总控模块的时间设定模式,由7段LED 灯显示所设定时间;2、时间设定后,启动洗衣机,进入洗衣机运转模式,即启动洗衣机运转模块,同时屏蔽总控模块总时间(Time_all )信号。

每次自动洗衣时间由总控模块自动分配。

七段LED 灯轮换显示工作模式(进水=1,洗衣=2,放水=3,脱水=4)和剩余时间。

3、3次自动洗衣完成后,洗衣机进入待机模式,七段LED 灯灭,再次等待时间设定。

电路设计洗衣机控制器主要电路如图所示:ULN2803是高电压大电流达林顿晶体管阵列,用于高电压大电流负载。

74LS138为动态扫描译码电路,可基于该电路扩展LED 显示为最高8位动态。

增加了VCC 所接上拉电阻,为LED 显示提供足够的驱动电流。

KEY 为机械开关,只针对单个按键进行合键判别,无对应行列扫描。

洗衣机控制器课程设计

课程设计任务书课程名称数字电子技术课题名称洗衣机控制器专业班级学号姓名指导教师任务书下达日期:设计完成日期:设计内容与设计要求一、设计内容:1.设计并制作一个电子定时器,用以控制洗衣机的电机作如下运转:启动—>预备10s —>洗涤Ⅰ30s—> 洗涤Ⅱ30s—>停止(放水)40 s—>甩干30s2. 用2位数码管显示洗涤时间(秒数),按倒计时方式对洗涤过程作计时显示,直到时间到停机,并发出音响信号报警。

3.用发光二极管显示洗涤过程的各道步骤。

4.* 总洗涤时间可由用户通过十进制拔码盘任意设定,并设置启动键,在预置定时时间后,按启动键开始机器运转。

5.*设置停止键,在洗涤过程中随时按该键可终止动作,并使显示器清0。

二、设计要求:1.设计思路清晰,给出整体设计框图和总电路图;2.单元电路设计,给出具体设计思路和电路;3.安装、调试电路;4.写出设计报告;主要设计条件1.提供调试用实验室;2.提供调试用实验箱和电路所需元件及芯片;说明书格式a.课程设计封面;b.任务书;c.说明书目录;d.设计总体思路,基本原理和框图(总电路图);e.单元电路设计(各单元电路图);f.安装、调试步骤;g.故障分析与电路改进;h.总结与体会;i.附录(元器件清单);j.参考文献;k.课程设计成绩评分表;进度安排第一周星期一:下达设计任务书,查找资料;星期二:确定总体设计方案;单元电路设计;星期三:电路仿真,修改方案;星期四:画出整机原理图草图及调试电路图;星期五:安装、调试电路;第二周星期一~三:安装、调试电路;星期四~五:验收电路,写设计报告,打印相关图纸;星期五:答辩、交设计报告书。

参考文献1、《电子线路设计、实验、测试》(第二版)华中理工大学出版社谢自美主编2、《新型集成电路的应用》---------电子技术基础课程设计华中理工大学出版社梁宗善主编3、《电子技术基础实验》高等教育出版社-------------陈大钦主编目录目录 (5)一.设计总体思路,基本原理和框图 (6)1.设计总体思路 (6)2.基本原理 (6)3.系统设计框图 (7)二.单元电路设计 (7)1、可预置数的减数计数器 (7)2、时间置数器 (9)3、步骤计数器及其显示、报警 (11)三.总电路图 (13)四.安装调试步骤 (19)五.故障分析与电路改进 (21)六.总结与调试体会 (22)七.附录(元器件清单) (23)八.参考文献 (23)电气与信息工程系课程设计评分表 (24)一.设计总体思路,基本原理和框图1.设计总体思路从课程设计要求来看,要求实现洗衣机的开机预备,分别洗涤2次,暂停放水,甩干,这就需要用到五个LED灯的状态来表示,且规定显示时间为预备10秒,2次洗涤都为30秒,暂停放水的时间为40秒,甩干也为30秒,如此一来,我们就要用到倒计时秒计数器,配合计数器我们还需要一个脉冲信号源,来让它实现倒计时。

课程设计---洗衣机控制器的设计

电子技术课程设计报告书课题名称洗衣机控制器的设计姓名学号院、系、部专业电子信息工程指导教师2010年 11 月 25日洗衣机控制器的设计1 设计目的(1) 熟悉集成电路的引脚安排。

(2)掌握各芯片的逻辑功能及使用方法。

(3)了解面包板结构及其接线方法。

(4)了解洗衣机控制器的组成及工作原理。

(5)熟悉洗衣机控制器的设计与制作。

(6)运用HVDL 语言完成洗衣机控制器的编程。

2 设计思路(1)设计洗衣机控制器电路。

(2)设计可预置时间(10-30分钟)的定时模块。

(3)设计洗衣机运作模块,控制洗衣机的进水,洗衣,放水,脱水运转。

(4)设计分频模块,为洗衣机提供‘秒’时钟。

(5)设计译码模块,完成对时间(分)的二进制译码和LED 管的动态扫描。

(6)设计电源电路和按键判别电路。

(7)设计显示电路,完成对剩余时间和工作状态的显示3 设计过程3.1 方案论证洗衣机控制器的整体框图如下(图一)所示:图 一(洗衣机控制器原理框图)FPGA 芯片 电源总控制键盘电路 译码模块洗衣机运作模块 显示电路 分频模块 时钟(1K )工作原理:1、开启电源后,洗衣机进入总控模块的时间设定模式,由7段LED 灯显示所设定时间;2、时间设定后,启动洗衣机,进入洗衣机运转模式,即启动洗衣机运转模块,同时屏蔽总控模块总时间(Time_all )信号。

每次自动洗衣时间由总控模块自动分配。

七段LED 灯轮换显示工作模式(进水=1,洗衣=2,放水=3,脱水=4)和剩余时间。

3、3次自动洗衣完成后,洗衣机进入待机模式,七段LED 灯灭,再次等待时间设定。

电路设计洗衣机控制器主要电路如图所示:ULN2803是高电压大电流达林顿晶体管阵列,用于高电压大电流负载。

74LS138为动态扫描译码电路,可基于该电路扩展LED 显示为最高8位动态。

增加了VCC 所接上拉电阻,为LED 显示提供足够的驱动电流。

KEY 为机械开关,只针对单个按键进行合键判别,无对应行列扫描。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子技术课程设计报告

设计题目:洗衣机定时控制器

院部:机械学院

专业:机械电子工程

学生姓名: 学号:

起迄日期: 2015 年 12 月30日2016年 1月 6日指导教师:丁跃浇

教研室主任:

1 引言

在我们的日常生活中,总免不了和各种各样的家用电器打交道,从而使得我们的生活更加的舒适方便。

而说到洗衣机,我们总能想到其中的数字倒计时时间显示控制各种部件的状态,使得整个洗衣机系统可以正常运转。

由此可见,洗衣机其中的定时控制器在其中起到了至关重要的作用,所以设计一个性能优良的定时控制器核心部件就显得尤为重要。

1.1指导思想

通过可加可减计数器74LS192来实现其中的主要时间倒计时功能,在通过其中的在不同时间下的各引脚不同的电平状态来控制洗衣机的正反暂停状态,并且通过相应的组合元件来控制电路的开关。

1.2方案论证

首先在拿到这个方案的时候,我认为这个设计的核心就是关于定时电路的设计,在99min内的能实现倒计时,那么采用什么元器件设计电路主体是比较稳定理想呢?在任务书中老师提供了161、192、138等元件,我通过相关资料了解了其功能,果然,其中的192是十进制加减计数器,由它就可以设计成满足要求的倒计时计数器。

在设计了倒计时计数器的主体电路之后,我就可以通过其不同引脚上的功能来延伸出外部控制电路,以达到实现洗衣机正转、反转、暂停和最终的停止等一系列功能。

1.3 基本设计任务

洗涤模式:

功能要求:

①洗涤时间在99分钟内由用户自行设定,单位为分钟。

②用两位数码管显示洗涤的预置时间(以分钟为单位),对洗涤过程作计时显示,直到时间到而停机。

③当定时时间达到终点时,一方面使电机停机(用三个LED表示电机的状态),同时发出音响信号提醒用户注意。

1.4电路设计思路及特点

对于洗衣机电机的工作顺序:“启动——>正转20s——>暂停10s——>反转20s——>暂停10s ——>正转20s——>……——>时间到停止”设计一个定时器控制洗衣机的电机的运转,由其转,传反转及暂停时间分析知道洗衣机运转的周期为60s,并且呈现周期循环,知道时间到停止为止。

我们可以利用计数器的功能进行60s的计数,及需要一个秒计数器,并且利用洗衣机的电机工作状态转换的时间来设置正转吗、暂停、反转。

如此则需要为计数器设置一个合适的脉冲,设计中的秒计数器所需的脉冲必为1HZ脉冲。

对于用数码管显示洗涤时间,按倒计数方式对洗涤对洗涤过程作倒计时显示,并且洗涤时间在99分钟内可由用户任意设定,并设置启动键,在预置定时时间后,按启动键开始机器运转。

分析知道我们还需要设置一个分钟计数器,可以利用秒计数器的借位端BO端连接到分计数器的DOWN端作为分计数器的输入信号来实现秒从分计数器上的借位从而构成分计数器的工作脉冲。

在要求中要求倒计时,显然我们需要递减计数器,和利用开关控制计数器的清零端CR的电平控制电路工作。

对于用LED模拟洗衣机的工作状态:LED1点亮表示正转,LED2点亮表示暂停,LED3点亮表示反转。

显然可以利用74LS138译码器,将秒十位的Qa、Qb、Qc分别接至A、B、C端进行译码,将输出4、5,0、3,1、2分别接至与非门输出分别接至LED1、LED2、LED3,从而实现洗衣机工作状态的指示。

2 电路设计

2.1 总体方框图

2.2 工作原理

首先,从秒脉冲出来的信号,经过一个控制电路后进入秒计数器进行秒计数,进行清零,这时用户置入洗涤时间,并按开始按钮,洗衣机开始工作。

当秒计数器变为零的时候,去分钟计数器上面借数;与此同时,从十秒位转化出来的信号进入移位寄存器后,LED灯表示出电机运转状态;当用户设定的洗涤时间结束后,电路报警并清零;同时电机指示灯熄灭。

3 各主要电路及部件工作原理

3.1置数减数器及显示部分

一百进制分计数器和六十秒计数器的原理是一样的,不同的只是它们的输入脉冲和进制不同而已,我们用四片74LS192来实现分计数和秒计数功能,我们要的只是减计数,所以我们把它的UP 端接到高电平上去,DOWN端接到秒脉冲上;十分秒位上的输入端B、C端接到高电平上,即从输入端置入0110(十进制的6),秒十位的LD端和借位端BO联在一起,再把秒位的BO端和十秒位的DOWN联在一起。

当秒脉冲从秒位的DOWN端输入的时候秒计数的192开始从9减到0;这时,它的借位端BO 会发出一个低电平到秒十位的输入端DOWN,秒十位的计数从6变到5,一直到变为0;当高低位全为零的时候,秒十位的BO发出一个低电平信号,DOWN为零时,置数端LD等于零,秒十位完成并行置数,下一个DOWN脉冲来到时,计数器进入下一个循环减计数工作中。

对于分计数来说,道理也是一样的;只是要求,当秒计数完成了,分可以自动减少,需要把秒十位的借位端BO端接到分计数的DOWN端作为分计数的输入信号来实现秒从分计数上的借位。

当然,这些计数器工作,其中的清零端CR要处于低电平,置数端不置数时要处于高电平。

这是一个独立工作的最高可以显示101分钟的计时器。

把四个192的QA/QB/QC/QD都接到外部的显示电路上就可以看到时间的显示了。

作为洗衣机控制器的一个模块,它还得有一定的接口来和其他的模块连接在一起协调工作,分计数的清零端LD是接在一起的;秒的清零端LD又是接在一起的,所以当要从外部把它们强制清零时,可以用一个三极管(NPN)或者两个或门就可以实现该功能。

还有我们可以利用分计数的UP 端来进行外部置数,当把它们各接到一个低触发(平时保持高电平,外部给一个力就输入一个低电平)的脉冲上就可以实现从0-9的数字输入。

3.3电机正反转即停止控制电路

在此部分电路中,三个指示灯,从左至右依次代表“正转”、“暂停”、“反转”。

从60秒到40秒内第一个灯亮,从40到30秒内是第二个灯亮。

在30到10秒内是第三个灯亮,然后剩下的十秒钟是第二个灯亮,如此完成第一个循环,刚好一分钟,之后的时间依次循环。

3.4蜂鸣器部分

当电动机的状态发生改变时即LED灯发生改变时,蜂鸣器会接受到一个脉冲,发出响声。

4 原理总图

5 仿真结果

6 分析与改进

6.1问题分析

1:计数器的进制设置于计数器之间的连接

2:LED指示灯的状态指示

3:工作后的停止设置

4:分秒置数开关的设定

5:清零开关的设置

6.2改进措施

1:减法计数器的BO平常位高电平,有借位时为低电平。

利用此特性,将其连接在高位计数器的DOWN端作为脉冲的输入,计数器的进制设置依靠其数入端D3、D2、D1、D0的置数。

2:LED灯的点亮与熄灭指示显示主要是取决于192的输出低三位,根据输入与输出的 10 关系,然后再利用指示灯应该点亮还是熄灭的规律列出真值表,求出所需要的门电路为与非门。

3:利用UP端的特性,为其可控置入低电平以改变十分位和个分为的数字显示,即实现置数功能。

为防止其置数的抖动,利用电容与电阻的组合连接电路,就可以实现置数功能的准确性,实现置数功能。

4:74LS192 CLR端平时为低电平,当需要清零时送入一个高电平信号即实现清零功能。

电路功能实现:两个置数开关可以实现0~99分钟以内任意洗涤时间的设置,数码显示其洗涤的剩余时间,LED灯为其指示洗衣机当前的工作状态,复位开关控制显示器的清零。

实用标准

7 设计体会及小结

经过了长时间的艰苦奋战,我们的洗衣机定时器终于成功了。

可以说我们已经是筋疲力尽了。

刚开始做的时候是热情饱满的,可是做着做着就有些烦躁了。

特别是在遇到问题而无法解决的时候,更是没有耐心去检查电路究竟出错在哪里。

我觉得做这次的设计做大的问题不是电路问题,而是焊接问题。

因为这个电路看起来很好做,但是实际上并不是那么容易,因为在焊接的时候有好多线,而且许多都交叉在一起,又有好多焊在一个引脚上,一不小心就会造成焊接错误。

有事时候由于焊接的不好会造成虚焊,这些问题都是比较但察觉的,也是很难去找到错误的根源的。

有一次由于不仔细把两个本来不该连在一起的引脚,由于在焊另一个引脚而不小心给牵连在了一起,而这种牵连基本上是看不见得。

就这个问题整整花费了我3个多小时我才找到了错误。

可以说这次课程设计要是没有耐心、细心和决心是绝对做不好的。

在遇到困难的时候没我也退缩过,特别是在最后的时候看到别的同学的都已经做好的时候,自己的心里也真的很不是滋味。

还有点后悔自己当时上课的时候没好好的听课。

但是在最后的关头我们没有放弃,并且互相鼓励,最终我们战胜了一切的困难,取得了胜利。

当看到我们的作品成功的时候,我的心里特别的激动,两周的辛苦没有白费。

这次设计最大的收获就是做每一件事都必须要有耐心,如果没有耐心我觉得什么事都不会成功。

还有就是在遇到困难的时候绝对不能低头,要有恒心和毅力去战胜一切苦难。

这次设计不仅锻炼了我的动手能力,还在不知不觉中考验着我的毅力和耐心。

从这次设计当中然我懂得了许多道理,要想成功就一定要付出比别人更多的代价。

总体来说感觉还是很开心,因为把理论与实际结合是一种非常有效的学习过程,获益匪浅。

文案大全。