基于FPGA的数字CMOS摄像机图像采集

基于FPGA的CCD相机的图像采集

4 7 , ia 10 3 Ch ) 0 n

Absr t t ac :Thi a rm an y de swih t sue s ̄ Uo s i to ucng t e ba kg o sp pe il a t he i l s sa w :nr d i h c r und ofC CD a e a d t ahe n n s ca nvr — c m r aa g t r g i pe i e ion i l m e t pr po i m eho o i h pe d i a e bae o FPGA ,nd patc a l ic sn t  ̄ t m tucur a t ntr a u to n , o sng a t d f h g s e m g s d n a riulry d susi g is s e sr t e nd i i e l f nc in s n m od l ,a h u e nd s ow he s ult eu to hePC II o eI s ic s ow o i p e e tt m e al nd PC Ii t ra e. t i m ai rs ft on l Pc r ta o ds u sh l t m l m n he Ca r i a nk n e fc

维普资讯 http://www.cqv本栏 贲任 辑: 薇 目 编 贾薇

・ ・ ・ 算机 工 程应 用技 术 ・ ・ ・・ 计

基于 F GA的 C D相机 的图像采集 P C

刘 基.德 建 杨 贵

( 防科 技 大 学 电子 科 学 与 工 程 学 院空 间所 , 国 湖南 长沙 4 0 7 ) 1 0 3

De i n o e I a e Ga e fCCD me a Ba e n F sg ft m g t r o h h Ca r s d o PGA

基于FPGA的高性能CMOS图像采集系统设计

基于FPGA的高性能CMOS图像采集系统设计樊春玲;范立超;明星;郭文记;邵巍【摘要】针对高性能CMOS图像传感器数据传输速度快、数据量大的特点,为了满足高性能图像采集系统的设计要求,基于高性能CMOS图像传感器CIS2521芯片,通过研究图像传感器芯片的工作方式及驱动控制特点,设计了一套以FPGA芯片作为控制核心处理器件,搭载CameraLink作为传输接口,以此来实现对高速图像数据的采集、缓存和传输等功能,为此本文给出了详细的硬件设计和实验结果验证.实验结果表明:该系统具有高性能、速度快、体积小、重量轻、速度快、集成度高等优点.%In order to meet the design requirement of high-performance image acquisition system,by studying the working mode and driving control characteristics of the image sensor,a speed image acquisition is designed based on high-performance CMOS image sensor CIS2521 chip,we choose FPGA as the control core processing device and equipped with CameraLink as the transmission interface to achieve high-speed image data acquisition,caching and transfer functions.This paper has given detail hardware design and experimental verification.The experimental results show that the system has the advantages of high-performance,fast speed,small volume,light weight,high speed and high integration.【期刊名称】《青岛科技大学学报(自然科学版)》【年(卷),期】2018(039)001【总页数】5页(P114-118)【关键词】CMOS图像传感器;高性能图像数据采集;FPGA;CameraLink接口【作者】樊春玲;范立超;明星;郭文记;邵巍【作者单位】青岛科技大学自动化与电子工程学院,山东青岛266042;青岛科技大学自动化与电子工程学院,山东青岛266042;中国科学院光电研究院,北京100094;中国科学院光电研究院,北京100094;青岛科技大学自动化与电子工程学院,山东青岛266042【正文语种】中文【中图分类】TP212目前,市面上的图像传感器主要分为电荷耦合器件(CCD)和互补金属氧化物半导体(CMOS)两种,随着半导体制造工艺的发展,CMOS图像传感器在分辨率、灵敏度、信噪比、功耗、集成度等方面取得了重大的突破[1-2]。

基于FPGA的增强型图像采集处理系统的设计与实现

基于FPGA的增强型图像采集处理系统的设计与实现基于FPGA的增强型图像采集处理系统的设计与实现摘要:本文基于FPGA技术,设计并实现了一种增强型图像采集处理系统。

该系统采用了Xilinx公司的FPGA芯片作为主控芯片,并根据图像采集处理的需求设计了相应的硬件电路。

通过该系统,能够对图像进行高效、准确的采集和处理,提高了图像处理的实时性和稳定性,具有较高的应用价值。

关键词:FPGA;图像采集处理;实时性;稳定性一、引言图像采集和处理是计算机视觉领域的重要研究方向之一。

在很多应用中,如医学影像分析、机器视觉、安防监控等,需要对图像进行实时采集和处理,以提取图像的有效信息。

然而,传统的图像采集与处理系统存在一些缺陷,如处理速度慢、实时性差、稳定性差等。

因此,设计一种基于FPGA的增强型图像采集处理系统具有重要的研究价值。

二、系统设计1. 系统架构本文设计的增强型图像采集处理系统主要包括两个模块:图像采集模块和图像处理模块。

其中,图像采集模块用于获取外部图像信号,并将其转换为数字信号输入到FPGA芯片中。

图像处理模块负责对采集到的图像进行处理,并输出处理结果。

2. 图像采集模块设计图像采集模块的设计基于FPGA芯片集成的高速ADC模块。

该模块能够将外部模拟信号转换为数字信号,并通过FPGA芯片的接口输入到系统中。

为保证采集的图像数据质量,我们选择了高分辨率、低噪声的ADC芯片,并根据系统需求进行了适当的配置。

3. 图像处理模块设计图像处理模块的设计主要包括图像预处理和图像算法两个部分。

图像预处理主要包括图像去噪、图像增强、图像滤波等处理方法,用于提取图像的有效信息。

图像算法部分根据具体应用需求设计,如图像分割、边缘检测、目标识别等。

为了提高系统的实时性,我们采用了流水线处理的方式,将多个处理步骤并行进行,减少了处理时间。

三、系统实现1. FPGA芯片编程本文选择了Xilinx公司的FPGA芯片作为主控芯片。

基于FPGA的图像采集处理系统

基于FPGA的图像采集处理系统在现代科技领域,特别是计算机视觉和机器学习领域,图像采集和处理已经成为一项至关重要的任务。

在许多应用中,需要快速、准确地对图像进行处理,这推动了图像采集和处理系统的研究和发展。

现场可编程门阵列(FPGA)作为一种可编程逻辑器件,具有并行处理能力强、功耗低、可重构等优点,使其成为构建高性能图像采集处理系统的理想选择。

FPGA是一种可通过编程来配置其硬件资源的集成电路,它由大量的可配置逻辑块、内存块和输入/输出块组成。

这些逻辑块和内存块可以在FPGA上被重新配置,以实现不同的逻辑功能和算法。

输入/输出块可以用于与外部设备进行通信。

基于FPGA的图像采集处理系统通常包括图像采集、预处理、传输、主处理和输出等几个主要环节。

这个阶段主要通过相机等设备获取图像数据。

相机与FPGA之间的接口可以是并行的,也可以是串行的。

并行接口通常传输速度更快,但需要更多的线缆;串行接口则使用更少的线缆,但传输速度可能较慢。

这个阶段主要是对采集到的原始图像数据进行初步处理,如去噪、灰度化、彩色化等。

这些处理任务可以在FPGA上并行进行,以提高处理速度。

经过预处理的图像数据需要通过接口或总线传输到主处理单元(通常是CPU或GPU)进行处理。

在传输过程中,可以使用DMA(直接内存访问)技术,以减少CPU的负载。

在这个阶段,主处理单元(通常是CPU或GPU)会对传输过来的图像数据进行复杂处理,如特征提取、目标检测、图像识别等。

这些处理任务需要大量的计算资源和算法支持。

处理后的图像数据可以通过接口或总线传输到显示设备或用于进一步的处理。

基于FPGA的图像采集处理系统具有处理速度快、可重构性强、功耗低等优点,使其在许多领域都有广泛的应用前景。

特别是在需要实时图像处理的场景中,如无人驾驶、机器视觉等,基于FPGA的图像采集处理系统将具有更高的性能和效率。

随着FPGA技术和相关算法的发展,我们可以预见,基于FPGA的图像采集处理系统将在未来得到更广泛的应用和推广。

基于FPGA的CMOS图像采集系统设计

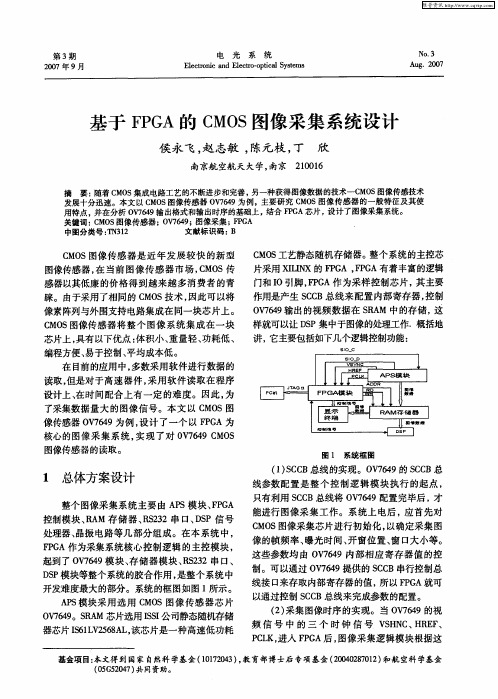

DP S 模块等整个系统 的胶合作用 , 是整个系统中 开发难度最大的部分。系统 的框图如图 1 所示。

AS P 模块采用选用 C O M S图像 传感 器芯片 0 74。S M芯片选用 IS 公司静态随机存储 V 69 R A SI

C O 工艺静态随机存储器。 MS 整个 系统的主控芯 片采用 XLN 的 F G ,P A有着丰富的逻辑 II X P A FG 门和 I O引脚 ,P A作为采样控制芯片, FG 其主要 作用是产生 S C C B总线来配置内部寄存器 , 控制 0 74 输出的视频数据在 S M 中的存储 , V 69 A R 这

维普资讯

第 3期

20 0 7年 9月

电

光

系 统

No 3 . Au .2 0 g 07

E e t n c a d E e to o t a y tms l cr i n l cr - p i lS s o c e

基于 F G P A的 C S图像采集 系统设计 MO

CO M S图像传感器是 近年发展较快 的新 型 图像传感器 , 当前 图像传 感器市场 , M S 在 C O 传 感器以其低廉的价格得到越来越多消费者的青 睐。由于采用 了相同的 C O 技术 , M S 因此可以将 像素阵列与外围支持 电路集成在 同一块芯片上。 CO M S图像传感器将整个 图像 系统 集成在一块 芯片上 , 具有以下优点 : 体积小 、 重量轻、 功耗低、 编程方便 、 易于控制、 平均成本低。 在 目 的应用中, 前 多数采用软件进行数据的

样就可以让 D P集中于图像的处理工作. S 概括地 讲, 它主要包括如下几个逻辑控制功能:

基于FPGA的双通道CMOS图像采集系统设计

0 引 言

整 个 系 统 的 可 靠 性 。 同 时 , 用 2片 大 容 量 的 S R M 以 采 D A

目前 , 越来越多 的图像采集 系统采用 C S图像传 感 MO

器 …作为图像采 集器件 。随着 集成 电路设 计技 术 的不断 提高 , MO C S图像传 感器 的采集速 度不 断增大 。在 实际 应用 中, 传统 的单通道 数据传输 方式和单 片机实现 的图像 处理系统 已经远远无法满 足设计要 求 , 须采用新 的数据 必 传输方式和设计方法来实现图像采集 、 传输和存储功能。

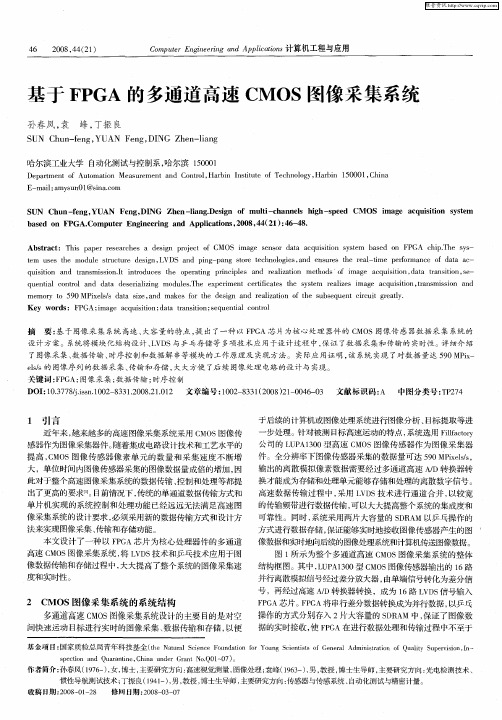

本 文 设 计 了一 种 以 F G 芯 片 为 核 心 处 理 器 的 双 通 道 PA

乒乓操作 的方式进行 数据存储 , 保证 能够实时地接 收图像

传感器产生的图像数据 。 经综合 分 析 和考 虑,P A采 用 A e FG hr a的 C c n yl e o E 2 3 F8 C 视频采集芯片用 飞利 浦的 S A 132块 型 P C 5 4 4 8, A 71 , 号为 K S 42的 S R M 和 F G 463 D A P A构成 图像 帧存储 与传输

Ab ta t Re lt r c s ig o g s u u l o t — e k i mb d e ma e p o e sn y tm. a i g sr c : a — me p o e sn fi e i s al a b t e n c n e e d d i g rc s i g s s i ma y l e T kn

teavnaeo aae poes g af l por al gt ar ( P A)b sdC S i g cu io h da t fprll rcsi , e rga g l n id mm b a r y F G e e a ae MO mae aq it n si ss m ids nd T em d l s ut eds n fs i fsotFF yt ei e . h o u rc r ei ,rtni t u( IO)adpn—ags r cn l e r ue e s g et u g i r n igpn o t h o g s e sd tee o i a

基于FPGA的视频图像采集处理系统的设计与实现

基于FPGA的视频图像采集处理系统的设计与实现基于FPGA的视频图像采集处理系统的设计与实现摘要:本文针对传统视频图像采集系统在处理速度和资源利用率方面的不足,设计了一种基于FPGA的视频图像采集处理系统。

该系统通过使用FPGA作为硬件平台,结合图像预处理、图像编码和图像解码等核心模块,实现了快速高效的视频图像采集与处理。

实验结果表明,该系统在视频图像采集和处理的功能上具有较好的性能,能够广泛应用于图像处理领域。

1. 引言随着科技的不断发展,视频图像采集与处理在许多领域中得到了广泛应用,如监控系统、医疗影像等。

传统的视频图像采集处理系统通常使用软件实现,但由于软件的运行效率较低,无法满足实时处理的需求。

因此,基于FPGA的硬件实现方案成为了改进的方向。

2. 系统设计基于FPGA的视频图像采集处理系统主要由以下几个模块组成:图像采集模块、图像预处理模块、图像编码模块、图像解码模块和图像显示模块。

图像采集模块主要负责采集外部图像信号,并将其输入到FPGA中。

图像预处理模块对输入的图像进行处理,如去噪、增强等,以提高图像质量。

图像编码模块将处理后的图像进行编码,压缩数据量,并减少传输带宽。

图像解码模块将接收到的编码数据解码成原始图像数据。

图像显示模块将解码后的图像数据进行显示,以供用户观看。

3. 系统实现在系统实现方面,首先需要选择适合的FPGA芯片作为硬件平台。

然后,利用Verilog来描述各个模块的功能,并进行相应的逻辑设计。

最后,通过将Verilog代码综合、布局和布线,生成FPGA配置文件,并烧录到FPGA芯片中。

4. 系统性能评估与实验结果分析为了评估系统的性能,进行了一系列实验。

实验结果表明,该系统在图像采集和处理的速度上优于传统的软件实现方法。

此外,该系统的资源利用效率也较高,能够满足实时处理的需求。

5. 系统应用展望基于FPGA的视频图像采集处理系统具有广泛的应用前景。

不仅可以应用于监控系统,还可以应用于医疗影像、工业检测等领域。

基于FPGA的多通道高速CMOS图像采集系统

DOI 1. 7 /i n10 — 3 1 0 8 1 1 文章编 号:0 2 83 (0 8 2 — 0 6 0 文献标识码 : 中图分类号: P 7 :03 8 .s. 2 8 3 . 0 . . 2 7 js 0 2 20 10 — 3 1 2 0 )1 0 4 — 3 A T24

1 引言

t m s s t e mo u e t cu e e i n L e u e h d l sr t r d sg , VDS n i g p n tr e h o o is a d e s r s t e r a — i e fr n e o aa a — u a d p n — a g so e t c n l ge , n n u e h e l t me p r ma c f d t c o q ii o a d r n mi s n I n r d c s h o e ai g r cp e a d r a iain u st n n t s s i . i t u e t e p r t p i i ls n e l t meh d o ma e c u st n, a a r n i o s — i a o t o n n z o t o s f i g a q ii o d t t s in, e i a t q e t l c n r l n d t d s raii g u n i o t a d aa e e ilz mo u e . h e p r n e i c t s h s se r aie ma e c u st n, a s s in n a o n d ls e x ei T me t c r f a e t e y tm e l s i g a q ii o t n miso a d ti z i r

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的数字CMOS摄像机图像采集一、数据采集系统概述数据采集是指将以各种形式输入的被测信号,包括语音信号、温度信号、湿度信号、图像信号等经过适当处理,成为计算机可以识别的数字信号,从而送入计算机进行存储处理的过程,数据采集卡就是典型的基于数据采集系统原理的集成计算机扩展卡。

如图1所示,在数据采集过程中主要有几个关键部分:(1)输入信号的幅度较小或者过大,需要经过放大器单元将输入信号幅度放大或者缩小;(2)输入信号带有较大的噪声,需要经过一个硬件的模拟滤波单元,将信号滤波整形;(3)将信号送到AD进行模数转换;(4)将信号传输到计算机;(5)存储记录和处理数据。

图1数据采集过程通常认为如果数字逻辑电路的频率超过50MHz,而且工作在这个频率之上的电路已经占到了整个电路系统的三分之一以上,就称为高速电路。

相应的,对于并行采样系统,如果采样频率达到50MHZ,数据量并行8bit以上;对于串行采样系统,如果采样频率达到200MHz,一般将这种采样系统也称为高速数据采集。

目前高速数据采集使用较多的采样频率一般在50M~100MHz之间。

采集系统分模拟系统和数字系统,大多数字采集系统中,CMOS图像传感器是系统的成像部件,它是系统的“眼睛”,能够捕获高速运动物体的图像,此模块是将采集的模拟图像转化为数字信号输出;图像处理模块是系统的中间缓存处理部分,此模块为了消除或降低前期采集携带噪声的影响,提高图像质量,将庞大的数据量进行压缩,以减小对存储介质容量的要求;数据传输模块是系统与外设搭建的桥梁,此模块是将实时采集的数据高速传输,给外设提供信息。

二、总体方案设计方案1:图像数据的传输通过USB总线技术完成系统的初始化以及将最终的传输信号准确无误地传送到上位机上。

USB技术具有简单化、通用性、可靠性、热插拔、传输速率高等优点,随之带来的是应用USB技术的复杂程度高、总线传输协议需要协调等问题。

方案2:利用两片SDRAM进行图像数据的短时间存储并快速传输,SDRAM是多Bank结构,例如在一个具有两个Bank的SDRAM的模组中,其中一个Bank在进行预充电期间,另一个Bank却马上可以被读取,这样当进行一次读取后,又马上去读取已经预充电Bank的数据时,就无需等待而是可以直接读取了,这也就大大提高了存储器的访问速度。

其优点是设计相对简单、不许考虑传输时转换总线的问题、较为可靠,缺点是SDRAM容量有限、传输时序需要计算准确、SDRAM经常刷新等。

根据综合分析和考虑,我们选用相对简单方便的方案2,选择器件如下:FPGA采用Altera 的Cyclone EP2C35F484C8,视频采集芯片用飞利浦的SAA7113作为A/D转换单元,两块型号为K4S641632E的SDRAM和FPGA构成图像帧存储及传输处理系统,ADV7125是数模转换芯片,和计算机VGA显示器相连作为显示终端,系统整体框图如图2所示。

图2视频监控系统整体框图以上图像视频监视系统的大部分设计工作都集中在对FPGA的编程开发上,通过分析可以确定出FPGA需要包含如下几个功能模块。

(1)视频接口配置模块:视频采集芯片SAA7113具有多种采集方式,这里FPGA通过I²C 总线对其内部寄存器进行配置,使其按照一定的格式进行采样。

(2)异步FIFO模块:当FPGA接收A/D采样的视频数据时,由于SAA7113和FPGA一般在不同的时钟频率下,这就会出现通常所说的异步时钟问题,处理不当就容易出现亚稳态,常用方法是在两者之间添加一块异步FIFO。

(3)视频变换模块:对得到的数字视频流进行解码,识别出行、场同步信号,并且根据需要选择采集图像的大小,进而变换成RGB格式的图像数据,以便于后续显示。

(4)图像帧存读写模块:将解码后的数据经由一个乒乓机制依次存放在两片RAM中,每个里面刚好存放一幅图像,通过乒乓机制使得两块存储区域交替进行存储输入和显示输出,避免等待,提高速度。

(5)VGA控制模块:根据VGA的工业参数,产生相应的行同步和场同步信号,并在适当时刻送入数据,经由ADV7125送VGA进行显示。

图3描述了FPGA内部的各个主要功能模块。

系统上电时,FPGA首先从外部Flash中读取配置数据,完成自身的程序加载,进入工作模式状态。

随后I²C配置接口模块完成对SAA7113的初始化,初始化结束后,FPGA等待采集图像的命令。

FPGA收到采集命令后,启动采集视频数据模块、异步FIFO模块和视频解码模块进行解码,将数据轮换写到两个帧存中,经通信模块送出,以上即为该系统的工作流程。

下面主要针对SDRAM控制模块的具体实现过程进行详细分析和介绍。

图3 FPGA系统内部各模块整体框图三、SDRAM控制模块系统要把每一幅图像数据存储到一个SDRAM里面供后续显示,由于SDRAM整个数据的写入和读出都需要一定的时间,为了避免中间等待过程,采用两片等大的SDRAM交替工作,一片在从FIFO向其写入时另一片向VGA输出,使用乒乓机制交换它们的工作性质。

这样问题的重点就集中在FPGA对SDRAM的读写控制模块上。

3.1SDRAM概述之所以要用到SDRAM,是因为它价格低、体积小、速度快、容量大,是比较理想的存储器件。

在基于FPGA的图像采集和集中显示系统中,常常要用到这种大容量、高速度的存储器。

但SDRAM的控制逻辑比较复杂,对时序要求也十分严格,这就要求有一个专门的控制器,使系统用户能很方便地操作SDRAM。

SDRAM器件的管脚分为控制信号、地址和数据3类。

通常一个SDRAM中包含几个BANK,每个BANK的存储单元是按行和列寻址的。

由于这种特殊的存储结构,SDRAM有以下几个工作特性。

(1)SDRAM的初始化SDRAM在上电100~200μs后,必须由一个初始化进程来配置SDRAM的模式存储器,模式存储器的值决定SDRAM的工作模式。

访问存储单位:为减少I/O引脚数量,SDRAM复用地址线,所有在读写SDRAM时,先由ACTIVE命令激活要读写的BANK,并锁存行地址,然后在读写指令有效时锁存列地址。

一旦BANK被激活后,只有执行一次预充命令后才能再次激活同一BANK。

(2)刷新和预充SDRAM的存储单元可以理解为一个电容,总是倾向于放电,因此必须有定时刷新周期以避免数据全失。

刷新周期可由(最小刷新周期+时候周期)计算获得。

对BANK预充电或者关闭已激活的BANK,可预充特定BANK也可同时作用于所有BANK,A10、BA0和BA1用于选择BANK。

(3)操作控制SDRAM的具体控制命令由一些专用控制引脚和地址线辅助完成。

CS、RAS、CAS和WR在时钟上升沿的状态决定具体操作动作,地址线和BANK选择控制线在部分操作动作中作为辅助参数输入。

由于特殊的存储结构,SDRAM操作指令比较多,不像SRAM一样只有简单的读写。

根据系统要求,本设计选用SAMSUNG的K4S6432 SDRAM芯片。

3.2SDRAM控制器总体设计SDRAM控制器与外部的接口示意图由图4给出,控制器右端接口信号均为直接与SDRAM对应管脚相连的信号;控制器左端的接口信号为与FPGA相连的系统控制接口信号,其中,CLK为系统时钟信号,RESET_N为复位信号,ADDR为系统给出的SDRAM地址信号,DAIN是系统用于写入SDRAM的数据信号,FPGA_RD和FPGA_WR为系统读、写请求信号(1为有效,0为无效),SDRAM_FREE是SDRAM的空闲状态标示信号(0为空闲,1为忙碌),FDATA_ENABLE是控制器给系统的数据收发指示信号(为0时,无法对SDRAM 进行数据收发;为1时,若是系统读操作,则系统此时可从DAOUT接收SDRAM的数据,若是写操作,则系统此时可以通过DAIN发送数据给SDRAM)。

图4总体设计框图和外部接口信号参照SDRAM的数据手册可知,它的指令译码对照表如表1所示。

表1 SDRAM指令译码对照表仔细分析SDRAM的各个接口信号、时序要求和工作模式,将该SDRAM控制器的内部进一步细化为多个功能模块,结构组成如图5所示,包括系统控制接口模块、CMD命令解析模块、命令相应模块、数据通路模块。

系统控制接口模块用于接收系统的控制信号,进而产生不同的CMD命令组合;CMD命令解析模块用于接收CMD命令并解码成操作指令;命令响应模块用于接收操作指令并产生SDRAM的操作动作;数据通路模块则用于控制数据的有效输入输出。

图5 SDRAM控制器的结构图3.3SDRAM系统控制接口子模块设计该模块主要包括初始化和系统指令分析功能。

其工作过程如下:由计数器控制在系统上电约200μs后,先进行SDRAM的初始化配置工作,由一个Precharge all back指令完成对所有BANK的预充,接着是多个Refresh指令,然后是模式配置指令LOADMODE,完成SDRAM 的工作模式设置。

之后进行控制器的初始化配置工作,先发出指令LOADREG1给控制器载入模式字,再发出LOADREG2指令载入控制器的刷新计数器值,完成控制器初始化配置。

上述初始化过程结束后,系统指令分析机制才可接收并分析系统的读写信号和地址信息,以及从下个模块反馈回来的CMD_ACK信号,并产生对应的CMD命令和SADDR地址信息给CMD命令解析模块。

通过程序设置,实现了根据初始化配置的参数来确定在读写到特定时刻发出Precharge或者Refresh的CMD指令,从而简化了系统的控制。

而每当收到CMD_ACK为1时,表示CMD指令已经发出并有效,此时就要发出NOP命令(CMD=000)。

要说明的是,SADDR是分时复用的,在初始化载入模式时,SADDR用以传输用户自己定义的模式字内容;而在正常的读写期间,SADDR作为地址线传输SDRAM所需的行、列和块地址。

代码示例如附件1.3.4CMD命令解析和命令相应子模块该模块首先对CMD指令进行判断,其结果解释输出相应的操作指令进行响应。

例如,CMD为001时,则会输出do_read信号为1;CMD为010时,则会输出do_write信号为1,在同一时刻,只会输出一种有效的操作指令。

然后该模块根据操作指令,做出符合SDRAM 读写规范的操作动作,来进行用户期望的操作;给出数据选通信号OE,来控制数据通路模块(写操作OE为1,读操作时OE为0)。

此外,该模块把系统非复用的地址ADDR处理为SDRAM复用的地址,分时送给SA、BA。

程序中地址复用的方法为:assign raddr=ADDR[ROWSTART+ROWSIZE-1:ROWSTART];//raddr为行地址assign eaddr=ADDR[COLSTART+COLSIZE-1:COLSTART];//eaddr为列地址assign baddr=ADDR[BANKSTART+BANKSIZE-1:BANKSTART];//baddr为BANK地址在程序中,WRITEA和READA的CMD指令实际隐含了ACTIVE命令,所以该模块在收到do_write或do_read指令后,会先进行激活动作,经过初始化配置规定的CAS延迟时间之后再进行读写动作。