半导体封装制程及其设备介绍

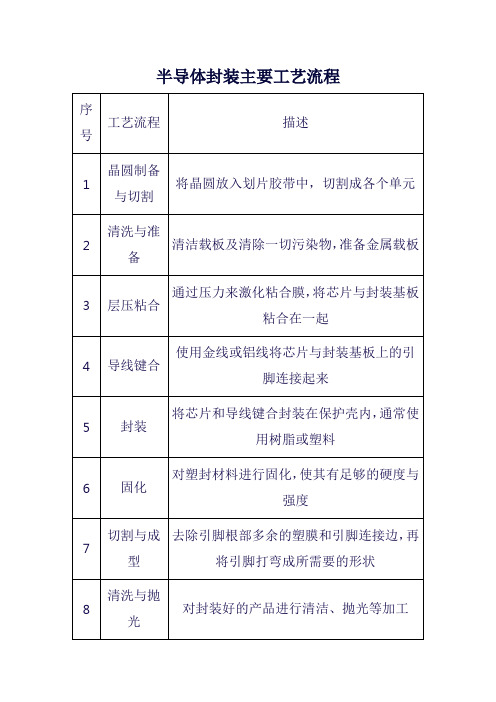

半导体封装主要工艺流程

序号

工艺流程

描述

1

晶圆制备与切割

将晶圆放入划片胶带中,切割成各个单元

2

清洗与准备

清洁载板及清除一切污染物,准备金属载板

3

层压粘合

通过压力来激化粘合膜,将芯片与封装基板粘合在一起

4

导线键合

使用金线或铝线将芯片与封装基板上的引脚连接起来

5

封装

将芯片和导线键合封装在保护壳内,通常使用树脂或塑料

6

固化

对塑封材料进行固化,使其有足够的硬度与强度

7

切割与成型

去除引脚根部多余的塑膜和引脚连接边,再将引脚打弯成所需要的形状

8

清洗与抛光

对封装好的产品进行清洁、抛光等加工

9

标识与打印

根据客户需要,在封装器件表面进行打印,用于识别

10

测试

对封装好的半导体器件进行测试,检验其性能和可靠性

半导体制造流程及生产工艺流程

半导体制造流程及生产工艺流程半导体是一种电子材料,具有可变电阻和电子传导性的特性,是现代电子器件的基础。

半导体的制造流程分为两个主要阶段:前端工艺(制造芯片)和后端工艺(封装)。

前端工艺负责在硅片上制造原始的电子元件,而后端工艺则将芯片封装为最终的电子器件。

下面是半导体制造流程及封装的主要工艺流程:前端工艺(制造芯片):1.晶片设计:半导体芯片的设计人员根据特定应用的需求,在计算机辅助设计(CAD)软件中进行晶片设计,包括电路结构、布局和路线规划。

2.掩膜制作:根据芯片设计,使用光刻技术将电路结构图转化为光刻掩膜。

掩膜通过特殊化学处理制作成玻璃或石英板。

3.芯片切割:将晶圆切割成单个的芯片,通常使用钻孔机或锯片切割。

4.清洗和化学机械抛光(CMP):芯片表面进行化学清洗,以去除表面杂质和污染物。

然后使用CMP技术平整芯片表面,以消除切割痕迹。

5.纳米技术:在芯片表面制造纳米结构,如纳米线或纳米点。

6.沉积:通过化学气相沉积或物理气相沉积,将不同材料层沉积在芯片表面,如金属、绝缘体或半导体层。

7.重复沉积和刻蚀:通过多次沉积和刻蚀的循环,制造多层电路元件。

8.清洗和干燥:在制造过程的各个阶段,对芯片进行清洗和干燥处理,以去除残留的化学物质。

9.磊晶:通过化学气相沉积,制造晶圆上的单晶层,通常为外延层。

10.接触制作:通过光刻和金属沉积技术,在芯片表面创建电阻或连接电路。

11.温度处理:在高温下对芯片进行退火和焙烧,以改善电子器件的性能。

12.筛选和测试:对芯片进行电学和物理测试,以确认是否符合规格。

后端工艺(封装):1.芯片粘接:将芯片粘接在支架上,通常使用导电粘合剂。

2.导线焊接:使用焊锡或焊金线将芯片上的引脚和触点连接到封装支架上的焊盘。

3.封装材料:将芯片用封装材料进行保护和隔离。

常见的封装材料有塑料、陶瓷和金属。

4.引脚连接:在封装中添加引脚,以便在电子设备中连接芯片。

5.印刷和测量:在封装上印刷标识和芯片参数,然后测量并确认封装后的器件性能。

半导体封装制程及其设备介绍

半导体封装制程及其设备介绍一、概述半导体芯片是一种微型电子器件,半导体封装制程是将芯片进行外层包装,从而保护芯片、方便焊接、测试等工作的过程。

比较常见的半导体封装方式有芯片贴装式、铅框式、无铅框式等。

本文将从半导体封装的制程入手,为大家介绍半导体封装制程及其设备。

二、半导体封装制程1. 粘结半导体封装的第一步是将芯片粘结到支撑贴片(Leadframe)上面。

支撑贴片是一种晶粒尺寸相对较大、但还不到电路板级别的导体片。

常用的粘接剂有黄胶、银胶等,其使用在制程时会加热到一定温度,使其能够黏合贴片和芯片。

2. 线缆连接芯片被粘接到支撑贴片上方后,需要进行内部连线。

通常使用铜线作为内部连线,常用的连线方式有金线焊接和铜线焊接。

它们的区别很大程度上取决于封装要求和芯片使用情况。

3. 包封装在连线之后,开始进行半导体封装的最后一步–包封装。

包封装是将芯片包封闭在一起,以进一步保护它。

常用的封装方式有QFP、BGA、SOIC、CHIP 贴片等。

三、半导体封装设备介绍1. 芯片粘结设备芯片粘结设备是半导体封装的第一步。

常用的芯片粘结设备包括黄胶粘合机、银胶粘合机、重合机等。

不同类型的设备适用于不同封装要求的芯片。

2. 线缆连接设备目前,铜线焊接机处于主流位置。

与金线焊接机相比,铜线焊接机具有成本更低、可靠度更高的优点。

因此,其能够更好地满足不同类型的芯片封装要求。

3. 包封装设备包封装设备是半导体封装的重要步骤。

常用的设备有 QFP 封装机、CHIP 贴片封装机等。

它们能够满足不同类型的封装要求,使芯片更加可靠。

四、半导体封装制程及其设备涉及到了许多知识点。

本文从制程和设备两个角度,为大家介绍了半导体封装制程及其设备。

不同的封装方式和设备对于产品的品质、成本以及生产效率都有很大的影响。

因此,在选择半导体封装制程和设备时,需要根据实际情况进行选择,以确保产品达到最佳性能和质量要求。

半导体封装制程及其设备介绍——【半导体芯片】

Dual In-line Package

Shape

Typical Features

Material Lead Pitch No of I/O

Ceramic Plastic

2.54 mm (100miles)

8 ~64

SIP

Single In-line Package

Plastic

2.54 mm (100miles) 1 direction

Material Lead Pitch No of I/O

Ceramic

1.27 mm (50miles) j-shape bend 4 direction

lead

18~124

Ceramic

0.5 mm

32~200

SMT (Optional)

Taping (Optional)

Grinding (Optional)

lead

3~25

Through Hole Mount

ZIP

Zigzag In-line Package

S-DIP

Shrink Dual In-line

Package

封裝型式

Shape

Typical Features

Material Lead Pitch No of I/O

Plastic

2.54 mm (100miles) 1 direction

Pack

封裝型式

Shape

Typical Features

Material Lead Pitch No of I/O

Plastic

1.27 mm (50miles) 2 direction

lead

8 ~40

半导体制程工艺流程及设备

半导体制程工艺流程及设备嘿,你有没有想过,那些小小的芯片是怎么被制造出来的呢?今天呀,我就来给你讲讲半导体制程工艺流程以及用到的设备,这可真是个超级有趣又超级复杂的事儿呢!咱先从最开始的晶圆制造说起。

晶圆就像是盖房子的地基一样,是整个半导体的基础。

晶圆是由硅这种材料制成的,你可别小看硅,它就像半导体世界里的超级明星。

这硅啊,要经过一系列的处理。

首先是提纯,这过程就像是把一堆沙子里的金子给挑出来一样困难。

要把硅提纯到非常非常高的纯度,几乎没有杂质才行。

我有个朋友在硅提纯的工厂工作,他就经常跟我抱怨说:“哎呀,这提纯工作可真不是人干的呀,一点点的差错就可能毁了一整批硅呢!”提纯之后呢,就要把硅做成圆柱体的硅锭,然后再把这个硅锭切割成一片片薄薄的晶圆。

这个切割过程可得非常小心,就像切一块超级薄的豆腐一样,一不小心就碎了。

这时候就用到了专门的切割设备,那些设备就像是精密的手术刀,把硅锭精准地切成一片片的晶圆。

有了晶圆之后,就要开始在上面进行各种加工了。

这就像是在一张白纸上画画一样,只不过这个画画的过程超级复杂。

其中一个重要的步骤是光刻。

光刻呀,你可以想象成是用光照在晶圆上画画。

这时候就需要光刻设备了,光刻设备就像是一个超级厉害的投影仪。

它把设计好的电路图案通过光线投射到晶圆上,而且这个图案超级精细,就像头发丝的千分之一那么细呢!我记得我第一次看到光刻图案的时候,我都惊呆了,我就想:“我的天呐,这怎么可能做到这么精细呢?”我当时就问一个做光刻的工程师,他就很自豪地说:“这就是科技的力量呀,我们通过各种技术手段才能把图案刻得这么精细呢。

”光刻完了之后,就是蚀刻。

蚀刻就像是把光刻出来的图案进行雕刻一样,把不需要的部分去掉,只留下我们想要的电路图案。

这就好比是雕刻一个石像,把多余的石头去掉,留下精美的雕像。

蚀刻用到的设备会喷出一些化学物质,这些化学物质就像小雕刻家一样,把晶圆上的材料按照光刻的图案进行去除。

不过这个过程可危险了,那些化学物质可都是腐蚀性很强的东西,就像一群小恶魔,要是不小心泄露了,可就会造成大麻烦。

半导体封装制程及其设备介绍

Solder paste

Die Prepare(芯片预处理) To Grind the wafer to target thickness then separate to single chip

---包括来片目检(Wafer Incoming), 贴膜(Wafer Tape),磨片(Back Grind),剥膜(Detape),贴片(Wafer Mount),切割(Wafer Saw)等系列工序,使芯片达到工艺所要求的形状,厚度和尺寸,并经过芯片目 检(DVI)检测出所有由于芯片生产,分类或处理不当造成的废品.

B Wafer roughness Measurement 粗糙度测量仪 主要为光学反射式粗糙度测量方式;

4.Grinding 配套设备

A Taping 贴膜机 B Detaping 揭膜机 C Wafer Mounter 贴膜机

Wafer Taping -- Nitto DR300II

Alignment

1.27, 0.762 mm (50, 30miles)

Ceramic 2, 4 direction lead

20~80

Ceramic

1.27,1.016, 0.762 mm (50, 40, 30

miles)

20~40

大家应该也有点累了,稍作休息

大家有疑问的,可以询问和交流

Surface Mount

半导体设备供应商介绍-前道部分

半导体设备供应商介绍-前道部分

常用术语介绍

1. SOP-Standard Operation Procedure 标准操作手册 2. WI – Working Instruction 作业指导书 3. PM – Preventive Maintenance 预防性维护 4. FMEA- Failure Mode Effect Analysis 失效模式影响分析 5. SPC- Statistical Process Control 统计制程控制 6. DOE- Design Of Experiment 工程试验设计 7. IQC/OQC-Incoming/Outing Quality Control 来料/出货质量检验 8. MTBA/MTBF-Mean Time between assist/Failure 平均无故障工作时间 9. CPK-品质参数 10. UPH-Units Per Hour 每小时产出 11. QC 7 Tools ( Quality Control 品管七工具 ) 12. OCAP ( Out of Control Action Plan 异常改善计划 ) 13. 8D ( 问题解决八大步骤 ) 14. ECN Engineering Change Notice ( 制程变更通知 ) 15. ISO9001, 14001 – 质量管理体系

半导体封装制程与设备材料知识简介

封裝型式

Shape

Typical Features

Materia Lead Pitch No of I/O l

Cerami c

1.27, 0.762 mm

(50, 30miles) 2, 4 direction

lead

20~80

Ceramic

1.27,1.016, 0.762 mm (50, 40, 30

(氧化处理)

Depositio n

(沉积)

WireBondin g

(焊线)

Laser mark (激光印字)

Laser Cut & package saw

(切割成型)

Testin g

(测试)

Lithograp hy

(微影)

Wafer Inspection (晶圆检查) 前段結束

Moldin g

(塑封)

Plastic

1.27 mm (50miles) 2 direction

lead

8 ~40

Plastic

1.0, 0.8, 0.65 mm 4 direction

lead

88~200

Surface Mount

FPG

Flat Package of Glass

LCC

Leadless Chip

Carrier

lead

18~124

Ceramic 0.5 mm

32~200

SMT (Optional)

Taping (Optional)

Assembly Main Process

Grinding (Optional)

Detaping (Optional)

Wafer Mount

半导体封装制程及其设备介绍详解演示文稿

半导体封装制程及其设备介绍详解演示文稿一、引言二、半导体封装制程的整体流程1.设计和制备芯片:在封装过程开始之前,需要进行半导体芯片的设计和制备。

这包括设计电路、选择材料、制造芯片等步骤。

2.选型和设计封装方案:根据芯片功能和其他要求,选择合适的封装方案。

封装方案的选择包括外形尺寸、引脚数量和布局、散热设计等。

3.制备基板:选择合适的基板材料,并进行加工和制备。

基板的制备是封装制程中的核心环节之一,目的是为芯片提供支撑和连接。

4.芯片连接:将芯片连接到基板上,通常使用焊接技术或金线键合技术。

焊接是将芯片的引脚与基板的焊盘连接起来,金线键合则是用金线将芯片与基板进行连接。

5.包封:将芯片和连接线封装进封装材料中,形成最终的封装产品。

常见的封装材料有环氧树脂和塑料,也有针对特殊应用的金属封装。

6.测试和质量检验:对封装后的产品进行测试和质量检验,确保其符合设计要求和标准。

测试主要包括电性能测试、可靠性测试和环境适应性测试等。

7.封装后处理:包括喷涂标识、气密性测试、老化测试等。

这些步骤都是为了保证封装产品的质量和性能稳定。

三、半导体封装制程的关键步骤及设备介绍1.基板制备基板制备是封装制程中的核心步骤,主要包括以下设备:(1)切割机:用于将硅片切割成芯片,常见的切割机有钻石切割机和线切割机。

(2)干法清洗机:用于清洗芯片表面的杂质。

清洗机主要有氧气等离子体清洗机和干气流清洗机等。

(3)晶圆胶切割机:用于将芯片粘贴在基板上。

2.连接技术连接技术是将芯片与基板连接起来的关键步骤,常见的设备有:(1)焊接机:用于焊接芯片和基板之间的引脚和焊盘。

常见的焊接机有波峰焊机和回流焊机。

(2)金线键合机:用于将芯片与基板之间进行金线键合连接。

常见的金线键合机有球焊键合机和激光键合机等。

3.封装工艺封装工艺是将芯片和连接线封装进封装材料中的步骤,主要设备有:(1)半导体封装设备:用于将封装材料和连接线封装成最终产品。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Very Small Quad Flatpack

封裝型式

Shape

Typical Features

Material Lead Pitch No of I/O

Ceramic

1.27 mm (50miles) j-shape bend 4 direction

lead

18~124

Ceramic

0.5 mm

半导体设备供应商介绍-前道部分

PROCESS

DIE BOND

CURE OVEN WIRE BONDER

PLASMA CLEAN Mold

VENDOR

HITACHI ESEC ASM C-SUN K&S SKW ASM MARCH TEPLA TOWA ASA

MODEL

DB700 ESEC2007/2008

WireBonding (焊线)

Lithography (微影)

Wafer Inspection (晶圆检查) 前段結束

Molding (塑封)

Laser mark (激光印字)

Laser Cut & package saw Testing

(切割成型)

(测试)

Package (包装)

製造完成

Through Hole Mount

Plastic

2.54 mm (100miles) 1 direction

lead

3~25

Through Hole Mount

ZIP

Zigzag In-line Package

S-DIP

Shrink Dual In-line

Package

封裝型式

Shape

Typical Features

Material Lead Pitch No of I/O

半导体封装制程及其设备介绍

半导体封装制程概述

半导体前段晶圆wafer制程 半导体后段封装测试

封装前段(B/G-MOLD)-封装后段(MARK-PLANT)-测试

封装就是將前製程加工完成後所提供晶圓中之每一顆IC晶粒獨立分離,並外 接信號線至導線架上分离而予以包覆包装测试直至IC成品。

半导体制程

IC制造开始

8 ~40

Plastic

1.0, 0.8, 0.65 mm 4 direction

lead

88~200

Surface Mount

FPG

Flat Package of Glass

LCC

Leadless Chip

Carrier

封裝型式

Shape

Typical Features

Material Lead Pitch No of I/O

1.27, 0.762 mm (50, 30miles)

Ceramic 2, 4 direction lead

20~80

Ceramic

1.27,1.016, 0.762 mm (50, 40, 30

miles)

20~40

Surface Mount

PLCC

Plastic Leaded Chip Carrier

DIP

Dual In-line Package

封 裝 型 式 (PACKAGE)

Shape

Typical Features

Material Lead Pitch No of I/O

Ceramic Plastic

2.54 mm (100miles)

8 ~64

SIP

Single In-line Package

Shape

Typical Features

Material Lead Pitch No of I/O

Ceramic Plastic

2.54 mm (100miles) half-size pitch in the

width direction

24~32

Ceramic Plastic

2.54 mm (100miles)

32~200

SMT (Optional)

Taping (Optional)

Die Saw

Assembly Main Process

Grinding (Optional)

Die Bond

Detaping (Optional)

Die Cure (Optional)

Wafer Mount

Plasma

UV Cure (Optional)

Wire Bond

Molding

Post Moldackage Saw

Cleaner

Memory Test

Card Asy

Card Test

Packing for Outgoing

半导体设备供应商介绍-前道部分

PROCESS

SMT - PRINTER SMT – CHIP MOUNT

Wafer Cutting (晶圆切断)

Wafer Reduce (晶圆减薄)

Etching (蚀刻)

后段封装开始

Diffusion Ion

Implantation (扩散离子植入)

Grind & Dicing (晶圓研磨及切割)

Die Attach (上片)

Oxidization (氧化处理)

Deposition (沉积)

ASM889898 QDM-4S

K&S MAXUM ULTRA UTC-2000 Eagle60 AP1000 TEPLA400

Plastic

2.54 mm (100miles) 1 direction

lead

16~24

Plastic

1.778 mm (70miles)

20 ~64

Through Hole Mount

SK-DIP

Skinny Dual In-line

Package

PBGA

Pin Grid Array

封裝型式

Surface Mount

SOP Small Outline Package

QFP Quad-Flat

Pack

封裝型式

Shape

Typical Features

Material Lead Pitch No of I/O

Plastic

1.27 mm (50miles) 2 direction

lead

TAPING INLINE GRINDER & POLISH

STANDALONE GRINDER DETAPING

WAFER MOUNTER DICING SAW

VENDOR

DEK SIMENS NITTO ACCRETECH DISCO NITTO NITTO DISCO

TSK

MODEL

HOR-2I HS-60 DR3000-III PG300RM 8560 MA3000 MA3000 DFD 6361 A-WD-300T