110nmcmos工艺

SOI_纳米技术时代的高端硅基材料

SOI—纳米技术时代的高端硅基材料林成鲁(中国科学院上海微系统与信息技术研究所;上海新傲科技有限公司,上海 201821) 摘 要: 绝缘体上硅(SOI)是纳米技术时代的高端硅基材料。

详细介绍了SO I在半导体技术领域中的应用,以及近年来为满足SOI的特殊应用要求研发的多种SOI新材料及其制备技术;综述了绝缘体上应变硅(sSO I),绝缘体上锗(GO I)等SO I技术的现状和发展动向;最后,对SOI技术的发展前景进行了展望。

关键词: 高端硅基材料;绝缘体上硅;绝缘体上应变硅;绝缘体上锗中图分类号: TN304 文献标识码: A 文章编号:100423365(2008)0120044206 SOI—Advanced Silicon2B ased Materials for N anotechnology EraL IN Cheng2lu(S hanghai I nstit ute of Microsystem and I nf ormation Technology,T he Chinese A cadem y of S ciences;S hanghai S I M GU I Technology Co.,L t d.,S hanghai201821,P.R.China) Abstract: Silicon2On2Insulator(SOI)is an advanced silicon2based material for Nanotechnology Era.Applications of SOI in microelectronics are described in detail.A variety of novel SOI materials for specific applications is exam2 ined,along with their fabrication technologies.The state2of2the2art of SOI technology,including strained silicon2on2 insulator(sSOI)and germanium2on2insulator(GOI),is reviewed.And finally,the development trend and f uture prospect of SOI technologies are discussed.K ey w ords: Advanced silicon2based material;Silicon on insulator(SOI);Strained silicon on insulator(sSOI) EEACC: 25201 纳米技术时代的高端衬底材料集成电路的特征尺寸在1999年开始缩小到亚100nm,英特尔(Intel)在2006年6月实现了90nm 与65nm的“制造接替”;65nm技术代的微处理器(CPU)由物理栅长仅为35nm的近三亿只金属2氧化膜2半导体场效应晶体管(MOSFET)组成,在芯片生产方面实现了里程碑式的跨越。

CMOS

CMOS课程作业NMOS管的I-V特性及输入输出特性曲线一 NMOS管I-V特性曲线1.NMOS管I-V特性电路图如图一所示:图一 NMOS管I-V特性曲线电路图2.生成网表如下:.title NMOS I-V curve*11微电子赵丽娜学号(后三位):035*Sheet Name:/V2 N-000002 GND 0V1 N-000001 GND 3M1 N-000002 N-000001 GND GND NM L=8U W=2U M=1.MODEL NM NMOS VT0=0.7 KP=110U GAMMA=0.4 LAMBDA=0.04 PHI=0.7 .DC V2 0 5 0.01.plot dc i(M1).op.probe.end3.仿真图如下:图二 NMOS管I-V特性曲线仿真流程图一图三 NMOS管I-V特性曲线仿真流程图二图四 NMOS管I-V特性曲线仿真流程图三图五 NMOS管I-V特性曲线(0-5V)若nmos漏极电压由0-5V变为0-10V,则会出现击穿,但由于我们使用的为理想模型,所以还是和之前趋势相同。

仿真后I-V特性如下图(此图为0-200V):图六 NMOS管I-V特性曲线(0-200V)二 NMOS管的输入输出特性1.NMOS管的输入输出特性电路图如下图所示:图七 NMOS管的输入输出特性曲线电路图2.网表如下:.title nmos IN–OUT curve*11微电子赵丽娜学号(后三位):035*Sheet Name:/V2 4 0 5*源极电阻电压为5伏特不变V1 2 0 0R1 4 3 10KM1 3 2 0 0 NM L=20U W=0.18U 3200*3 2 0 0依次表示mos管的漏、栅、源、衬底的节点编号(3 代表漏极).MODEL NM NMOS VT0=0.7 KP=110U GAMMA=0.4 LAMBDA=0.04 PHI=0.7.DC V1 0 5 0.1*栅极电压从0变到5.plot dc v(3)*输出漏极电压也就是vout.op选中的东西自己写的.end3.仿真进行仿真过程如图所示:图八 NMOS管的输入输出特性仿真流程图4.NMOS管的输入输出特性曲线图九 NMOS管的输入输出特性曲线(0-5V)图十 NMOS管的输入输出特性曲线(0-20V)。

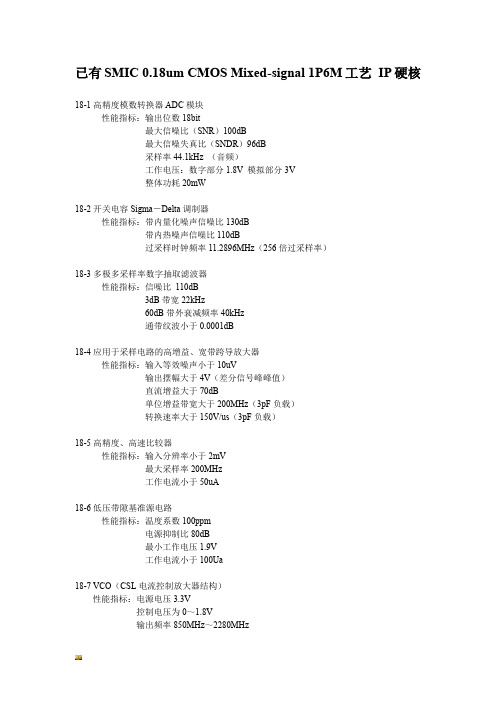

新版已有SMIC 0.18um CMOS Mixed-signal 1P6M工艺 IP硬核汇总441.doc

已有SMIC 0.18um CMOS Mixed-signal 1P6M工艺IP硬核18-1高精度模数转换器ADC模块性能指标:输出位数18bit最大信噪比(SNR)100dB最大信噪失真比(SNDR)96dB采样率44.1kHz (音频)工作电压:数字部分1.8V 模拟部分3V整体功耗20mW18-2开关电容Sigma-Delta调制器性能指标:带内量化噪声信噪比130dB带内热噪声信噪比110dB过采样时钟频率11.2896MHz(256倍过采样率)18-3多极多采样率数字抽取滤波器性能指标:信噪比110dB3dB带宽22kHz60dB带外衰减频率40kHz通带纹波小于0.0001dB18-4应用于采样电路的高增益、宽带跨导放大器性能指标:输入等效噪声小于10uV输出摆幅大于4V(差分信号峰峰值)直流增益大于70dB单位增益带宽大于200MHz(3pF负载)转换速率大于150V/us(3pF负载)18-5高精度、高速比较器性能指标:输入分辨率小于2mV最大采样率200MHz工作电流小于50uA18-6低压带隙基准源电路性能指标:温度系数100ppm电源抑制比80dB最小工作电压1.9V工作电流小于100Ua18-7 VCO(CSL电流控制放大器结构)性能指标:电源电压3.3V控制电压为0~1.8V输出频率850MHz~2280MHz功耗6.6mW。

相位噪声仿真值-78dBc@1MHz,测试值为-65dBc@1MHz。

18-8. VCO(差分环型振荡器结构)性能指标:电源电压1.8V控制电压为0~1.5V输出频率1.33GHz~1.93GHz功耗36mW相位噪声仿真值-107dBc@1MHz,测试值为-89dBc@1MHz。

18-9. 射频分频器性能指标:电源电压1.8V,最高工作频率2.3GHz。

18-10. 鉴频鉴相器性能指标:电源电压1.8V,无死区,操作频率仿真值500MHz。

对输入信号的占空比没有要求,引入噪声低。

最新—高精度cmos带隙基准源的

—高精度c m o s带隙基准源的摘要基准电压源是模拟电路设计中广泛采用的一个关键的基本模块。

所谓基准电压源就是能提供高稳定度基准量的电源,这种基准源与电源、工艺参数和温度的关系很小,但是它的温度稳定性以及抗噪性能影响着整个电路系统的精度和性能。

本文的目的便是设计一种高精度的CMOS带隙基准电压源。

本文首先介绍了基准电压源的国内外发展现状及趋势。

然后详细介绍了带隙基准电压源的基本结构及基本原理,并对不同的带隙基准源结构进行了比较。

接着对如何提高带隙基准的电源抑制比以及带隙基准电压源的温度补偿原理进行了分析,还总结了目前提高带隙基准电压源温度特性的各种方法。

在此基础上运用曲率校正、内部负反馈电路、RC滤波器、快速启动电路,设计出了具有良好的温度特性和高电源抑制比的带隙基准电压源电路。

最后应用HSPICE仿真工具对本文中设计的带隙基准电压源电路进行了完整模拟仿真并分析了结果。

模拟和仿真结果表明,电路实现了良好的温度特性和高电源抑制比,0℃~100℃温度范围内,基准电压温度系数大约为11.2ppm/℃,在1Hz到10MHz频率范围内平均电源抑制比(PSRR)可达到-80dB,启动时间为700s 。

关键词: 带隙基准电压源;温度系数;电源抑制比;AbstractVoltage reference is the vital basic module which is widely adopted in analog circuits. It can supply a voltage with high stability. The power supply, technics parameter rand temperature has lesser effete to this voltage. Its temperature stability and antinoise capability influence the precision and performance of the whole system. The purpose of this article is to design a high precision CMOS bandgap voltage reference.In this article, the present situation and developmental trend of voltage reference studies both at home and abroad are presented. The structure and principle of voltage reference are analyzed in detail, and then the different structures of bandgap voltage reference are compared. By analyzing the power supply rejection ratio (PSRR) and the principle of temperature compensation, the method of improving the temperature characteristic is summarized. The design of a bandgap voltage reference circuit with high power supply rejection ratio and good temperature characteristic is completed by applying curvature emendation, inside negative feedback technology, RC filter and fast start-up circuit. At last, the circuits have been simulated with HSPICE simulation tools.The simulation results show that,the circuit with good temperature characteristic and high power supply rejection ratio, and at the temperature range of 0℃ to 100℃, the temperature coefficient(TC) is about 11.2ppm/℃. In the frequency range of 1Hz to 10MHz, the average power supply rejection ratio is more than -80dB and it has a turn-on time less than 700s .Key Words: bandgap voltage reference; temperature coefficient; power supply rejection ratio;目录摘要 (I)Abstract....................................................... I I 1.绪论 (1)1.1 国内外研究现状与发展趋势 (1)1.2 课题研究的目的意义 (2)1.3 本文的主要内容 (2)2. 基准电压源的原理与电路 (3)2.1 基准电压源的结构 (3)2.1.1直接采用电阻和管分压的基准电压源 (3)2.1.2有源器件与电阻串联组成的基准电压源 (4)2.1.3带隙基准电压源 (6)2.2 带隙基准电压源的基本原理 (6)2.2.1与绝对温度成正比的电压 (7)2.2.2负温度系数电压V BE (7)2.3 带隙基准源的几种结构 (8)2.4 V BE的温度特性 (11)2.5 带隙基准源的曲率校正方法 (13)2.5.1线性补偿 (13)2.5.2高阶补偿 (13)本章小结 (17)3. 高精度CMOS带隙基准源的电路设计与仿真 (18)3.1 高精度CMOS带隙基准电压源设计思路 (18)3.2 核心电路 (19)3.3 提高电源抑制比电路 (20)3.3.1负反馈回路 (21)3.3.2 RC滤波器 (22)3.4 快速启动电路及快速启动电路的控制电路 (23)3.4.1快速启动电路的控制电路 (23)3.4.2快速启动电路 (24)3.5 CMOS带隙基准电压源的温度补偿原理 (24)3.6 高精度CMOS带隙基准电压源的电路仿真 (27)3.6.1仿真工具的介绍 (27)3.6.2核心电路的仿真结果 (27)3.6.3电源抑制比电路的仿真结果 (28)3.6.4快速启动电路的仿真结果 (28)3.6.5整体电路的仿真结果 (29)本章小结 (30)结论 (32)致谢 (33)参考文献 (34)1.绪论基准电压源(Reference V oltage)是指在模拟电路或混合信号电路中用作电压基准的具有相对较高精度和稳定度的参考电压源。

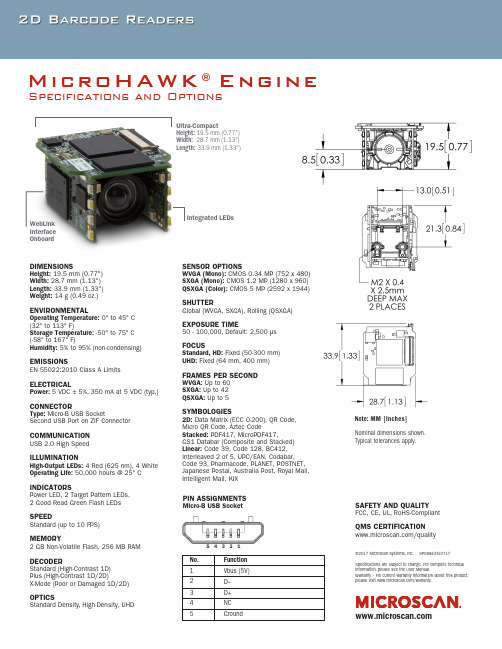

CMOS传感器选项及相关参数说明书

SENSOR OPTIONSWVGA (Mono): CMOS 0.34 MP (752 x 480)SXGA (Mono): CMOS 1.2 MP (1280 x 960)QSXGA (Color): CMOS 5 MP (2592 x 1944)SHUTTERGlobal (WVGA, SXGA), Rolling (QSXGA)EXPOSURE TIME 50 - 100,000, Default: 2,500 μs FOCUSStandard, HD: Fixed (50-300 mm)UHD: Fixed (64 mm, 400 mm)FRAMES PER SECONDWVGA: Up to 60SXGA: Up to 42QSXGA: Up to 5SYMBOLOGIES2D: Data Matrix (ECC 0-200), QR Code, Micro QR Code, Aztec CodeStacked: PDF417, MicroPDF417, GS1 Databar (Composite and Stacked)Linear: Code 39, Code 128, BC412, Interleaved 2 of 5, UPC/EAN, Codabar, Code 93, Pharmacode, PLANET, POSTNET, Japanese Postal, Australia Post, Royal Mail, Intelligent Mail, KIXPIN ASSIGNMENTSMicro-B USB SocketNo. Function 1 Vbus (5V) 2 D – 3 D+ 4 NC 5GroundMicroHAWK ®EngineUltra-CompactHeight: 19.5 mm (0.77")Width: 28.7 mm (1.13")Length: 33.9 mm (1.33")Integrated LEDsWebLinkInterfaceOnboardSpecifications and OptionsNote: MM [Inches]Nominal dimensions shown. Typical tolerances apply.DIMENSIONSHeight: 19.5 mm (0.77") Width: 28.7 mm (1.13") Length: 33.9 mm (1.33") Weight: 14 g (0.49 oz.)ENVIRONMENTALOperating Temperature: 0° to 45° C (32° to 113° F)Storage Temperature: -50° to 75° C (-58° to 167° F)Humidity: 5% to 95% (non-condensing)EMISSIONSEN 55022:2010 Class A LimitsELECTRICALPower: 5 VDC ± 5%, 350 mA at 5 VDC (typ.)CONNECTORType: Micro-B USB SocketSecond USB Port on ZIF ConnectorCOMMUNICATIONUSB 2.0 High SpeedILLUMINATIONHigh-Output LEDs: 4 Red (625 nm), 4 White Operating Life: 50,000 hours @ 25° CINDICATORSPower LED, 2 Target Pattern LEDs, 2 Good Read Green Flash LEDsSPEEDStandard (up to 10 FPS)MEMORY2 GB Non-Volatile Flash, 256 MB RAMDECODERStandard (High-Contrast 1D)Plus (High-Contrast 1D/2D)X-Mode (Poor or Damaged 1D/2D)OPTICSStandard Density, High-Density, UHD©2017 Microscan Systems, Inc. SP088E-EN-0717Specifications are subject to change. For complete technical information, please see the User Manual.Warranty – For current warranty information about this product,please visit /warranty.SAFETY AND QUALITY FCC, CE, UL, RoHS-Compliant QMS CERTIFICATION/qualityM icro HAWK ®E nginE F iEld oF V iEW And r EAd r AngE c HArtsWVGA Sensor Read RangesSXGA Sensor Read RangesExample Read Range:Example Read Range:Example Read Range:UHD Read RangesNote: Minimum 1D element is typically 1/2 the size of minimum 2D element. Example: 10 mil 2D = 5 mil 1D.。

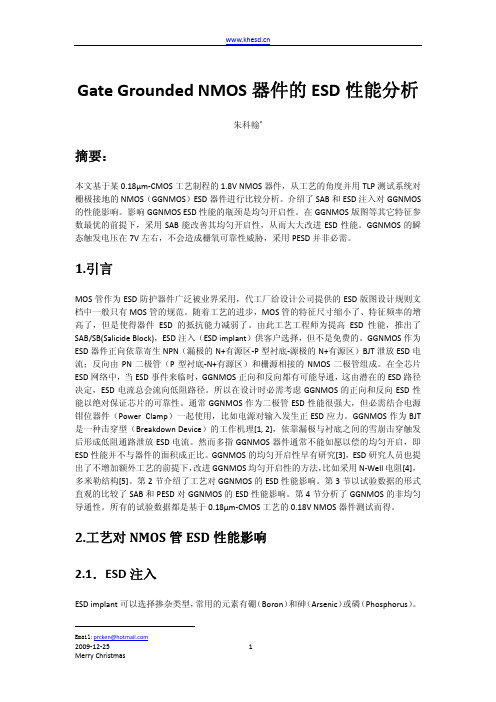

GGNMOS

Gate Grounded NMOS器件的ESD性能分析朱科翰∗摘要:本文基于某0.18μm‐CMOS工艺制程的1.8V NMOS器件,从工艺的角度并用TLP测试系统对栅极接地的NMOS(GGNMOS)ESD器件进行比较分析。

介绍了SAB和ESD注入对GGNMOS 的性能影响。

影响GGNMOS ESD性能的瓶颈是均匀开启性。

在GGNMOS版图等其它特征参数最优的前提下,采用SAB能改善其均匀开启性,从而大大改进ESD性能。

GGNMOS的瞬态触发电压在7V左右,不会造成栅氧可靠性威胁,采用PESD并非必需。

1.引言MOS管作为ESD防护器件广泛被业界采用,代工厂给设计公司提供的ESD版图设计规则文档中一般只有MOS管的规范。

随着工艺的进步,MOS管的特征尺寸缩小了、特征频率的增高了,但是使得器件ESD的抵抗能力减弱了。

由此工艺工程师为提高ESD性能,推出了SAB/SB(Salicide Block),ESD注入(ESD implant)供客户选择,但不是免费的。

GGNMOS作为ESD器件正向依靠寄生NPN(漏极的N+有源区‐P型衬底‐源极的N+有源区)BJT泄放ESD电流;反向由PN二极管(P型衬底‐N+有源区)和栅源相接的NMOS二极管组成。

在全芯片ESD网络中,当ESD事件来临时,GGNMOS正向和反向都有可能导通,这由潜在的ESD路径决定,ESD电流总会流向低阻路径。

所以在设计时必需考虑GGNMOS的正向和反向ESD性能以绝对保证芯片的可靠性。

通常GGNMOS作为二极管ESD性能很强大,但必需结合电源钳位器件(Power Clamp)一起使用,比如电源对输入发生正ESD应力。

GGNMOS作为BJT 是一种击穿型(Breakdown Device)的工作机理[1, 2],依靠漏极与衬底之间的雪崩击穿触发后形成低阻通路泄放ESD电流。

然而多指GGNMOS器件通常不能如愿以偿的均匀开启,即ESD性能并不与器件的面积成正比。

MEMS工艺(5表面硅加工技术)

表面微加工

表面微加工技术主要靠在基底上逐 层添加材料而构造微结构

表面微加工器件是由三种典型的部 件组成:⑴牺牲层;⑵微结构层; ⑶绝缘层部分

基本概念

在微机械加工中,通常将两层薄膜中的下 面一层腐蚀掉,只保留上面的一层,这种 技术称为牺牲层腐蚀,又称为分离层腐蚀。 利用牺牲层腐蚀技术直接在衬底表面制作 微机械元件结构的技术被称为“硅表面微 机械加工技术”。

不同淀积方法生成的二氧化硅性质表

。)

PECVD 200℃ SiO1。9(H) 可变(Adams 说 不一致) 失氢 2.3 1.47 300(压)到300 (拉) 3到6

淀积类型 典型温度 成分 台阶覆盖率 热稳定性 密度(g/cm3) 折射率 应力(Mpa) 电介质强度 (106V/cm或 102V/μm) 腐蚀速率 (nm/min)(H2O: HF=100:1)

多晶硅材料的主要特点 (2)多晶硅薄膜对生长衬底的选择不 苛刻。衬底只要有一定的硬度、平整度 及能耐受住生长工艺温度即可。 (3)可以通过对生长条件及后工艺的 控制来调整多晶硅薄膜的电阻率,使它 成为绝缘体、导体或半导体,从而适应 不同器件或器件不同部分的需要。

多晶硅材料的主要特点

(4)多晶硅薄膜作为半导体材料 可以像单晶硅那样通过生长、扩散 或离子注入进行掺杂,形成N型或 P型半导体,制成p-n结;可以采用 硅平面工艺进行氧化、光刻、腐蚀 等加工。

二氧化硅当然是硅加工实验室中最常用的 介质。它可以自身生长,也可以淀积,有 无掺杂剂都行,既使掺杂后仍然绝缘。

热生长型SiO2常用作MOS门绝缘层。如 果淀积的SiO2 中掺入磷,那就叫做磷硅 玻璃、“P玻璃”或PSG,它常用作最终 钝化层;

如果掺入硼,那就叫做硼硅玻璃或BSG;如 果在玻璃中掺入磷和硼的混合物,则常称为 BPSG或低温氧化物(LTO),它具有良好 的低温回流特性,可使高深宽比表面结构 “光洁化”或平面化。 在IC工艺中,SiO2是一种多用途的基本材料, 它通过热氧化生长和为满足不同要求采用不 同工艺淀积获得。

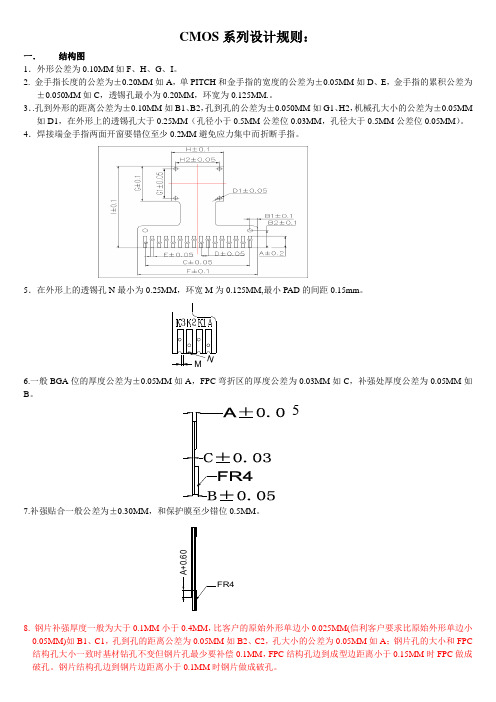

CMOS系列设计规则

CMOS 系列设计规则:一. 结构图1.外形公差为0.10MM 如F 、H 、G 、I 。

2. 金手指长度的公差为±0.20MM 如A ,单PITCH 和金手指的宽度的公差为±0.05MM 如D 、E ,金手指的累积公差为±0.050MM 如C ,透锡孔最小为0.20MM ,环宽为0.125MM.。

3..孔到外形的距离公差为±0.10MM 如B1、B2,孔到孔的公差为±0.050MM 如G1、H2,机械孔大小的公差为±0.05MM 如D1,在外形上的透锡孔大于0.25MM (孔径小于0.5MM 公差位0.03MM ,孔径大于0.5MM 公差位0.05MM )。

4.焊接端金手指两面开窗要错位至少0.2MM 避免应力集中而折断手指。

5.在外形上的透锡孔N 最小为0.25MM ,环宽M 为0.125MM,最小PAD 的间距0.15mm 。

6.一般BGA 位的厚度公差为±0.05MM 如A ,FPC 弯折区的厚度公差为0.03MM 如C ,补强处厚度公差为0.05MM 如B 。

7.补强贴合一般公差为±0.30MM ,和保护膜至少错位0.5MM 。

8. 钢片补强厚度一般为大于0.1MM 小于0.4MM ,比客户的原始外形单边小0.025MM(信利客户要求比原始外形单边小0.05MM)如B1、C1,孔到孔的距离公差为0.05MM 如B2、C2,孔大小的公差为0.05MM 如A ;钢片孔的大小和FPC 结构孔大小一致时基材钻孔不变但钢片孔最少要补偿0.1MM ,FPC 结构孔边到成型边距离小于0.15MM 时FPC 做成破孔。

钢片结构孔边到钢片边距离小于0.1MM 时钢片做成破孔。

治具针不用减小):2mm区域内(如下),如有特殊情况连接位区域需要改变请在制作图纸时在图纸上注明连接位区域尺寸(如钢片外形尺寸只有3mm时连接位区域改为1.5mm等)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

110nmcmos工艺

110nm CMOS工艺

简介

•110纳米(nm)CMOS工艺是一种微电子制造工艺,用于制造集成电路(IC)。

•CMOS是互补金属氧化物半导体(Complementary Metal-Oxide-Semiconductor)的缩写。

概述

•110nm CMOS工艺是在110纳米尺寸上制造电子器件和电路的一种高度先进的工艺。

•它具有以下特点:

–高度集成:该工艺允许在单个芯片上集成大量的晶体管和其他电子器件。

–低功耗:CMOS工艺可以提供低功耗和高能效的电路设计。

–高性能:110nm CMOS工艺可以支持高速操作和大容量存储。

–可靠性:该工艺具有较高的电路可靠性和长时间稳定性。

应用领域

110nm CMOS工艺在许多领域中得到广泛应用,包括但不限于:

•通信技术:用于制造无线通信芯片、射频电路和高速数据传输设备。

•汽车电子:用于制造汽车控制系统、驱动电路和安全装置。

•消费电子:用于制造智能手机、平板电脑、数字相机等消费电子产品。

•工业控制:用于制造过程控制、自动化和机器人技术。

•医疗器械:用于制造医疗成像设备、心脏起搏器和生物传感器。

•军事应用:用于制造军事雷达、导航系统和通信设备。

未来发展

随着科技的不断进步,110nm CMOS工艺正在被更先进的工艺所取代,例如90nm、65nm、45nm等。

这些更小的工艺尺寸能够实现更高的

集成度和更低的功耗。

然而,110nm CMOS工艺仍然在一些特定领域内

有其独特的优势,因此在一段时间内仍然具备一定的市场需求。

结论

110nm CMOS工艺是一种可靠、高性能和低功耗的微电子制造工艺。

它在通信技术、汽车电子、消费电子、工业控制、医疗器械和军事应

用领域等多个领域中得到广泛应用。

尽管新的工艺不断涌现,但110nm

CMOS工艺仍然具有自己的优势和市场需求,在特定领域中将继续发挥重要作用。

优势

110nm CMOS工艺具有以下优势:

•可靠性:该工艺在电路的长时间运行和稳定性方面表现出色。

•成熟度:110nm CMOS工艺是一种成熟的工艺,具有可靠的制造流程和良好的规模经济效益。

•性价比:相对于更先进的工艺,110nm CMOS工艺提供了更高的性价比,适用于一些成本敏感的应用。

•设计周期短:由于该工艺已经经过广泛验证和使用,设计人员可以更快速地实现他们的设计,加快产品上市时间。

•可用性:由于长时间的使用,该工艺在制造方面可获得更多的技术支持和资源。

挑战

虽然110nm CMOS工艺具有许多优势,但也面临一些挑战:

•功耗:相对于更先进的工艺,110nm CMOS工艺的功耗相对较高,不适用于某些低功耗应用。

•集成度限制:110nm CMOS工艺不适用于需要更高集成度的应用,因为器件尺寸相对较大。

•效能限制:相对于更高级的工艺,110nm CMOS工艺在频率和性能方面存在一定的限制。

结语

110nm CMOS工艺作为一种成熟的制造工艺,已经在多个领域中得到广泛应用。

它具有可靠性、成熟度和性价比等优势。

尽管面临一些挑战,但110nm CMOS工艺仍然在特定领域内具备市场需求。

随着技术的不断发展,我们预计更先进的工艺将取代110nm CMOS工艺,但它的应用将延续一段时间,并为特定应用场景带来价值。