IC版图闩锁预防

版图绘制及Virtuoso工具软件

GDS文件操作

28/ 103

Display Control Window

工艺流程

Design Rule

Virtuoso软件

PDK简介

版图设计

GDS文件操作

29/ 103

Virtuoso下快捷键的使用

• • • • • • • • • • • • • Ctrl+A 全选 Shift + X,进入子模块 Shift + B,升到上一级视图 Ctrl + C 中断某个命令,一般用 ESC代替 Shift + C 裁切(chop) C 复制,复制某个图形 Ctrl + D 取消选择。亦可点击空白 处实现。 Ctrl + F显示上层等级 Shift + F显示所有等级 F fit,显示你画的所有图形 K 标尺工具 Shift + K清除所有标尺 L 标签工具 Design Rule Virtuoso软件 M 移动工具 Shift + M 合并工具,Merge N 斜45对角+正交 Shift + O 旋转工具, Rotate O 插入接触孔 Ctrl + P 插入引脚, Pin Shift + P 多边形工具, Polygon P 插入Path(路径) Q 图形对象属性(选中一个图形先) R 矩形工具, 绘制矩形图形 S 拉伸工具, 可以拉伸一个边,也可 以选择要拉伸的组一起拉伸 • U 撤销, Undo • Shift + U重复, Redo, 撤销后反悔 • • • • • • • • • • •

工艺流程

Design Rule

Virtuoso软件

PDK简介

版图设计

GDS文件操作

40/ 103

反相器电路版图及特性

5、驱动大负载(Driving Large Loads)

Cload = 20pF

多级驱动用于改善大负载时

的开关时间. 1

比例因子可以用:

A

Cload Cin1

N

优化的驱动级的数目可以用 公式表示:

N ln Cload Cin1

Yellow Green Green Red Blue Magenta Black Black Black

Representation

Intra-Layer Design Rules(设计规则)

规定各层次的最小宽度和最小间距,相关层次之间的最 小间距.

Same Potential

Well Active

ßn= ßp

则必须要满足 (W/L)p=3(W/L)n

2、反相器的时序特性

(1)Rise and Fall times are measured between the 10% and 90% points in a transition. (tr 和tf 的定义)

(2)Delay time is measured between the 50% point in the input and the 50% point in the output.

4、闩锁效应(Latch-up)

此尖峰可以导致闩锁效应(latch-up). 通 管Q过2C导2通电.容的下降沿尖峰使得晶体 电流流经晶体管 Q2 导致RW1 和 RW2

上的电压下降 ,并使得Q1管导通. 流 RS经2 上晶产体生管压Q降1 的,使电得流Q在2进电一阻步R导S1通和. 通过C1的上升沿尖峰具有和前面同

一种ESD保护电路的版图设计

课程名称:集成电路版图设计穿、抗闩锁、寄生小、面积小、工艺兼容等特点[6,7],且在深亚微米互补性氧化金属半导体CMOS工艺中,ESD保护电路由于要承受大电流或大电压的保护,通常把管子做得比较大,以实现I/O输入输出ESD保护、电源钳位ESD 保护和轨到轨ESD保护。

因此ESD保护电路的设计需要结合实际情况与应用需求,再综合考虑以上各个因素,才能设计出具有较好鲁棒性指标的保护电路。

除了要有较好鲁棒性的ESD保护电路外,我们还需注意一些外接引脚所引起的静电效应,做到电路(软件)和硬件的完美结合。

在集成电路的引脚中,除了少数一些自己能抵抗ESD 的引脚外,我们都需要将他们接到衬底或扩散层上去,比如说NPN 管的集电极,这些面积较大的结能在静电荷聚积到足以破坏器件之前吸收掉它们。

而在提供电源或大功率的引脚上,我们可以多接一些扩散层。

又由于那些直接连接到MOS 管栅极的的引脚很容易形成ESD 的介电体,因此必须有一些特别的保护结构设计在这些引脚上,比如我们可以用一些大的电阻(500Ω~5KΩ)或者是使电流不经过没有任何连接的发射极而直接接到外部的衬底上[8]。

3.2传统的静电保护电路和版图设计传统的方法是利用了TVS二极管的特性来保护电路免受ESD的冲击。

TVS全称是瞬态抑制二极管(Transient V oltage Suppressor),是一种二极管形式的高效能保护器件。

当TVS二极管的两极受到反向瞬态高能量冲击时,它能以10的负12次方秒量级的速度,将其两极间的高阻抗变为低阻抗,吸收高达数千瓦的浪涌功率,使两极间的电压箝位于一个预定值,有效地保护电子线路中的精密元器件,免受各种浪涌脉冲的损坏。

图1 电路中的TVS二极管如图2所示,传统的静电保护电路一般设计在芯片的管脚旁边,静电保护源和地,这样保证PMOS 和NMOS 在芯片正常工作时候处于关闭状态,这种类型的静电保护电路存在二个寄生二极管(TVS),当IO 到VCC 放生正静电时候,静电通过上面的寄生二极管正向通道泄放,当IO 到GND发生正静电时候,N+(漏端)-P+(衬底)-N+(源端)形成寄生NPN,静电通过这个寄生三极管泄放,当IO 到GND 发生负静电时候,静电通过下面的寄生二极管正向导通泄放,当IO 到VCC 放生负静电时候,静电没有合适的泄放通路。

集成电路版图设计

思考题

1. MOS管沟道的宽长比(W/L)如何确定? 2. MOS管沟道的宽度(W)和长度(L)如何 确定? 3. MOS管源漏区尺寸如何确定?

HIT Micro-Electronics Center

2004年8月

3

HMEC

集成电路设计原理

微电子中心

6.1.1 MOS管宽长比(W/L)的确定 VDD 1. NMOS逻辑门电路 (1)NMOS逻辑门电路是有比电路, ML 根据VOL的要求,确定最小R 。 Vi Vo 2 MI (VDD VTL ) VOL E/E饱和负载 2R(VOHVTI) VTD 2 VDD VOL 2 (V V ) E/D OH TE R MD (2) 根据负载CL情况和速度要求(tr Vo 和tf) 确定负载管和等效输入管的 ME Vi 最小W/L 。

HIT Micro-Electronics Center

2004年8月 21

HMEC

集成电路设计原理

微电子中心

6.2.3 优化设计 4. 复用单元的设计 将常用结构的 组合图形(包括电 路单元)按设计规 则要求设计为可复 用的单元,供设计 过程中调用, 减少设计错 误,并便于 修改。

HIT Micro-Electronics Center

HIT Micro-Electronics Center

2004年8月

10

HMEC

集成电路设计原理

微电子中心

6.1.4 MOS管源漏区尺寸的确定

一般是根据MOS管的沟道宽度W和相 关的设计规则来确定源漏区最小尺寸。 源漏区尺寸越小,寄生电容以及漏电 就越小。

MOS管的源漏区具有可互换性

HIT Micro-Electronics Center

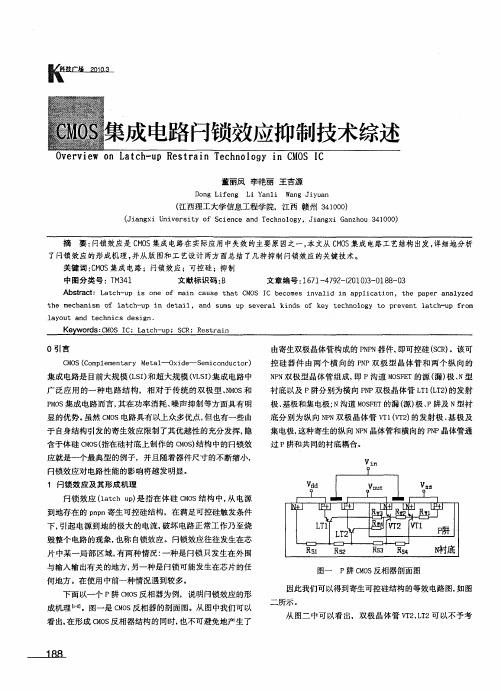

CMOS集成电路闩锁效应抑制技术

CMOS集成电路闩锁效应抑制技术董丽凤;李艳丽;王吉源【摘要】闩锁效应是CMOS集成电路在实际应用中失效的主要原因之一,而且随着器件特征尺寸越来越小,使得CMOS电路结构中的闩锁效应日益突出.文章以P 阱CMOS反相器为例,从CMOS集成电路的工艺结构出发,采用可控硅等效电路模型,较为详细地分析了闩锁效应的形成机理,给出了闩锁效应产生的三个基本条件,并从版图设计和工艺设计两方面总结了几种抑制闩锁效应的关键技术.【期刊名称】《电子与封装》【年(卷),期】2010(010)009【总页数】3页(P28-30)【关键词】CMOS集成电路;闩锁效应;可控硅;抑制【作者】董丽凤;李艳丽;王吉源【作者单位】江西理工大学信息工程学院,江西,赣州,341000;江西理工大学信息工程学院,江西,赣州,341000;江西理工大学信息工程学院,江西,赣州,341000【正文语种】中文【中图分类】TM341CMOS(Complementary Metal-Oxide-Semiconductor)集成电路是目前大规模(LSI)和超大规模(VLSI)集成电路中广泛应用的一种电路结构,相对于传统的双极型、NMOS和PMOS集成电路而言,其在功率消耗、噪声抑制等方面具有明显的优势,虽然CMOS电路具有以上众多优点,但也有一些由于自身结构引发的寄生效应限制了其优越性的充分发挥,隐含于体硅CMOS(指在硅衬底上制作的CMOS)结构中的闩锁效应就是一个最典型的例子,并且随着器件尺寸的不断缩小,闩锁效应对电路性能的影响将愈发明显。

闩锁效应(latch up)是指在体硅CMOS结构中,从电源到地存在的PNPN寄生可控硅结构,在满足可控硅触发条件下,引起电源到地的极大电流,破坏电路正常工作乃至烧毁整个电路的现象,也称自锁效应。

闩锁效应往往发生在芯片中某一局部区域,有两种情况:一种是闩锁只发生在外围与输入输出有关的地方,另一种是闩锁可能发生在芯片的任何地方,在使用中前一种情况遇到较多。

CMOS集成电路闩锁效应抑制技术综述

由寄生双极 晶体管构成 的 P P N N器件 , 即可控硅 (C ) SR 。该可

控硅 器件 由两个 横 向的 P P双极 型 晶体管 和两 个纵 向的 N NN双 极型晶体管 组成, P沟道 M S E P 即 OF T的源 ( 极 、 漏) N型

集成 电路是 目前大规模 (S ) L I 和超大规模 (L I 集成 电路 中 V S)

~

O e v e n a c - p R s r i e h o o Y n C O I v r i w o L t h u e t a n T c n l 9 i M S C

董丽凤 李艳丽 王 吉源

D g on Li en Li f g Yanl W ng i a di u y an

l yo a ut and ec t hni s c de gn. si

K y r s: M S C L t h u e wo d C O I ; a c - p; S R;R s r i C e ta n

0引 言

C O c m l m n a y M t l- x d - S m c n u tr M S(o p e e tr e a- O i e e io d c o ) -

R

{ =. If l ,, l

f

n成 集 c , )

电

\ f= z ., :

式 () I I 2 甲 较小, 凼此有 :

I

。

路

锁

“r ‘ r 1

0I 工R ,I ,

’ss

以 pI = (II- , c [ l z广 ( I  ̄T 厂 -

中 图 分 类 号 :T 3 1 M4 文 献 标 识 码 : B 文 章 编 号 : 6 1 4 9 -2 1 )- 1 8 0 l 7 - 72 (0 03 0 8 - 3

CMOS电路中的闩锁效应研究

MO 部分 S : 双极部 分

一

开启状态 ( ac u ) L th p

一 作点2 I

一 ~

・ ・

闭状态

.

.

5 S R器件 的 I 冈 C V

—

Rw l I

由图 5 以总结 出产生 L th p的必要条件 : 可 a u c

L th p的测试 方法一般分两类 ,即电流触发 和 ac u 电压触发。

间产生很大 的电流 。 此时该电路即被闩锁。

续下去 , 直至两个晶体管都完全导通, 在 。 ’ 之 到/ S

我们再 来看该 S CR器件 的 I 图 ( 5) V 图 。

,

T作点 1

图 2 叠加寄生双极晶体管的反相器剖面图

由此 我们得 到了N阱 C MOS 反相 器的完整等效 电

冈 1 N阱反相器纵 向结构图

2 闩锁效应 的原理

我们 以一个最基本 的N阱 C MOS 反相器为例 。其 纵 向结 构如 图 1 示 。 所 在形成 C S MO 反相器结构的同时 , 也必然形成 由 寄生 双级 晶体 管构 成 的 P N 器件 ,即可控硅 器件 NP

可 以看 出 ,在 图 2中 : ( )有两个纵 向 P P晶体管和两个横 向 NP 1 N N晶

( ) SCR ,如 图 2。

1 引言

最初的几代 MOS 工艺仅提供 N S器件 ,而随 MO 着C MOS技术时代 的到来 ,一个新 的问题也随之诞 生 ,这就是 闩锁效 应 ( ac u o闩锁效应是 指在 L th p

芯片 的电源和地之间存 在一个低阻抗 的通路 ,产生很 大 的电流 ,导致 电路 无法正常工 作 ,甚至烧毁 电路 。 下文将对这一现象做具体 的分析 。

MOS晶体管及其版图

MOS晶体管及其版图第四章 MOS晶体管及其版图学习指导学习⽬标与要求1.了解集成电路中有源器件MOS晶体管的结构2.了解集成电路中有源器件MOS晶体管版图定义、内涵及实质,掌握集成电路中有源器件MOS晶体管版图的特点3.掌握集成电路中有源器件MOS晶体管的特性、不同类型MOS晶体管版图设计及MOS晶体管版图的失配及匹配的设计技巧4.基本掌握集成电路中有源器件MOS晶体管版图设计⽅法学习重点1.集成电路中有源器件MOS晶体管的特性2.不同类型MOS晶体管版图设计及MOS晶体管版图的失配及匹配的设计技巧学习难点1.MOS晶体管版图设计技巧及设计⽅法2.MOS晶体管版图的失配及匹配的设计⽅法及设计准则第⼀节 NMOS 晶体管及版图⼀、 N MOS 晶体管概述1. NMOS 晶体管的简化三端电路模型:NMOS 晶体管在栅极和晶体管的其余部分之间存在绝缘层,没有直流电流从栅极流过。

电容CGS 和CGD 分别代表由栅介质产⽣的栅源电容和栅漏电容。

电容符号上绘制的斜线表⽰电容值的⼤⼩与偏置有关。

压控电流源I1为栅氧化层下从漏极经过沟道流向源极的电流。

漏极电压ID 的⼤⼩取决于栅源电压VGS 和栅漏电压VDS 。

2. 2种类型的NMOS 晶体管:(A)增强型NMOS;(B)耗尽型NMOS3. 器件跨导k 决定了在给定Vgst 的情况下流过MOS 管的漏极电流⼤⼩,可表明⼀个MOS管的尺⼨。

器件跨导的单位是A/V2或者µA/V 2。

k’是⼀个常数,叫做⼯艺跨导,为载流⼦的有效迁移率,。

4. 阈值电压Vt 是指当背栅与源极连接在⼀起时使能栅介质下⾯恰好产⽣沟道所需要的栅源电压。

MOS 管的阈值电压与以下因素有关:栅极电材料,背栅掺杂,栅氧化层厚度,表⾯态电荷密度,氧化层中的电荷密度(固定点荷和可⽤电荷)。

(A) (B)k k'(/)W L =n r k 'ox t οµεε=⼆、 NMOS 晶体管的版图1. ⾃对准硅栅NMOS 晶体管的背栅由⽣长在P+衬底上的P 型外延层构成。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

龙源期刊网 http://www.qikan.com.cn

IC版图闩锁预防

作者:贺雪群

来源:《数字技术与应用》2019年第03期

龙源期刊网 http://www.qikan.com.cn

摘要:在版图设计当中,latch-up闩锁是比较常见的现象。电路设计上有可能自然形成,

但版图设计中更容易形成这种结构。除了普通情况下形成的latch-up结构,我们还有可能碰到

比较特殊的情况,比如管子的SUB为衬切的情况,这种情况下稍有不慎就会形成latch-up闩

锁。

关键词:衬切;latch-up;衬切管

中图分类号:TN4 文献标识码:A 文章编号:1007-9416(2019)03-0109-01

1 普通情况下预防闩锁

在版图设计当中,闩锁是比较常见的现象。如图1所示,两个普通的CMOS管子的扩散

区相互之间形成了寄生的VPNP和LNPN,它们与寄生电阻、构成了图1(B)中的结构。在

非正常情况下,如果某一个寄生管开启,比如Q1,则流过Q1的电流会开启Q2,它们相互之

间提供基极电流,并在Q1、Q2的放大倍数的情况下维持这个过程,直至切断电源。

一般情况下,我们可以通过以下几种方法来防止latch-up现象的发生:

(1)PMOS的SUB是确定的情况下,可以通过增大剖面图中S1、S2的值来降低LNPN

的β,因为VPNP的β一般来说是固定的。

(2)在MOS周围的TAP多打孔,以减小Rn-和Rp-,这样VPNP和LNPN的Vbe结基本

上处于短接的状态,BJT不能开启。

2 管子为衬切的时候预防闩锁

有时候,电路会碰到PMOS的SUB是衬切的情况,如图2。

在衬切的瞬间,电路上存在电源掉零的情况,对应latch-up结构中的VPNP的B会掉到

零,那么VPNP的BE结会开启,VPNP开始工作,如果在画衬切PMOS的DNW中画有

NMOS,那么就会导致latch-up结构开始工作,这个是我们不希望出现的。

衬切的情况一般出现在功率部分,少数在控制部分也有。在功率管部分,除了要做到前面

提到的普通情况下的预防latch-up措施,还要把衬切的管子PMOS单独画在一个DNW中,如

龙源期刊网 http://www.qikan.com.cn

图2所示。这种情况下,在电源掉零的情况下,VPNP不可避免的开启,但抬高的也只是P-的

电位,从而破坏了latch-up结构。在控制部分,如果出现了衬切的管子,单独画在一个DNW

中有点奢侈,可以通过改动电路,在衬切管的S端与PIN之间加一个电阻,起到限流的作用,

以减小Q0的,管子Q0更难开启,如图3所示。

参考文献

[1] (美)黑斯廷斯.《模擬电路版图的艺术》[J].电子工业出版社,2007(04):145.

IC Layout Latch-up Prevent

HE Xue-qun

(xiamen Lingxi Semiconductor Technology Co., Ltd., Xiamen Fujian; 361008)

Abstract:In the layout design, latch-up latch is a common phenomenon. Circuit design may

naturally form, but it is easier to form this structure in layout design. In addition to the latch-up

structure formed under normal conditions, we may also encounter a special case, such as the SUB

of the tube is the case of the lining, in which case the latch-up latch is formed with carelessness.

Key words:PMOS’s SUB isn’t fixed;latch-up;Latch prevention