全差分运算放大器结构框图解析 常见的全差分运算放大器电路分析

全差分CMOS运算放大器的设计

全差分CMOS运算放大器的设计CMOS运算放大器的设计报告人:指导老师:二0一三年十一月目录第一章绪论 (4)1.1设计平台及软件介绍 (4)1.1.1PSPICE简介 (4)1.1.2 L-Edit简介 (4)1.1.3 Cadence OrCAD Capture简介 (4)1.2 设计方法 (5)1.2.1CMOS运算放大器设计方法 (5)1.2.2运算放大器的性能优化 (5)第二章全差分运算放大器基础 (7)2.1 MOS器件基本特性 (7)2.1.1 MOSFET的结构和大信号特性 (7)2.1.2 MOSFET的小信号模型 (8)2.2运算放大器概述 (9)2.3全差分运算放大器特点 (10)第三章CMOS模拟运放设计 (12)3.1设计目标 (12)3.2电路结构分析 (12)3.3.1 输入级设计 (13)3.3.2电流镜电路 (14)3.3.3偏置电路 (15)3.3.4 输出级 (16)3.3.5 整体电路 (16)第四章运放参数的模拟与测量 (18)4.1瞬态分析 (18)4.2 温度特性 (19)4.3输出阻抗 (20)4.4交流特性分析 (21)5.1版图设计基础 (22)5.1.1设计流程 (22)5.1.2 L-edit中的版图设计 (23)5.2 版图设计 (24)5.3版图参数的提取并仿真 (25)5.3.1版图参数的提取和修改 (25)5.3.2电路仿真 (25)第六章总结 (27)【参考资料】 (28)附录: (29)一、Pspice仿真代码: (29)1、原理层次仿真代码(偏置电压由直流电压直接替代) (29)2、MOS分压电路中MOS宽长比确定电路 (31)3、最终Pspice仿真代码 (31)二、版图生成代码 (33)三、版图修改代码 (36)第一章绪论1.1设计平台及软件介绍1.1.1 PSPICE简介PSPICE是由SPICE(Simulation Program with Intergrated Circuit Emphasis)发展而来的用于微机系列的通用电路分析程序。

全差分运算放大器设计说明

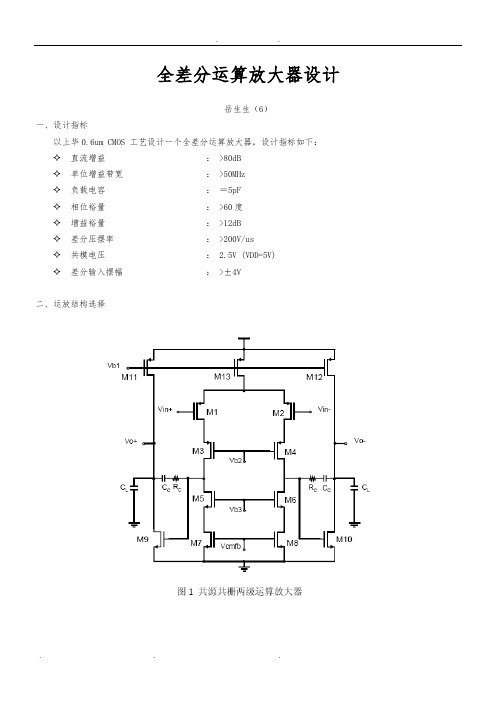

全差分运算放大器设计岳生生(6)一、设计指标以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下:✧直流增益: >80dB✧单位增益带宽: >50MHz✧负载电容:=5pF✧相位裕量: >60度✧增益裕量: >12dB✧差分压摆率: >200V/us✧共模电压: 2.5V (VDD=5V)✧差分输入摆幅: >±4V二、运放结构选择运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。

如图2所示;(b )折叠共源共栅,folded-cascode 。

如图3所示;(c )共源共栅,telescopic 。

如图1的前级所示。

本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT NV之和小于0.5V ,输出端的所有PMOS管的,DSAT PV之和也必须小于0.5V 。

对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。

另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。

考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。

两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。

三、性能指标分析1、 差分直流增益 (Adm>80db)该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益1351113571135135753()m m m o o o o o m m m m o o o o m m g g gg gg G A R r rr r g g r r r r=-=-=-+第二级增益92291129911()m o o o m m o o gg G AR r rgg=-=-=-+整个运算放大器的增益:4135912135753911(80)10m m m m overallo o o o m m o o dB g g g gAA A g g g gr r r r ==≥++2、 差分压摆率 (>200V/us )转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。

10_差分放大电路_Revised

d1d1

++ vo vO - - vo1 vo2 vO1 vO2 vsvS

IO

RR d2 d2 d2 d2 id2 iD2

T1T1 s1 s1 ++ vgs1 VGS1 1- - 1

ro

-VSS

g2 i2i2 g2 vv + + + vV gs2 GS2 - - + vic vic - ro - TT 2 2 s2s2

3、动态分析:仅输入差模信号

vi1

vi1和vi2大小相等,相位相反。 vO1和vO2大小相等,相位相 反。 vO = vO1-vO2 0,信号

vi2

vO

t

t

vGS1 VGSQ

vGS2 VGSQ

t

被放大

+VDD

t

t

iD1 IDQ

iD2 IDQ

Rd1 iD1 d1 T1 s1 1 - IO -VSS + vO1 vO - vO2 vS d2 T2 s2 -

有

1 vic = (vi1 vi2 ) 2 vid vi1 = vic 2 vid vi2 = vic 2

差放

用vid、vic表示vi1和vi2

两输入端中的共模信号 大小相等,相位相同;差模信 号大小相等,相位相反。

共模信号相当于两个输入 端信号中相同的部分 差模信号相当于两个输入 端信号中不同的部分

差动放大电路

当两个输入端并接到一起,

+Vcc R3 15k + Vo RL 10k T1 T2 Re 1K R2 1k R4 15k +15V

且加入共模信号Vic时,

Vc 1 Vc 2 R1 rbe (1 )2 Re

经典全差分运放FullyDifferentialFolded-cascodeOPAMP

经典全差分运放FullyDifferentialFolded-cascodeOPAMPFully Differential Folded-cascode OPAMP(一)电路架构:1.Design of the biasing circuit:一开始,可以先设计biasing circuit。

偏压电路有许多架构,如果采用wide-swing和constant-g m的合并电路,就必须加入激活电路。

激活电路的设计以不影响偏压电路的正常工作,和低消耗功率为原则。

如Fig.1(b)所示,Q18的W/L是small,因此Q17、Q18所吃的静态电流很小,消耗功率也小。

基本的操作原理在J&M的课本里有详细描述。

但要如何inject激活电路的电流到偏压网络呢?让我们来看看Fig.1(a),注意其中有两个loop和其对称性,只要仔细观察,这两个loop都会形成正回授。

当你用NMOS技术设计时,可以将激活电流inject到标示点X、Y,以产生PMOS(Q14、Q9)的drain电流。

同理,你也可以用PMOS设计激活电路,当然,电流的injecting point就不同了。

Rb值的设计,必须看你要偏压网络流多少电流来计算。

算完后可以做仿真,以得到最佳值,使偏压电流很match。

Fig.1(a)Fig.1(b)2.Design of the main amplifier:由于这个amplifier是one stage的设计,gain会不够,所以必须使用cascode的架构。

又为了增加output swing,故再把PMOS 给折叠下来,形成folded-cascode,最后输出是double-ended output。

先不管fully-differential架构的优点与应用,我们来看看整个架构的内部行为。

首先必须了解电路的大信号行为,最重要的为slewing。

如Fig.2所示,其中没加Q11和Q12。

考虑一个pulse加在Vin-与Vin+之间,当pulse由low 到high,Q1 turn on & Q2 turn off,所以流过Q4的drain电流全部流到Q5,并对node X上的电容充电,Vout-的dc电压会缓缓上升,此即称为positive slewing,slew rate 如下:SR=另一方面,流经Q10和Q9的电流会discharge在node Y上的电荷,这个电流由CMFB所控制。

全差分放大器(一)

图 4 分析差分放大器, 主差分放大器有两个反馈 通路, 每输入端一个。这自然形成两个反相放大器, 而反相拓扑结构很适合全差分放大器。两个反馈通 路 的 对 称 性 对 于 获 得 良 好 的 CMRR 性 能 很 重 要 。 CMRR 与 电 阻 匹 配 误 差 成 正 比 , 电 阻 匹 配 误 差 为 0.1%时, CMRR 为 60 dB。Vocm 误差放大器的任务 是使输出共模电压与 Vocm 引脚电压相等。对称反 馈时, 输出保持平衡, Vout +和 Vout- 摆幅关于 Vocm 输入电压对称。

电阻 R2 和 R4 的噪 声未经放大 直接强加到 输 出。可用 Er2 和 Er4 表示。

各噪声源相加得到总输出差分噪声( Eod) :

各噪声源以平方和的形式相加。与输入相关的 噪声被放大, 放大系数为电路噪声增益 Gn=2/(β1+ β2) 。如果采用同步反馈( β1=β2=β) , 则噪声增益 Gn= 1/β=1+Rf /Rg。

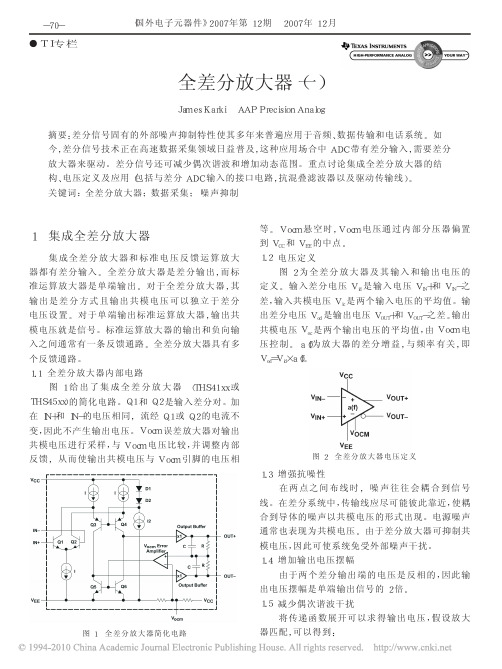

1 集成全差分放大器

集成全差分放大器和标准电压反馈运算放大 器都有差分输入。全差分放大器是差分输出, 而标 准运算放大器是单端输出。对于全差分放大器, 其 输出是差分方式且输出共模电压可以独立于差分 电压设置。对于单端输出标准运算放大器, 输出共 模电压就是信号。标准运算放大器的输出和负向输 入之间通常有一条反馈通路。全差分放大器具有多 个反馈通路。 1.1 全差分放大器内部电路

假定 a(f)β1>>1 且 a(f)β2>>1, 式 15 简化为:

若电阻匹配, 即 R1=R3, R2=R4, 在图 4 电路 中, 反馈通路是平衡的, 因此β1=β2=β, 传递函数为:

差动放大器电路图-差动放大电路工作原理分析解读

差动放大器电路图-差动放大电路工作原理分析

差动放大器

差动放大电路工作原理

基本差动放大电路:下图为差动放大器的两种典型电路。

其中左图为射极偏置,右图为电流源偏置。

差动放大(a)射极偏置差放(b)电流源偏置差放

差动放大电路有两个输入端子和两个输出端子,因此信号的输入和输出均有双端和单端两种方式。

双端输入时,信号同时加到两输入端;单端输入时,信号加到一个输入端与地之间,另一个输入端接地。

双端输出时,信号取于两输出端之间;单端输出时,信号取于一个输出端到地之间。

因此,差动放大电路有双端输入双端输出、单端输入双端输出、双端输入单端输出、单端输入单端输出四种应用方式。

上面两个差动放大器电路均为双端输入双端输出方式。

差动放大电路的外信号输入分差模和共模两种基本输入状态。

当外信号加到两输入端子之间,使两个输入信号vI1、vI2的大小相等、极性相反时,称为差模输入状态。

此时,外输入信号称为差模输入信号,以vId表示,且有:

当外信号加到两输入端子与地之间,使vI1、vI2大小相等、极性相同时,称为共模输入状态,此时的外输入信号称为共模输入信号,以vIC表示,且:

当输入信号使vI1、vI2的大小不对称时,输入信号可以看成是由差模信号vId和共模信号vIc两部分组成,其中

根据上述,可得到下图的统一的简化差动放大电路。

其中,IEE为差动对管公共射极支路的静态电流,Rem表示公共射极于地之间的动态

差动放大电路简化电路。

欢迎转载,信息来自。

全差分运算放大器设计

全差分运算放大器设计岳生生(200403020126)一、设计指标以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下:✧直流增益:>80dB✧单位增益带宽:>50MHz✧负载电容:=5pF✧相位裕量:>60度✧增益裕量:>12dB✧差分压摆率:>200V/us✧共模电压:2.5V (VDD=5V)✧差分输入摆幅:>±4V二、运放结构选择运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。

如图2所示;(b )折叠共源共栅,folded-cascode 。

如图3所示;(c )共源共栅,telescopic 。

如图1的前级所示。

本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT NV之和小于0.5V ,输出端的所有PMOS管的,DSAT PV之和也必须小于0.5V 。

对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。

另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。

考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。

两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。

三、性能指标分析1、 差分直流增益 (Adm>80db)该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益1351113571135135753()m m m o o o o o m m m m o o o o m m g g gg gg G A R r rr r g g r r r r=-=-=-+第二级增益92291129911()m o o o m m o o gg G AR r rgg=-=-=-+整个运算放大器的增益:4135912135753911(80)10m m m m overallo o o o m m o o dB g g g gAA A g g g gr r r r ==≥++2、 差分压摆率 (>200V/us )转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。

差分放大电路 全篇

Rb

Uoc

Rb

T1

T2

Uic1

Iec1 Rc Uoc1 Uoc2 Rc Iec2

2Ree

2Ree

Uic2

Uoc 0

A Uc(双)

U oc U ic

Uoc1 Uoc2 0 Uic

差放的特点: 输入无差别,输出就不动;输入有差别,输出就变动。

共模抑制比CMRR—衡量差放的一个重要指标。

CMRR A Ud A Uc

差分电路的输入输出方式

单端输入 输入方式

双端输入

单端输出

输出方式

双端输出

Uo

+

差模信号和共模信号 +

Uo Uo

-

差模信号

Ui1

Ui2

一对大小相等,极性 -

+

相反的信号,用Uid1、Uid2

表示, Uid1= - Uid2

共模信号 一对大小相等,极性相同的信号, 用Uic1、Uic2表示,Uic1= Uic2

5. 双端输入/单端输入 指标比较

输出方式

双出

单出

AUD

(Rc

//

1 2

RL )

rbe

(Rc // RL )

2rbe

Rid

2rbe

双出

单出

(Rc

//

1 2

RL )

rbe

(Rc // RL )

2rbe

2rbe

Ro

2 Rc

Rc

2 Rc

Rc

集成运算放大器概述

集成运算放大器结构特点 集成运算放大器组成及各部分作用 集成运算放大器主要参数 理想集成运算放大器及两个工作区域

2. 当V+>V-时,Vo为正向输出饱和电压VOH 当V+<V-时,Vo为负向输出饱和电压VOL 其数值接近运放的正负电源电压

差分放大电路 ppt课件

图06.03双电源差分放大电路

(动画6-1)

11

6.3 差分放大电路的动态计算

6.3.1差模状态动态计算 6.3.2共模状态动态计算 6.3.3恒流源差分放大电路

2020/12/12

12

6.3.1 差模状态动态计算

差分放大电路的差模工作状态分为四种: 1. 双端输入、双端输出(双----双) 2. 双端输入、单端输出(双----单) 3. 单端输入、双端输出(单----双) 4. 单端输入、单端输出(单----单) 主要讨论的问题有: 差模电压放大倍数 差模输入电阻 输出电阻

Avc

=

v OC1 v IC

R 'L

R b rbe (1 ) 2 R e

R 'L 2Re

2020/12/12

图06.08 共模微变等效电路21

(2)共模抑制比

共模抑制比KCMR是差分放大器的一个重 要指标。

K CMR

Avd Avc

,或

KCM R20lgAAvvdc dB

双端输出时KCMR可认为等于无穷大,单端 输出时共模抑制比

IB = RsV E(1EVB )2ERe

IC = IB V C = V CC I C R c V E = 2 I C R e V EE V CE = V C V E V B = V E + V BE

由IB的计算式可知,Re对 一半差分电路而言,只有2 Re 才2能020/获12/1得2 相同的电压降。

产生零点漂移的主要原因是温度的影响,所以 有时也用温度漂移或时间漂移来表示。工作点参数

的变化往往由相应的指标来衡量。

一般将在一定时间内,或一定温度变化范围

内的输出级工作点的变化值除以放大倍数,即将

差分运算放大电路分析

差分运算放大电路分析

差分运算放大电路是电路中最常用的放大电路,其原理为:事先将

输入信号的相反相的两个分量进行放大,而后再通过网络将其组合起来,从而形成需要的输出信号。

此类放大电路具有放大性能稳定且信

号失真小的特点,几乎能够满足各种电路要求,也可以说,差分放大

电路是任何电路设计中必不可少的一块拼图。

主要特性:

·输入干扰电压低:通过交流信号的差分放大可以消除小的输入干扰电压,从而极大地改善可靠性。

·低失真:由于放大比较平均,具有良好的稳定性和高性能,因此可以

抑制失真。

·宽带宽:由于不需要考虑共模反馈,可以有较宽的带宽。

·可靠性高:由于可以消除较小的干扰并具有稳定性,因此差分放大电

路具有较高的可靠性。

·极高的噪声功率比:一般是10dB以上,大大优于标准单端放大电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

全差分运算放大器结构框图解析常见的全差分运算放大器电路分析

全差分(运算放大器)就是一种具有差分输入,差分输出结构的运算(放大器)。

(差分放大器)相对于单端输出的放大器具有如下一些优势。

首先,由于随着CMOS 工艺尺寸不断缩小,从0.5μm 减小至0.35μm,0.18μm,90nm,(芯片)的(供电)电压也不断减小从5V降到3.5V,1.8V,1.2V甚至更低。

在如此低的供电电压的情况下,单端输出的运算放大器很难能理想地工作,为了保证电路能够得到足够大的(信号)摆幅,我们需要采用全差分的运算放大器结构。

其次,全差分运算放大器能够有效抑制电路的共模信号,并且能够减小电路的偶次谐波失真。

但是为了得到这些性能,全差分运算放大器需要一个共模反馈环路来控制输出的共模电平。

理想情况下,这个共模反馈控制环路会使得输出的共模电平稳定在VDD/2。

所以,一个全差分放大器通常由主放大器和共模反馈环路两部分组成,它在现代的(电路设计)中应用非常广泛。

1.全差分运算放大器结构框图

共模反馈的基本思想就是由一个共模采样电路取得电路的输出共模信号,然后把共模信号与一个参考信号相比较,将比较后的误差信号放大后再输入主放大器以调节输出共模电压。

对于输入的差分信号来说,共模反馈环路不会对交流信号产生影响,相当于说共模环路对于交流是开路的。

所以,电路的差分增益和相位就由主放大器决定。

但是,对于输入的共模信号,共模反馈环路决定了输出的共模电平,这时,共模环路的增益和相位就会对电路的输出共模电平的精度和稳定性产生影响。

全差分放大器在应用中的一种电路形式,差分输出的信号摆幅vO1-vO2 为单端信号vO1(vO2)摆幅的两倍,所以在输出端可以有较大的输出动态范围,相对于单端输出提高了处理信号的幅度能力。

2. 常见的全差分运算放大器电路

(a)是普通的全差分放大器电路,通常作为一个放大器的输入级部分。

图7-3(b)是折叠式全差分运算放大器电路,它的增益会比较大,可以达到60~70dB,但同时会消耗比较大的功耗,因为它有四条支路需要(电流)。

折叠式运算放大器在实际的应用中会比较广泛,因为它单级的增益比较大,这样可以避免使用多级电路实现高增益,也就避免了多级放大器的频率补偿问题。

图7-4(a)是套筒式全差分运算放大器电路,它的增益和折叠式全差分运算放大器差不多,但速度会快些,输入共模范围会小一点。

图7- 4(b)是电流镜形式的全差分放大器,它的速度比较快,但是它需要的电流也比较大

表7-1比较了套筒式共源共栅和折叠式共源共栅结构的性能特点,因为这两种电路结构在实际的设计中用到的最多。

3. 共模反馈的原理

由于全差分运算放大器的共模输出电压不能通过差分信号的负反馈来控制,所以我们需要一个额外的共模反馈环路来确定输出的共模电平,这个共模电平的选择原则通常是用来得到最大的差分输出增益或者是最大的输出电压摆幅。

共模反馈电路通常由共模电压采样电路和误差放大电路两部分组成,通常有:

其中,Vo,cm 为输出共模电平,Vo,dm 为输出差分电压,α1,α2,α3 为系数。

对于理想的共(模电)平采样电路,后面两项均为0。

α2Vo,dm 来自共模电平采样电路的不可避免的失配,α3Vo,dm2 是由于电路的非线性I-V 特性所导致的。

对于全差分运算放大器电路,由于其拥有共模放大和差模放大两种信号,为了考虑共模和差模之间的交叉放大,所以通常会使用信号流图来简化全差分运算放大电路。

其中(AD)D(ASC)是我们想要的差分增益(共模增益),(ADC),(AC)D(ASD)来自电路内部的管子之间的不匹配,ACC 来自于主放大器的非理想(电流源),ADS 来自共模电平采样的不匹配,ACS 是共模电平采样的增益。

α1 和α2 分别对应于ACS和ADS。

因为图7- 7的信号流图中有两个不同的环路,VS和Vo,cm之间是共模环路,其环路增益(Loop G(ai)n)为LGCM= ASC·ACS;VS 和Vo,dm 间的环路的存在会影响差分信号的输出,可以把这个环路称为内部差分环路,其环路增益为LGDM= ASD·ADS。

但是,LGDM 比LGCM小很多,几乎可以不考虑。

另外,图7- 7中还给出了共模信号和差分信号之间的交叉增益,可以表示为ΔLGCM=ACS· ASD 和ΔLGDM=ADS· ASC。

使用Mason 公式,我们可以得到如下公式(号表示有效增益):

其中,D=1-LGCM-LGDM

有效的开环差分增益ADD几乎等于ADD。

对于典型值来说,共模反馈环路对于整个放大器的CMRR 没有明显的影响,因为CMRR* = ADD*/ACD* ≈ CMRR。

但是,共模电平采样的不匹配会导致显著的差分到共模的增益ADC。

4.共模采样的结构

共模反馈环路在通常的全差分放大器中是必须的,它确定了放大器的输出共模电平,稳定了输出端信号。

一个好的共模反馈环路应该是和差分环路具有相似的通路,如果共模环路和差分环路可以共用,那将是非常好的。

(电容)CM 采样差分放大器的输出共模电平,VCM 通过电容C1 被电容CM 采样,VCM_REF用来调节放大器的尾电流源。

开关电容的共模反馈在两个方面优于连续时间的共模反馈,一个是对放大

器的输出摆幅上没有了限制,另一个就是避免了阻性的负载。

但是,开关电容电路也带来一些负作用。

一个是开关引入了大量的噪声,这在某些低噪声应用中会成为主要的噪声来源。

另一个就是开关引起的电荷注入会导致一定的失调。

总体来说,连续时间共模反馈和离散时间共模反馈各有优缺点,在选择共模反馈电路时要根据实际电路情况进行确定。

第11页共11页。