FPGA硬件电路设计及FPGA平台介绍ppt课件

FPGA培训课件资料

FPGA的发展趋势

总结词

随着人工智能和云计算的快速发展, FPGA的应用前景广阔,未来将朝着更高 性能、更低功耗和更智能化方向发展。

VS

详细描述

随着人工智能和云计算的快速发展,对高 性能计算和数据处理的需求不断增加, FPGA作为一种高效的硬件加速器受到了 广泛关注。未来,FPGA将朝着更高性能 、更低功耗和更智能化方向发展,以满足 不断增长的计算需求。同时,随着5G、 物联网等技术的普及,FPGA在边缘计算 和嵌入式系统中的应用也将得到进一步拓 展。

人工智能算法加速

FPGA能够针对特定算法进行硬件优化,提供高效 的计算能力,加速人工智能应用的运行。

定制化解决方案

FPGA允许针对特定需求进行硬件定制,为人工智 能应用提供更灵活、高效的解决方案。

实时处理能力

FPGA具备并行处理和低延迟特性,适用于需要实 时响应的人工智能应用场景。

云计算与FPGA

调试工具

用于在FPGA芯片上实时调试数字电 路和系统,如Xilinx的ChipScope、 Altera的SignalTap等。

03 FPGA设计实践

数字逻辑设计

01

02

03

数字逻辑基础

介绍数字逻辑的基本概念、 门电路、触发器等基础知 识。

组合逻辑设计

讲解如何使用逻辑门电路 进行组合逻辑设计,包括 加法器、比较器、多路选 择器等。

FPGA培训课件资料

目 录

• FPGA概述 • FPGA基础知识 • FPGA设计实践 • FPGA应用案例 • FPGA开发挑战与解决方案 • FPGA未来展望

01 FPGA概述

FPGA的定义与特点

总结词

FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,具有高 度的灵活性和可定制性。

《FPGA入门学习》课件

LED闪烁设计

总结词

通过LED闪烁设计,掌握FPGA的基本控制功能和数字逻辑设计。

详细描述

LED闪烁设计是FPGA入门学习的基本项目之一,通过该设计,学习者可以了解FPGA的基本控制功能 ,掌握数字逻辑设计的基本原理和方法。LED闪烁设计通常涉及到LED灯的驱动和控制,需要学习者 掌握基本的数字逻辑门电路和时序控制。

FPGA具有并行处理和高速计算的优点,适 用于数字信号处理中的实时信号处理和算 法加速。

数字滤波器设计

频谱分析和正交变换

FPGA可以实现高性能的数字滤波器,如 FIR滤波器和IIR滤波器,用于信号降噪和特 征提取。

FPGA可以高效地实现FFT等正交变换算法 ,用于频谱分析和信号频率成分的提取。

图像处理应用

优化设计技巧

时序优化

讲解如何通过布局布线、时序分析等手段优化 FPGA设计,提高时序性能。

资源共享

介绍如何通过资源共享减少FPGA资源占用,提 高设计效率。

流水线设计

讲解如何利用流水线设计技术提高系统吞吐量。

硬件仿真与调试技术

仿真工具使用

介绍常用HDL仿真工具(如ModelSim)的使用方法 。

03

CATALOGUE

FPGA开发实战

数字钟设计

总结词

通过数字钟设计,掌握FPGA的基本开发流程和硬件描述语言的应用。

详细描述

数字钟设计是FPGA入门学习的经典项目之一,通过该设计,学习者可以了解FPGA开 发的基本流程,包括设计输入、综合、布局布线、配置下载等。同时,数字钟设计也涉 及到硬件描述语言(如Verilog或VHDL)的应用,学习者可以掌握基本的逻辑设计和

基础语言。

FPGA开发流程

《FPGA底层硬件开发》PPT课件

整理ppt

40

硬核乘法器使用

整理ppt

41

硬核乘法器实例化

module multiply1(sclr,rfd,rdy,nd,clk,a,b,q); input sclr,nd,clk; output rfd,rdy; input [17:0] a,b; output [35:0] q;

multiply multiply(.sclr(sclr),.rfd(rfd), .rdy(rdy),.nd(nd),.clk(clk),.a(a),.b(b), .q(q));

每来一个时钟脉冲加法器将频率控制字k与累加寄存器相加将结果送至累加寄存器输入端累加寄存器将加法器在上一时钟脉冲产生的新相位数据反馈到加法器输入端使加法器在下一时钟脉冲继续与频率控制器相加累加寄存器输出数据即合成信号的相位n位加法整理ppt46ram用上述相位数据作为地址查波形存储器rom表得到信号幅值波形存储器存储余弦信号波形

BUFG CLKFX_BUFG_INST(.I(CLKFX_BUF),.O(CLKFX_OUT));

整理ppt

15

第二全局时钟

• 长线资源,驱动性能、抖动、延时指标仅次于全局时钟; • 可驱动片内任一逻辑信号,一般用于高频、高扇出的时钟

使能信号及高速路径上的关键信号 • 全局时钟不占用逻辑资源,也不影响其它布线资源;但第

二全局时钟资源要占用

• 使用方法:定义线网约束属性

NET “s1” USELOWSKEWLINES; NET “s2” USELOWSKEWLINES; NET “s3” USELOWSKEWLINES;

整理ppt

16

DCM模块

• 强大的DLL模块,功能包括:

• 消除时钟延时 • 频率合成 • 时钟相位调整

FPGA设计与应用ppt课件

PLD器件: CPLD: MAX3000/5000/7000/9000和Classic系列 FPGA: FLEX6K/8K/10K、APEX20K、ACEX1K、APEXⅡ、Mercury、

Excalibur、Stratix 开发软件:

MAX+PLUSⅡ :支持公司多款PLD器件,同时支持多种HDL语言,包括VHDL、 Verilog HDL、AHDL。

33

3. 基本简单数学运算 ◆ 4位加法器

逐位进位加法器

超前进位加法器

进位选择加法器

输入数据同比特位进行运算时,都要等待前 一比特的进位信号状态完成(建议:用在位 数不超过16位的加法器)。对于多位逐位进 位加法器来说,也可采用流水方式改善性能。

输入数据同比特位进行运算时,不需要等待 前一比特的进位信号。实现速度比较快,但 资源占用也比较大。建议使用在16位加法器 上比较合适。对于位数较多的也可采用流水 方式。

QuartusII内嵌的调试工具有SignalTapII和SignalProbe。

30

1.6 简单电路的HDL设计 1 基本组合逻辑运算 2 基本时序器件—寄存器 3 基本简单数学运算

31

1 基本组合逻辑运算 ◆与运算 ◆或运算 ◆异或运算 ◆ 与非运算 ◆2选1多路选择器 ◆两位比较器

32

2 基本时序器件—寄存器 ◆D触发器 ◆T触发器 ◆J-K触发器 ◆ 时序器件—移位寄存器

第五步:如果整个设计超出 器件的宏单元或I/O单元资源, 可以将设计划分到多片同系

列的器件中。

第六步:将试配器产生的器 件编程文件通过编程器或下

载电缆载入到目标芯片 FPGA中

25

设计输入

26

1.5 FPGA常用开发工具 QuartusII中集成的EDA开发工具可以分为两类: Altera自己提供的软件工具 其它EDA厂商提供的软件工具,统称为第三方工具

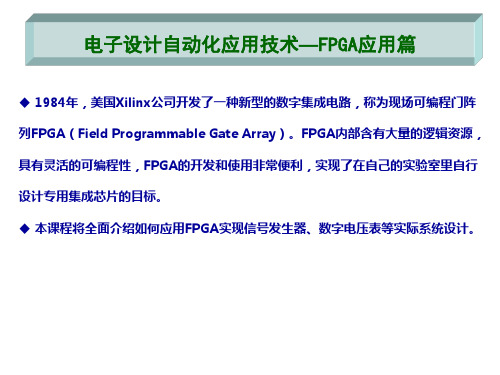

电子设计自动化应用技术—FPGA应用篇精品课件第1章

1.3 使用FPGA的条件

使用FPGA开展数字系统设计,必须具备如下几个基本条件:计算机、 FPGA开发工具、FPGA芯片开发平台。硬件描述语言、FPGA芯片基本原 理、FPGA开发工具的使用。具备上述条件,就可以尝试完成一些小系统 的设计,有了一定的经验积累之后,就可以实现大系统的设计。本课程就 是为FPGA开发应用感兴趣的学生开设的。

1.2 为什么用FPGA

•选用FPGA的重要原因:传统数字集成电路规模小、缺乏灵活性;专用集 成电路ASIC虽然规模大,但设计周期长、成本很高。 • 使用FPGA有很多优势:可以在实验室里随时对FPGA进行编程,比传统 数字集成电路使用灵活,因此在设计灵活性方面FPGA具有很强的吸引力。 由于FPGA的逻辑资源多,可以实现非常复杂的逻辑功能,代替ASIC实现 的功能,开发FPGA需要的设计成本很低,因此在逻辑资源和设计成本方面 FPGA同样具有很强的吸引力。目前,使用FPGA进行电子系统设计的设计 师越来越多。

1.4 课程包括那些内容

今天在市场上看到的FPGA内部逻辑门的数量少则几万门,多则几百万 门,型号多样,各成体系,且没有统一的规律。设计工具更是令人眼花缭 乱。课程想向学生呈现FPGA开发流程,在实际系统设计中如何使用FPGA。 课程内容由四个主要部分组成。

一、FPGA芯片,介绍芯片结构组成,通过Altera公司的一个实际FPGA 芯片的讨论,了解FPGA的工作原理、编程方法。

二、FPGA开发工具,介绍工具组成和使用,通过实际工具QuartusII的 介绍,了解FPGA的开发流程和工具使用。

三、FPGA芯片开发语言,通过VHDL介绍,学习电子系统的描述方法。 四、FPGA应用实例,通过实例学习FPGA的设计、验证、综合和实现。

FPGA基础知识PPT课件

.

18

基本可编程逻辑单元

由查找表(Look up table)触发器(FF)组成;

LUT一般是4输入查找表,高端器件(xilinx v5)采用LUT-6结构; LUT可看成4位地址线的16x1的RAM 结构

FF是可编程的触发器,可配置成同步/异步复位、同步/异步置位、 使能、装载等功能触发器;

a,b,c,d

.

29

SOPC(System on programmable chip):片上可编 程系统 FPGA内嵌入了CPU/DSP,具备实现软硬件协同 设计的能力; Xilinx:

FPGA基于查找表加触发器的结构,采用SRAM工 艺,也有采用flash或者反熔丝工艺;主要应用高 速、高密度大的数字电路设计;

FPGA由可编程输入/输出单元、基本可编程逻辑 单元、嵌入式块RAM、丰富的布线资源(时钟/长 线/短线)、底层嵌入功能单元、内嵌专用的硬核 等组成;

目前市场上应用比较广泛的FPGA芯片主要来自 Altera与Xilinx。另外还有其它厂家的一些低端芯 片(Actel、Lattice);

.

10

FPGA器件结构 可编程输入/输出单元 可编程逻辑单元 嵌入式块RAM 布线资源 底层嵌入功能单元

.

11

FPGA器件结构

Xilinx spatan-3器件结构

.

12

Altera cyclone II器件结构

LAB

.

13

FPGA器件结构 可编程输入/输出单元 可编程逻辑单元 嵌入式块RAM 布线资源 底层嵌入功能单元

.

5

CPLD器件结构

MAX7000 CPLD内部结构

宏单元

.

6

宏单元(乘积项)

第7章FPGACPLD硬件结构与工作原理讲述素材PPT课件

15

一、PLD基础

举例:用PROM完成半加器逻辑阵列

F0A0A1A0A1 F1A1A0

16

一、PLD基础

PLA:逻辑阵列示意图

A1

A0

或阵列 (可编程)

A1 A 1

A0 A 0

与阵列(可编程)

F1

F0

17

一、PLD基础

PAL:逻辑阵列示意图

A1 A0 A0

F0

A1

F1

F1 F0

PAL结构

PAL的常用表示

PLD中或阵列的表示

14

一、PLD基础

PROM:逻辑阵列结构

A0 A1

An1

… … …

与阵列 (不可

W0 W1

编程) Wp1

或阵列 (可编程)

F0 F1

Fm1

p2n

其逻辑函数是:

F0 Mp1,0Wp1M1,0W1M0,0W0 F1 Mp1,1Wp1M1,1W1M0,1W0

Fm1 Mp1,m1Wp1M1,m1W1M0,m1W0

FPGA:基于查找表结构

输入A 输入B 输入C 输入D

查找表 LUT

输出P P=F(A,B,C,D)

27

输入A 输入B 输入C 输入D

二0 、FPGA/CPLD结构与工作原理

0

多路选择器

0

0

0

1

1

16×1 0 SRAM 0

输出P

0

0

0

0

0

1

1

P ABCD ABCD ABCD AB28CD

举例: Cyclone 2系列

输入缓 冲电路

与阵列

输出逻辑宏 单元OLMC

20

FPGA入门学习ppt课件

4.顶层设计:创建一个顶层文件,将各模块实例 化,添加输入、输出引脚;编译,仿真。

5. 给输入、输出引脚分配引脚号码,编程下载。

14

详细步骤 最好每个工程都有

自己的工作目录!

▪ 第1步:在资源管理器下创建一个工作目录second。

▪ 第2步:启动ISE,执行菜单命令“ File > New Project ”,创 建一个工程,工程名为second。

15

子模块设计——100分频器

[模块1] 10KHz到100Hz的分频电路(采用Verilog HDL语言描述)

编程目

PLD

标文件

计算机接口

器件编程接口

PCB Board

3

EDA技术的范畴

PCB 设计

电路设计 本课程内容!

PLD 设计

IC 版图设计

模拟电路 数字电路 混合电路 设计输入 逻辑综合 仿真 编程下载4 Nhomakorabea 问题的提出

▪设计一个电子秒表电路,使之完成以下功能:

➢ 按0.01s的步长进行计时; ➢ 具有异步清零和启动/停止计数功能; ➢ 并用数码管显示其秒高位、秒低位,百分秒高位、

编程

EDA软件 + 空白PLD

数字系统

▪ 首先在计算机上安装EDA软件,它们能帮助设计者自动 完成几乎所有的设计过程;再选择合适的PLD芯片,可 以在一片芯片中实现整个数字系统。

9

现代的数字系统设计方法(续1)

1.根据设计要求划分功能模块

2. PLD开发(利用EDA工具)

(1)设计输入:采用硬件描述语言(HDL),用条件语句或赋值 语句表示输入和输出的逻辑关系,将整个程序输入到计算机中;

bsecd [3..0] 译码器 bsecm[3..0] 译码器

FPGA硬件电路设计及FPGA平台介绍

FPGA硬件电路设计及FPGA平台介绍FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,通过在硬件电路中配置逻辑元件和互连资源来实现特定功能。

相比于专用集成电路(ASIC),FPGA具有灵活性、可重构性和可编程性的优势,适用于需要频繁修改或定制的应用场景。

1.需求分析:明确目标应用的功能和性能需求,包括输入输出接口、处理算法和时序要求等。

2.架构设计:根据需求分析,设计FPGA电路的系统级架构,确定各个模块之间的功能关系和数据流。

3.模块设计:将系统级架构划分为若干个功能模块,对每个模块进行详细设计,包括模块功能、接口定义和内部逻辑电路的设计。

4.时序设计:对FPGA电路进行时序约束和分析,保证各个模块之间的时序关系和时序容限满足系统要求。

5. 逻辑综合:将设计的RTL(Register Transfer Level,寄存器传输级)描述转化为门级电路网表,在逻辑综合阶段可以对电路进行优化。

6.物理布局:将逻辑电路的网表转化为物理布局,在硬件电路中确定各个逻辑元件和互连线的具体位置。

7.静态时序分析:通过静态时序分析工具对布局完成的电路进行时序验证,保证时序约束满足需求。

FPGA平台是指进行FPGA硬件电路设计的基础工具和开发平台。

常见的FPGA平台有Xilinx、Altera等厂商提供的开发工具和FPGA开发板。

以下是对两个常见的FPGA平台的介绍:1. Xilinx:Xilinx是一家全球领先的可编程逻辑器件和开发工具提供商。

Xilinx的FPGA产品系列包括Zynq、Spartan、Virtex等多个系列,分为低端、中端和高端,适用于不同的应用场景和性能需求。

对于FPGA硬件电路设计,Xilinx提供了Vivado开发套件,包括设计工具、仿真工具和调试工具等,方便用户进行设计、验证和调试。

2. Altera(Intel FPGA):Altera是一家全球领先的可编程逻辑器件和高速通信解决方案提供商,2024年被英特尔收购并更名为Intel FPGA。

FPGA基础知识ppt

xx年xx月xx日

目录

• fpga概述 • fpga基本结构 • fpga工作原理 • fpga设计和优化 • fpga开发工具 • fpga发展趋势和挑战 • fpga与其他芯片的比较

01

fpga概述

fpga定义

定义

FPGA(Field Programmable Gate Array)即现场可编程门 阵列,是一种高度灵活的硬件设施,可以通过编程来配置其 硬件资源,实现用户特定的功能。

04

fpga设计和优化

设计和优化方法

算法级优化

基于算法级别的优化,主要从算 法设计,数据流,控制流等方面 进行优化

模块级优化

对模块进行优化,包括逻辑优化 、资源优化、调度优化等

系统级优化

对整个系统进行优化,包括任务 划分、系统结构、分布式等

资源管理

资源利用

合理利用 FPGA 内部资源,尽量避免资源浪费

采用低功耗器件、降低芯片温度、减少热功耗等 措施

动态功耗管理

通过动态调整工作频率、电压等参数,实现功耗 管理

静态功耗管理

通过静态功耗管理技术,如多阈值电压设计、门 控时钟等,降低芯片功耗

05

fpga开发工具

xilinx开发工具

Vivado

Xilinx的旗舰级开发环境,支持从IP生成、设计、仿真、 调试到比特流生成等全流程开发。

低功耗设计

优化FPGA的功耗设计,实现更 低功耗和更长的电池寿命,同时 开展绿色能源的研究,利用太阳 能等可再生能源为FPGA提供能 源。

硬件加速器

用FPGA加速特定的计算密集型 任务,如深度学习、图像处理和 科学计算等,提高整体计算性能 。

fpga面临的挑战