基于VHDL语言的数字锁相环的设计与实现

一种可编程全数字锁相环的设计与实现

一种可编程全数字锁相环的设计与实现李凤华;刘丹丹;单长虹【摘要】针对传统的全数字锁相环电路参数不可调、锁相速度慢及锁相范围窄的缺点,提出了一种可编程全数字锁相环.采用电子设计自动化技术完成了该系统设计,并对所设计的电路进行了计算机仿真与分析,最后,采用FPGA予以硬件电路的实现;系统仿真与硬件实验证明,该锁相环中数字滤波器和数控振荡器的参数可以自主设定,改变数字滤波器的参数可加快锁相速度,改变数控振荡器的参数可扩大锁相范围;该锁相环具有锁相速度快、锁相范围宽、电路结构简单、参数设计灵活和易于集成等优点,可适用于许多不同用途的领域.【期刊名称】《计算机测量与控制》【年(卷),期】2016(024)001【总页数】4页(P243-245,248)【关键词】全数字锁相环;电子设计自动化;计算机仿真;可编程【作者】李凤华;刘丹丹;单长虹【作者单位】南华大学电气工程学院,湖南衡阳421001;南华大学电气工程学院,湖南衡阳421001;南华大学电气工程学院,湖南衡阳421001【正文语种】中文【中图分类】TB114.3锁相环路已在模拟和数字通信等各个方面得到了较为广泛的应用,比如其同步特性就保证了通信中系统的稳定性[1]。

随着集成电路的发展,部分模拟锁相环也渐渐被数字锁相环取代[2]。

与模拟锁相环相比,数字锁相环易于集成、可靠性高、设计方便、价格优廉,并且有很强的通用性,克服了模拟锁相环中对温度敏感、直流零点漂移、抗干扰性能差和无法嵌入SOC构成片内锁相环系统等缺点[3-4]。

但现有的一些全数字锁相环的锁相范围窄、用途单一、通用性不强。

且设计方案复杂,修改电路参数不易。

对于用于不同用途的锁相环而言,需要重新进行电路系统的设计,若要满足锁相系统的锁相速度和锁相范围等方面的性能指标要求,整个设计过程就比较复杂[5-6]。

本文提出了一种可编程的全数字锁相环,介绍了它的系统结构、工作原理及各分模块的设计方案。

利用Quartus II软件工具对电路系统进行了仿真验证,并根据仿真结果对电路参数的变化对锁相系统的影响进行了分析。

基于PI控制的全数字锁相环设计

基于PI控制的全数字锁相环设计作者:蒋小军单长虹原华盛臻来源:《现代电子技术》2013年第02期摘要:针对以往全数字锁相环研究中所存在电路结构复杂、设计难度较大和系统性能欠佳等问题,提出了一种实现全数字锁相环的新方法。

该锁相环以数字比例积分控制的设计结构取代了传统的一些数字环路滤波控制方法。

应用EDA技术完成系统设计,并进行计算机仿真。

仿真结果表明:在一定的频率范围内,该锁相环锁定时间最长小于15个输入信号周期,相位抖动小于输出信号周期的5%,且具有电路结构简单、环路性能好和易于集成的特点。

关键词:比列积分控制;全数字锁相环;超高速集成电路硬件描述语言;现场可编程门阵列中图分类号:TN402⁃34 文献标识码:A 文章编号:1004⁃373X(2013)02⁃0141⁃03锁相环在通信、无线电电子学和自动控制等领域得到了极为广泛的应用,它已成为各类电子系统中一个十分重要的部件。

由于全数字锁相环(ADPLL)消除了模拟锁相环中压控振荡器(VCO)的非线性,鉴相器不精确,部件易饱和以及高阶环不稳定等特点,而其本身又具有参数稳定、可靠性高、易于集成的特点[1⁃2],因此,ADPLL得到了越来越多的应用。

传统的数字锁相环系统是希望通过采用具有低通特性的环路滤波器,获得稳定的振荡控制数据。

对于数字滤波器采用基于DSP的运算电路的全数字锁相环[3],当环路带宽很窄时,环路滤波器的实现将需要很大的电路量,这给专用集成电路的应用和片上系统SoC(System on Chip)的设计带来一定困难。

另一种类型的全数字锁相环是采用脉冲序列低通滤波计数电路作为环路滤波器,如随机徘徊序列滤波器、先N后M序列滤波器等[1,4]。

这些电路通过对鉴相器模块产生的相位误差脉冲进行计数运算,获得可控振荡器模块的振荡控制参数。

由于脉冲序列低通滤波计数方法是一个比较复杂的非线性处理过程,难以进行线性近似。

因此,无法采用系统传递函数的分析方法确定锁相环的设计参数,不能实现对全数字锁相环性能指标的解耦控制和分析,无法满足较高的应用要求。

VHDL学习经验

浅谈VHDL学习一,检查时钟clk上升沿有以下三种途径:1,clk'EVENT AND clk ='1';2,NOT clk'STABLE AND clk ='1';3,RISING_EDGE(clk);发生事件,就是电平发生变化.The rising_edge and falling_edge functions are defined in the std_logic_1164 package二,检查时钟clk下降沿有以下三种途径:1,clk'EVENT AND clk ='0';2,NOT clk'STABLE AND clk ='0';3,FALLING_EDGE (clk);VHDL是由美国国防部为描述电子电路所开发的一种语言,其全称为(Very High Speed Integrated Circuit) Hardware Description Language。

与另外一门硬件描述语言Verilog HDL相比,VHDL更善于描述高层的一些设计,包括系统级(算法、数据通路、控制)和行为级(寄存器传输级),而且VHDL具有设计重用、大型设计能力、可读性强、易于编译等优点逐渐受到硬件设计者的青睐。

但是,VHDL是一门语法相当严格的语言,易学性差,特别是对于刚开始接触VHDL的设计者而言,经常会因某些小细节处理不当导致综合无法通过。

为此本文就其中一些比较典型的问题展开探讨,希望对初学者有所帮助,提高学习进度。

一.关于端口VHDL共定义了5种类型的端口,分别是In, Out,Inout, Buffer及Linkage,实际设计时只会用到前四种。

In和Out 端口的使用相对简单。

这里,我们主要讲述关于buffer和inout使用时的注意事项。

与Out端口比,Buffer端口具有回读功能,也即内部反馈,但在设计时最好不要使用buffer,因为buffer类型的端口不能连接到其他类型的端口上,无法把包含该类型端口的设计作为子模块元件例化,不利于大型设计和程序的可读性。

数字锁相环提取同步信号电路图

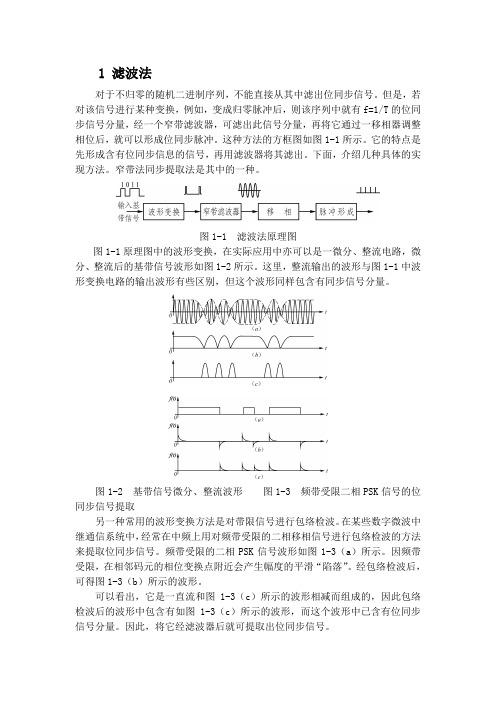

1 滤波法对于不归零的随机二进制序列,不能直接从其中滤出位同步信号。

但是,若对该信号进行某种变换,例如,变成归零脉冲后,则该序列中就有f=1/T的位同步信号分量,经一个窄带滤波器,可滤出此信号分量,再将它通过一移相器调整相位后,就可以形成位同步脉冲。

这种方法的方框图如图1-1所示。

它的特点是先形成含有位同步信息的信号,再用滤波器将其滤出。

下面,介绍几种具体的实现方法。

窄带法同步提取法是其中的一种。

图1-1 滤波法原理图图1-1原理图中的波形变换,在实际应用中亦可以是一微分、整流电路,微分、整流后的基带信号波形如图1-2所示。

这里,整流输出的波形与图1-1中波形变换电路的输出波形有些区别,但这个波形同样包含有同步信号分量。

图1-2 基带信号微分、整流波形图1-3 频带受限二相PSK信号的位同步信号提取另一种常用的波形变换方法是对带限信号进行包络检波。

在某些数字微波中继通信系统中,经常在中频上用对频带受限的二相移相信号进行包络检波的方法来提取位同步信号。

频带受限的二相PSK信号波形如图1-3(a)所示。

因频带受限,在相邻码元的相位变换点附近会产生幅度的平滑“陷落”。

经包络检波后,可得图1-3(b)所示的波形。

可以看出,它是一直流和图1-3(c)所示的波形相减而组成的,因此包络检波后的波形中包含有如图1-3(c)所示的波形,而这个波形中已含有位同步信号分量。

因此,将它经滤波器后就可提取出位同步信号。

2 锁相法位同步锁相法的基本原理和载波同步的类似。

在接收端利用鉴相器比较接收码元和本地产生的位同步信号的相位,若两者相位不一致(超前或滞后),鉴相器就产生误差信号去调整位同步信号的相位,直到获得准确的位同步信号为止。

前面讨论的滤波法原理中,窄带滤波器可以是简单的单调谐回路或晶体滤波器,也可以是锁相环路。

我们把采用锁相环来提取位同步信号的方法称为锁相法。

下面介绍在数字通信中常采用的数字锁相法提取位同步信号的原理。

基于VHDL的ASK调制与解调设计与实现

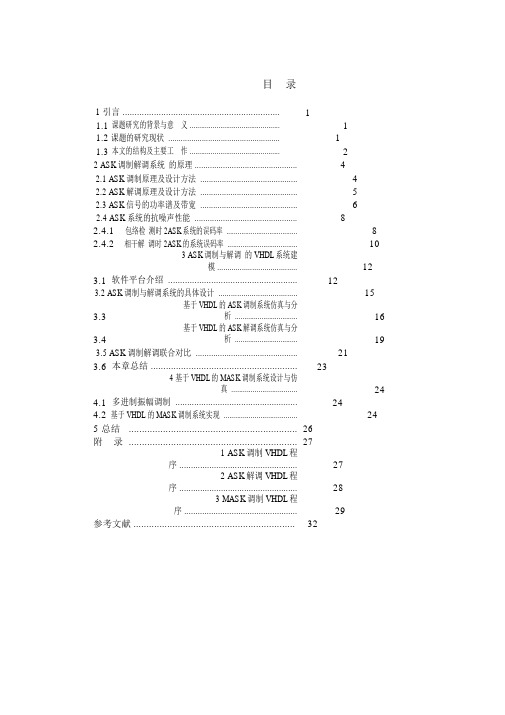

目录1 引言 (1)1.1课题研究的背景与意义 (1)1.2课题的研究现状 (1)1.3本文的结构及主要工作 (2)2 ASK调制解调系统的原理 (4)2.1 ASK 调制原理及设计方法 (4)2.2 ASK 解调原理及设计方法 (5)2.3 ASK 信号的功率谱及带宽 (6)2.4 ASK 系统的抗噪声性能 (8)2.4.1包络检测时 2ASK系统的误码率 (8)2.4.2相干解调时 2ASK的系统误码率 (10)3 ASK调制与解调的 VHDL系统建模 (12)3.1软件平台介绍 (12)3.2 ASK 调制与解调系统的具体设计 (15)3.3基于 VHDL 的 ASK调制系统仿真与分析 (16)3.4基于 VHDL 的 ASK解调系统仿真与分析 (19)3.5 ASK 调制解调联合对比 (21)3.6本章总结 (23)4 基于 VHDL的 MASK调制系统设计与仿真 (24)4.1多进制振幅调制 (24)4.2基于 VHDL 的 MASK调制系统实现 (24)5 总结 (26)附录 (27)1 ASK调制 VHDL程序 (27)2 ASK解调 VHDL程序 (28)3 MASK调制 VHDL程序 (29)参考文献 (32)第I页共II页1引言1.1 课题研究的背景与意义通信即传输信息,进行信息的时空转移。

通信系统的作用就是将信息从信源【1 】发送到一个或多个目的地。

实现通信的方式和手段很多,如手势、语言、旌旗、烽火台和击鼓传令,以及现代社会的电报、电话、广播、电视、遥控、遥测、因特【 2】网和计算机通信等,这些都是消息传递的方式和信息交流的手段。

伴随着人类的文明和科学技术的发展,电信技术也是以一日千里的速度飞速发展,如今,在自然科学领域涉及“通信”这一术语时,一般指“电通信”。

现代通信系统要求通信距离远、通信容量大、传输质量好。

作为其关键技术之一的调制解调技术一直是人们研究的一个重要方向通过调制,不仅可以进行频谱搬移,把调制信号的频谱搬移到所希望的位置上,而且它对系统的传输有效性和传输的可靠性有着很大的影响【3】。

基于FPGA的全数字锁相环设计研究

基于FPGA的全数字锁相环设计研究

赵杨;王龙;赵群;周品亦

【期刊名称】《光电技术应用》

【年(卷),期】2007(22)6

【摘要】介绍了一种基于FPGA(现场可编程门阵列)的全数字锁相环设计方法与性能研究, 详细叙述了基于FPGA的全数字锁相环系统的硬件设计构成和软件构建思路,并运用VHDL硬件描述语言实现了全数字锁相环系统,给出了电路系统的仿真结果.通过仿真结果对锁相环系统进行了简要的性能分析.

【总页数】4页(P63-66)

【作者】赵杨;王龙;赵群;周品亦

【作者单位】东北电子技术研究所,辽宁,锦州,121000;总装备部驻锦州地区军事代表室,辽宁,锦州,121017;渤海船舶职业学院电气工程系,辽宁,葫芦岛,125001;中国人民解放军63889部队,河南,孟州,454750

【正文语种】中文

【中图分类】TP274

【相关文献】

1.基于FPGA的全数字锁相环的复频域分析与实现 [J], 马莽原;石新春;王慧;孟建辉;付超

2.基于FPGA实现的变PI参数全数字锁相环 [J], 彭咏龙;朱劲波;李亚斌

3.基于FPGA的全数字Costas锁相环的设计仿真 [J], 刘浩

4.基于FPGA的自动变模全数字锁相环的设计 [J], 甘国妹;曹江亮;于丞琳

5.基于FPGA的全数字延时锁相环的设计 [J], 李锐; 田帆; 邓贤君; 单长虹

因版权原因,仅展示原文概要,查看原文内容请购买。

锁相环路(PLL)电路设计实例

软件实现PLL的代码示例

01

```systemverilog

02

// 定义PLL模块

03

module pll(input wire clk_in, output reg clk_out);

软件实现PLL的代码示例

01

parameter FREF = 100e3; // 参考频率

02

parameter N = 10; // 分频比

相位保持一致。

电荷泵型PLL的电路实现

电荷泵由两个开关和两个电容 组成,一个开关用于充电,另

一个用于放电。

当输入信号与VCO输出信号 的相位存在误差时,电荷泵 的开关会根据误差信号的极 性进行切换,从而在电容上

积累或释放电荷。

电容上的电荷量会转换为电压 信号,该电压信号通过低通滤 波器平滑后,用于调整VCO的

频率。

电荷泵型PLL的性能分析

01

电荷泵型PLL具有较高的带宽和较快的响应速度,因此适用于高 速数据传输和无线通信等应用。

02

由于电荷泵型PLL采用电荷传输方式,因此对电源噪声和电磁干

扰较为敏感,需要采取相应的措施进行抑制。

电荷泵型PLL的另一个优点是易于集成,因此适合于大规模生产

03

和应用。

04

软件实现PLL的代码示例

assign clk_out = div_by_n;

always @(posedge clk_in) begin phase_error <= #1 ($posedge clk_in ? 32'hFFFFFFFF : phase_error 1);

软件实现PLL的代码示例

PLL电路设计实例:模拟型 PLL

计数器的VHDL设计与实现

期刊论文—EDA课程设计题目:计数器的VHDL设计与实现学生姓名:***学生学号:09专业班级:计算机科学与技术0902班指导老师:***计数器的VHDL设计与实现摘要:介绍了各种基本计数器的组成及其工作原理,重点研究了可变模计数器的设计与实现, 在对现有的可变模计数器的研究基础上,在Quartus 开发环境中,用VHDL语言设计一种功能更加强大的可变模计数器,它具有清零、置数、使能控制、可逆计数和可变模等功能,并且对传统的可变模计数器的计数失控问题进行研究,最终设计出一种没有计数失控缺陷的可变模计数器,并通过波形仿真和EPF10K20TI144-4系列实验箱,验证了其各项设计功能。

结果表明该设计正确.功能完整。

运行稳定。

关键词:VHDL;计数器;可变模计数;可逆计数VHDL Design and Realization of CounterAbstract:This paper analyzes all kinds of basic counter and its working principle, focus on the counter variable mode of design and implementation. In the environment of Quartus based on research of the existing module—alterable counter,a module—alterable counter with more functions,such as clear,set,enable control,reversible count,module—alterable count and so on,which is designedwith VHDL.By researching the problem of losing control existed in traditional module—alterable counter.A module—alterablecounter with no fault designed.And through the waveform simulation and EPF10K20TI144-4 series experiment box,all of the functions are verified.The resuit indicates that the counter is designed correctly,and has integral functions and stable operation.Keywords:VHDL;counter;divided frequency impIement;reversible引言随着电子技术、计算机技术和EDA技术的不断发展,数字系统规模越来越大,传统的电路设计已难以适应复杂电子系统的设计要求。

锁相环_精品文档

锁相环锁相环,又称为锁相放大器或者锁相放大器,是一种基于反馈机制的控制系统,用于稳定和锁定两个信号的相位差。

锁相环的原理可以在许多领域中得到应用,包括通信、电子仪器、雷达等。

锁相环工作原理锁相环的核心原理是采用一个反馈环来纠正输入信号的相位差。

一般来说,锁相环由三个主要部分组成:相位比较器、低通滤波器和可变频率振荡器。

首先,锁相环将输入信号和参考信号通过相位比较器进行比较,产生一个误差信号。

相位比较器会计算两个信号之间的相位差,并且生成一个电压或电流信号,表示这个相位差。

如果输入信号和参考信号的相位差为零,那么相位比较器输出的误差信号也将为零。

接着,误差信号通过低通滤波器进行滤波处理,去除高频噪声和杂散信号。

低通滤波器可以使锁相环对于高频噪声具有良好的抑制能力,提高系统的稳定性和抗干扰性。

最后,滤波后的误差信号被送往可变频率振荡器,控制其输出的频率和相位。

可变频率振荡器会根据误差信号的大小和方向来调整输出信号的频率和相位,以减小相位差。

如果误差信号为正,则输出频率增加;如果误差信号为负,则输出频率减小。

通过不断调整输出频率和相位,锁相环可以将输入信号和参考信号的相位差保持在一个可接受的范围内。

应用领域锁相环在通信领域中有广泛的应用。

在通信系统中,锁相环可以用来确保发送和接收的信号保持同步。

例如,在无线通信中,锁相环可以用来抑制多径干扰和载波漂移,提高通信质量和稳定性。

另外,锁相环还可以用于时钟恢复和数据捕获等方面。

除了通信领域外,锁相环在电子仪器和雷达等领域也有重要的应用。

在电子仪器中,锁相环可以用来稳定和控制仪器的频率和相位。

例如,在频谱分析仪和信号发生器中,锁相环可以确保仪器输出的信号具有准确的频率和相位信息。

在雷达系统中,锁相环可以用来实现目标检测和跟踪。

通过锁相环,雷达可以准确地测量目标和干扰源之间的相对相位差,从而提高雷达测量的精度和可靠性。

总结锁相环是一种基于反馈机制的控制系统,用于稳定和锁定两个信号的相位差。

鉴相器

鉴相器开放分类:电子电子技术电子术语通信编辑词条分享英文名:phasedetector鉴相器,顾名思义,就是能够鉴别出输入信号的相差的器件。

它是PLL,即锁相环的重要组成部分。

锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组使输出电压与两个输入信号之间的相位差有确定关系的电路。

表示其间关系的函数称为鉴相特性。

鉴相器是锁相环的基本部件之一,也用于调频和调相信号的解调。

常见的鉴相特性有余弦型、锯齿型与三角型等。

鉴相器特性用u d(t)=k d f【θe(t)】表示。

式中k d为鉴相器的增益系数;θe(t)=θ1(t)-θ2(t),表示两个输入信号之间的相位差。

函数f【²】表示鉴相特性,它反映鉴相器的输出电压u d(t)与相位差的关系。

常见的鉴相特性有余弦型、锯齿型与三角型等。

鉴相器鉴相器可以分为模拟鉴相器和数字鉴相器两种。

二极管平衡鉴相器是一种模拟鉴相器。

两个输入的正弦信号的和与差分别加于检波二极管,检波后的电位差即为鉴相器的输出电压。

其鉴相特性通常为余弦型的。

鉴频鉴相器是一种数字鉴相器。

两个输入信号是脉冲序列,其前沿(或后沿)分别代表各自的相位。

比较这两个脉冲序列的频率和相位即可得到与相位差有关的输出。

这种鉴相器的鉴相特性为锯齿形。

因它兼具鉴频作用,故称鉴频鉴相器二极管平衡鉴相器这是一种模拟鉴相器,原理电路如图1。

二极管D1、D2和C1R1、C2R2构成两个峰值检波器。

两个输入的正弦信号u1(t)=U1sin(ωt+θ1)、u2(t)=U2sin(ωt+θ2) 的和与差分别加于检波二极管D1和D2,检波后的电压差即为鉴相器的输出电压u d。

当U2U1时,u d∝U1cos(θ1-θ2)。

在这种情况下,它的鉴相特性是余弦型的(图2a)。

鉴相器鉴频鉴相器这是一种数字鉴相器。

两个输入信号是脉冲序列,其前沿(或后沿)分别代表各自的相位。

比较这两个脉冲序列的频率和相位即可得到与相位差有关的输出。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

© 1994-2009 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

© 1994-2009 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

© 1994-2009 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

© 1994-2009 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

© 1994-2009 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

© 1994-2009 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

© 1994-2009 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

© 1994-2009 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

© 1994-2009 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

© 1994-2009 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net