100进制计数器

一年级数学下册 第三单元《认识100以内的数》教案 苏教版

一年级数学下册第三单元《认识100以内的数》教案苏教版教学内容:1、数数、数的基本含义2、数的组成和读写3、整十数加一位数及相应的减法4、练习五5、数的顺序6、比较数的大小7、多一些、少一些、多得多、少得多8、练习六9、复习教学目标:1、使学生认识计数单位“一”和“十”,能够正确地数出数量在100以内的物体的个数,知道100以内的数是由几个十和几个一组成的;掌握100以内数的顺序,会比较100以内数的大小。

2、使学生认识个位、十位,初步理解个位、十位上的数所表示的意义,并初步认识百位;能够正确、熟练地读写100以内的数。

3、使学生了解加法和减法算式中各部分的名称;结合数的认识,能够正确、熟练地口算整十数加一位数以及相应的减法。

4、使学生会用100以内的数表示日常生活中的事物,并进行简单的估计和交流,从而感受数与生活的联系,培养从数学的角度观察周围事物和日常生活的意识,培养同学之间的相互合作、交流的态度。

在认数的活动中,获得一些成功的体验,增强对数学学习的兴趣和自信心。

教学重点:100以内数的读法和写法教学难点:理解数位的意义1、数数、数的基本含义教学内容:数数、数的基本含义教学目标:1、让学生通过操作实践活动,初步理解非整十两位数的意义,会按顺序数出100以内的数,会读、写非整十的两位数,会用学具表示这些数,知道这些数的组成。

2、继续培养动手操作能力、抽象概括能力和语言表达能力。

3、培养用数学的观念,看周围事物和看日常生活的意识,培养与同学相互合作交流的态度。

教学重点:100以内的数和数的组成。

教学难点:知道几十九后面的数是几。

体会满十进一的计数方法。

教学过程:一、揭示课题:出示一些非整十数:全班有31人、小明的体重是25千克……告诉学生几十几的数在生活中的作用可大了。

讲述:今天我们就来认识一些“几十几”的两位数。

(板书课题:认识几十几)二、直观认识几十几:1、谈话:请小朋友们数出23根小棒摆在课桌上,看谁摆得又快又好。

数字电子技术3

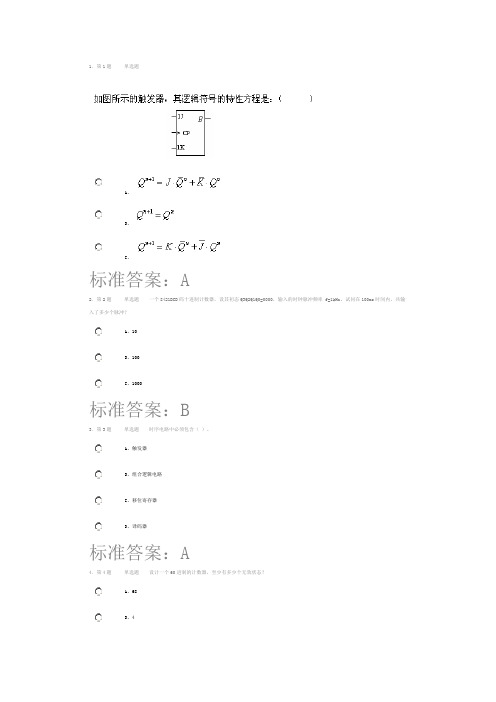

1.第1题单选题A、B、C、标准答案:A2.第2题单选题一个8421BCD码十进制计数器,设其初态Q3Q2Q1Q0=0000,输入的时钟脉冲频率 f=1kHz。

试问在100ms时间内,共输入了多少个脉冲?A、10B、100C、1000标准答案:B3.第3题单选题时序电路中必须包含()。

A、触发器B、组合逻辑电路C、移位寄存器D、译码器标准答案:A4.第4题单选题设计一个60进制的计数器,至少有多少个无效状态?A、68B、4C、28标准答案:B5.第5题单选题A、4B、5C、6D、15标准答案:B6.第6题单选题下图所示的触发器,哪个是上升沿触发的边沿D触发器逻辑符号?A、B、C、D、标准答案:A 7.第7题单选题A、9B、6C、60D、54标准答案:D 8.第8题单选题A、RSB、不变C、DD、T标准答案:C 9.第9题单选题A、6进制计数器B、5进制计数器C、7进制计数器D、以上都不正确标准答案:A10.第10题单选题若需要每输入240个脉冲分频器能输出一个脉冲,则由二进制加计数器构成的分频器至少需要多少个触发器?A、7B、8C、9标准答案:B11.第11题单选题A、具有自启动特性B、无自启动特性标准答案:A12.第12题单选题对于集成计数器74LS161,如下描述正确的是:A、同步4位二进制计数器,具有同步清零功能B、同步4位二进制计数器,具有异步清零功能C、同步8421BCD十进制计数器,具有异步清零功能标准答案:B13.第13题单选题一个8位二进制加法计数器,如果输入脉冲频率 f=256kHz,试求此计数器最高位触发器输出脉冲频率?A、32kHzB、1kHzC、128 kHz标准答案:B14.第14题单选题对于JK触发器,输入J=0,K=1,CP脉冲作用后,触发器的状态为()。

A、0B、1C、保持不变D、翻转标准答案:A15.第15题单选题A、边沿JK触发器,下降沿触发B、钟控JK触发器,下降沿触发C、边沿JK触发器,上升沿触发D、钟控JK触发器,上升沿触发标准答案:A 16.第16题单选题A、数码寄存器B、同步8进制计数器C、同步3进制计数器D、移位寄存器标准答案:B 17.第17题单选题A、5B、6C、7D、818.第18题单选题A、7B、5C、6D、8标准答案:D19.第19题单选题有一个与非门构成的基本RS触发器,欲使其输出状态保持原态不变,其输入信号应为()。

《数字电子技术基础》复习题

10.组成计数器的各个触发器的状态,能在时钟信号到达时同时翻转,它属

于计数器。

答:同步

11.组成计数器的各个触发器的状态,在时钟信号到达时不能同时翻转,它属于计数器。

答:异步

12.两片中规模集成电路10进制计数器串联后,最大计数容量为()位。

答:100

13.驱动共阳极七段数码管的译码器的输出电平为()有效。

A.110 B.001 C.100 D.000

答:B

11.8—3线优先编码器(74LS148)中,8条输入线 ~ 同时有效时,优先级最高为I7线,则 输出线的状态是()

A.000 B.010 C.101 D.111

答:A

12.引起组合逻辑电路中竟争与冒险的原因是()

A.逻辑关系错;B.干扰信号;C.电路延时;D.电源不稳定。

答:D

5.指出下列各式中哪个是四变量A、B、C、D的最小项

A.ABC;B. A+B+C+D;C.ABCD;D. A+B+D

答:C

6.测得某逻辑门输入A、B和输出F的波形如图所示,则F(A,B)的表达式为()

A.F=AB B. F=

C.F= D. F=A⊕B

答:B

7.函数F(A,B,C)=AB+AC的最小项表达式为( )。

答:C

13.一个16选一的数据选择器,其地址输入(选择控制输入)端的个数是()

A.1 B.2 C.4 D.16

答:C

14.半加器和的输出端与输入端的逻辑关系是()

A、与非B、或非C、与或非D、异或

答:D

15.逻辑数F=A +B ,当变量的取值为()时,将出现冒险现象。

A.B=C=1 B.B=C=0 C.A=1,C=0 D.A=0,B=0

(2-4章)第二讲 EDA的仿真技术

31

C 0 保持 0

功能表(74161功能 表与此相同)

X X X

74160时序图

Rd

LD

EDA

D0 D1 D2 D3

CP

1 1 1 0

S1 S2 Q0 Q1 Q2 Q3

C

1 1 1 0

0 0

0 1

1 0 0 1

0 0 0 0

计数

1 0 0 0

0 1 0 0

1 1 0 1 保持

Rd=1/LD=1

32

清零 置数 Rd=0 LD=0/S1=S0=1/Rd=1

集成同步二进制加计数器74161

符号:

Q0 Q0

CP LD

EDA

Q1 Q1

Q2 Q2

Q3 Q3

C C

74161

Q 0Q 1Q 2Q 3 R d S 1 S 2

34

清零 置数

集成同步十进制计数器74162

Q0 Q0 Q1 Q1 Q2 Q2 Q3 Q3

C C

EDA

符号:

CP LD

74163

Rd:同步复位信号,其它同 74163。74162是十进制计数器, 当计到9时进位输出变为高电平。

Q 0Q 1Q 2Q 3 R d S 1 S 2

CP

Rd 0 1 1 1 1

●

EWB的特点:

Ⅱ提供交互式的人机图形界面 ; Ⅲ 具有下拉式的电路编辑和即时波形显示功能; Ⅳ 具有虚拟的仪器仪表设备 Ⅴ 提供了较为详细的电路分析手段

4

Ⅰ具有完整的模拟和数字混合仿真的功能和元器件库;

数电课设-六进制同步加法计数器(无效态010-100)

目录之杨若古兰创作1.课程设计的目的与感化......................................... 错误!未定义书签。

2.设计任务.................................................................... 错误!未定义书签。

3.设计及仿真分析过程............................................. 错误!未定义书签。

3.1六进制同步加法计数器(有效态010,100) (2)3.1.1设计过程................................................ 错误!未定义书签。

3.1.2输出转换设计....................................... 错误!未定义书签。

3.1.3仿真分析................................................ 错误!未定义书签。

3.2 74160构成50进制同步加法计数器并显示 (6).2.1设计请求 (6)3.2.274LS160功能简介 ................................ 错误!未定义书签。

3.2.3仿真分析................................................ 错误!未定义书签。

4实验仪器. (7)5设计总结和体会 (7)6参考文献 (8)1.加深对教材的理解和思考,并通过实验设计、验证证明理论的准确性.2.进修自行设计必定难度并有效处的计数器、加法器、寄存器等.3.检测本人的数字电子技术把握能力.1.设计分析六进制同步加法计数器(有效态010,100)3.1六进制同步加法计数器(有效态010,100) 000 001 011 101 110 111 排列:012Q Q Q因为JK 触发器功能齐全,使用灵活,这里选用3个CP 降低沿触发的边沿JK 触发器采取同步, CP0=CP1=CP2=CP (式1)由图1所示的形态图可直接画出如图2 所示电路次态的卡诺图.再分解开即可以得到图3 所示的各触发器的卡诺图. 明显,由图3所示各卡诺图即可很容易得到形态方程:Q Q Q Q Q Q n n n n n n n n n n n n n n n n Q Q Q Q Q Q Q Q Q Q 1001210110112101212)(+⎪⎪⎪⎩⎪⎪⎪⎨⎧+=+=+=+++ (式2)JK 触发器的特征方程为:n n n Q K Q J Q +=+1(式3)变换形态方程(式2),使之与特征方程(式3)的方式分歧,比较后得出驱动方程=0J 1=0K (式4)将有效态010,101代入形态方程(式2)进行计算,结果如下: 010 111100有效态不成轮回,故此时序电路能自启动.将设计好的计数器输出端Q2n+1、Q1n+1、Q0n+1所示数据旌旗灯号通过门电路的组合转换成十位数输出,对应真值表列出如下表1表1输出形态转换表列出形态方程:C=Q2n+1B=Q2n+1Q0n+1+Q1n+1Q0n+1(式5)A=(Q2n+1Q1n+1+Q2n+1Q2n+1)Q0n+1+Q2n+1Q1n+1Q0n+1根据上步所设计的逻辑电路图,在Multisim中构建逻辑电路如下图所示图4图5图6图7图8图974160构成50进制同步加法计数器并显示请求使用两片集成芯片74LS160和一些须要的门电路设计一个50进制加法计数器.CLK是脉冲输入端;RCO是进位旌旗灯号输出端;ENP和ENT是计数器工作形态端;CLR是异步清零端;LOAD是置数端;VCC接正电源,GND接地;A~D是数据输入端,QA~QD是计数器形态输出端.电源电压5V,输入电压5V.其形态表下所示表2 74LS160形态表根据上步所设计的逻辑电路图,在Multisim中构建逻辑电路如图10所示图10. 50进制计数器仿真结果运转仿真电路,LED数码管从00开始顺次计数,累计到49后又跳转到00,实现50进制计数器的功能.4实验仪器集成芯片:74LS112芯片2个(每个芯片包含2个JK触发器),74LS00芯片1个(每个包含4个与非门电路),74LS08芯片1个(每个包含4个与门电路),74LS160芯片两片.数字道理教学零碎试验台一台(含导线、脉冲、电源等).5设计总结和体会经过本次课程设计,不但使我学到了很多的常识而且大大的提升了我的动手实践能力,使我受益匪浅.比方,在设计过程中,稍有失慎就会出错,所以,我们必定要高度的看重,仔细的去完成设计.接线过程是反映一个动手能力的平台,只需利用好它,对本人的动手能力很有帮忙.是以,我们必定要本着一丝不苟的精神来完成每次课设,捉住锻炼本人的机会,逐步提升本人的能力.6参考文献[1]《数字电子技术基础简明教程》第三版.清华大学电子学教研室组编. 余孟尝主编.高等教育出版社. 2006[2]《数字逻辑实验指点书》信息学院数字逻辑实验室编. 张利萍,张群芳主编.。

基础rs触发器逻辑功效测试[精彩]

![基础rs触发器逻辑功效测试[精彩]](https://img.taocdn.com/s3/m/7616447ea88271fe910ef12d2af90242a895ab62.png)

实训九基本R-S触发器功能测试一、实训目的1.通过实训熟悉基本RS触发器的逻辑功能和特点;2.通过实训掌握基本RS触发器的测试方法;3.通过实训熟悉异步输入信号RD、SD、RD、SD的作用;4.通过实训掌握基本RS触发器的典型应用;二、实训原理基本RS触发器是由两个与非门交叉耦合组成,它是最基本的触发器,也是构成其它复杂触发器电路的一个组成部分。

当R D=S D=1时,两个与非门的工作都尤如非门,Q接至与非门G2的输入,使G2输出为Q;Q接至与非门G1的输入,使G1的输出为Q。

从而使触发器维持输出状态不变。

三、实训仪器和设备S303-4型(或其它型号)数字电路实训箱一只;SR8(或其它型号)双踪示波器一只;直流稳压电源一台;74LS00 二输入四与非门1片。

四、实训内容和步骤1.两个TTL与非门首尾相接构成的基本R-S触发器的电路如图7-2-1所示逻辑电路。

图9-1 基本R-S触发器功能测试2.按表9-1所示的顺序在Sd、Rd两端信号,观察并记录R-S触发器Q端的状态,并将结果填入表9-1中表9-13.Sd4.Sd端接高电平,Rd端加脉冲。

5.令Sd=Rd,在Sd端加脉冲。

6.记录并观察2、3、4三种情况下,Q,Q n+1端的状态。

从中总结基本R-S触发器的Q端的状态改变和输入端的关系。

五、实训思考题试根据基本R-S触发器给定的输入信号波形画出与之对应的输出端的波形;试写出基本R-S触发器的约束方程,并说明哪个是复位端、哪个是置位端?六、训注意事项接线时要注意电路图中各引脚的编号,连接时不要接错;手动施加0、1输入电平时要注意开关动作的稳定性和可靠性,要避免开关的抖动;用双踪示波器观察输出波形时,要注意选择一个较为合适的输入信号的频率。

实训十. 计数器的功能测试一、实训目的1.掌握计数器的工作原理;2.通过实训熟悉计数器的功能特点和典型应用;3.通过实训掌握如何利用现有集成计数器来构成N进制计数器的方法。

电子秒表9分59秒99毫秒

《电子技术》课程设计报告题目数字式秒表学院(部)太原科技大学华科学院专业自动化班级自动化102201H学生姓名孔祥云学号************月日至月日共周指导教师(签字)目录一.设计任务和要求二.总体框图三.选择器件四.功能模块五.总体设计电路图六.课程总结七.故障分析数字式秒表一.设计要求:1、秒表由五位七段LED显示器显示,其中一位显示“min”,四位显示“s”,其中显示分辨率为0.01s,计时范围为0~9分59秒99毫秒;2、具有清零、启动计时、暂停计时及继续计时等功能;3、控制开关为两个;启动(继续)/暂停计时开关和复位开关。

二.总体框图由上图数字式秒表电路的结构框图可知,整个电路由方波信号发生器,分频电路,计数显示电路,启停电路与清零电路,五部分组成。

设计时,计数显示电路组成时间显示电路,键控部分由于控制各部分电路,故在单元电路设计分析时省去。

故该电路可以分为脉冲信号发生器、分频电路、计数器电路、时间显示电路、控制电路五大单元电路三.选择器件1.74LS160计数进74LS160D的引脚如右图2-3-5所示,从图中可以看到74LS160D共有16个引脚吗,其中有Cp脉冲输入引脚clk(下降沿有效),LOAD为预置数控制端(低电平有效),CLR为异步清零端(低电平有效), A、B、C、D为预置数输入端,ENP和ENT是计数使能端(高电平有效),RCO是进位输出端,QD、QC、QB、QA分别是计数输出位,其工作原理图如图2-3-6所示.74LS160管脚分布图图2-3-6 74LS160计数器工作原理图1)异步清零:当CLR端输入为低电平时候,其它输入端不管输入什么值,计数器将直接清零,也就是说输出的QD、QC、QB、QA为0000.2)同步预置数:当CLR端输入高电平,LOAD端输入低电平时,且有Cp脉冲下降沿作用时,完成将输入端DCBA的数据置入计数器操作,使Q D Q C Q B Q A=DCBA.由于这个操作需要CP下降沿同步,所以称为同步预置数。

100S计时器

100s计时器实验报告学院:物理电气信息学院姓名:学号:专业:电子信息工程班级:电子(1)班一、实验目的掌握100s计时器的设计步骤。

认识元器件及判断元器件。

了解元器件的焊接过程。

学习借助仪表查排故障。

二、实验原理1、直流电源及50HZ信号交流9V经桥式整流、滤波、三端稳压成5V直流为整机工作电源。

50HZ正弦交流信号经R1、C2变成锯齿波,再经Q1整形成50HZ方波从集电极输出。

2、CD4024(7位二进制串行计数器输入50HZ,输出1HZ。

D5、D6、D7组成二极管与门电路Q1~Q6为010011时输出1HZ。

RST复位端,高电平时清零。

3、CD4518(8421编程十进制同步加计数器)CLK为1Hz,EN高电平有效;IC4:2是低位,记到1001即到9时进高位到IC4:1。

RST复位端,高电平时清零。

4、CD4511(驱动共阴LED的BCD码七段译码器CD4511具有BCD码转换、消隐、锁存、七段译码、大电流驱动等特点。

功能:A、B、C、D端为BCD码输入,A为最低位;LT为显示测试端,高电位正常工作,低点位显示8;B1为消隐,高点位正常工作,低电位各段均不显示;LE为锁存控制,高电位锁存,低电位传输数据。

5数码管七段共阴数码管,七段阴极共地,从4511七段译码器A~G端送来的高电平信号点亮各字段。

6、控制电路74HC132的1、2与非门组成RS触发器,完成启动、停止控制。

C7为上电复位电容。

三、实验步骤1、清除覆铜板表面氧化层及油污,并用清洁水冲洗(轻砂多砂)2、热转印(转印纸对齐,一端用胶带在背面固定)3、修板(仔细检查电路,用油性记号笔修断点)4、腐蚀(用三氯化铁溶液腐蚀)5、打孔(先打小孔,后打大孔)6、用砂纸去除黑色热印层(轻砂多砂),去除墨层和钻孔毛束使焊点光亮。

7、修板(检查电路有无短路、断路)8、涂松香水(助焊、抗氧化)四、实验过程1、焊接在装配工作中,焊接技术很重要,元件的安装,主要利用锡焊,它不但能固定零件,而且能保证可靠的电流通路,焊接质量的好坏,将直接影响电路的质量。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

四川工商学院电子信息工程学院电子电路课程设计100进制计数器设计学生姓名杨露学号2015101027所在学院电子信息工程学院专业名称通信工程班级15通信(移动)(1)班指导教师周春梅成绩×××四川工商学院二○一七年十二月电子电路课程设计任务书计数器内容摘要:计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。

计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。

计数器可以用来显示产品的工作状态,一般来说主要是用来表示产品已经完成了多少份的折页配页工作。

它主要的指标在于计数器的位数,常见的有3位和4位的。

很显然,3位数的计数器最大可以显示到999,4位数的最大可以显示到9999。

关键词:计数器指令触发器CounterAbstract:The count is one of the most simple basic computing counter logic circuit is to realize this operation, the counter in digital systems is to count the number of pulses to achieve the measurement and counting and control functions, also has the function of frequency division, the counter is composed of basic counting unit and a control gate, a all kinds of trigger counting unit is composed of a series of information storage function, the trigger RS flip-flop, T flip-flop, D flip-flop, JK flip-flopetc.. The counter is widely used in digital systems, such as the address of the instruction count in the computer controller, in order to remove the order of the next instruction, in the arithmetic unit for multiplication and division operations to write down the number of addition and subtraction, and as in the digital instrument of pulse counting etc.. The counter can be used to display the working status of the product, are commonly used to indicate the product has completed a number of copies of the folding with page. Its main indicator is the number of bits of the counter, 3 - bit and 4 - bit common. It is clear that the maximum of the 3 digit counter can be displayed to 999, the maximum of the 4 digits can be displayed to 9999.Keywords:Counter Instructions Trigger目录前言 (1)1 设计内容 (1)1.1 设计要求 (1)2 涉及工具 (2)2.1 计数器 (2)2.1.1 计数器的应用 (2)2.1.2 计数器的种类 (2)2.2 触发器 (2)2.2.1 触发器的作用 (3)2.2.2 触发器的种类 (3)2.3 数码管 (4)2.3.1 数码管的结构 (4)2.3.1 数码管的应用范围 (4)3 实验流程 (4)3.1 新建工程 (4)3.2 书写程序 (6)3.3 程序仿真 (7)4 结束语 (11)附录 (12)附录1:程序 (12)参考文献 (13)100进制计数器前言计数器电路是一种随时钟输入CP的变化,其输出按一定的顺序变化的时序电路,其变化的特点不同可将计数器电路按以下几种进行分类:按照时钟脉冲信号的特点分为同步计数器和异步计数器两大类,其中同步计数中构成计数器的所有触发器在同一个时刻进行翻转,一般来讲其时钟输入端全连在一起;异步计数器即构成计数器的触发器的时钟输入CP没有连在一起,其各触发器不在同一时刻变化。

一般来讲,同步计数器较异步计数器具有更高的速度。

按照计数的数码变化升降分为加法计数器和减法计数器,也有一些计数器既可实现加计数又可实现减计数器,这类计数器为可逆计数器。

按照输出的编码形式可分为:二进制计数器、二—十进制计数器、循环码计数器等。

按计数的模数(或容量)分:十进制计数器、十六进制计数、六十进制计数器等。

1 设计内容设计出带有异步清零、同步使能、可预置初值和进位功能的8位100进制计数器设计。

1.1 设计要求在数字系统中,计数器不仅能记录输入时钟脉冲的个数,还可以实现分频、定时、产生节拍脉冲和脉冲序列等。

常用的计数器包括加法计数器、减法计数器和加减可逆计数器。

用层次化设计方法设计一个可控的100进制计数器的计数、译码电路:➢计数器的时钟输入信号为1s➢计数器的功能是从0到99计数2 涉及工具计数器,触发器,数码管。

2.1 计数器狭义的计数器是指一些常用计时器,例如体育比赛中测试时间的计时器等,但本词条所要介绍的并不是这种计时器,要介绍的是应用更为广泛的时序逻辑电路中的计数器。

2.1.1 计数器的应用计数器应用包括通话、短信、数据等类别的记录,并支持用户自主选择清零日期,以及按照类别添加提醒数值,如用户可以选择每月任一一天,或者第一天、最后一天作为记录循环清零日,同时添加通话时长、短信条数、数据流量数量的提醒节点。

计数器的应用极为广泛,不仅能用于计数,还可用于分频、定时,以及组成各种检测电路和控制电路。

为了使用方便,在有些单片集成计数器上还附加了异步置零、预置数、保持等功能,并设置了相应的控制端。

2.1.2 计数器的种类如果按照计数器中的触发器是否同时翻转分类,可将计数器分为同步计数器和异步计数器两种。

如果按照计数过程中数字增减分类,又可将计数器分为加法计数器、减法计数器和可逆计数器,随时钟信号不断增加的为加法计数器,不断减少的为减法计数器,可增可减的叫做可逆计数器。

另外还有很多种分类不一一列举,但是最常用的是第一种分类,因为这种分类可以使人一目了然,知道这个计数器到底是什么触发方式,以便于设计者进行电路的设计。

此外,也经常按照计数器的计数进制把计数器分为二进制计数器、十进制计数器等等。

2.2 触发器触发器(trigger)是SQL server 提供给程序员和数据分析员来保证数据完整性的一种方法,它是与表事件相关的特殊的存储过程,它的执行不是由程序调用,也不是手工启动,而是由事件来触发,比如当对一个表进行操作(insert,delete,update)时就会激活它执行。

触发器经常用于加强数据的完整性约束和业务规则等。

触发器可以从DBA_TRIGGERS ,USER_TRIGGERS 数据字典中查到。

SQL3的触发器是一个能由系统自动执行对数据库修改的语句。

触发器可以查询其他表,而且可以包含复杂的SQL语句。

它们主要用于强制服从复杂的业务规则或要求。

例如:您可以根据客户当前的帐户状态,控制是否允许插入新订单。

触发器也可用于强制引用完整性,以便在多个表中添加、更新或删除行时,保留在这些表之间所定义的关系。

然而,强制引用完整性的最好方法是在相关表中定义主键和外键约束。

如果使用数据库关系图,则可以在表之间创建关系以自动创建外键约束。

触发器与存储过程的唯一区别是触发器不能执行EXECUTE语句调用,而是在用户执行Transact-SQL语句时自动触发执行2.2.1 触发器的作用可在写入数据表前,强制检验或转换数据;触发器发生错误时,异动的结果会被撤销;部分数据库管理系统可以针对数据定义语言(DDL)使用触发器,称为DDL触发器;可依照特定的情况,替换异动的指令(INSTEAD OF)。

2.2.2 触发器的种类DML触发器:当数据库中表中的数据发生变化时,包括insert,update,delete任意操作,如果我们对该表写了对应的DML触发器,那么该触发器自动执行。

DML触发器的主要作用在于强制执行业务规则,以及扩展Sql Server约束,默认值等。

因为我们知道约束只能约束同一个表中的数据,而触发器中则可以执行任意Sql命令。

DDL触发器:它是Sql Server2005新增的触发器,主要用于审核与规范对数据库中表,触发器,视图等结构上的操作。

比如在修改表,修改列,新增表,新增列等。

它在数据库结构发生变化时执行,我们主要用它来记录数据库的修改过程,以及限制程序员对数据库的修改,比如不允许删除某些指定表等。

登录触发器:登录触发器将为响应LOGIN 事件而激发存储过程。

与SQL Server 实例建立用户会话时将引发此事件。

登录触发器将在登录的身份验证阶段完成之后且用户会话实际建立之前激发。

因此,来自触发器内部且通常将到达用户的所有消息(例如错误消息和来自PRINT 语句的消息)会传送到SQL Server 错误日志。

如果身份验证失败,将不激发登录触发器。

2.3 数码管数码管是一种半导体发光器件,其基本单元是发光二极管。

数码管按段数可分为七段数码管和八段数码管,八段数码管比七段数码管多一个发光二极管单元,也就是多一个小数点(DP)这个小数点可以更精确的表示数码管想要显示的内容;按能显示多少个(8)可分为1位、2位、3位、4位、5位、6位、7位等数码管。