触发器代码VHDL

第19讲VHDL顺序描述语句

END rsff; ARCHITECTURE rtl OF rsff IS BEGIN

PROCESS(s,r) VARIABLE last_state :BIT;

BEGIN ASSERT(NOT(s =‘1’AND r =‘1’)) REPORT “Both s and r equal to‘1’.” SEVERITY ERROR; IF(s =‘0’AND r =‘0’)THEN last_state := last_state; ELSIF(s =‘0’AND r =‘1’)THEN last_state := 0; ELSE last_state := 1; END IF; q <= last_state; qb <= not(last_state);

q <= tmp2;

END PROCESS;

END rtl;

上例是一个取三个输入位矢量最大值的功能描述, 它在结构体中的进程语句中使用了两个过程调用语 句。

B. 函数调用语句

函数调用与过程调用是十分相似的,不同之处是, 调用函数将返还一个指定数据类型的值,函数的参 量只能是输入值。

函数语句分为两个部分,函数首和函数体。 (1)函数首的格式为: FUNCTION 函数名称(参数列表) RETURN 数据类型名; (2)函数体的格式为: FUNCTION 函数名称(参数列表) RETURN 数据类型名 IS

RETURN语句是一段子程序结束后,返回主程序的控制 语句。它只能用于函数与过程体内,并用来结束当前最内层 函数或过程体的执行。

RETURN语句的书写格式为:

RETURN; RETURN 表达式;

EDA技术实用教程-VHDL版课后答案

第一章1-1 EDA技术与ASIC设计和FPGA开发有什么关系? P3~4答:利用EDA技术进行电子系统设计的最后目标是完成专用集成电路ASIC的设计和实现;FPGA和CPLD是实现这一途径的主流器件。

FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC。

FPGA和CPLD的应用是EDA技术有机融合软硬件电子设计技术、SoC(片上系统)和ASIC设计,以及对自动设计与自动实现最典型的诠释。

1-2与软件描述语言相比,VHDL有什么特点? P6答:编译器将软件程序翻译成基于某种特定CPU的机器代码,这种代码仅限于这种CPU而不能移植,并且机器代码不代表硬件结构,更不能改变CPU的硬件结构,只能被动地为其特定的硬件电路结构所利用。

综合器将VHDL 程序转化的目标是底层的电路结构网表文件,这种满足VHDL设计程序功能描述的电路结构,不依赖于任何特定硬件环境;具有相对独立性。

综合器在将VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约束条件,选择最优的方式完成电路结构的设计。

l-3什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么? P5什么是综合? 答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

有哪些类型? 答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。

(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。

(3)从RTL级表示转换到逻辑门(包括触发器)的表示,即逻辑综合。

(4)从逻辑门表示转换到版图表示(ASIC设计),或转换到FPGA的配置网表文件,可称为版图综合或结构综合。

综合在电子设计自动化中的地位是什么? 答:是核心地位(见图1-3)。

VHDL5套试卷标准答案

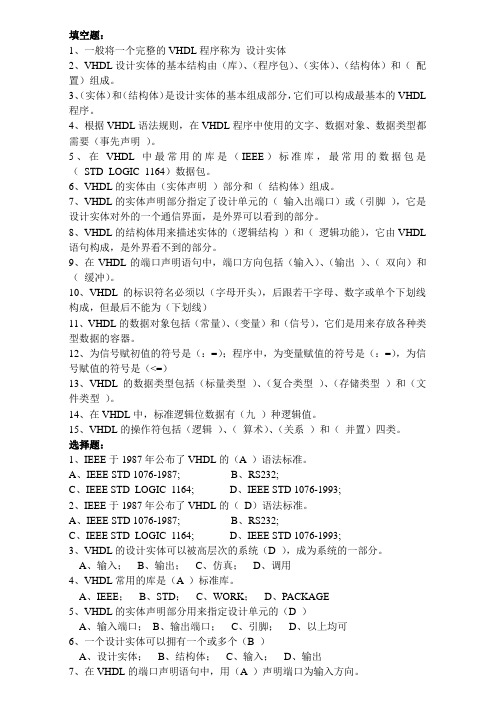

填空题:1、一般将一个完整的VHDL程序称为设计实体2、VHDL设计实体的基本结构由(库)、(程序包)、(实体)、(结构体)和(配置)组成。

3、(实体)和(结构体)是设计实体的基本组成部分,它们可以构成最基本的VHDL 程序。

4、根据VHDL语法规则,在VHDL程序中使用的文字、数据对象、数据类型都需要(事先声明)。

5、在VHDL中最常用的库是(IEEE)标准库,最常用的数据包是(STD_LOGIC_1164)数据包。

6、VHDL的实体由(实体声明)部分和(结构体)组成。

7、VHDL的实体声明部分指定了设计单元的(输入出端口)或(引脚),它是设计实体对外的一个通信界面,是外界可以看到的部分。

8、VHDL的结构体用来描述实体的(逻辑结构)和(逻辑功能),它由VHDL 语句构成,是外界看不到的部分。

9、在VHDL的端口声明语句中,端口方向包括(输入)、(输出)、(双向)和(缓冲)。

10、VHDL的标识符名必须以(字母开头),后跟若干字母、数字或单个下划线构成,但最后不能为(下划线)11、VHDL的数据对象包括(常量)、(变量)和(信号),它们是用来存放各种类型数据的容器。

12、为信号赋初值的符号是(:=);程序中,为变量赋值的符号是(:=),为信号赋值的符号是(<=)13、VHDL的数据类型包括(标量类型)、(复合类型)、(存储类型)和(文件类型)。

14、在VHDL中,标准逻辑位数据有(九)种逻辑值。

15、VHDL的操作符包括(逻辑)、(算术)、(关系)和(并置)四类。

选择题:1、IEEE于1987年公布了VHDL的(A)语法标准。

A、IEEE STD 1076-1987;B、RS232;C、IEEE STD_LOGIC_1164;D、IEEE STD 1076-1993;2、IEEE于1987年公布了VHDL的(D)语法标准。

A、IEEE STD 1076-1987;B、RS232;C、IEEE STD_LOGIC_1164;D、IEEE STD 1076-1993;3、VHDL的设计实体可以被高层次的系统(D ),成为系统的一部分。

VHDL入门:关于按键消抖的那个process

这学期的EDA课程设计有涉及到一个按键信号稳定的问题,虽然就算没有这块处理,最后成绩只会扣3分,但自己觉得像LED亮度变化,数字钟设置这些功能,如果没有加进一个稳定按键信号的模块,根本不能算是已实现的功能。

按键消抖的程序在网上有几种可供选择,但这里只讨论一种,本人觉得简单得来又比较强大的一种。

其实消抖的原理就是把一个按键周期内所输入的所有有效信号,包括那些毛刺,处理成一个脉冲输入。

能达到这点,就可以实现消抖功能了。

功能的源代码:代码中的 key 是按键输入,count 是自定义的计数器,N的值可以根据需要结合时钟频率设置,如果只是想达到按键一次输入一个脉冲的效果,建议 count 的时长设为 5ms,key_en 是处理完后输出的单个脉冲,至于有效信号是 '0' 还是'1' ,这要看板上的电路设计了。

此代码中是 '0' 为有效信号。

不要怀疑这段代码有错,理清逻辑后再套用,如果弄不明白什么原理,建议还是别用,用了可能会更糟糕。

要注意的是一个 process 中只能有一个时钟信号,否则很容易出错,就算编译通过,实际操作还是不行。

所以如果要对多个按键消抖,一定要在 "if clk'event and clk='1' then" 语句的内部增加,别重新设置一个 clk'event 。

还有就是按键的消抖功能块最好用单独的 process 运行,将 key_en 设置成新的按键输入信号,而实际的输入信号 key 只在按键消抖的process 中读入。

之所以说这种消抖方法简单得来又比较强大,是因为这方法不需要用到什么状态机、component 之类较高级点的东西,只需要多个 process 即可;另外这种方法还有其他的拓展用途,比如可以利用这个 count 延时周期设置一个短按键和长按键的识别,实现长按此键切换或者 reset 等等的功能,这里不详细解释。

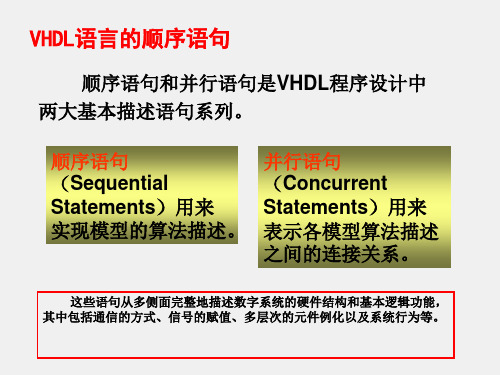

第五章_VHDL语言的主要描述语句

例:

library ieee; use ieee.std_logic_1164.all; entity kdec24 is port(a:in std_logic_vector (1 downto 0); en:in std_logic; f:out std_logic_vector (3

architecture d of kdec24 is begin

执行到该语句等待20ns以后,再继续执行下一条指令。

wait for( a*(b+c));

若a=2,b=50ns,c=70ns, 则执行到该语句时,就要等待2*(50+70)=240ns后, 再继续执行后续语句。

2016/3/23 20

例:利用wait for构成输入信号波形

process entity inhibittestbench is begin end entity inhibittestbench; xt<='0';yt<='0'; architecture beh of wait for 10 ns; inhibittestbench is xt<='0';yt<='1'; component inhibit is wait for 10 ns; port (x,y:in bit;z: out bit); xt<='1';yt<='0'; end component inhibit; wait for 10 ns; signal xt,yt,zt:bit; xt<='1';yt<='1'; begin wait; --进入无限期等待, u1: inhibit port map (xt, yt, 避免进入无限期循环; zt); end process; end architecture beh;

第19讲 VHDL顺序描述语句(4)

上例是一个对两个输入整数取最大值的功能描述,在结构体的进程中定义 了一个取最大值的函数。在函数体中正是通过RETURN语句将比较得到的 最大值返回的,并结束该函数体的执行。

NULL语句

NULL语句是空操作语句,不完成任何操作,执行NULL语句

只是让程序运行流程走到下一个语句。

NULL语句的书写格式为:NULL; 常用于CASE语句中,利用NULL来表示所余的不用的条件下 的操作行为,以满足CASE语句对条件值全部列举的要求。 CASE Opcode IS WHEN "001" => tmp := rega AND regb ; WHEN "101" => tmp := rega OR regb ; WHEN "110" => tmp := NOT rega ; WHEN OTHERS => NULL ; END CASE ;

BEGIN ASSERT(NOT(s ='1'AND r ='1'))

REPORT "Both s and r equal to '1'"

SEVERITY ERROR; IF(s ='0' AND r ='0') THEN last_state := last_state; ELSIF(s ='0'AND r ='1') THEN last_state := '0'; ELSE

q:OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );

END max;

ARCHITECTURE rtl OF max IS procedure maximum(a,b:IN STD_LOGIC_VECTOR; c:out std_logic_vector) IS BEGIN IF(a > b)THEN c := a;

VHDL教程

LE2 进位输出 (到 LAB中的下一个逻辑单元) 27

FLEX 系列的级联链

性能优越, 适合扇入大的逻辑功能

“与”级联链

2.4 ns

“或”级联链

LE 1

0.6 ns

LE1 IN [3..0] LUT

IN [3..0]

LUT

LE2 IN [4..7] LUT IN [4..7] LUT

LE2

16位地址译码速度可达 2.4 + 0.6x3=4.2 ns

23

连续布线和分段布线的比较

连续布线 ( Altera 基于查找表(LUT)的 FPGA )

LAB

LE

24

连续布线 = 每次设计重复的可预测性和高性能

FLEX 10K系列FPGA结构图

IOC IOC IOC IOC IOC IOC IOC IOC

. . .

. . .

. . .

. . .

嵌入式 阵列块

• EAB的大小灵活可变 256x8 512x4 2048x1

1024x2

• 通过组合EAB 可以构成更大的模块 • 不需要额外的逻辑单元,不引入延迟, EAB 可配置为深度达2048的存储器 512x4 512x4

256x8 256x8

256x16

512x8

30

FLEX 10K 系列的EAB

数据宽度 8,4,2,1 地址宽度 8,9,10,11

什么是查找表?

• 一个N输入查找表 (LUT,Look Up Table)可以实现N个输入 变量的任何逻辑功能,如 N输入“与”、 N输入“异或” 等。 • 输入多于N个的函数、方程必须分开用几个查找表( LUT) 实现

输入1 输入2 查黑 找盒 表子

VHDL简单实例

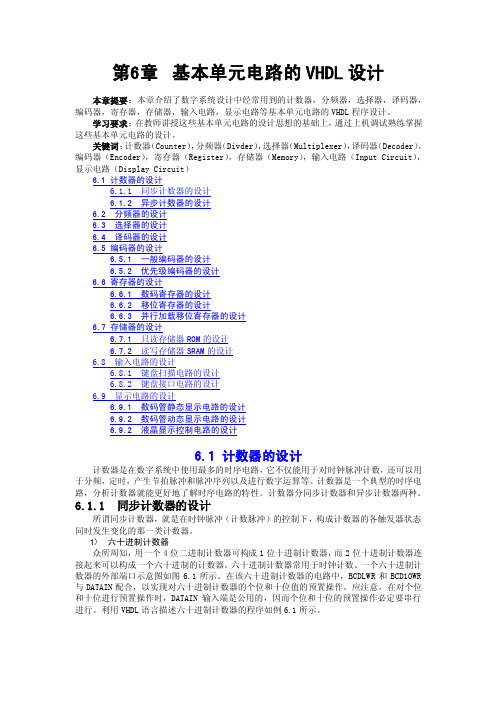

第6章基本单元电路的VHDL设计本章提要:本章介绍了数字系统设计中经常用到的计数器,分频器,选择器,译码器,编码器,寄存器,存储器,输入电路,显示电路等基本单元电路的VHDL程序设计。

学习要求:在教师讲授这些基本单元电路的设计思想的基础上,通过上机调试熟练掌握这些基本单元电路的设计。

关键词:计数器(Counter),分频器(Divder),选择器(Multiplexer),译码器(Decoder),编码器(Encoder),寄存器(Register),存储器(Memory),输入电路(Input Circuit),显示电路(Display Circuit)6.1 计数器的设计6.1.1 同步计数器的设计6.1.2 异步计数器的设计6.2 分频器的设计6.3 选择器的设计6.4 译码器的设计6.5 编码器的设计6.5.1 一般编码器的设计6.5.2 优先级编码器的设计6.6 寄存器的设计6.6.1 数码寄存器的设计6.6.2 移位寄存器的设计6.6.3 并行加载移位寄存器的设计6.7 存储器的设计6.7.1 只读存储器ROM的设计6.7.2 读写存储器SRAM的设计6.8 输入电路的设计6.8.1 键盘扫描电路的设计6.8.2 键盘接口电路的设计6.9 显示电路的设计6.9.1 数码管静态显示电路的设计6.9.2 数码管动态显示电路的设计6.9.2 液晶显示控制电路的设计6.1 计数器的设计计数器是在数字系统中使用最多的时序电路,它不仅能用于对时钟脉冲计数,还可以用于分频,定时,产生节拍脉冲和脉冲序列以及进行数字运算等。

计数器是一个典型的时序电路,分析计数器就能更好地了解时序电路的特性。

计数器分同步计数器和异步计数器两种。

6.1.1 同步计数器的设计所谓同步计数器,就是在时钟脉冲(计数脉冲)的控制下,构成计数器的各触发器状态同时发生变化的那一类计数器。

1) 六十进制计数器众所周知,用一个4位二进制计数器可构成1位十进制计数器,而2位十进制计数器连接起来可以构成一个六十进制的计数器。