FPGA在增量式编码器接口电路设计中的应用

一种增量编码器的接口电路设计

• 199•引言:在自动控制领域,电编码器常用于速度与位置的检测。

增量式编码器不能直接获得转动系统的速度和位置信息,只能通过处编码器输出的两路脉冲信号来计算这两个位置的相对角度差。

本文设计了一种通用的增量式编码器计数和辨向电路,可以将编码器输出的两路脉冲信号处理为倍频脉冲信号和转向电平信号,直接进入单片机处理器进行计数和判定旋转方向。

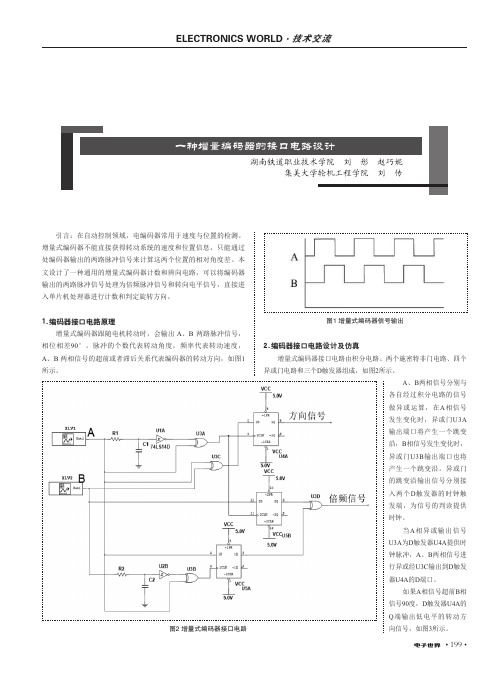

1.编码器接口电路原理增量式编码器跟随电机转动时,会输出 A 、B 两路脉冲信号,相位相差90°。

脉冲的个数代表转动角度,频率代表转动速度,A 、B 两相信号的超前或者滞后关系代表编码器的转动方向,如图1所示。

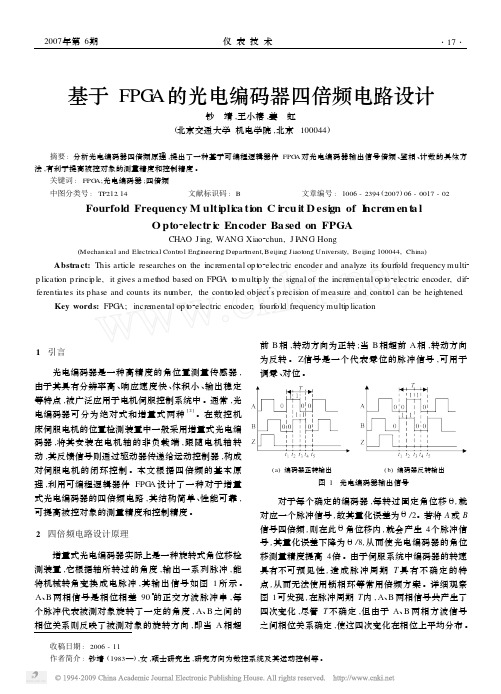

图1 增量式编码器信号输出2.编码器接口电路设计及仿真增量式编码器接口电路由积分电路、两个施密特非门电路、四个异或门电路和三个D 触发器组成,如图2所示。

一种增量编码器的接口电路设计湖南铁道职业技术学院 刘 彤 赵巧妮集美大学轮机工程学院 刘 传图2 增量式编码器接口电路A 、B 两相信号分别与各自经过积分电路的信号做异或运算,在A 相信号发生变化时,异或门U3A 输出端口将产生一个跳变沿,B 相信号发生变化时,异或门U3B 输出端口也将产生一个跳变沿。

异或门的跳变沿输出信号分别接入两个D 触发器的时钟触发端,为信号的判读提供时钟。

当A 相异或输出信号U3A 为D 触发器U4A 提供时钟脉冲,A 、B 两相信号进行异或经U3C 输出到D 触发器U4A 的D 端口。

如果A 相信号超前B 相信号90度,D 触发器U4A 的Q 端输出低电平的转动方向信号,如图3所示。

• 200•图3 A相超前B相90度方向信号仿真如果A 相信号滞后B 相信号90度,D 触发器U4A 的Q 端输出高电平的转动方向信号,如图4所示。

图4 B相超前A相90度方向信号仿真A 相跳变沿信号输出接D 触发器U5B 时钟触发端,B 相信号接U5B 的D 输入端,B 相跳变沿信号输出接D 触发器U5A 时钟触发端,A 相信号接U5A 的D 输入端,D 触发器U5A 和U5B 的输出端经异或门电路U3D ,在跳变沿的时钟下严格输出倍频信号,增加了计数脉冲数量,提高测量精度,倍频仿真波形如图5所示。

基于FPGA增量式编码器的接口设计与实现

信。同时在并 口之前 ,用锁存电路来消除硬件电路延 时所 可 能 引起 的计 数 错 误 ,减 轻 了后 续 微 机 的 负担 ,

可 提高 被控对 象 的测 量和 控制精 度 。

光 电编码器 在 现代 电机 控制 系统 中常用 以检 测转

子的位置与速度 ,是通过光电转换将输出轴上 的机械

几 何位 移 量转换 成 脉 冲或 数 字量 的高 精度 角位 置 测量 传 感 器 。 由 于 其 具 有 分 辨 率 高 、响应 速 度 快 、体 积 小 、输 出稳 定 等特 点 ,被 广 泛应 用于 电机伺 服 控 制 系

(c ol f e cm u i t n ,X’ eho g a U i r t,X’ 0 2 h a Sho o l o m nc i s inTc nl i l nv sy i n 1 3 ,C i ) T e ao a o c ei a 7 0 n

Ab ta t Opia —n rme t n o e , wh c sas ald p oo lcrc a g rp st n s n o , i h oe o sr c tc li ce na e c d r l ih i lo c e h tee ti n e- o ii e s r ste c r f l o

部 件 。 分 析 了光 电编 码 器 4倍 频 原 理 ,提 出 了 一 种 基 于 可 编 程 逻 辑 器 件 F G 对 光 电 增 量 式 编 码 器 输 出信 号 4倍 频 、 PA

鉴 相、计数 的具体方法 ,它对提 高编码 器分辨 率与实现 高精 度、高稳定性的信号检测及位 置伺服控 制具有一 定的现 实

d vc n me s r me to trs e d a d rtrp st n i rv r s se . Th ril e e rh s o h n rme tl e ie i au e n fmoo p e n oo o ii n d ie y tm o e a t e r s ac e n t e i ce n a c

基于FPGA的光电编码器四倍频电路设计

收稿日期:2006-11 作者简介:钞靖(1983—),女,硕士研究生,研究方向为数控系统及其运动控制等。

基于FPG A 的光电编码器四倍频电路设计钞 靖,王小椿,姜 虹(北京交通大学机电学院,北京100044) 摘要:分析光电编码器四倍频原理,提出了一种基于可编程逻辑器件FPG A 对光电编码器输出信号倍频、鉴相、计数的具体方法,有利于提高被控对象的测量精度和控制精度。

关键词:FPG A;光电编码器;四倍频中图分类号:TP212.14 文献标识码:B 文章编号:1006-2394(2007)06-0017-02Fourfold Frequency M ulti pli ca ti on C i rcu it D esi gn of I ncre m en t a lO pto 2electr i c Encoder Ba sed on FPGACHAO J ing,WANG Xiao 2chun,J I A NG Hong(Mechanical and Electrical Contr ol Engineering Depart m ent,Beijing J iaot ong University,Beijing 100044,China )Abstract:This article researches on the incre mental op t o 2electric encoder and analyze its f ourf old frequency multi 2p licati on p rinci p le,it gives a method based on FPG A t o multi p ly the signal of the incre mental op t o 2electric encoder,dif 2ferentiates its phase and counts its nu mber,the contr oled object πs p recisi on of measure and contr ol can be heightened .Key words:FPG A;incre mental op t o 2electric encoder;f ourf old frequency multi p licati on1 引言光电编码器是一种高精度的角位置测量传感器,由于其具有分辨率高、响应速度快、体积小、输出稳定等特点,被广泛应用于电机伺服控制系统中。

增量型编码器信号类型及其接口

电力系统2019.11 电力系统装备丨67Electric System2019年第11期2019 No.11电力系统装备Electric Power System Equipment 目开发及建设者除了要考虑光照资源、安装条件、上网条件、电价因素、组件及其他设备成本外,鉴于屋顶光伏项目更多应用于自发自用或自发自用余电上网的模式,开发及建设单位需要尽量利用项目场地条件,通过优化方案、降低建设成本和运维费用,进而降低度电成本。

随着太阳能光伏发电效率的不断提高和电站系统建设成本的不断下降,自主型投资资本会加速进入建筑光伏发电领域,推动屋顶电站广泛应用。

本文暂未纳入电价因素,可以想象,在某些峰谷电价差显著的地区,或者工商业电价较高的负荷地区,参考此文对比结果,采用满铺方案尽量多发电将会带来更高的收益。

参考文献[1] G B50797-2012,光伏发电站设计规范[S].[2] P Vsyst 6.75使用手册.[3] G B19964-2012,光伏发电站接入电力系统技术规定[S].[4] 晶澳JAP6-72-330/3BB 型组件技术资料.[5] 正泰CPS SC100KT-O/US-480组串式逆变器技术资料.在现代控制领域中编码器的应用非常广泛,编码器主要分为增量型和绝对值型两种。

增量型编码器因其价格低廉,应用简便,在实际生产中较绝对值型编码器应用更普遍。

其既可以与变频器、伺服控制器等驱动装置的接口直接连接,也可以与计数器、计算机、PLC 等设备连接,实现角度、长度、速度、位置测量或设备的同步控制。

增量型编码器的品牌和型号繁多,不同品牌和型号的编码器的电压、分辨率、信号类型、抗干扰能力、传输距离以及兼容性等各不相同,信号和接口的表述方式存在差异,给日常应用带来诸多不便。

在这里重点对增量型编码器信号及其兼容性进行分析,以帮助大家在实际应用中正确选择和使用增量型编码器。

1 增量型编码器输出类型增量型编码器有多种输出类型,常见的如TTL 、HTL 、RS422、PNP 、NPN 、推挽式输出等,这些类型之间有的可以兼容,有的不能兼容,有的兼容但稳定性差,导致编码器在实际应用中经常出现一些莫名其妙的问题。

基于FPGA的绝对式编码器的解码电路设计

Ma n u f a c t u r i n g T e c h n o l o g y , G u a n g x i 5 3 0 0 0 4, C h i n a )

c o n t r o l l e r . T h e n md u l a r i z a t i o n c o n c e p t wa s a p p l i e d t o t h e c i r c u i t , wh i c h c o n s i s t s o f d e c o d i n g , d e s e r i a l i z e r , c y c l i c r e d u n d a n c y c h e c k i n g , d a t a - s e p a r a t i o n p r o c e s s i n g nd a o t h e r m o d u l e s . T h e r e s u l t s s h o w t h a t t h i s F P G A— b a s e d d e c o d i n g c i r c u i t C n a i m p l e me n t t h e c o mmu n i c a t i o n b e t w e e n t h e a b s o l u t e e n c o d e r o f T S 5 6 4 3 N1 0 0 a n d f o l l o w- u p p r o c e s s o r . T h e c o n t r o l l e r o f u p p e r c o mp u t e r c a n a c q u i r e i n f o r ma t i o n f r o m e n e o d e r v i a t h i s c i r c u i t . T h e s e i n d i c a t e t h a t F P GA— b a s e d d e c o d i n g c i r c u i t ma y r e p l a c e t h e e x — p e n s i v e s p e c i a l c o n v e n e r o f AU5 6 8 8 c h i p a n d c a n s i mp l i f y t h e d e s i g n o f s y s t e m s t r u c t u r e a n d r e d u c e p r o d u c t S c o s t .

基于FPGA的循环码编译码器设计与实现

基于FPGA的循环码编译码器设计与实现摘要循环码编译码器性能稳定,有较强的检错、纠错能力,在通信、军事方面具有广泛的应用。

本次设计采用基于VHDL语言,以FPGA为硬件载体,设计了一个循环码编译码器。

设计分为编码器和译码器两部分,其中编码器可以为(15,7)循环码进行编码器,译码器电路由迭代译码算法电路、钱氏搜索译码算法电路、差错定位电路以及译码电路等组成。

在MaxplusⅡ开发平台上进行编译、仿真,设计的编码器可以完成7位信息码的循环码编码,译码器可以完成检错和两位错码的纠错,仿真结果证明了编译码器设计合理,达到预期目标。

关键词:VHDL;循环码;编码器;译码器DESIGN AND IMPLEMENTATION OF A CYCLIC CODE OFFPGA-BASED CODECSABSTRACTCyclic code codec performances stable, has strong error detection, error correction capability with a wide range of applications in the communications, military. Designing a Codec with VHDL as development language, and FPGA as hardware support. This design is divided into two parts, the encoder and decoder, and encoder is (15,7) cyclic code encoder, decoder circuit can be divided into iterative decoding algorithm circuit, Chien search circuit decoding algorithm, error location circuit and decoding circuits, etc. After compilation, simulation development platform on Maxplus II, the encoder can be completed on 7 cyclic code encoding information code, decoder can complete error detection and error correction two error codes, and it proved the rationality of codec designed, achieved the desired goals.Key words: VHDL; Cyclic code; Encoder; Decoder目录1 绪论 (1)1.1 研究背景以及发展现状 (1)1.2 研究目的及意义 (1)2 相关原理 (3)2.1 线性分组码 (3)2.2 循环码 (4)2.2.1 定义 (4)2.2.2 任一(n,k)循环码的生成多项式 (5)2.2.3 循环码的编码 (6)2.2.4 循环码的译码 (6)2.3 BCH码 (6)3 编译码器设计 (9)3.1 编码器设计原理 (9)3.2 译码器设计原理 (10)3.2.1由接收多项式r(x)求伴随式s (9)3.2.2由伴随式s求出错误位置 (10)4 编译码器实现 (13)4.1 编译码器实现流程图 (13)4.2 编码器实现 (14)4.3 译码器实现 (16)4.3.1 迭代译码算法电路以及相应代码实现 (16)4.3.2 钱氏搜索译码算法电路以及相应代码实现 (16)4.3.3 差错定位电路以及相应代码实现 (18)4.3.4 译码电路以及相应代码实现 (20)4.4 编码器顶层文件生成模块 (23)4.5 译码器顶层文件生成模块 (23)4.6 编译码器模块仿真 (21)4.6.1 编码器模块仿真 (21)4.6.2 译码器模块仿真 (24)4.7 FPGA板级验证 (23)5 总结 (27)参考文献 (26)致谢 (27)附录 (28)附件1:开题报告 (41)附件2:译文及原文影印件 (53)1 绪论1.1 研究背景以及发展现状循环码中,在码集中对两个码组编码,使用非进位相加,和仍属这个码组;这个码组里,把里面任何码组编码,然后对这个码组实行向左循环移位的操作,此时编出码依旧是此码组的[1]。

基于FPGA的接口转换电路设计

基于FPGA的接口转换电路设计摘要:21世纪是信息化的世纪,计算机技术迅速发展,越来越多的计算机采用传输速率更快且性能更加优良的USB接口,而个人计算机上的RS232,正在逐渐被淘汰。

但在工业领域中RS232应用仍十分广泛。

本文在此应用背景下,研究和设计USB与RS232之间的接口转换电路,硬件开发采用了SOPC设计,添加不同功能的模块,构建NIOSII系统,在QuartuII中完成硬件开发,而软件开发在NIOSIIIDE中完成,利用FPGA 平台,实现USB与RS232之间的接口转换,实现上位控制计算机与底层设备之间的数据通信。

关键词:USB接口;RS232接口;FPGA;SOPC随着计算机科学技术的迅速发展,如今对计算机的数据通信速度有了更高的要求,因此计算机的外围接口也发展迅速。

由于USB在个人计算机上应用越来越广泛,逐渐淘汰了RS232,但目前仍然很多采用RS232串行接口的工业设备、仪器仪表领域中,考虑到可行性和成本原因,立即将这些设备改造成USB接口是不可行的。

因此本文选择在FPGA开发平台下实现USB转RS232接口,通过这样将计算机与传统的设备相连,实现USB与RS232接口的双向数据传输,同时也扩大了USB的传输距离。

一、基于FPGA嵌入式IP的SOPC系统基于FPGA的嵌入式IP硬核SOPC系统是在FPGA中预先植入NIOS处理器。

为了更好的通用性,必须将常规的嵌入式处理器集成诸多通用和专用的接口,但这样又不得不增加芯片的成本和功耗。

但如果将ARM或者其他处理器核以IP硬核的方式植入FPGA中,利用FPGA的可编程逻辑资源和可擦除性,按照系统功能需求来添加接口功能模块,如USB模块和RS232模块,既能实现目标系统功能,又能实现系统的低成本和低功耗。

这样使得FPGA灵活的硬件设计与处理器的强大软件功能有机地结合在一起,更有效地实现SOPC系统。

虽然基于FPGA嵌入IP硬核能有效降低系统成本和功耗,但也有不足之处:(1)IP硬核多来自第三方公司。

基于FPGA增量式编码器的接口设计与实现

文中设计了一个基于FPGA的简单且精度高的接口电路,其结构简单、性能可靠。具有滤波、硬件辨向、4倍频计数和数据锁存等功能。计数结果以并口输出,可与PC机、ARM或FPGA等部件进行并行通信。同时在并口之前,用锁存电路来消除硬件电路延时所可能引起韵计数错误,减轻了后续微机的负担,可提高被控对象的测量和控制精度。

运用FPGA实现4倍频、鉴相电路,采用全数字反馈电路的设计方法,由于倍频、鉴相电路设计在同一芯片上,一方面,FPGA门电路高数量较大,时钟频率可达上百MHz的可编程逻辑器件,可以把他设计成所需的各种逻辑器件,可并行处理多项任务。因此处理速度比单片机或DSP快得多;另一方面,芯片内部的门电路、触发器的参数特性完全一致,能保证在相同转速下4倍频脉冲信号的周期保持一致。作为板级芯片,电路做在芯片内部,其抗干扰能力比分离器件有很大提高。同时,由于现场可编程,可以方便地实现对电路的重新设计或修改,增强了系统的灵活性、通用性和可靠性。

3 仿真波形

用Verilog HDL语言完成电路描述,各功能模块运用原理图方式进行描述,芯片采用Ahera公司Cyclone系列的EP1C12Q240C8N。在Quart-usII10.0环境下进行功能和时序仿真。编译后结果,A、B即为差分整形电路的输出,当A相超前B相时,输出正向4倍频脉冲,OA[7..0]为编码器正转时4倍频脉冲个数;反之,输出反向4倍频脉冲,OB[7..0]为反转时4倍频脉冲个数。利用OA[7..0]与OB[7..0]可以方便地实现编码器的可逆计数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPG A在增量式编码器接口电路设计中的应用孙士尉1,刘立军2(11河北工程技术高等专科学校,061001;21廊坊开发区昂瑞自动化工程有限公司,065000)摘要:利用FPG A和Veril og HDL语言,采用自顶向下的设计方法,设计了增量式光电编码器的接口电路,具有硬件辨向、倍频和计数等功能,可与微机或DSP并行通讯,并消除了硬件延时可能引起的错误。

关键词:增量式光电编码器;FPG A;Veril og HDL;接口中图分类号:TP302 文献标识码:B 文章编号:1004-0420(2008)04-0021-030 前言光电编码器在现代电机控制系统中常常用以检测转子的位置与速度,是通过光电转换将输出轴上的机械几何位移量转换成脉冲或数字量的传感器。

按信号输出形式分为两种类型:绝对式和增量式。

绝对式光电编码器具有输出数字量可与微机或DSP直接接口,无累积误差等优点,但是价格高、制造工艺复杂,不宜实现小型化。

增量式光电编码器不具有计数和接口电路,一般是输出A、B、Z脉冲信号,但是价格较低,因此比较常用。

增量式光电编码器的输出信号可以直接连接到微机或DSP的计数器输入端,由其软件来辨相和计数。

而这占用了微机的硬件资源和软件执行时间,对于微机系统运行繁忙或实时性较高的场合是不允许的。

市场上也有实现光电编码器与电机控制系统连接的仪表,但是价格昂贵,使用也比较复杂。

本文设计了一个基于FPG A的简单且精度高的接口电路,具有硬件辨向与计数功能,计数结果以并口输出,可与微机或DSP并行通讯。

同时在并口之前用锁存电路来消除硬件电路延时所可能引起的计数错误,减轻了后续微机的负担。

1 接口电路总体方案设计增量式光电编码器利用双光栅叠栅条纹技术,对空间位置进行光学放大,通过光电接收器输出相位相差90°的两路信号sinθ和cosθ,判向电路根据这两号的相位关系,确定码盘的转动方向,然后按光栅付之间的转动方向对正弦信号的每个周期进行增或减计数,正转则加,反转则减,于是便可获得相对某一位置的计数值N。

若光栅节距角为:δ,那么相对该指定位置的角度粗码值θ就为:θ=N×δ。

假设增量式光电编码器输出两个互差90°的方波信号为A、B,每转一周每个信号输出N个脉冲。

A、B 信号的相位关系体现了光电编码器旋转方向。

当光电编码器顺时针旋转时,A超前B90°;逆时针旋转时,B 超前A90°。

辨向电路通过A、B的相位关系来判断旋转方向,并且据此决定当一个计数脉冲出现时应该对当前计数值加1还是减1。

图1中用D触发器实现辨向。

并用一个异或门从A、B信号产生计数脉冲,起到倍频作用。

图1 接口电路结构图光电编码器顺时针旋转时,信号A超前B90°,D 触发器(上升沿触发)输出Q(波形W1)为高电平,Q(波形W2)为低电平。

此时,counter计数器的加计数端up为1,于是在clk(A、B倍频后的结果)的作用下加一计数。

当光电编码器逆时针旋转时情况相反,信号B超前A90°,D触发器(上升沿触发)输出Q(波形W1)为低电平,Q(波形W2)为高电平。

此时,counter 计数器的加计数端dn为1,于是在clk的作用下减一计数。

这里counter为16位计数器,顺时针旋转计数范围0~65535,逆时针旋转时计数范围0(65535)~-65535。

编码器每转一周也会同时输出一个标记窄脉冲Z,Z用来同时重置计数器。

计数器工作时存在时间的延时,如果计数器还未准备好,处理器就来读取数据,读取的数据将是错误—12—的。

为了避免错误的发生,这里设计了一个数据锁存电路latch 。

锁存器的触发窄脉冲比计数脉冲W 3或W 4延时半个周期。

这样,当计数器未稳定时,其输出的数据不会通过锁存器。

另外,图1中buff 为微机读取数据所需的并行口缓存电路。

2 接口电路的FPG A 实现以上介绍的是整个接口电路的原理,其中辨向、倍频、计数、锁存、缓冲、延时等功能模块在一片FPG A 上实现,这里我们采用A ltera 公司Cycl one 系列的EP1C12Q240C8芯片。

2.1 接口芯片的功能及引脚介绍图2 接口芯片如图2,接口芯片有5个输入,16个输出,下面就每个端口的意义作一说明:A:编码器的A 相输入;B :编码器的B 相输入;Z:编码器的Z 相输入;SYS_CLK:接口的全局时钟;RD:处理器读信号;D0~D15:输出的16位计数值。

2.2 Veril og HDL 程序对于硬件描述语言主要有VHDL 和Veril og HDL 两种,其中Veril og HDL 类似C 语言,通俗易懂,所以我们采用了Veril og HDL 。

部分程序代码如下:module encoder_interface (a,b,z,sys_clk,rd,q ); input a,b,z,sys_clk,rd; out put [15:0]q; wire w0,w1,w2,w3,w4; wire [15:0]q0;//计数器输出 wire [15:0]q1;//锁存器输出 wire [15:0]q2;//缓冲器输出 xor (w0,a,b );//异或倍频 d_trigger (a,b,w1,w2);//d 触发器辨向 counter (w1,w2,z,w0,q0);//计数器实例化 latch (sys_clk,q0,q1);//锁存器 buff (rd,q1,q2);//缓冲器end module//33333333d 触发器模块module d_trigger (clk,d,qq,qqf ); input clk,d; out put qq,qqf; reg qq; al w ays @(posedge clk ) qq =d; not (qqf,qq );end module//33333333计数器模块module counter (up,dn,clr,clk,d ); input up,dn,clr,clk; out put [15:0]d; reg [15:0]d; al w ays @(posedge clk ) begin if (clr )d =0; else if (up ) d =d +1; if (dn ) d =d -1; endend module//33333333锁存模块module latch (clk,d0,qq1); input clk; input [15:0]d0; out put [15:0]qq1; delay (clk,e ); al w ays (posedge e ) qq1=d0; endmodule//3333333333缓冲模块module buff (rd,d1,qq2); input rd; input [15:0]d1; out put [15:0]qq2; al w ays (posedge rd ) begin—22— qq2=d1; endend module //延时模块module delay (clk,e ); input clk; out put e; reg [5:0]shift; assign e =shift[5]; al w ays@(posedge clk ) shift <={shift[4:0],data_in};end module3 仿真波形用Veril og HDL 语言完成电路描述之后,本文采用Quartus Ⅱ6.0工具对程序进行了功能和时序仿真。

仿真结果如图3:图3 时序图4 结束语本文设计了增量式光电编码器的一种简单且高精度的鉴相、计数和接口电路,可根据光电编码器的转向进行递增或递减计数,并可与微机或DSP 直接进行并行通讯。

实验结果验证了本设计的正确性。

需要指出的是,本电路上电后,只有在出现一次Z 脉冲之后检测结果才正确。

参考文献:[1] 方艳辉.增量式编码器全数字量相加技术的研究[C ].中国科学院研究生院硕士学位论文,2005.[2] 吴志刚.光电编码器的原理与应用[J ].浙江冶金,2001,(2).[3] 夏宇闻.复杂数字电路与系统的Veril og HDL 设计技术[M ].北京:北京航空航天大学出版社,1999.[4] 谈艳云.用Veril ogHDL 语言设计分频器和32位计数器[J ].微计算机应用,2002.收稿日期:2008-04-23作者简介:孙士尉(1979-),男,讲师,北京科技大学控制理论与控制工程专业在读硕士。

第五届亚洲风能大会暨国际风能设备展览会在京举行本届展会的展览面积超过了25000平米,比2007年的第四届增长近40%。

凭借25000平米的展览面积和权威会议,本届展会已与欧洲、美国风电展并列世界最大风能专业展会。

代表了全球风电产业的最高水平的GE 、ALST OM 、Nordex 、ABB 、W inergy 、Moeller 、华锐、东汽、中石油、中石化等,270家参展企业中,67%来自海外,增长超过50%;专业观众数量超过18000人次;举办了20多个专业论坛。

本次大会既依托于国家发改委、中国电力企业联合会等政府主管部门的大力支持及丹麦风能集团等国际组织的积极配合。

体现出全球风电产业对中国市场的重视。

MOE LLER 展台是标志性的环保绿色,展示了我们优势的风能相关产品:2000A 接触器D I L H2000,D I L M 系列接触器,框架开关I Z M123,各种塑壳开关NZ M 系列,自动控制产品,先进的DAR W I N 系统产品。

吸引了大批专业人士前来参观交流,了解MOELLER 产品,了解了MOELLER 有关风能和其他电气控制的解决方案。

随着传统能源日益枯竭和价格不断攀升,风电成为目前最具规模化开发条件和商业化发展前景的发电方式。

Moeller 作为一直参加风能的参展商再一次透过亚洲风能大会暨国际风能设备展览会展示最新的技术、产品和服务。

穆勒在低压电气领域中或许还未做到最好,但是相信在风能这片领域下,穆勒能够尝试做到最好,做到更好。

—32—。