MOSFET-2-清华大学半导体物理

有关半导体的参考文献

有关半导体的参考文献参考文献:1. 陶铸, 朱建新. 半导体物理学[M]. 清华大学出版社, 2017.2. 张宇. 半导体器件物理与模拟[M]. 电子工业出版社, 2018.3. 石磊, 朱建新. 半导体器件物理与工艺[M]. 机械工业出版社, 2019.4. 朱建新. 半导体物理与器件[M]. 清华大学出版社, 2020.半导体材料是一类具有特殊电学性质的材料,广泛应用于电子器件和集成电路中。

随着科技的不断进步,半导体物理学和器件工艺也得以迅速发展。

本文将对半导体物理学和器件工艺的一些重要内容进行介绍。

半导体物理学是研究半导体材料的电学性质和输运特性的学科。

《半导体物理学》一书详细介绍了半导体材料的基本性质、能带理论、载流子输运、PN结和二极管、MOS结和MOS场效应晶体管等内容。

通过学习半导体物理学,可以了解半导体材料的结构、能带结构以及载流子的产生、输运和复合过程,为后续学习半导体器件物理和工艺奠定基础。

半导体器件物理与模拟是研究半导体器件的电学特性和模拟方法的学科。

《半导体器件物理与模拟》一书详细介绍了半导体器件的物理效应、载流子输运、PN结和二极管、MOS场效应晶体管、BJT等内容。

通过学习半导体器件物理与模拟,可以了解各种半导体器件的工作原理、特性和模拟方法,为后续设计和优化半导体器件提供理论指导。

半导体器件物理与工艺是研究半导体器件制备工艺和性能改善方法的学科。

《半导体器件物理与工艺》一书详细介绍了半导体器件的制备工艺、薄膜技术、光刻技术、离子注入和扩散技术等内容。

通过学习半导体器件物理与工艺,可以了解各种半导体器件的制备过程和性能改善方法,为实际的半导体器件制造提供技术支持。

半导体物理与器件是综合了半导体物理学和半导体器件物理与工艺的学科。

《半导体物理与器件》一书全面介绍了半导体物理和器件的基本原理和应用。

通过学习半导体物理与器件,可以深入了解半导体材料的物理性质、器件的工作原理和制备工艺,为实际的半导体器件设计和制造提供理论指导和技术支持。

半导体物理基础 第六章 MOS

QS QB qNa xd

2 qNa xd S 2k s 0

(6-5)

和

(6-6)

6.2 理想MOS电容器

代入(6-44)式解出 x

d

Xd

kS 0 kS 0 2VG 1 C0 2 C0 C0 qkS 0 N a

2 0 12

(6-45)

C 2C 1 qN k VG C0 a S 0

6.2 理想MOS电容器

积累区( VG <0)

MOS系统的电容C基本上等于绝缘体电容 C0。当负偏压的数值逐渐减少时,空间电 荷区积累的空穴数随之减少,并且 QS 随 C也就变小。 平带情况( VG =0)

S

的变化也逐渐减慢, C S 变小。总电容

C FB C0

1 k 0 LD 1 k s x0

(6-1)

掌握载流子积累、耗尽和反型和强反型的概念。 正确画出流子积累、耗尽和反型和强反型四种情况的能带图。 导出反型和强反型条件

6.2 理想MOS电容器

6.2 理想MOS电容器

系统单位面积的微分电容

微分电容C与外加偏压 VG 的关系称为MOS系统的电容—电压特性。

dQM C dVG

(6-1)

S =半导体表面的电场

k0 =氧化物的相对介电常数

k S =半导体相对介电常数

xd =空间电荷区在半导体内部的边界亦即空间电荷区宽度。

外加电压 VG 为跨越氧化层的电压

V0和表面势 S 所分摊:

(6-2)

VG V0 S

6.1 理想MOS结构的表面空S结构内的电位分布

(6-22)

dV0 d s 1 dVG C dQM dQM dQM

半导体物理与器件基础知识

9金属半导体与半导体异质结一、肖特基势垒二极管欧姆接触:通过金属-半导体的接触实现的连接。

接触电阻很低。

金属与半导体接触时,在未接触时,半导体的费米能级高于金属的费米能级,接触后,半导体的电子流向金属,使得金属的费米能级上升。

之间形成势垒为肖特基势垒。

在金属与半导体接触处,场强达到最大值,由于金属中场强为零,所以在金属——半导体结的金属区中存在表面负电荷。

影响肖特基势垒高度的非理想因素:肖特基效应的影响,即势垒的镜像力降低效应。

金属中的电子镜像到半导体中的空穴使得半导体的费米能级程下降曲线。

附图:电流——电压关系:金属半导体结中的电流运输机制不同于pn结的少数载流子的扩散运动决定电流,而是取决于多数载流子通过热电子发射跃迁过内建电势差形成。

附肖特基势垒二极管加反偏电压时的I-V曲线:反向电流随反偏电压增大而增大是由于势垒降低的影响。

肖特基势垒二极管与Pn结二极管的比较:1.反向饱和电流密度(同上),有效开启电压低于Pn结二极管的有效开启电压。

2.开关特性肖特基二极管更好。

应为肖特基二极管是一个多子导电器件,加正向偏压时不会产生扩散电容。

从正偏到反偏时也不存在像Pn结器件的少数载流子存储效应。

二、金属-半导体的欧姆接触附金属分别与N型p型半导体接触的能带示意图三、异质结:两种不同的半导体形成一个结小结:1.当在金属与半导体之间加一个正向电压时,半导体与金属之间的势垒高度降低,电子很容易从半导体流向金属,称为热电子发射。

2.肖特基二极管的反向饱和电流比pn结的大,因此达到相同电流时,肖特基二极管所需的反偏电压要低。

10双极型晶体管双极型晶体管有三个掺杂不同的扩散区和两个Pn结,两个结很近所以之间可以互相作用。

之所以成为双极型晶体管,是应为这种器件中包含电子和空穴两种极性不同的载流子运动。

一、工作原理附npn型和pnp型的结构图发射区掺杂浓度最高,集电区掺杂浓度最低附常规npn截面图造成实际结构复杂的原因是:1.各端点引线要做在表面上,为了降低半导体的电阻,必须要有重掺杂的N+型掩埋层。

华北电力 考研 北京 大纲 半导体物理

半导体物理课程编号:00500070课程名称:半导体物理英文名称:Semiconductor Physics总学时:48总学分:3适用对象: 电子科学与技术专业本科先修课程:量子力学、固体物理一、课程性质、目的和任务本课程是电子科学与技术专业的一门专业基础课。

通过本课程的教学,使学生掌握半导体物理的基本概念及基本理论和方法。

培养学生运用所学知识,分析实践中碰到的一些现象,提高解决实际问题的能力。

也为进一步学习后续的半导体器件等课程打好基础。

二、教学要求和内容基本要求:了解半导体材料的基本性质,掌握半导体物理的基本理论和方法。

并学会运用这些基本理论和方法,分析解决在半导体的研究和生产实践中遇到的各种问题。

基本内容:1.The Crystal Structure of Solids2.Introduction to Quantum Mechanics3.Introduction to the Quantum Theory(难点)4.The Semiconductor in Equilibrium(重点、难点)5.Carrier Transport Phenomena(重点、难点)7.The pn Junction(重点)8.Fundamentals of the Metal-Oxide-Semiconductor Field-Effect Transistor(重点、难点)三、教学安排及方式以课堂讲授为主,辅助于课堂讨论。

五、推荐教材和教学参考书教材:《Semiconductor Physics and Devices》,Donald A. Neamen编著,McGraw-Hill出版社,2003年版。

参考书:《半导体物理学》,刘恩科等编著,电子工业出版社出版社,2003年版。

《半导体物理学》,顾祖毅等编著,清华大学微电子研究所出版,1994年版。

六、补充说明大纲执笔者:李守荣大纲校对者:郝建红大纲审核者:制定日期:2006-8-18。

C-V特性-MOS管原理半导体物理与器件

2019/12/7

相当于金属电容与半导体电容串联 电阻越串越大,电容越串越小

1.2 C-V特性

电容-电压特性测试曲线

理想MOS电容C-V特性

测量电源:MOS外加栅压,在直流电压上叠加一交流小信号电压。

直流电压:决定器件工作点,调整大小使MOS先后处于堆积、平带、 耗尽、本征、反型几种状态

2019/12/7

禁带中央:CV曲线实虚线重和

2019/12/7

1.2 C-V特性

例图:需要额外牺牲三个负电荷 来中和界面态的正电

界面陷阱的影响:本征前

+++ ------

---

201199//1122/7/7

本征态

本征之前:EFi>EF,总有施主态在EFS之 上,施主态失去电子界面陷阱带正电。 正施主态数量是栅压的函数。 C-V曲线左移,左移量随栅压不等

黑(灰)色部分可以 理解为两种材料界面 或空间电荷区,一般 书中不画。

1.3MOSFET原理

MOSFET结构

绝缘栅场效应晶体管(Insulated Gate, IGFET): 栅极与其它电极之间是相互绝缘的。

例图:因为Qss均为正电荷, 需要额外牺牲负电荷来中和 界面的正电

++ -----

C'FB

tox

ox ox kT

tox e

s

eN a

2019/12/7

Qss ' VFB C V曲线左移,反之右移

1.2 C-V特性

界面陷阱的分类

被电子占据(在EFS之下)带负电,不被电子占据(在EFS之上)为中 性

CV特性概念和CV特性测试原理 MOS电容在不同半导体表面状态下的特点和公式 频率特性 高低频情况图形及解释 思考:若直流电压变化快,CV曲线如何?

半导体物理学第八章知识点

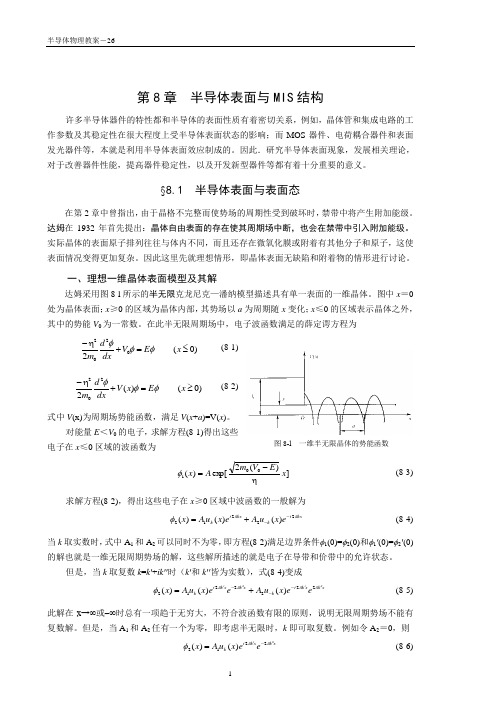

第8章 半导体表面与MIS 结构许多半导体器件的特性都和半导体的表面性质有着密切关系,例如,晶体管和集成电路的工作参数及其稳定性在很大程度上受半导体表面状态的影响;而MOS 器件、电荷耦合器件和表面发光器件等,本就是利用半导体表面效应制成的。

因此.研究半导体表面现象,发展相关理论,对于改善器件性能,提高器件稳定性,以及开发新型器件等都有着十分重要的意义。

§8.1 半导体表面与表面态在第2章中曾指出,由于晶格不完整而使势场的周期性受到破坏时,禁带中将产生附加能级。

达姆在1932年首先提出:晶体自由表面的存在使其周期场中断,也会在禁带中引入附加能级。

实际晶体的表面原子排列往往与体内不同,而且还存在微氧化膜或附着有其他分子和原子,这使表面情况变得更加复杂。

因此这里先就理想情形,即晶体表面无缺陷和附着物的情形进行讨论。

一、理想一维晶体表面模型及其解达姆采用图8-l 所示的半无限克龙尼克—潘纳模型描述具有单一表面的一维晶体。

图中x =0处为晶体表面;x ≥0的区域为晶体内部,其势场以a 为周期随x 变化;x ≤0的区域表示晶体之外,其中的势能V 0为一常数。

在此半无限周期场中,电子波函数满足的薛定谔方程为)0(20202≤=+-x E V dx d m φφφη (8-1))0()(2202≥=+-x E x V dx d m φφφη (8-2)式中V (x)为周期场势能函数,满足V (x +a )=V(x )。

对能量E <V 0的电子,求解方程(8-1)得出这些电子在x ≤0区域的波函数为 ])(2ex p[)(001x E V m A x η-=φ (8-3) 求解方程(8-2),得出这些电子在x ≥0区域中波函数的一般解为kx i k kx i k e x u A e x u A x ππφ22212)()()(--+= (8-4)当k 取实数时,式中A 1和A 2可以同时不为零,即方程(8-2)满足边界条件φ1(0)=φ2(0)和φ1'(0)=φ2'(0)的解也就是一维无限周期势场的解,这些解所描述的就是电子在导带和价带中的允许状态。

半导体物理-绪论

英国曼彻斯特大学物 理学家 安德烈·980-2000年的全球国民生产总值(WGP)及电子、汽车、半导体和钢铁工业的销售量,并外插此曲线到2010年止

太阳能电池、LED, 半导体制冷、IC设

计

从上图中可以得知: 电子工业和半导体工业已经超过传统的钢铁工业、汽车工业,成为

21世纪的高附加值、高科技的产业。电子工业的高速发展依赖于半导体 工业的快速提高,而在半导体工业中其核心是集成电路(电集成、光集 成、光电集成),集成电路在性能、集成度、速度等方面的快速发展是 以半导体物理、半导体器件、微电子工艺的发展为基础的。

半导体物理-绪论

课程介绍

联想???

定 位

半导体物理

近年诺贝尔物理学奖

法国科学家阿尔贝·费尔 (2007年) 德国科学家彼得·格林贝格尔

巨磁电阻效应,是指磁性材料的电阻率在有外磁场作用时 较之无外磁场作用时存在巨大变化的现象。根据这一效应 开发的小型大容量计算机硬盘已得到广泛应用。

高锟、威拉德·博伊尔和乔治·史密斯 (2009年)

“研究二维材料石墨烯的开创性实验”而共享。2004年制 成的石墨烯已迅速成为物理学和材料学的热门话题,现在 是世界上最薄的材料,仅有一个原子厚。在改良后,石墨 烯致力于塑造低功率电子元件,如晶体管。相比之下,铜 线和半导体都会产生电脑芯片75%的能量消耗,人们确定 了石墨烯拥有取代硅留名史册的本事。

《科学》:2009年十大科学突破 石墨烯微观结构:六角型呈蜂巢晶格的平面薄膜

高二物理竞赛课件MOSFET的小信号等效模型

MOSFET的小信号等效模型

2023/7/20

2

一、跨导gm

线性区

gm

iD vGS

|Q

nCox

W L

VDS

2023/7/20

3

一、跨导gm

亚阈值区

实际上,对MOS管,在vGS<VGS(th)时, 就已有漏极电流iD。这种现象称为亚阈区导电效应。

iD

ID0

W L

exp(vGS -VTH nVT

|Q

1 2

n (VGS

VGS(th) )2

rds

1 VDS I D

11

rds I D

(VDS 1)

考虑基区宽 度调制效应

线性区

当vDS较小时,可等效为电阻。

2023/7/20

5

三、背栅跨导gmb

iD

g mb

vGS 常数,vDS 常数

vBS

gmb ( -1) gm

(η=1. 1~)

2023/7/20

11

– MOSFET利用栅源电压改变表面感生电荷,

控制漏极电流。

返回

2023/7/20

7

作业 P52:

例题

2023/7/20

8

随堂小测试(5min)

1. 画出JFET的低频小信号模型?等效参数? 2. MOS管小信号等效电路? 写上学号。

2023/7/20

9

)1-

exp(

vDS VT

)

(式) P42

式中:ID0称为特征电流。 n是与衬底调制有关的因子。约为 ~3 。

亚阈区的跨导

gmsub:

g msub

ID nVT

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电场对迁移率的影响在前面的长沟道模型中,假设载流子迁移率是常数。

实际上,V GS 和V DS 分别在沟道中产生纵向电场和沿沟道方向的水平电场,都会对载流子的迁移率产生影响。

低场迁移率(弱场近似)水平电场较小时,载流子迁移率和水平位置无关,称作低场迁移率,。

(体材料)•分析弱场下纵向电场对低场迁移率的影响;•分析水平强电场对迁移率的影响•弱场下纵向电场对低场迁移率的影响前提:载流子速度小于饱和速度(纵向弱场)和体材料中的电子比较:沟道中的电子不仅受到晶格振动、杂质等散射,另外还受到沟道“壁”的散射—导致载流子的平均自由时间减小,迁移率下降。

沟道“壁”的含义:势垒由界面势垒和Si导带势垒构成。

对沟道中的大部分电子,势阱很的散射使得沟道中载。

热运动速度三个方向的平均自由程是相等的。

X方向受到额外的散射对平均自由时间的影响例:假设纵向电场为105V/cm。

电子在一个平均自由程内损失全部动量:由沟道“壁”散射决定的平均自由时间为:X方向最大动能为:因此,最大的平均自由时间为:沟道“壁”散射决定的平均自由时间约为体材料的1/6。

纵向电场对迁移率的影响:•能量相同的载流子在不同纵向电场下平均自由时间不同,电场越大,平均自由时间越短。

(势阱宽度不同)•载流子在YZ平面内的平均自由时间和体材料相同•不同纵向电场下,电子迁移率不同。

电场越强,迁移率越低。

决定沟道纵向电场的因素(电荷):掺杂浓度、偏置、沟道深度根据实验结果得到的低场迁移率:纵向电场对I-V特性的影响:恒定迁移率:考虑纵向电场影响:忽略沟道电压变化的影响:其中:恒定迁移率和考虑纵向电场后的比较沟道中水平电场对迁移率的影响速度饱和效应—弱场下,载流子的漂移速度随电场增大而增大;电场增大到一定值,漂移速度达到饱和。

原因:随电场增大,散射机制的变化。

沟道中载流子漂移速度的经验公式:例:根据公式7.64:得:对于现代集成电路技术,速度饱和效应尤其显著。

取沟道长度为0.18,漏极电流的变化:m μ非饱和区的I-V特性:对比:速度饱和对I-V特性的影响:•利用沟道宽长比调整I-V 特性;•饱和漏电压的变化:减小。

NFET减小更多。

•沟道宽长比不变的情况下,饱和漏极电流随沟道长度减小如何变化?速度饱和效应的物理本质:问题1:真的是沟道夹断需要的漏电压变小了吗?问题2:漏极电流饱和时,沟道夹断了吗?问题3:速度饱和首先在靠近源端还是漏端出现?问题4:当沟道夹断时,饱和电流是由什么机制决定的?E速度饱和效应是现代集成电路的器件设计和研究中必须考虑的因素!模型和实验结果的对比NFET参数:电源电压:1.8V阈值电压和低场迁移率的测量实际工作中,MOSFET的阈值电压是通过测量而不是计算得到的。

如何从实验数据得到阈值电压?非饱和区漏极电流:,whereV DS很小时,可以忽略速度饱和效应:栅源电压不太大时,漏极电流近似为:对转移特性曲线:斜率为:跨导令:得到截距为:MOSFET 的一级近似认为:只有V GS >V T 时,才能有漏极电流流过MOSFET V GS < V T 时的漏极小电流称为亚阈值电流。

这种近似对大多数实际情况是适用的。

但是在某些应用中,非常小的电流也是不能忽略的(关态电流)。

亚阈值电流(扩散电流为主):萨方程不适用于亚阈值区的原因: 强反型近似中的关于耗尽层的假定不适用 该假定认为:V GS ≤V T 时,Q n =0。

实际上,Q n 随表面势指数变化。

当栅电压低于阈值电压时,Q n 指数下降,漏极电流也是如此。

强反型时,由于|Q n |数值很大,计算|Q n |时可忽略V GS =V T 时已经出现了的表面电子电荷。

只考虑了漂移电流,未考虑扩散电流 在亚阈值区,扩散电流>>漂移电流。

亚阈值区导电与BJT 中基区的电流传输相似。

下图为ψF<V S< 2ψF时的能带图此时半导体表面弱反型,相当于低掺杂的n型区。

沿沟道方向是n+/n-/n+结构,电流中扩散电流成分远大于漂移电流。

亚阈值电流的形成在亚阈值区,漏极电压几乎全部降落在反向偏置的漏衬结耗尽区上,因此,漏极电流的漂移流部分可以忽略。

另一方面,自由载流子浓度沿沟道方向的梯度相当大,因此,亚阈值电流的主要成分是扩散流,类似于基区均匀掺杂的BJT的基区电流。

栅极电压V G使半导体表面能带弯曲,降低了从源区到沟道区的电子势垒,电子从重掺杂的源区(类似BJT的发射区)注入到p型表面区(类似BJT的基区),大部分注入的电子被漏区收集(类似BJT的集电区)。

•亚阈值区漏极电流随栅压指数变化亚阈值电流为:亚阈值电流分析表征电容分压作用:栅压变化对沟道电压的影响半对数坐标转移特性曲线对于电容分压,可以忽略亚阈值区沟道中的载流子。

电压关系:亚阈值电流栅压摆幅S(亚阈值)定义:电流变化十倍(一个数量级),栅压变化的幅度将亚阈值电流公式代入,得:•利用S可以很方便地看出MOSFET从弱反型过渡到强反型时,电流变化跨越多少个数量级。

•结合栅压摆幅和关态漏电流要求可以作为设计阈电)。

压的依据,进而确定电源电压(5VT影响栅压摆幅的因素:氧化层厚度;衬底掺杂浓度界面陷阱密度MOSFET小尺寸效应—短(窄)沟道效应1、有效沟道长度和漏电压的关系•沟道长度调制效应:时,夹断点向源端移动,导致有效沟道长度减小,输出特性不饱和。

•短沟效应:即使,沟道未发生夹断,有效沟道长度也会随漏电压增大而减小。

有效沟道长度小于源、漏两个冶金结界面之间的距离。

考虑短沟效应后的输出特性饱和前漏极电流大于饱和电流•如果外加漏电压,漏衬结空间电荷区主要向沟道方向扩展,有效沟道长度减小;漏极电流和有效沟道长度成反比,随漏电压增大而增大。

•上述分析对长沟器件中也成立,只是对长沟器件影响很小。

2、阈电压和漏电压的关系—漏场感应势垒下降效应(DIBL)•长沟器件中,漏电压对源端势垒没有影响•短沟器件,漏电压导致源端势垒降低:1)沟道缩短,漏、源耗尽区的相互影响2)V DS增加,漏区发出的电力线的一部分穿透到源区研究方法:二维数值模拟•相同沟道长度下,有效阈电压随漏电压增大而减小;•相同漏电压条件下,有效阈电压随沟道长度减小而减小。

DIBL 效应对MOSFET 特性的影响:V DS 增加导致势垒降低,表面更加反型(沟道更加吸引电子),沟道导电能力增强,等效于有效阈电压的下降。

3、漏源电荷共享效应数值以下时,有效阈电压会随沟道长度的减小而下降。

电荷共享原理:•长沟器件,绝大多数栅极正电荷发出的电力线都终止在反型层的电子和耗尽区内的电离受主;•短沟器件:耗尽区的电离受主有一部分是用来终止源漏的电离施主发出的电力线。

当沟道长度与源漏耗尽区宽度相比拟时,表面耗尽区和源漏耗尽区交界的电离受主只有一部分用来终止栅极正电荷的电力线,因此,栅极正电荷将在反型层感应出更多的电子,表面能带弯曲更多。

导致:1)在相同的栅压下漏极电流变大;2)和长沟器件相比,较低的栅压就可以使半导体表面达到强反型,有效阈电压降低。

交界区的电离受主电荷一部分属于表面耗尽区,一部分属于源漏耗尽区,称为源漏电荷共享。

电荷共享效应随沟道长度减小而增强,有效阈电压也随之减小。

COMPLEMENTARY MOSFETs -CMOSN阱CMOS反相器CMOS :集成电路中利用NFET 和PFET 构成电路的一种基本单元。

降低直流(静态)功耗•N 阱(P 型衬底)•PFET 做在N 阱内•共输出、输入•衬底和阱形成pn结,总处于反偏。

•输入电压为0时:NFET不导通,PFET导通。

输出电压为V DD,为高电平。

•输入电压为V DD时:NFET 导通,PFET不导通。

输出电压为0 ,为低电平。

直流通路。

负载电容对开关特性的影响:负载电容的来源:引线电容、输出电容等。

是产生动态功耗的主要因素。

分析开关过程对负载电容输出从低到高:对负载电容充电;输出从高到低:负载电容放电。

充放电经过的回路不同。

开关一次,完成一次从电源到地的能量传输:动态功耗等于:现代数字集成电路工作频率很高,因此,动态功耗很大。

减小动态功耗:•降低工作电压:受阈电压摆幅的限制•减小负载电容传输延时(栅延时)定义:输出信号变化为V DD 的50%需要的时间。

包括:上升延时和下降延时。

(负载电容充放电)考虑输出信号从V DD 变到V DD /2,负载电容上电荷变化:传输延时:CMOS 反相器输入高电平后NFET 电流的变化:栅极从低电平切换成高电平,NFET 漏电压为V DD 。

如果饱和漏电压小于V DD /2,在t df 时间内漏极电流不变,得t df 为:同理:传输延时为:MOSFET的小信号等效电路MOSFET的寄生参数R S,R D:串联电阻;R BS,R BD:源漏和衬底之间的电阻;C OS,C OD:交叠电容;C GD,C GS:栅-源、栅-漏电容;C jS,C jD:源、漏和衬底的势垒电容。

小信号等效电路跨导:输出电导:由基本的MOSFET结构图得到小信号等效电路。

本征MOSFET 加上寄生参数。

dsd gs m d v g v g i +=漏极电流(低频):高频低频和的表达式:考虑速度饱和效应的直流特性:跨导:饱和区的跨导?跨导的含义:单位栅压变化导致漏极电流的变化量。

反映栅压对漏极电流的控制能力。

考虑速度饱和效应后,沟道长度对跨导的影响?和理想情况相比Parameter from Table 7.1考虑速度饱和效应后,跨导仍然和沟道长度有关。

沟道越短,跨导越大,栅压对漏极电流的控制越强。

的放大作用和截止频率:高频时,等效电路如图:输入阻抗不再是无穷大,输入回路存在给电容充放电的电流。

输出回路交流短路时,栅极电流:短路输出电流:截止频率:电流增益等于1时的频率(交流输出短路)。

截止频率:用于信号放大时,MOSFET工作在饱和区,代入饱和区跨导:只考虑速度饱和时截止频率和沟道长度的关系:沟道越短,截止频率越高。

MOSFET SCALINGScaling down (按比例缩小):高速、高集成度、低功耗、低成本。

Dennard在1974 年提出了Scaling down,其指导思想是在MOS 器件内部电场不变的条件下,通过缩小器件的纵向和横向尺寸,同时按同样比例缩小电源电压,由此可大大提高器件的性能。

这种缩小规律以保持器件内部电场强度不变为条件,称为CE(恒场)律。

与原尺寸的器件相比,由于器件内部的电场保持不变,因而不会出现迁移率降低、碰撞电离、热载流子效应等强场效应。

之后还提出了CV(恒压)律,但CV律对电路性能的提高不及CE律,所以CE律应用最为广泛最小沟道长度L min (短沟效应不严重影响器件性能):Given by Brews. et al:例:设计沟道长度为0.2 的MOSFET ,尽量减小短沟效应。