七段数码管显示器

八位七段数码管动态显示电路设计

八位七段数码管动态显示电路的设计一七段显示器介绍七段显示器,在许多产品或场合上经常可见。

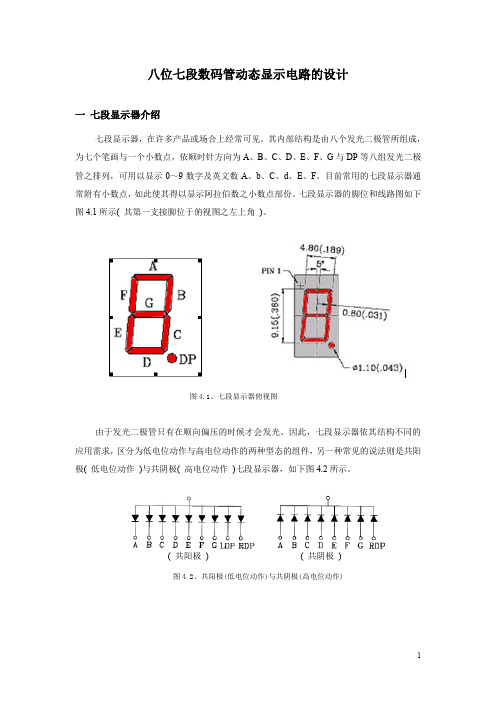

其内部结构是由八个发光二极管所组成,为七个笔画与一个小数点,依顺时针方向为A、B、C、D、E、F、G与DP等八组发光二极管之排列,可用以显示0~9数字及英文数A、b、C、d、E、F。

目前常用的七段显示器通常附有小数点,如此使其得以显示阿拉伯数之小数点部份。

七段显示器的脚位和线路图如下图4.1所示( 其第一支接脚位于俯视图之左上角)。

图4.1、七段显示器俯视图由于发光二极管只有在顺向偏压的时候才会发光。

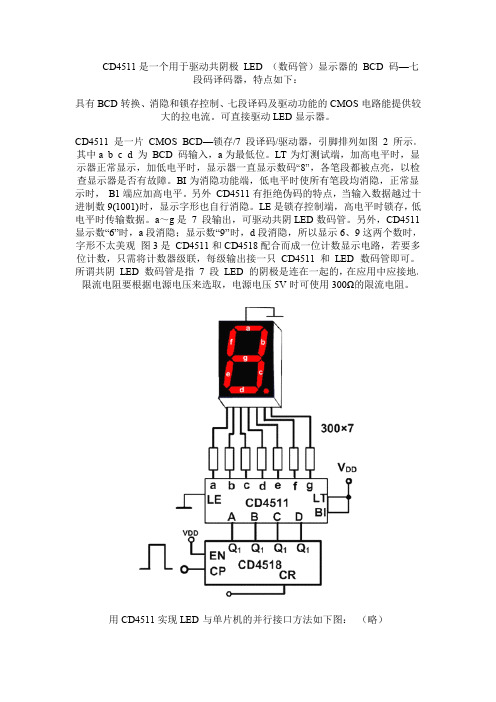

因此,七段显示器依其结构不同的应用需求,区分为低电位动作与高电位动作的两种型态的组件,另一种常见的说法则是共阳极( 低电位动作)与共阴极( 高电位动作)七段显示器,如下图4.2所示。

( 共阳极) ( 共阴极)图4.2、共阳极(低电位动作)与共阴极(高电位动作)要如何使七段显示器发光呢?对于共阴极规格的七段显示器来说,必须使用“ Sink Current ”方式,亦即是共同接脚COM为VCC,并由Cyclone II FPGA使接脚成为高电位,进而使外部电源将流经七段显示器,再流入Cyclone II FPGA的一种方式本实验平台之七段显示器模块接线图如下图4.5所示。

此平台配置了八组共阳极之七段显示器,亦即是每一组七段显示器之COM接脚,均接连至VCC电源。

而每一段发光二极管,其脚位亦均与Cyclone II FPGA接连。

四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。

八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。

图4.5、七段显示器模块接线图七段显示器之常见应用如下➢可作为与数值显示相关之设计。

⏹电子时钟应用显示⏹倒数定时器⏹秒表⏹计数器、定时器⏹算数运算之数值显示器二七段显示器显示原理七段显示器可用来显示单一的十进制或十六进制的数字,它是由八个发光二极管所构成的( 每一个二极管依位置不同而赋予不同的名称,请参见图4.1 ) 。

(完整word版)八位七段数码管动态显示电路设计

八位七段数码管动态显示电路的设计一七段显示器介绍七段显示器,在许多产品或场合上经常可见。

其内部结构是由八个发光二极管所组成,为七个笔画与一个小数点,依顺时针方向为A、B、C、D、E、F、G与DP等八组发光二极管之排列,可用以显示0~9数字及英文数A、b、C、d、E、F。

目前常用的七段显示器通常附有小数点,如此使其得以显示阿拉伯数之小数点部份。

七段显示器的脚位和线路图如下图4.1所示( 其第一支接脚位于俯视图之左上角)。

图4.1、七段显示器俯视图由于发光二极管只有在顺向偏压的时候才会发光。

因此,七段显示器依其结构不同的应用需求,区分为低电位动作与高电位动作的两种型态的组件,另一种常见的说法则是共阳极( 低电位动作)与共阴极( 高电位动作)七段显示器,如下图4.2所示。

( 共阳极) ( 共阴极)图4.2、共阳极(低电位动作)与共阴极(高电位动作)要如何使七段显示器发光呢?对于共阴极规格的七段显示器来说,必须使用“ Sink Current ”方式,亦即是共同接脚COM为VCC,并由Cyclone II FPGA使接脚成为高电位,进而使外部电源将流经七段显示器,再流入Cyclone II FPGA的一种方式本实验平台之七段显示器模块接线图如下图4.5所示。

此平台配置了八组共阳极之七段显示器,亦即是每一组七段显示器之COM接脚,均接连至VCC电源。

而每一段发光二极管,其脚位亦均与Cyclone II FPGA接连。

四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。

八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。

图4.5、七段显示器模块接线图七段显示器之常见应用如下可作为与数值显示相关之设计。

⏹电子时钟应用显示⏹倒数定时器⏹秒表⏹计数器、定时器⏹算数运算之数值显示器二七段显示器显示原理七段显示器可用来显示单一的十进制或十六进制的数字,它是由八个发光二极管所构成的( 每一个二极管依位置不同而赋予不同的名称,请参见图4.1 ) 。

CD4511(BCD码七段码译码器)

表 3-2 CD 4511 的真值表

8421 BCD 码对应的显示见下图

:

选用共阴极数码管,对于 CD4511 ,它与数码管的基本连接方式如下图 :

J=

=(C+B)D+BI

如不考虑消隐 BI 项,便得 J=(B+C)D 据上式,当输入 BCD 代码从 1010---1111 时,J 端都为“1”电平,从而使显示器中

的字形消隐。

输出 输入 LE BI LI D C B A a b c d e f g 显示 X X 0 XXXX1111111 8 X 0 1 X X XX 0 0 0 0 0 0 0 消隐 0 1 1 0 0 0 0 1111110 0 0 1 1 0 0 0 1 0110000 1 0 1 1 0 0 1 0 1101101 2 0 1 1 0 0 1 1 1111001 3 0 1 1 0 1 0 0 0110011 4 0 1 1 0 1 0 1 1011011 5 0 1 1 0 1 1 0 0011111 6 0 1 1 0 1 1 1 1110000 7 0 1 1 1 0 0 0 1111111 8 0 1 1 1 0 0 1 1110011 9 0 1 1 1 0 1 0 0 0 0 0 0 0 0 消隐 0 1 1 1 0 1 1 0 0 0 0 0 0 0 消隐 0 1 1 1 1 0 0 0 0 0 0 0 0 0 消隐 0 1 1 1 1 0 1 0 0 0 0 0 0 0 消隐 0 1 1 1 1 1 0 0 0 0 0 0 0 0 消隐 0 1 1 1 1 1 1 0 0 0 0 0 0 消隐 1 1 1 X X XX 锁 存 锁存

a、b、c、d、e、f、g:为译码输出端,输出为高电平 1 有效。 CD4511 的内部有上拉电阻,在输入端与数码管笔段端接上限流电阻就可

七段数码管显示

七段数码管显示设计报告目录一、设计任务二、题目分析与整体构思三、硬件电路设计四、程序设计五、心得体会一.设计任务数码的显示方式一般有三种:第一种是字型重叠式;第二种是分段式;第三种是点阵式。

目前以分段式应用最为普遍,主要器件是七段发光二极管(LED)显示器。

它可分为两种,一是共阳极显示器(发光二极管的阳极都接在一个公共点上),另一是共阴极显示器(发光二极管的阳极都接在一个公共点上,使用时公共点接地)。

数码管动态扫描显示,是将所用数码管的相同段(a~g 和p)并联在一起,通过选位通信号分时控制各个数码管的公共端,循环依次点亮各个数码管。

当切换速度足够快时,由于人眼的“视觉暂留”现象,视觉效果将是数码管同时显示。

根据七段数码管的显示原理,设计一个带复位的七段数码管循环扫描程序,本程序需要着重实现两部分:1. 显示数据的设置:程序设定4 位数码管从左至右分别显示1、2、3、4;2. 动态扫描:实现动态扫描时序。

利用EXCD-1 开发板实现七段数码管的显示设计,使用EXCD-1 开发板的数码管为四位共阴极数码管,每一位的共阴极7 段数码管由7 个发光LED 组成,7 个发光LED 的阴极连接在一起,阳极分别连接至FPGA相应引脚。

四位数码管与FPGA 之间通过8 位拨码开关(JP1)进行连接。

二.题目分析与整体构思使用EXCD-1 开发板的数码管为四位共阴极数码管,每一位的共阴极7 段数码管由7个发光LED 组成,呈“”字状,7 个发光LED 的阴极连接在一起,阳极分别连接至FPGA 相应引脚。

SEG_SEL1、SEG_SEL2、SEG_SEL3 和SEG_SEL4 为四位7 段数码管的位选择端。

当其值为“1”时,相应的7 段数码管被选通。

当输入到7 段数码管SEG_A~ SEG_G 和SEG_DP 管脚的数据为高电平时,该管脚对应的段变亮,当输入到7 段数码管SEG_A~SEG_G 和SEG_DP 管脚的数据为低电平时,该管脚对应的段变灭。

七段显示译码器7448功能,引脚图及应用电路

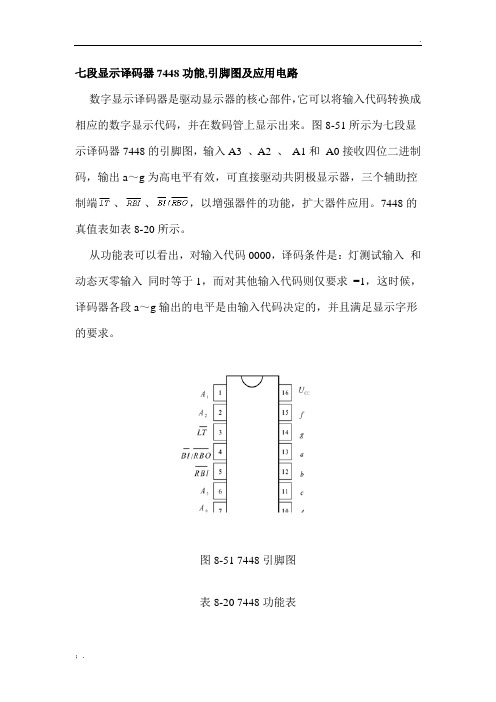

七段显示译码器7448功能,引脚图及应用电路数字显示译码器是驱动显示器的核心部件,它可以将输入代码转换成相应的数字显示代码,并在数码管上显示出来。

图8-51所示为七段显示译码器7448的引脚图,输入A3 、A2 、A1和A0接收四位二进制码,输出a~g为高电平有效,可直接驱动共阴极显示器,三个辅助控制端、、,以增强器件的功能,扩大器件应用。

7448的真值表如表8-20所示。

从功能表可以看出,对输入代码0000,译码条件是:灯测试输入和动态灭零输入同时等于1,而对其他输入代码则仅要求=1,这时候,译码器各段a~g输出的电平是由输入代码决定的,并且满足显示字形的要求。

图8-51 7448引脚图表8-20 7448功能表灯测试输入低电平有效。

当 = 0时,无论其他输入端是什么状态,所有输出a~g均为1,显示字形8。

该输入端常用于检查7448本身及显示器的好坏。

动态灭零输入低电平有效。

当=1,,且输入代码时,输出a~g均为低电平,即与0000码相应的字形0不显示,故称“灭零”。

利用=1与= 0,可以实现某一位数码的“消隐”。

灭灯输入/动态灭零输出是特殊控制端,既可作输入,又可作输出。

当作输入使用,且= 0时,无论其他输入端是什么电平,所有输出a~g均为0,字形熄灭。

作为输出使用时,受和控制,只有当,,且输入代码时,,其他情况下。

该端主要用于显示多位数字时多个译码器之间的连接。

【例8-13】七段显示器构成两位数字译码显示电路如图8-52所示。

当输入8421BCD码时,试分析两个显示器分别显示的数码范围。

图8-52 两位数字译码显示电路解:图8-52所示的电路中,两片7448的均接高电平。

由于7448(1)的,所以,当它的输入代码为0000时,满足灭零条件,显示器(1)无字形显示。

7448(2)的,所以,当它的输入代码为0000时,仍能正常显示,显示器(2)显示0。

而对其他输入代码,由于,译码器都可以输出相应的电平驱动显示器。

fpga7位数码管

fpga7位数码管FPGA 7位数码管FPGA(Field Programmable Gate Array)是一种可编程逻辑设备,具有处理器和数字电路的能力。

FPGA可以实现各种功能,其中之一是用于控制数码管的显示。

本文将介绍如何使用FPGA来控制7位数码管。

一、背景介绍现代电子设备中广泛使用的七段数码管,由七段LED组成,可显示0到9的数字及一些字母。

每个段都有一个独立的引脚,通过控制这些引脚的开关状态,可以实现不同数字和字母的显示。

二、FPGA实现控制七段数码管在FPGA中,使用逻辑门和触发器来实现控制七段数码管的功能。

首先,需要将逻辑门和触发器进行配置和互连,以实现所需的逻辑功能。

然后,通过输入信号来控制逻辑门和触发器的状态,从而控制数码管的显示。

三、数码管显示控制方法为了实现对七段数码管的显示控制,可以采用静态显示和动态显示两种方法。

静态显示是指通过逐一控制每个数字的七段LED来显示所需的数字。

动态显示是指通过快速切换多个数码管的显示来实现多个数字的显示。

四、时序控制在FPGA中,时序控制非常重要。

时序控制指的是根据特定的时钟信号来确定每个操作的执行时间和顺序。

通过对时序进行合理的设置,可以确保数码管显示的准确性和稳定性。

五、代码实现使用Verilog HDL语言可以编写FPGA的代码,实现对七段数码管的控制。

以下是一个简单的示例代码:```verilogmodule SevenSegmentDisplay(input wire [6:0] segments,output wire [3:0] digits,output wire anode);reg [23:0] counter;reg [3:0] digit;reg an;always @(posedge clk) begincounter <= counter + 1;if (counter == 24'd500000) begincounter <= 0;digit <= digit + 1;if (digit == 4'd9)digit <= 0;endendalways @(posedge clk) begin an <= (counter <= 12'd5); endassign segments = {7'b111_1110, // 07'b011_0000, // 1// ...};assign anode = an;assign digits = 4'b0111 - digit; endmodule```上述代码中,使用了一个时钟信号和一个计数器,通过计数器的值来确定当前需要显示的数字,然后通过修改晶体管的状态来实现数字的显示。

实验报告 实验七 八段数码管显示实验

实验报告实验七八段数码管显示实验----b46086b6-6eaf-11ec-8071-7cb59b590d7d实验报告--实验七-八段数码管显示实验EDA实验报告七段或八段数码管显示实验1、实验目的1)了解数码管动态显示的原理。

2)了解如何通过总线控制数码管显示器2、实验要求:利用实验仪提供的显示电路,动态显示一行数据.提示:显示显示缓冲区的内容(例如,可以使用60H~65h作为缓冲区)。

修改显示缓冲区的内容时,可以显示修改后的内容(为键盘扫描和显示实验做准备)。

3、实验说明实验仪器提供了一个6位8段编码的LED显示电路。

学生可以控制显示,只要他们根据地址输出相应的数据。

显示器共有6位,以动态方式显示。

8位段码和6位码由两个74ls374芯片输出。

位代码由mc1413或uln2022反相驱动后,选择相应的显示位。

本实验仪中8位段码输出地址为0x004h,位码输出地址为0x002h。

此处x是由key/ledcs决定,参见地址译码。

在进行键盘和led实验时,需要将按键/LEDC连接到相应的地址解码。

以便使用相应的地址进行访问。

例如,如果钥匙/ledcs连接到CS0,则段代码地址为08004h,位代码地址为08002h。

七段数码管的字型代码表如下表:a-----f | | b | |------| g | e | c-----d。

h显示字体gfedcba段代码001111113FH100011006H210110115BH3100111114FH41100111066H51016DH61111017DH70000 1107H81111117FH911011116fha111011177hb11111007chc011100139hd10111105ehe111100179hf111000171h4.原理图和接线5、实验内容1)使用仪器和仪表开发平台模型本实验用到了wave6000软件平台,电脑一台,lab6000实验箱,示波器,若干连线,串行数据线。

7448简介及数码管简介

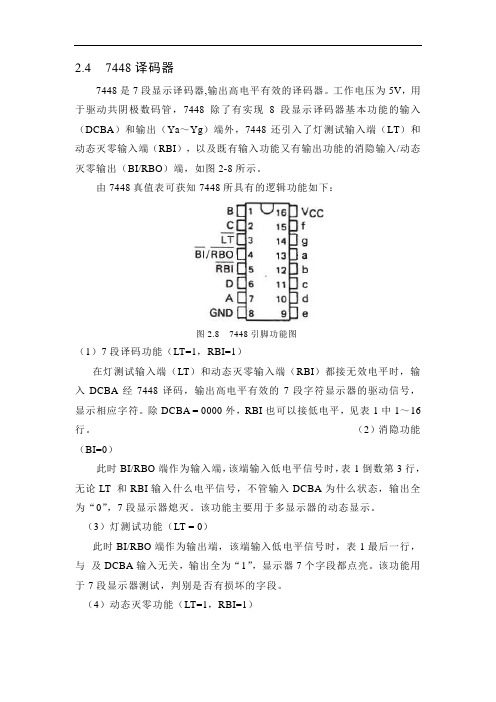

2.4 7448译码器7448是7段显示译码器,输出高电平有效的译码器。

工作电压为5V,用于驱动共阴极数码管,7448除了有实现8段显示译码器基本功能的输入(DCBA)和输出(Ya~Yg)端外,7448还引入了灯测试输入端(LT)和动态灭零输入端(RBI),以及既有输入功能又有输出功能的消隐输入/动态灭零输出(BI/RBO)端,如图2-8所示。

由7448真值表可获知7448所具有的逻辑功能如下:图2.8 7448引脚功能图(1)7段译码功能(LT=1,RBI=1)在灯测试输入端(LT)和动态灭零输入端(RBI)都接无效电平时,输入DCBA经7448译码,输出高电平有效的7段字符显示器的驱动信号,显示相应字符。

除DCBA = 0000外,RBI也可以接低电平,见表1中1~16行。

(2)消隐功能(BI=0)此时BI/RBO端作为输入端,该端输入低电平信号时,表1倒数第3行,无论LT 和RBI输入什么电平信号,不管输入DCBA为什么状态,输出全为“0”,7段显示器熄灭。

该功能主要用于多显示器的动态显示。

(3)灯测试功能(LT = 0)此时BI/RBO端作为输出端,该端输入低电平信号时,表1最后一行,与及DCBA输入无关,输出全为“1”,显示器7个字段都点亮。

该功能用于7段显示器测试,判别是否有损坏的字段。

(4)动态灭零功能(LT=1,RBI=1)此时BI/RBO端也作为输出端,LT 端输入高电平信号,RBI 端输入低电平信号,若时DCBA = 0000,表1倒数第2行,输出全为“0”,显示器熄灭,不显示这个零。

DCB A≠0,则对显示无影响。

该功能主要用于多个7段显示器同时显示时熄灭高位的零。

(5)7448/SN7448译码器0-9真值表如表2.2所示:表2.2 7448/SN7448译码器0-9真值表数码管是一种半导体发光器件,其基本单元是发光二极管。

2.5.1产品分类数码管按段数分为七段数码管和八段数码管,八段数码管比七段数码管多一个发光二极管单元(多一个小数点显示);按能显示多少个“8”可分为1位、2位、4位等等数码管。