8线-3线编码器

组合逻辑电路习题解答

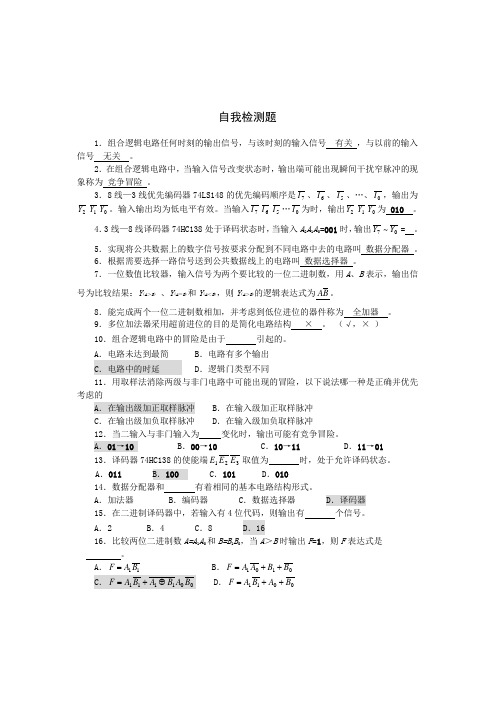

自我检测题1.组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 有关 ,与以前的输入信号 无关 。

2.在组合逻辑电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄脉冲的现象称为 竞争冒险 。

3.8线—3线优先编码器74LS148的优先编码顺序是7I 、6I 、5I 、…、0I ,输出为2Y 1Y 0Y 。

输入输出均为低电平有效。

当输入7I 6I 5I …0I 为时,输出2Y 1Y 0Y 为 010 。

4.3线—8线译码器74HC138处于译码状态时,当输入A 2A 1A 0=001时,输出07Y ~Y = 。

5.实现将公共数据上的数字信号按要求分配到不同电路中去的电路叫 数据分配器 。

6.根据需要选择一路信号送到公共数据线上的电路叫 数据选择器 。

7.一位数值比较器,输入信号为两个要比较的一位二进制数,用A 、B 表示,输出信号为比较结果:Y (A >B ) 、Y (A =B )和Y (A <B ),则Y (A >B )的逻辑表达式为B A 。

8.能完成两个一位二进制数相加,并考虑到低位进位的器件称为 全加器 。

9.多位加法器采用超前进位的目的是简化电路结构 × 。

(√,× ) 10.组合逻辑电路中的冒险是由于 引起的。

A .电路未达到最简 B .电路有多个输出C .电路中的时延D .逻辑门类型不同11.用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的A .在输出级加正取样脉冲B .在输入级加正取样脉冲C .在输出级加负取样脉冲D .在输入级加负取样脉冲12.当二输入与非门输入为 变化时,输出可能有竞争冒险。

A .01→10B .00→10C .10→11D .11→0113.译码器74HC138的使能端321E E E 取值为 时,处于允许译码状态。

A .011 B .100 C .101 D .01014.数据分配器和 有着相同的基本电路结构形式。

Verilog八线-三线优先编码器设计(74LS148)

Verilog⼋线-三线优先编码器设计(74LS148)if语句法1//8线-3线优先编码器设计(74LS148)2//3//EI | A7 A6 A5 A4 A3 A2 A1 A0 | Y2 Y1 Y0 GS EO4//0 | 0 x x x x x x x | 0 0 0 0 15//0 | 1 0 x x x x x x | 0 0 1 0 16//0 | 1 1 0 x x x x x | 0 1 0 0 17//0 | 1 1 1 0 x x x x | 0 1 1 0 18//0 | 1 1 1 1 0 x x x | 1 0 0 0 19//0 | 1 1 1 1 1 0 x x | 1 0 1 0 110//0 | 1 1 1 1 1 1 0 x | 1 1 0 0 111//0 | 1 1 1 1 1 1 1 0 | 1 1 1 0 112//0 | 1 1 1 1 1 1 1 1 | 1 1 1 1 013//1 | x x x x x x x x | 1 1 1 1 1141516module encoder_83 (din, EI, GS, EO, dout);17input [7:0] din; //编码输⼊端data_in,低电平有效18input EI; //使能输⼊端EI(选通输⼊端),EI为 0 时芯⽚⼯作,即允许编码19output [2:0] dout; //编码输出端data_out20output GS; //⽚优先编码输出端,优先编码器⼯作⼯作状态标志GS,低电平有效21output EO; //使能输出端EO(选通输出端)22reg [2:0] dout;23reg GS, EO;24always @(din or EI)25if(EI) begin dout <= 3'b111; GS <= 1; EO <= 1; end //所有输出端被锁存在⾼电平26else if (din[7] == 0) begin dout <= 3'b000; GS <= 0; EO <= 1; end27else if (din[6] == 0) begin dout <= 3'b001; GS <= 0; EO <= 1; end28else if (din[5] == 0) begin dout <= 3'b010; GS <= 0; EO <= 1; end29else if (din[4] == 0) begin dout <= 3'b011; GS <= 0; EO <= 1; end30else if (din[3] == 0) begin dout <= 3'b100; GS <= 0; EO <= 1; end31else if (din[2] == 0) begin dout <= 3'b101; GS <= 0; EO <= 1; end32else if (din[1] == 0) begin dout <= 3'b110; GS <= 0; EO <= 1; end33else if (din[0] == 0) begin dout <= 3'b111; GS <= 0; EO <= 1; end34else if (din == 8'b11111111) begin dout <= 3'b111; GS <= 1; EO <= 0; end//芯⽚⼯作,但⽆编码输⼊35else begin dout <= 3'b111; GS <= 1; EO <= 1; end //消除锁存器(latch)36endmodule3738//EI = 0 表⽰允许编码,否则所有输出端被封锁在⾼电平(控制芯⽚⼯作)39//EO = 0 表⽰电路⼯作,但⽆编码输⼊(⽤于级联)40//GS = 0 表⽰电路⼯作,且有编码输⼊(判断输⼊端是否有输⼊)testbench:1 `timescale 1 ps/ 1 ps2module encoder_83_vlg_tst();3reg EI;4reg [7:0] din;5wire EO;6wire GS;7wire [2:0] dout;8 encoder_83 i1 (.EI(EI), .EO(EO), .GS(GS), .din(din), .dout(dout));9initial10begin11 EI = 1;12 din = 8'b11111111;13 #10 EI = 0;14 #10 din = 8'b01010101;15 #10 din = 8'b10101010;16 #10 din = 8'b11010101;17 #10 din = 8'b11101010;18 #10 din = 8'b11110101;19 #10 din = 8'b11111010;20 #10 din = 8'b11111101;21 #10 din = 8'b11111110;22 #10 din = 8'b11111111;23end24endmoduleView Codecase语句法1//8线-3线优先编码器设计(74LS148)2//3//EI | A7 A6 A5 A4 A3 A2 A1 A0 | Y2 Y1 Y0 GS EO4//0 | 0 x x x x x x x | 0 0 0 0 15//0 | 1 0 x x x x x x | 0 0 1 0 16//0 | 1 1 0 x x x x x | 0 1 0 0 17//0 | 1 1 1 0 x x x x | 0 1 1 0 18//0 | 1 1 1 1 0 x x x | 1 0 0 0 19//0 | 1 1 1 1 1 0 x x | 1 0 1 0 110//0 | 1 1 1 1 1 1 0 x | 1 1 0 0 111//0 | 1 1 1 1 1 1 1 0 | 1 1 1 0 112//0 | 1 1 1 1 1 1 1 1 | 1 1 1 1 013//1 | x x x x x x x x | 1 1 1 1 1141516module encoder_83_case (din, EI, GS, EO, dout);17input [7:0] din; //编码输⼊端data_in,低电平有效18input EI; //使能输⼊端EI(选通输⼊端),EI为 0 时芯⽚⼯作,即允许编码19output [2:0] dout; //编码输出端data_out20output GS; //⽚优先编码输出端,优先编码器⼯作⼯作状态标志GS,低电平有效21output EO; //使能输出端EO(选通输出端)22reg [2:0] dout;23reg GS, EO;24always @(din or EI)25if(EI)26begin dout <= 3'b111; GS <= 1; EO <= 1; end //所有输出端被锁存在⾼电平27else28casez (din) //建议⽤casez语句,casez把z/?匹配成任意。

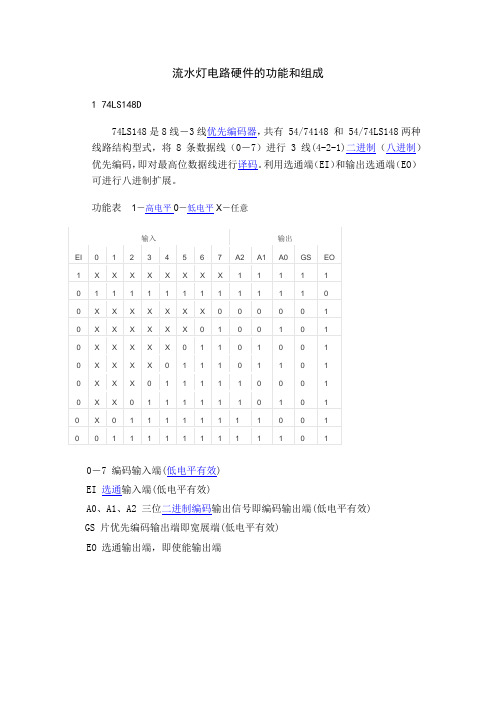

流水灯电路硬件的功能和组成

流水灯电路硬件的功能和组成1 74LS148D74LS148是8线-3线优先编码器,共有 54/74148 和 54/74LS148两种线路结构型式,将8条数据线(0-7)进行 3 线(4-2-1)二进制(八进制)优先编码,即对最高位数据线进行译码。

利用选通端(EI)和输出选通端(EO)可进行八进制扩展。

功能表0-7 编码输入端(低电平有效)EI 选通输入端(低电平有效)A0、A1、A2 三位二进制编码输出信号即编码输出端(低电平有效)GS 片优先编码输出端即宽展端(低电平有效)EO 选通输出端,即使能输出端图72.2 74LS138D74LS138 为3 线-8 线译码器,共有 54/74S138和 54/74LS138 两种线路结构型式,其74LS138工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

下图是它的原理结构图以及真值表:功能表表1无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1--芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

2 74LS04D是个6反相器,整形,隔离,提升带负载能力的作用,即给输入引脚处提供高阻特性,使信号上升时间(上升沿陡峭程度)不受内部电路影响单片机集成电路芯片,是采用超大规模集成电路技术把具有数据处理能力的中央处理器CPU 随机存储器RAM、只读存储器ROM、多种I/O口和中断系统、定时器/计时器等功能(可能还包括显示驱动电路、脉宽调制电路、模拟多路转换器、A/D转换器等电路)集成到一块硅片上构成的一个小而完善的微型计算机系统,在工业控制领域的广泛应用。

组合逻辑电路习题解答

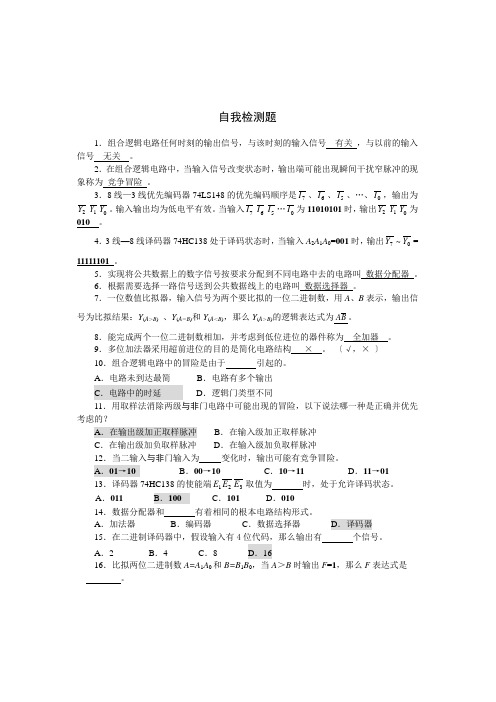

自我检测题1.组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 有关 ,与以前的输入信号 无关 。

2.在组合逻辑电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄脉冲的现象称为 竞争冒险 。

3.8线—3线优先编码器74LS148的优先编码顺序是7I 、6I 、5I 、…、0I ,输出为2Y 1Y 0Y 。

输入输出均为低电平有效。

当输入7I 6I 5I …0I 为11010101时,输出2Y 1Y 0Y 为 010 。

4.3线—8线译码器74HC138处于译码状态时,当输入A 2A 1A 0=001时,输出07Y ~Y = 11111101 。

5.实现将公共数据上的数字信号按要求分配到不同电路中去的电路叫 数据分配器 。

6.根据需要选择一路信号送到公共数据线上的电路叫 数据选择器 。

7.一位数值比拟器,输入信号为两个要比拟的一位二进制数,用A 、B 表示,输出信号为比拟结果:Y (A >B ) 、Y (A =B )和Y (A <B ),那么Y (A >B )的逻辑表达式为B A 。

8.能完成两个一位二进制数相加,并考虑到低位进位的器件称为 全加器 。

9.多位加法器采用超前进位的目的是简化电路结构 × 。

〔√,× 〕 10.组合逻辑电路中的冒险是由于 引起的。

A .电路未到达最简 B .电路有多个输出C .电路中的时延D .逻辑门类型不同11.用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的?A .在输出级加正取样脉冲B .在输入级加正取样脉冲C .在输出级加负取样脉冲D .在输入级加负取样脉冲12.当二输入与非门输入为 变化时,输出可能有竞争冒险。

A .01→10B .00→10C .10→11D .11→0113.译码器74HC138的使能端321E E E 取值为 时,处于允许译码状态。

A .011 B .100 C .101 D .01014.数据分配器和 有着相同的根本电路结构形式。

图3.103位二进制(8线-3线)编码器的框图

1 1 0 1 1 1 1 1 1 1 0 010 1

1 0 1 1 1 1 1 1 1 1 0 001 1

0 1 1 1 1 1 1 1 1 1 0 000 1

该编码器为输入低电平有效

优先编码器74LS148的功能表和逻辑符号

8线-3线优先编码器74LS148的逻辑图和功能表

返回

图3.3.5 二-十进制优先编码器74LS147

0 0 0 0 10 0 0 1 0 0

0 0 0 0 01 0 0 1 0 1

0 0 0 0 00 1 0 1 1 0

0 0 0 0 00 0 1 1 1 1

图3.11 3位二进制编码器

返回

键盘输入8421BCD码编码器(分析)

VCC 1kΩ×10

S0 0

S1 1

S2 2

S3 3

S4 4

S5 5

图3.3.27 双全加器74LS183 (a)1/2逻辑图 (b)图形符号

作业:

• 任选一标准逻辑器件(74系列或4000系列 均可);

• 查数据手册(datasheet); • 描述其功能和主要参数; • 用该器件完成一简单设计,并对电路的正

确性进行仿真验证; • 参考网站:

的逻辑图

返回

用两片74LS148接成的16线-4线优先编码器

该编码器为输入低电平有效

返回输Leabharlann 高电平有效双4选1数据选择器74LS153

功能表

输入

使能

地址

S

A1 A0

1 ××

000

001

010

011

输出

Y 0

D0 D1 D2 D3

图3.3.20 双4选1数据选择器74LS153

编码器和译码器

在许多数字设备中,数字信号的运算都是按照二进制代码进行的,而运算的 结果往往又必须转换成十进制的形式显示出来,也可以认为,编码器和译码器都 属于代码转换器类。

在数字电路中,用二进制信息表示特定对象的过程称为编码。能实现编码的 逻辑电路称为编码器。常用的编码器有二进制编码器、二-十进制编码器、优先 编码器等。

A I8 I9 B I4 I5 I6 I7 C I2 I3 I6 I7 D I1 I3 I5 I7 I9

前面讨论的二进制编码器和二-十进制编码器的输入信号是相互排斥的,同 一时刻只允许有一个有效输入信号,若同时有两个以上的输入信号要求编码时, 输出端就会出现错误。而优先编码器可以有多个输入信号同时有效,编码器按照 输入信号的优先级别进行编码。

例7.4 用一个74LS138实现逻辑函数 Y ABC ABC ABC 。

解 Y0 ABC ,Y4 ABC Y,7 ABC

,则

其逻辑图如下图所示。

Y Y0 Y4 Y7 Y 0Y 4Y 7

CT74LS138实现逻辑函数Y的逻辑图

在数字系统装置中,经常需要把数字、文字和符号等二进制编码翻译成人 们习惯的形式,直观地显示出来,以便于查看和对话。这种可以直接驱动显示 器的译码器称为显示译码器。

用门电路实现逻辑电路,如下图所示。

8线-3线编码器逻辑图

用BCD码对十进制数进行编码的电路,称为二-十进制编码器。 其中,输入信号为为 ,输出信号为 ,所以也称为十线-四线译码器。列出 二-十进制编码器的编码表,如下表所示。

二-十进制编码器的编码表

根据二-十进制编码器的编码表可以写出输出逻辑函数表达式为

二进制编码器是用n位二进制表示2n个信号的编码器。以三位二进制编码器 为例进行介绍。

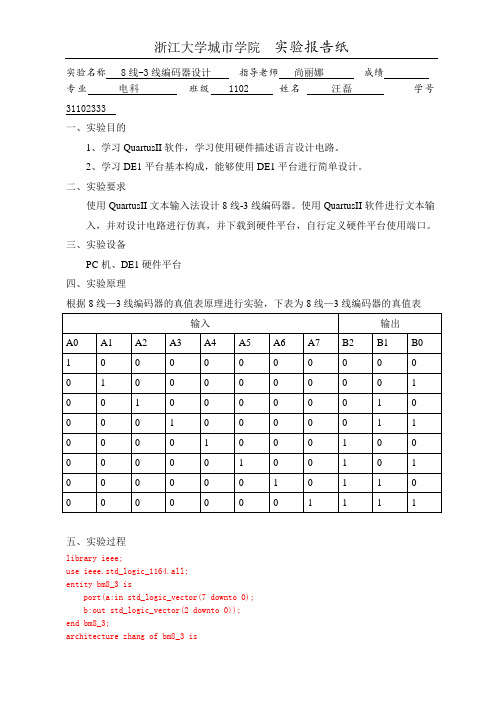

实验二 8线-3线编码器设计

实验名称 8线-3线编码器设计指导老师尚丽娜成绩专业电科班级 1102 姓名汪磊学号31102333一、实验目的1、学习QuartusII软件,学习使用硬件描述语言设计电路。

2、学习DE1平台基本构成,能够使用DE1平台进行简单设计。

二、实验要求使用QuartusII文本输入法设计8线-3线编码器。

使用QuartusII软件进行文本输入,并对设计电路进行仿真,并下载到硬件平台,自行定义硬件平台使用端口。

三、实验设备PC机、DE1硬件平台四、实验原理根据8线—3线编码器的真值表原理进行实验,下表为8线—3线编码器的真值表五、实验过程library ieee;use ieee.std_logic_1164.all;entity bm8_3 isport(a:in std_logic_vector(7 downto 0);b:out std_logic_vector(2 downto 0));end bm8_3;architecture zhang of bm8_3 isbeginprocess(a)begincase a iswhen"00000001"=>b<="000";when"00000010"=>b<="001";when"00000100"=>b<="010";when"00001000"=>b<="011";when"00010000"=>b<="100";when"00100000"=>b<="101";when"01000000"=>b<="110";when others=>b<="111";end case;end process;end zhang;六、实验结果该程序还存在一些不足,当出现10000000是和非正常输入的时候是一样的输出,所以我们进行了一些修改,修改程序与结果如下:library ieee;use ieee.std_logic_1164.all;entity e isport(a:in std_logic_vector(7 downto 0);b:out std_logic_vector(3 downto 0));end e;architecture zhang of e isbeginprocess(a)begincase a iswhen"00000001"=>b<="0000";when"00000010"=>b<="0001";when"00000100"=>b<="0010";when"00001000"=>b<="0011";when"00010000"=>b<="0100";when"00100000"=>b<="0101";when"01000000"=>b<="0110";when"10000000"=>b<="0111";when others=>b<="1111";end case;end process;end zhang;思考题一:思考题二:entity e isport(a:in bit_vector(7 downto 0);b:out bit_vector(3 downto 0)); end e;architecture zhang of e isbeginprocess(a)begincase a iswhen"00000001"=>b<="0000";when"00000010"=>b<="0001";when"00000100"=>b<="0010";when"00001000"=>b<="0011";when"00010000"=>b<="0100";when"00100000"=>b<="0101";when"01000000"=>b<="0110";when"10000000"=>b<="0111";when others=>b<="1111";end case;end process;end zhang;七、心得体会对操作更加熟练,加深对其的认识。

编码器译码器

任务资料

3.编码器

(1)二进制编码器(8线-3线编码器) 逻辑电路图:

根据真值表可以写出逻辑函 数表达式: Y2= 14+15+16+17 Y1= 12+13+16+17 Y0= 11+13+15+17

任务资料

3.编码器

(2)二-十进制编码器(8421BCD编码器)

将十进制数0~9的10个数字编成二进制代码的电路,称为二-十进 制编码器。示意图(图7.1.6):

任务资料

2.显示译码器

(3)74LS48集成显示译码器 显示原理图: 74ls48输出时高电平,与 之配合使用的是共阴极半 导体数码管,显示电路原 理图如图7.2.8所示。 74LS47的引脚排列和功能基本 与其相同,区别在于输出为低 电平有效。 图7.2.8 半导体数码管显示电路原理图

学习愉快!

10~17为编码器8路 输入信号,分别表示8个 编对象。

输入 输出

Y2、Y1、Y0为3位输出 信号,表示的是每个输入 信号所对应的编码。

任务资料

3.编码器

(1)二进制编码器(8线-3线编码器) 普通编码器任何时刻只允许一个输入信输入(即有效编码),否则 发生混乱。 真值表(如表7.1.3所示):。

项目七 组合逻辑电路

主讲:XXXXX

任务资料

3.编码器

数字不仅可以用来表示数量和顺序,还可以用来编码。在日 常生活中,我们可以接触到很多数字组成的编码,像邮政编码、 门牌号、车牌号等等,这些都是数字编码在生活中的应用。

比如身份证号码,每个公民一出生,就有一个身份证 的号码。由公安机关按照居民身份号码国家标准编制。

器中,输入、输出都是高电平

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

表

输 出 I3 0 0 0 1 0 0 I2 0 0 0 1 1 0 0 1 0 0 1 0 0 Y 2 Y 1Y 0 0 0

说明:输入高电平有效,Y2为最高位(8421BCD码)

0

4 0

0

0 0

1

1

根据真值表写函数表达式(与-或式): Y2=I4+I5+I6+I7

Y1=I2+I3+I6+I7 Y0=I1+I3+I5+I7

直接实现 Y2=I4+I5+I6+I7 Y1=I2+I3+I6+I7 Y0=I1+I3+I5+I7

Y2 Y1 Y0

1

I0 I1 I2 I3 I4 I5 I6 I7

1

1

作业:思考设计二—十进制编码器(输入低电平有 效)

表

输 出 I3 0 0 I2 0 0 Y2 Y1 Y0 0 0

十进 制数 0 1 2 3 4 5 6

输 I7 0 0 1 I6 0 I5 I1 0

入0 0 1 1 2 0 3 0 0 0 0 0 0 0 1 0 0 0 0 0 输 I7 0 1 0 0 0 I6 0 I5 I1 0 入 I4 I0 0

【新授】

例:设计一个 三位二进制编码器。

--- 8 线-3线编码器

八个输入

I0 I1 I2

.

最多能对 几个信号编码?

编 码 器 Y0 Y1 Y2

三位输出

输入:用I0~I7表示0~7这 8个数字,高电平有效; 输出:用Y0、Y1、Y2表示, 高电平有效。

本节课的任务: 设计该编码器

I7

真 值

说明:输入高电平有效,Y2为最高位

8线-3线编码器

章辉军 定南职专

【知识回顾】

组合逻辑电路的设计步骤:

实际 逻辑 功能

列表

真值 表

推导

逻辑 表示 式

化简

最简 表达 式

画图

逻辑 电路 图

分析实际逻辑功能时,首先要确定输入量、输出量,并 进行状态赋值,搞清楚输入量、输出量的逻辑关系,这非 常重要!

【知识介绍】

1.什么是编码器?

在逻辑电路中,编码器是将有特定意义的输 入数字信号、文字符号等,编成相对应的若干位 二进制代码形式输出的组合逻辑电路。