电流镜负载的差分放大器设计概要

差分放大器工作原理详细讲解

差分放大器工作原理详细讲解Differential amplifiers, also known as difference amplifiers, are essential components in analog electronic circuits. They amplify the difference between two input signals while rejecting any common-mode signals present. They play a crucial role in filtering out noise and providing high common-mode rejection ratios. Differential amplifiers are commonly used in a variety of applications such as audio amplifiers, instrumentation amplifiers, and data acquisition systems.差分放大器,也称为差分放大器,是模拟电子电路中的重要组件。

它放大两个输入信号之间的差异,同时抑制任何共模信号。

它在滤除噪声和提供高共模抑制比方面发挥着至关重要的作用。

差分放大器通常用于各种应用,如音频放大器、仪器放大器和数据采集系统。

The differential amplifier works on the principle of amplifying the voltage difference between its two input terminals. When the two input signals are equal, the output voltage is ideally zero, providing common-mode rejection. This rejection of common-mode signals is achieved through the balanced configuration of the amplifier circuit,which amplifies only the difference between the two input voltages. By using matched transistors and resistors, the amplifier can effectively reject any signals that are common to both inputs.差分放大器的工作原理是放大其两个输入端之间的电压差。

CMOS集成电路电流源负责的差分放大器

目录必做项目:与非门电路的设计一设计目的与指导二设计及过程分析三结果分析四体会五任务分工选做项目:电流镜负载的差分放大器设计一设计目的与要求二设计及过程分析三结果分析四体会五任务分工必做项目:与非门电路的设计一、设计目的与指导本项目要求基于csmc 0.35um 工艺,完成一个二输入与非门(2NAND)的电路设计。

设计要求如下:1、为了给顶层设计留出更多的布线资源,版图中只能使用金属1 和多晶硅作为互连线,输入,输出和电源、地线等pin 脚必须使用金属12、版图满足设计规则要求,并通过LVS 检查3、设计分析分析二输入与非门(2NAND)的电路,确定器件的宽长比。

设置华大九天环境启动 Aether建立自己的设计库用 Schematic Editor 画电路原理图形成符号图在 MDE 中进行电路仿真分析仿真结果,是否满足要求,若不满足要求,修正电路的参数,重新仿真。

4、版图设计用 Layout Editer 画版图利用 Aeolus 工具进行版图验证和提取DRC 规则检测LVS 检查5、Tape out增加焊盘等外围电路输出 GDSII 版图结果。

二设计及过程分析(一)电路原理图设计电路原理图由两个NMOS和两个PMOS组成。

两个PMOS并联,两个NMOS串联,然后将两个NMOS和两个PMOS串联起来。

最后加上相应的引脚(包括input、output、inputoutput),原理图如下图所示:在给5V电压时,对V0与V1进行直流仿真分析直到VOUT斜率变化最大值在2.5V左右。

不断调节管子宽长比,直至其满足要求,测得NMOS的W/L=0.8/0.5,PMOS的W/L=2/0.5.仿真图如下图所示(二)生成符号图在schematic editor工作界面,创建symbol view,生成符号图。

符号图如下图所示:符号图创建完成后,重新建立一个schematic editor,调用刚刚创建的符号图,并加上相应的输入信号,然后进行仿真,查看波形。

10ma恒流源电路

10ma恒流源电路10mA恒流源电路是一种常用的电路设计,它可以提供稳定的10mA电流输出。

恒流源电路在许多应用中都有重要的作用,比如电流源、电流驱动器等。

本文将介绍10mA恒流源电路的原理、设计方法和应用。

一、原理恒流源电路的原理是通过反馈控制,使得输出电流保持恒定。

其中,关键的元件是电流源和负载电阻。

电流源可以是电流镜、差分放大器等,而负载电阻则是通过调节电阻值来控制输出电流大小。

二、设计方法设计一个10mA恒流源电路,需要确定电流源和负载电阻的数值。

常见的电流源设计方法有电流镜电路和差分放大器电路。

1. 电流镜电路设计电流镜电路是一种常用的电流源设计方法。

它使用了一个或多个晶体管来实现恒定的电流输出。

可以通过调整电流镜中晶体管的尺寸比例来控制输出电流大小。

2. 差分放大器电路设计差分放大器也可以用作恒流源电路的设计方法。

通过调整差分放大器中的电阻值和电压源,可以实现恒定的电流输出。

差分放大器电路的设计相对复杂一些,但在某些应用中具有优势。

三、应用10mA恒流源电路在许多应用中都有广泛的应用。

以下是几个常见的应用场景:1. 电流源恒流源电路可以作为电流源来提供稳定的电流输出。

在一些需要恒定电流的电路中,如温度传感器、光电传感器等,恒流源电路可以提供稳定的电流驱动。

2. 电流驱动器恒流源电路也可以作为电流驱动器来驱动其他电路。

比如,在LED 驱动电路中,恒流源电路可以提供恒定的电流输出,保证LED的亮度稳定。

3. 模拟电路在模拟电路设计中,恒流源电路常常用于偏置电流的提供。

通过将恒流源电路连接到某些元件的基极或源极,可以实现对电路的偏置控制。

四、总结10mA恒流源电路是一种常用的电路设计,它可以提供稳定的10mA电流输出。

恒流源电路的设计方法有电流镜电路和差分放大器电路,根据实际应用需求选择合适的设计方法。

恒流源电路在电流源、电流驱动器和模拟电路设计中有着广泛的应用。

通过合理设计和调整,恒流源电路可以满足不同应用场景的需求,提供稳定可靠的电流输出。

45纳米工艺下的有源电流镜的差分放大器设计

45纳米工艺下的有源电流镜的差分放大器设计在45纳米工艺下设计差分放大器常常是信息电子学设计者面临的挑战之一。

差分放大器是电路设计中的重要组成部分,它能够在输入信号中提取出差分信号,从而实现信号放大和滤波的功能。

这篇文章将从差分放大器的结构、工作原理、设计步骤以及45纳米工艺下的优化方案等方面进行介绍,旨在给读者提供一些指导意义。

差分放大器的基本结构包括两个输入端(非反相输入端和反相输入端),一个输出端和一对工作在共模模式下的有源负载电流镜。

有源电流镜的作用在于提供一个稳定的工作电流,确保差分放大器的稳定性和线性度。

在45纳米工艺下,由于工艺缩减,发生器负载电阻的功耗限制也有一定挑战。

差分放大器的工作原理是利用差分对输入信号进行放大。

当输入信号的差分模式信号增大时,差分对的两个晶体管的电流将以不同的幅度变化,从而使输出信号增大。

而当输入信号的共模模式信号变化时,差分对的两个晶体管的电流将以相同的幅度变化,从而抵消掉输出信号的变化。

通过这种方式,差分放大器能够提取出输入信号中的差分信号,实现信号放大。

在45纳米工艺下设计差分放大器,需要考虑的因素相对较多。

首先,由于纳米级工艺的缩减,晶体管的尺寸变小,因此需要对晶体管进行精确的模型参数提取,以确保设计的准确性。

其次,由于工艺缩减,电路中的线性度、功耗和噪声都会受到一定的限制。

因此,在设计差分放大器时需要平衡这些参数,以实现最佳性能。

在实际的设计过程中,可以采用一些优化方案来改善差分放大器的性能。

例如,可以采用主动偏置电路来提高电路的线性度和稳定性;可以使用级联放大器来增加放大器的增益和带宽;还可以采用反馈电路来降低放大器的噪声水平。

这些优化方案可以根据具体的设计要求和工艺条件来选取。

综上所述,差分放大器在45纳米工艺下的设计是一个具有挑战性的任务。

通过合理地选择和优化电路结构,提取模型参数,平衡各种性能指标等方法,可以实现一款稳定、线性、低功耗的差分放大器。

电流镜负载的差分放大器设计

《IC课程设计》报告电流镜负载的差分放大器设计摘要在对单极放大器与差动放大器的电路中,电流源起一个大电阻的作用,但不消耗过多的电压余度。

而且,工作在包河区的MOS器件可以当作一个电流源。

在模拟电路中,电流源的设计是基于对基准电流的“复制”,前提是已经存在一个精确的电流源可以利用。

但是,这一方法可能引起一个无休止的循环。

一个相对比较复杂的电路被用来产生一个稳定的基准电流,这个基准电流再被复制,从而得到系统中很多电流源。

而电流镜的作用就是精确地复制电流而不收工艺和温度的影响。

在典型的电流镜中差动对的尾电流源通过一个NMOS镜像来偏置,负载电流源通过一个PMOS镜像来偏置。

电流镜中的所有晶体管通常都采用相同的栅长,以减小由于边缘扩散所产生的误差。

而且,短沟器件的阈值电压对沟道长度有一定的依赖性。

因此,电流值之比只能通过调节晶体管的宽度来实现。

而本题就是利用这一原理来实现的。

目录1设计目标 (1)2相关背景知识 (2)3设计过程 (6)3.1 电路结构设计 (6)3.2 主要电路参数的手工推导 (6)3.3 参数验证(手工推导) (7)4 电路仿真 (9)4.1 用于仿真的电路图 (9)NMOS: (9)PMOS (9)整体电路图 (10)4.2 仿真网表(注意加上注释) (10)4.3 仿真波形 (13)5 讨论 (17)6 收获和建议 (17)参考文献 (19)1设计目标设计一个电流镜负载的差分放大器,参考电路图如下:工艺ICC网站的0.35um CMOS工艺电源电压5V增益带宽积25MHz低频开环增益100负载电容2pF输入共模范围3V功耗、面积尽量小2相关背景知识据题目所述,电流镜负载的差分放大器的制作为0.35um CMOS 工艺,要求在5v 的电源电压下,负载电容为2pF 时,增益带宽积大于25MHz ,低频开环增益大于100,同时功耗和面积越小表示性能越优。

我们首先根据0.35um CMOS 工艺大致确定单个CMOS 的性能,即在一定值的W/L 下确定MOS 管在小信号模型中的等效输出电阻和栅跨导,然后记下得到的参数并将其带入到整体电路中计算,推导电流镜负载的差分放大器电路中的器件参数,例如,小信号模型的增益、带宽、功耗等,再分析是否满足题目中的各项指标的要求。

模拟集成电路课程设计差分放大器设计报告

模拟集成电路课程设计--差分放大器设计报告设计报告姓名:徐彭飞学号:201221030137 姓名:杨萍学号:201250300004差分放大器设计报告设计内容:设计一个差分放大器的模拟集成电路模块,给出电路原理图,对电路进行直流、交流、瞬态分析并给出仿真结果,给出简单的集成电路版图。

差分放大器的性能指标:1、负载电容CL=2pF2、VDD=5V3、放大管的Vdsat=200±30mV4、对管的m取4的倍数5、低频开环增益>1006、GBW>25MHz7、PM>608、共模输入范围模输入范围>3V一、电路原理图:器件尺寸:M0、M1的尺寸:M=4, W/L=2/2 M2的尺寸:M=2W, /L=W/L2/22/2 M5的尺寸:M1=1W, /L2=/22/2 M3、M4的尺寸:M=4, W/L=2/2 vp:正输入端 vn:负输入端二、电路原理图符号:三、仿真时的Power电路:四、差分放大器的DC/AC仿真(一)放大器的DC/AC仿真电路原理图:正输入端vp:加激励信号,DC=2.5,AC magnitude=1V 负输入端vn:大电阻(1G)、大电容(1F)反馈I3:提供电流源C2:放大器的负载大器的负载R0:1GC0:1FI0:调用Power(二)MOSFET的直流工作点:(三)交流分析得到的带宽、增益、相位裕度:五、单位增益接法的放大器电路的瞬态仿真(一)单位增益接法的放大器电路原理图:输入为阶跃脉冲信号(二)瞬态仿真输出波形(三)直流扫描(输出电压随直流量的变化)六、简单的电路版图。

电流镜负载的差分放大器设计

《IC课程设计》报告——模拟部分电流镜负载的差分放大器设计摘要在对单极放大器与差动放大器的电路中,电流源起一个大电阻的作用,但不消耗过多的电压余度。

而且,工作在包河区的MOS器件可以当作一个电流源。

在模拟电路中,电流源的设计是基于对基准电流的“复制”,前提是已经存在一个精确的电流源可以利用。

但是,这一方法可能引起一个无休止的循环。

一个相对比较复杂的电路被用来产生一个稳定的基准电流,这个基准电流再被复制,从而得到系统中很多电流源。

而电流镜的作用就是精确地复制电流而不收工艺和温度的影响。

在典型的电流镜中差动对的尾电流源通过一个NMOS镜像来偏置,负载电流源通过一个PMOS镜像来偏置。

电流镜中的所有晶体管通常都采用相同的栅长,以减小由于边缘扩散所产生的误差。

而且,短沟器件的阈值电压对沟道长度有一定的依赖性。

因此,电流值之比只能通过调节晶体管的宽度来实现。

而本题就是利用这一原理来实现的。

目录1设计目标 (1)2相关背景知识 (2)3设计过程 (6)3.1 电路结构设计 (6)3.2 主要电路参数的手工推导 (6)3.3 参数验证(手工推导) (7)4 电路仿真 (9)4.1 用于仿真的电路图 (9)NMOS: (9)PMOS (9)整体电路图 (10)4.2 仿真网表(注意加上注释) (10)4.3 仿真波形 (13)5 讨论 (17)6 收获和建议 (17)参考文献 (19)1设计目标设计一个电流镜负载的差分放大器,参考电路图如下:2相关背景知识据题目所述,电流镜负载的差分放大器的制作为0.35um CMOS 工艺,要求在5v 的电源电压下,负载电容为2pF 时,增益带宽积大于25MHz ,低频开环增益大于100,同时功耗和面积越小表示性能越优。

我们首先根据0.35um CMOS 工艺大致确定单个CMOS 的性能,即在一定值的W/L 下确定MOS 管在小信号模型中的等效输出电阻和栅跨导,然后记下得到的参数并将其带入到整体电路中计算,推导电流镜负载的差分放大器电路中的器件参数,例如,小信号模型的增益、带宽、功耗等,再分析是否满足题目中的各项指标的要求。

全差分运算放大器设计

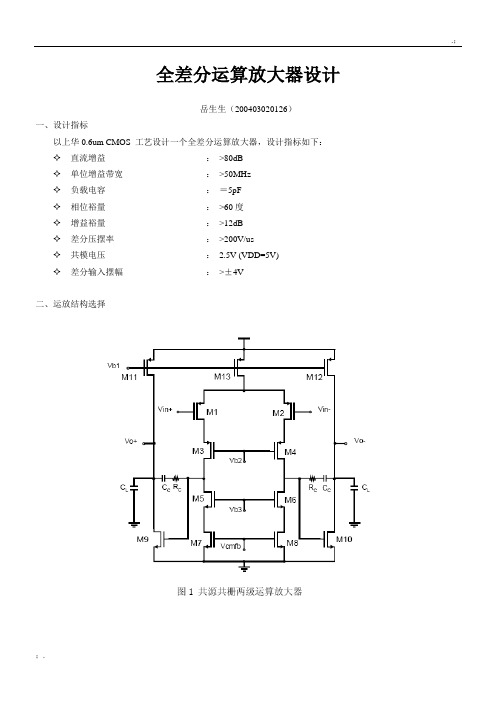

全差分运算放大器设计岳生生(200403020126)一、设计指标以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下:✧直流增益:>80dB✧单位增益带宽:>50MHz✧负载电容:=5pF✧相位裕量:>60度✧增益裕量:>12dB✧差分压摆率:>200V/us✧共模电压:2.5V (VDD=5V)✧差分输入摆幅:>±4V二、运放结构选择运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。

如图2所示;(b )折叠共源共栅,folded-cascode 。

如图3所示;(c )共源共栅,telescopic 。

如图1的前级所示。

本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT NV之和小于0.5V ,输出端的所有PMOS管的,DSAT PV之和也必须小于0.5V 。

对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。

另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。

考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。

两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。

三、性能指标分析1、 差分直流增益 (Adm>80db)该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益1351113571135135753()m m m o o o o o m m m m o o o o m m g g gg gg G A R r rr r g g r r r r=-=-=-+第二级增益92291129911()m o o o m m o o gg G AR r rgg=-=-=-+整个运算放大器的增益:4135912135753911(80)10m m m m overallo o o o m m o o dB g g g gAA A g g g gr r r r ==≥++2、 差分压摆率 (>200V/us )转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电流镜负载的差分放大器设计摘要在对单极放大器与差动放大器的电路中,电流源起一个大电阻的作用,但不消耗过多的电压余度。

而且,工作在饱和区的MOS器件可以当作一个电流源。

在模拟电路中,电流源的设计是基于对基准电流的“复制”,前提是已经存在一个精确的电流源可以利用。

但是,这一方法可能引起一个无休止的循环。

一个相对比较复杂的电路被用来产生一个稳定的基准电流,这个基准电流再被复制,从而得到系统中很多电流源。

而电流镜的作用就是精确地复制电流而不受工艺和温度的影响。

在典型的电流镜中差动对的尾电流源通过一个NMOS镜像来偏置,负载电流源通过一个PMOS镜像来偏置。

电流镜中的所有晶体管通常都采用相同的栅长,以减小由于边缘扩散所产生的误差。

而且,短沟器件的阈值电压对沟道长度有一定的依赖性。

因此,电流值之比只能通过调节晶体管的宽度来实现。

而本题就是利用这一原理来实现的。

一、设计目标(题目) (3)二、相关背景知识 (4)1、单个MOSTFET的主要参数包括: (4)三、设计过程 (5)1、电路结构 (5)2、主要电路参数的手工推导 (6)3、参数验证(手工推导) (7)四、电路仿真 (7)1、NMOS特性仿真及参数推导 (7)2、PMOS特性仿真及参数推导 (10)3、最小共模输入电压仿真 (12)4、电流镜负载的差分放大器特性仿真及参数推导 (14)五、性能指标对比 (18)六、心得 (18)一、设计目标(题目)电流镜负载的差分放大器设计一款差分放大器,要求满足性能指标:● 负载电容pF C L 1=● V VDD 5=● 对管的m 取4的倍数● 低频开环增益>100● GBW(增益带宽积)>30MHz● 输入共模范围>3V● 功耗、面积尽量小参考电路图如下图所示设计步骤:1、仿真单个MOS 的特性,得到某W/L 下的MOS 管的小信号输出电阻和跨导。

2、根据上述仿真得到的器件特性,推导上述电路中的器件参数。

3、手工推导上述尺寸下的差分级放大器的直流工作点、小信号增益、带宽、输入共模范围。

4、如果增益和带宽不符合题目要求,则修改器件参数,并重复上述计算过程。

5、一旦计算结果达到题目要求,用Hspice仿真验证上述指标。

如果仿真得到的增益和带宽不符合要求,则返回步骤2,直至符合要求二、相关背景知识传统运算放大器的输入级一般都采用电流镜负载的差分对。

如下图所示。

1、单个MOSTFET的主要参数包括:1.直流参数:开启电压Vt,即当Vds为某一固定值使Id等于一微小电流时,栅源间的电压。

2.交流小信号参数:PMOS、NMOS的栅跨导 g m : g m 越大,说明器件的放大能力越强,可以通过设计宽长比大的图形结构来提高跨导。

小信号电阻 r0 : r0 说明了Vds对Id的影响,是输出特性在某一点上切线斜率的倒数。

3.相关公式:电流公式:()()2D n OX GS TH 1I C ()V V 12DS W V Lμ=-+λ MOS 管等效电阻公式:22221o ds D r r I ==λ 44441o ds D r r I ==λ (饱和区)Gds=λnI D电压增益: 2(2||4)vd m ds ds A g r r =增益带宽积:2m L g GBW C π=三、设计过程1、电路结构整体电路如上图。

2、主要电路参数的手工推导根据题目要求:⏹ 负载电容pF C L 1=⏹ 低频开环增益>100⏹ GBW(增益带宽积)>30MHz因以上公式不考虑沟道长度调制效应和体效应,所以理论计算和实际值会有一定误差,因此在此将增益带宽积提升为40MHz 。

由2mL g GBW C π= ,得;2m Lg C π>40610⨯ 得; m g >2.51⨯()-410又有 m g=2m g = (22x 22ox W u C k L ⎛⎫⎛⎫⎪ ⎪= ⎪ ⎪ ⎪ ⎪⎝⎭⎝⎭) 从工艺库得到:model nvn nmos :+tox= '1.17e-08+toxn' 、+u0= 3.8300000e-02得:2x ox u C =6.1839⨯()-410后经仿真计算得到的2x ox u C =7.8600⨯()-410 选取ID2=15U 得: 2W L ⎛⎫ ⎪ ⎪ ⎪⎝⎭>3.396 ,考虑到存在一定误差,2W L ⎛⎫ ⎪ ⎪ ⎪⎝⎭选择10. 要使MN2和MN4同时饱和,最小V in.CM =V dsat2+V th4。

仿真得V dsat2=0.552V 。

V th4=0.780V . 得最小输入共模电压V in.CM =1.332V .仿真得V in.CM =4.5V 时,增益为45db ,增益带宽积为53MHz. 仍满足要求。

得输入共模范围大于:4.5-1.332=3.168V>3V 事实上当MN2和MN4没有同时饱和也能达到增益和带宽要求,输入共模电压V in.CM =1.1V 时,I D4=16.6u ,增益为58.3db ,增益带宽积为32.1MHz 。

3、参数验证(手工推导)根据上节的电路器件尺寸,通过手工推导出电路要求设计的各项指标。

并将计算出来的指标与要求进行对比。

如果实际电路未能达到设计要求,则还需返回上一节的计算和推动过程,直至所设计电路符合题目要求。

为了减小面积并增大增益,PMOS 的宽长比选取为1. 仿真得2W L ⎛⎫ ⎪ ⎪ ⎪⎝⎭=10的NMOS 的λn=0.03581. 2W L ⎛⎫ ⎪ ⎪ ⎪⎝⎭=1的PMOS 的λp=0.01791 2m g ==4.307⨯()-410. 故增益带宽积为2mLg GBW C π==68.548MHz >30MHz ,满足题目要求。

Ro2||Ro4=22441D D =1.241⨯106 故2(2||4)vd m ds ds A g r r ==534.5>100. 满足要求。

四、电路仿真1、NMOS 特性仿真及参数推导单个NMOS 管以二极管形式连接,如图,其中电流I=15u ,W=20U ,L=2U,VDD=5V .仿真网表:.prot.lib 'E:\viewlogic\05model\h05hvcddtt09v01.lib' tt.lib 'E:\viewlogic\05model\h05hvcddtt09v01.lib' res.lib 'E:\viewlogic\05model\h05hvcddtt09v01.lib' cap.unprotMN1 N1N32 N1N32 0 0 NVN L=2U W=20U M=4 V1I3 N1N46 0 5I1I30 N1N46 N1N32 DC=15U* DICTIONARY 1* GND = 0.options list node post.op.OPTIONS INGOLD=2 CSDF=2 .END静态仿真结果:**** mosfetssubcktelement 0:mn1model 0:nvnregion Saturatiid 1.500e-05ibs -3.406e-22ibd -3.204e-17vgs 8.466e-01vds 8.466e-01vbs 0.vth 7.805e-01vdsat 7.733e-02vod 6.606e-02beta 5.205e-03gam eff 8.945e-01gm 2.428e-04gds 5.372e-07gmb 9.836e-05cdtot 1.242e-13cgtot 3.438e-13cstot 3.494e-13cbtot 3.953e-13cgs 2.619e-13cgd 1.993e-14从中可得到gm=2.428e-04,和手工推导得到的有一定误差。

推导NMOS参数:由公式Gds=λnI D。

得λn=0.03581。

2、PMOS特性仿真及参数推导单个PMOS管以二极管形式连接,如图,其中电流I=15u,W=2U,L=2U,VDD=5V.仿真网表:.prot.lib 'E:\viewlogic\05model\h05hvcddtt09v01.lib' tt.lib 'E:\viewlogic\05model\h05hvcddtt09v01.lib' res.lib 'E:\viewlogic\05model\h05hvcddtt09v01.lib' cap.unprotMN1 0 0 N1N7 N1N9 NVP L=2U W=2U M=1 V1I2 N1N9 0 5I1I3 N1N9 N1N7 DC=15U* DICTIONARY 1* GND = 0.options list node post.op.OPTIONS INGOLD=2 CSDF=2.END静态仿真结果:**** mosfetssubcktelement 0:mn1model 0:nvpregion Saturatiid -1.500e-05ibs 2.495e-18ibd 4.729e-18vgs -2.363e+00vds -2.363e+00vbs 2.636e+00vth -1.387e+00vdsat -9.069e-01vod -9.767e-01beta 3.101e-05gam eff 3.500e-01gm 2.751e-05gds 2.687e-07gmb 4.199e-06cdtot 2.382e-15cgtot 9.145e-15cstot 7.903e-15cbtot 5.428e-15cgs 8.640e-15cgd 4.210e-16从中可得到gm=2.751e-05。

推导NMOS参数:由公式Gds=λnI D。

得λp=0.01791。

3、最小共模输入电压仿真电路图:仿真网表:.prot.lib 'E:\viewlogic\05model\h05hvcddtt09v01.lib' tt.lib 'E:\viewlogic\05model\h05hvcddtt09v01.lib' res.lib 'E:\viewlogic\05model\h05hvcddtt09v01.lib' cap.unprot*MN1 N4 N2 N3 0 NVN L=2U W=20U M=4 *MN2 N6 N5 N3 0 NVN L=2U W=20U M=4 MN1 N4 N2 N3 0 NVN L=2U W=20U M=4 MN2 N6 N2 N3 0 NVN L=2U W=20U M=4MN3 N1 N1 0 0 NVN L=2U W=2U M=1 MN4 N3 N1 0 0 NVN L=2U W=2U M=1 MP1 N4 N4 N7 N7 NVP L=2U W=2U M=1MP2 N6 N4 N7 N7 NVP L=2U W=2U M=1*VP N2 0 DC=2 AC=1V 180IREF N7 N1 DC=30UVDD N7 0 5VC1 N6 0 1P*VN N5 0 DC=2 AC=1VVN N2 0 5.dc VN 0 5 0.1* DICTIONARY 8* 1 = N1* 2 = N2* 3 = N3* 4 = N4* 5 = N5* 6 = N6* 7 = N7* GND = 0*.options probe*.AC DEC 40 100 100MEG.op*.print VDB(N6).print I1(MN2).END波形图:从图中可以看出使MN2和MN4同时饱和的最小输入共模电压V in.CM=1.4V。