第4讲内存解析

DDR系列内存详解及硬件设计规范-Michael

D D R 系列系列内存内存内存详解及硬件详解及硬件设计规范By: MichaelOct 12, 2010haolei@目录1.概述 (3)2.DDR的基本原理 (3)3.DDR SDRAM与SDRAM的不同 (5)3.1差分时钟 (6)3.2数据选取脉冲(DQS) (7)3.3写入延迟 (9)3.4突发长度与写入掩码 (10)3.5延迟锁定回路(DLL) (10)4.DDR-Ⅱ (12)4.1DDR-Ⅱ内存结构 (13)4.2DDR-Ⅱ的操作与时序设计 (15)4.3DDR-Ⅱ封装技术 (19)5.DDR-Ⅲ (21)5.1DDR-Ⅲ技术概论 (21)5.2DDR-Ⅲ内存的技术改进 (23)6.内存模组 (26)6.1内存模组的分类 (26)6.2内存模组的技术分析 (28)7.DDR 硬件设计规范 (34)7.1电源设计 (34)7.2时钟 (37)7.3数据和DQS (38)7.4地址和控制 (39)7.5PCB布局注意事项 (40)7.6PCB布线注意事项 (41)7.7EMI问题 (42)7.8测试方法 (42)摘要:本文介绍了DDR 系列SDRAM 的一些概念和难点,并分别对DDR-I/Ⅱ/Ⅲ的技术特点进行了论述,最后结合硬件设计提出一些参考设计规范。

关键字关键字::DDR, DDR, SDRAM SDRAM SDRAM, , , 内存模组内存模组内存模组, , , DQS DQS DQS, DLL, MRS, ODT , DLL, MRS, ODT, DLL, MRS, ODTAug 30, 2010 – Added DDR III and the PCB layout specification - by Michael.Hao1.概述DDR SDRAM全称为Double Data Rate SDRAM,中文名为“双倍数据流SDRAM”。

DDR SDRAM在原有的SDRAM的基础上改进而来。

DDR系列基础知识讲解

DDR3 SDRAM:Double-Data-Rate Three Synchronous Dynamic Random Access Memory,第三代双倍数据率同步动态随机存取存储器;

据输 出之前的一个时钟上升沿开始到数据传到I/O总线上止的这段时间;

2021-7-18

名词解析

tWR:Write Recovery Time,写回,保证数据的可靠写入而留出足够的写入/ 校正

时间,被用来说明对同一个bank的最后有效操作到预充电命令之间的时间量; BL:Burst Lengths,突发长度,突发是指在同一行中相邻的存储单元连续进

特性分析

存储原理 存储原理示意图:行选与列选信号将使存储电容与外界间的传输电路导通,

从而 可进行放电〔读取〕与充电〔写入〕。另外,图中刷新放大器的设计并不固

定, 目前这一功能被并入读出放大器〔Sense Amplifier ,简称S-AMP〕;

特性分析

• DDR • 延迟锁定回路〔DLL〕的任务是根据外部时钟动态修正内部时钟的延迟来

名词解析

AL:Additive Latency,附加潜伏期〔DDR2〕; WL:Write Latency,写入命令发出到第一笔数据输入的潜伏期; tRAS:Active to Precharge Command,行有效至预充电命令间隔周期; tDQSS:WRITE Command to the first corresponding rising edge of DQS,

传输,届时可通过A112位地址线来控制这一突发模式;

第4讲:网络层故障诊断与排除

8. 检查设备基本配置 当发生路由表项丢失或其他问题时,使用此方法。 (1) 使用display rip 命令查看RIP的各种参数设置 看RIP是否已经启动,相关的接口是否已经使能,network 命令设置的网段是否正确。 (2) 用debug rip 系列命令查看RIP的调试信息 每隔30秒钟,在所指定运行RIP的接口上,路由器将报告 RIP路由更新报文的传输,debug信息显示了发送每个路由 更新报文的路由和度量值。 通过debug信息可以很明白地看出RIP报文是否被正确地收 发。如果发送或接收有问题,也可从debug信息中看到是 什么原因导致发送或接收报文失败。

10. OSPF排错步骤 由于OSPF协议自身的复杂性,在配置的过程中可能会出 现错误。 OSPF协议正常运行的标志是:在每一台运行该协议的路 由器上,应该得到的路由一条也不少,并且都是最优路径。 一般步骤如下: (1) 配置故障处理。检查是否已经启动并正确配置了OSPF 协议。 (2) 局部故障处理。检查两台直接相连的路由器之间协议运 行是否正常。 (3) 区域故障处理。检查一下系统设计(主要是指区域的划分) 是否正确。 (4) 其他疑难问题。路由时通时断、路由表中存在路由却无 法PING通该地址。需要针对不同的情况具体分析。

9. RIP正常时的异常解决 应当考虑是否在接口上配置undo rip work命令,是否 验证有问题,是否引入其他路由有问题,是否访问控 制列表配置不正确等。 查看接口的display current-configuration信息,可以 看到RIP在接口模式下的配置信息是否正确。例如, 该接口是否收发RIP报文,接口配置验证了什么和验 证是什么类型的,接口向外发送的报文是RIP1还是 RIP2,是广播发送还是多播发送,接口在接收和发 送路由时是否增加附加的路由权。 查看display current-configuration信息,可以看到 RIP在协议模式下的配置信息是否正确。例如,是否 引入其他协议的路由,如果引入,是以多大的路由权 值引入的,是否对路由进行过滤和按什么规则过滤等。

内存讲解

同样地,DDR3内存也把这种技术当作性能提升的法宝,其数 据预读取已从DDR2的4位提升至8位,此时内存颗粒的核心频 率只相当于数据频率的1/8,即使内存颗粒的核心频率只有 100MHz,DDR3的数据频率也能达到800MHz。正是8位数据 预读取技术这个强大的“魔方”把DDR3的性能再往上推了一 个台阶。

当DDR发展到极限时,DDR2就来接班了,它在技术体系上继 承于DDR,主要针对“I/O Buffer”(输入/输出缓冲)部件作 出改进。以往I/O Buffer的频率等同于内存颗粒的核心频率, DDR2则把I/O Buffer的频率提升一倍,这样一来,DDR2每次 预读取的数据就达到了4位,每次传输的数据量就比DDR多一 倍。注意观察,我们不难发现,在内存从SDRAM进化至 DDR2的过程中,数据预读取技术扮演着最为关键的角色。

图4-5

Tiny-BGA

Tiny-BGA(Tiny Ball Grid Array,小型球栅阵列封装)封装方式 能减小芯片和整个内存的PCB的面积。Tiny-BGA可视为超小型的BGA 封装。Tiny-BGA封装的电路连接也和传统方式不同,内存芯片和电路 板的连接依赖芯片中心位置的细导线。在Tiny-BGA封装中,内存颗粒 是通过一个个锡球焊接在 PCB上的,由于焊点和PCB的接触面积较大, 所以内存芯片在运行中所产生的热量可以很容易地传导到PCB板上并 散发出去。Kingmax内存采用的就是Tiny-BGA封装方式。Kingmax内 存如图4-6所示。

按内存的封装方式分

SOJ TSOP Tiny-BGA BLP CSP

内存其实是由数量庞大的集成电路组成的,只不过这些电路都需 要最后封包完成。这类将集成电路封包的技术就是封装技术。封装也 可以说是安装半导体集成电路芯片用的外壳,它不仅担任放置、固定、 密封、保护芯片和增强导热性能的作用,而且还是沟通芯片内部世界 与外部电路的桥梁——芯片上的接点用导线连接到封装外壳的导线上, 这些导线又通过印制电路板上的导线与其他部件建立连接。因此对于 很多集成电路产品而言,封装技术都是非常关键的一环。根据内存的 封装形式,可以将内存分为以下几类。

微处理器(第2讲-第4讲)xiugai

1

1.3.1 微型机算计的构成

微型计算机系统的三个层次

微处理器(Microprocessor) 微型计算机(Microcomputer) 微型计算机系统(Microcomputer System)

2

微型计算机系统的三个层次

微 型 计算机 (主机)

微处理器 存储器 I/O接口 总线

ALU 寄存器 控制器

硬件系统 微 型 计算机 系 统 软件系统

外 设 系统软件 应用软件

键盘、鼠标 显示器 软驱、硬盘、光驱 打印机、扫描仪

3

第一层次:核心级——微处理器 微处理器简称CPU,是计算机的核心, 主要包括: 运算器ALU 控制器CU 寄存器组Registers CPU实现了运算功能和控制功能

10

内存操作

读:将内存单元的内容取入CPU,原单元内容不改变; 写:CPU将信息放入内存单元,单元中原内容被覆盖; 内存的读写步骤为:

CPU把要读写的内存单元的地址放到AB上 若是写操作, CPU紧接着把要写入的数据放到DB上 CPU发出读写命令 数据被写入指定的单元或从指定的单元读出到DB 若是读操作, CPU紧接着从DB上取回数据

• ① 通用数据寄存器 • 用来暂存计算过程中所用到的操作数,结果或其它信息。 • (16位)AX、BX、CX、DX • (8位)AH、AL、BH、BL、CH、CL。 AX(AH、AL):累加器,它是算术运算的主要寄存器,所有 I/O指令都使用这一寄存器与外部设备交换数据。

BX(BH,BL):基址寄存器,对内存储器寻址时,常用来存放

ห้องสมุดไป่ตู้

第四讲内存作业题1答案

第四讲内存作业题及答案一填空1 CPU 的外频是100MHz ,倍频是17 ,那么CPU 的工作频率(即主频)是(1.7)GHz2 在拆装微机的器件前,应该释放掉手上的(静电)3 目前在主流主板上的BIOS芯片通常为(Flash ROM)芯片4 AGP(Accelerated Graphics Port)插槽插的组件是(显卡)5 SDRAM内存条的金手指通常是(168 )线的,DDR SDRAM内存条的金手指通常是(184 )线的,DDRII 内存条的金手指通常是( 240)线的。

6 BIOS是计算机中最基础的而又最重要的程序,其中文名称是( 基本输入输出系统)。

7 (硬件)是构成计算机系统的物质基础,而(软件)是计算机系统的灵魂,二者相辅相成,缺一不可8 CPU的接口形式只有两类:(插卡式)或(针角式)9 在计算机系统中,CPU起着主要作用,而在主板系统中,起重要作用的则是主板上的(芯片组)10 计算机电源一般分为:(AT)和(ATX)。

11 世界上最大的两个芯片(cpu)生产厂商是(AMD)和(INTEL ),两个芯片组的生产厂商是(VIA)和(INTEL),两个显示卡芯片生产厂商是(ATI)和(NVIDIA),其中(ATI )已经被AMD公司兼并12 电源向主机系统提供的电压一般为(+ 12 )V,(+5 )V,(+3.3 )V.13 主板上有一块时钟发生器(也即时钟芯片),它一般时与主板上的另外一块芯片(晶体振荡器)配合在一起工作。

14 AGP总线的频率为(66MHz和133MHz两种)。

15 SATA接口(总线)的数据传输方式为(串行)。

16 给cpu加上散热片和风扇的主要目的是为了(为了散去CPU在工作过程中产生的热量)。

17 机箱前面板信号线的连接,HDD LED是指(硬盘灯),RESET指的是(复位开关)。

18 DDR内存为双面(184)针的插槽结构。

19 安装CPU是涂抹硅胶的目的是为了更好的(对CPU进行散热)。

内存条详细讲解

内存条详细讲解内存条是连接CPU 和其他设备的通道!起到缓冲和数据交换作用!!!!内存的作用与分类内存是电脑中的主要部件,它是相对于外存而言的。

我们平常使用的程序,如WindowsXP系统、打字软件、游戏软件等,一般都是安装在硬盘等外存上的,但仅此是不能使用其功能的,必须把它们调入内存中运行,才能真正使用其功能,我们平时输入一段文字,或玩一个游戏,其实都是在内存中进行的。

通常我们把要永久保存的、大量的数据存储在外存上,而把一些临时的或少量的数据和程序放在内存上。

内存分为DRAM和ROM两种,前者又叫动态随机存储器,它的一个主要特征是断电后数据会丢失,我们平时说的内存就是指这一种;后者又叫只读存储器,我们平时开机首先启动的是存于主板上ROM中的BIOS程序,然后再由它去调用硬盘中的Windows,ROM的一个主要特征是断电后数据不会丢失。

根据内存条上的引脚多少,我们可以把内存条分为30线、72线、168线等几种。

30线与72线的内存条又称为单列存储器模块SIMM,168线的内存条又称为双列存储器模块DIMM。

目前30线内存条已经没有了;前两年的流行品种是72线的内存条,其容量一般有4兆、8兆、16兆和32兆等几种;目前市场的主流品种是168线内存条,168线内存条的容量一般有16兆、32兆、64兆、128兆等几种,一般的电脑插一条就OK了,不过,只有基于VX、TX、BX芯片组的主板才支持168线的内存条。

内存发展简史起初,电脑所使用的内存是一块块的IC,我们必须把它们焊接到主机板上才能正常使用,一旦某一块内存IC坏了,必须焊下来才能更换,这实在是太费劲了。

后来,电脑设计人员发明了模块化的条装内存,每一条上集成了多块内存IC,相应地,在主板上设计了内存插槽,这样,内存条就可随意拆卸了,从此,内存的维修和扩充都变得非常方便。

根据内存条上的引脚多少,我们可以把内存条分为30线、72线、168线等几种。

30线与72线的内存条又称为单列存储器模块SIMM,168线的内存条又称为双列存储器模块DIMM。

有线数字电视讲座第四讲-有线数字电视机顶盒-2

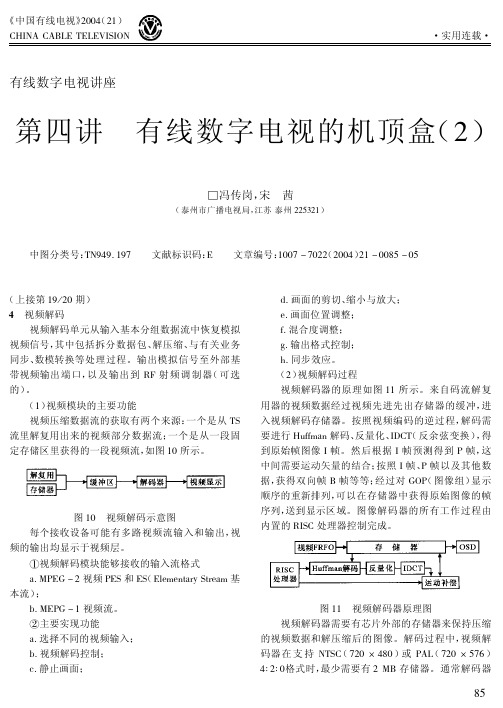

《中国有线电视》2004(21)CHINA CABLE TELEVISION・实用连载・有线数字电视讲座第四讲 有线数字电视的机顶盒(2)□冯传岗,宋 茜(泰州市广播电视局,江苏泰州225321)中图分类号:TN949.197 文献标识码:E 文章编号:1007-7022(2004)21-0085-05(上接第19/20期)4 视频解码视频解码单元从输入基本分组数据流中恢复模拟视频信号,其中包括拆分数据包、解压缩、与有关业务同步、数模转换等处理过程。

输出模拟信号至外部基带视频输出端口,以及输出到RF 射频调制器(可选的)。

(1)视频模块的主要功能视频压缩数据流的获取有两个来源:一个是从TS流里解复用出来的视频部分数据流;一个是从一段固定存储区里获得的一段视频流,如图10所示。

图10 视频解码示意图每个接收设备可能有多路视频流输入和输出,视频的输出均显示于视频层。

①视频解码模块能够接收的输入流格式a.MPEG -2视频PES 和ES (Elementary Stream 基本流);b.MEPG -1视频流。

②主要实现功能a.选择不同的视频输入;b.视频解码控制;c.静止画面;d.画面的剪切、缩小与放大;e.画面位置调整;f.混合度调整;g.输出格式控制;h.同步效应。

(2)视频解码过程视频解码器的原理如图11所示。

来自码流解复用器的视频数据经过视频先进先出存储器的缓冲,进入视频解码存储器。

按照视频编码的逆过程,解码需要进行Huffman 解码、反量化、IDCT (反余弦变换),得到原始帧图像I 帧。

然后根据I 帧预测得到P 帧,这中间需要运动矢量的结合;按照I 帧、P 帧以及其他数据,获得双向帧B 帧等等;经过对GOP (图像组)显示顺序的重新排列,可以在存储器中获得原始图像的帧序列,送到显示区域。

图像解码器的所有工作过程由内置的RISC 处理器控制完成。

图11 视频解码器原理图视频解码器需要有芯片外部的存储器来保持压缩的视频数据和解压缩后的图像。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

am,与超频 版分开,D3代表是DDR3内 存;N代表是Non -ECC,即 不带ECC内存校验功能,9代 表CAS内存延迟是9,及9-99

另2

• KHX(HyperX)一向 是金士顿高端内存的 代名词,1600是频率, CL延迟为8,D3表示 DDR3代,K3三通道, 6G表示总容量

4. DDR3

DDR3是一种电脑内存规格。它属于SDRAM家族的内 存产品,提供了相较于DDR2 SDRAM更高的运行 效能与更低的电压,是DDR2 SDRAM(四倍资料 率同步动态随机存取内存)的后继者(增加至八 倍),也是现时流行的内存产品。

DRAM内存的规范(内存主频)

1.DDR SDRAM 规范

(1)DDR200 (2)DDR266 (3)DDR333 (4)DDR400

2.DDR2

(1)DDR2 400 (2)DDR2 533 (3)DDR2 667 (4)DDR2 800

3.DDR3

(1)DDR3 800 (3)DDR3 1333 (5)DDR3 1800 (7)DDR3 2000 (9)DDR3 2200 (2)DDR3 1066 (4)DDR3 1600 (6)DDR3 1866 (8)DDR3 2133 (10)DDR3 2400

4.5内存的类型

• 内存主要分为ROM和RAM两类

• ROM:ROM数据不能随意更新,但是在任何时候都可以 读取。即使是断电,ROM也能够保留数据。但是资料一 但写入后只能用特殊方法或根本无法更改 。 • RAM:在通电情况下不能长时间保持电量,需要每隔一 段时间就进行一次重新加电过程,RAM通常是作为操作 系统或其他正在运行程序的临时存储介质。

2. DDR SDRAM(Double Data Rate SDRAM)

DDR就是双倍数据传输率(Double Data Rate),DDR SDRAM就是双倍 数据传输率的SDRAM, DDR内存是SDRAM 的升级版本,它是更先进 的SDRAM。SDRAM只在时钟周期的上升沿传输指令、地址和数据。而 DDR SDRAM的数据线有特殊的电路,可以让它在时钟的上下沿都传输 数据。 DDR SDRAM与普通SDRAM的另一个比较明显的不同点在于电压,普通 SDRAM的额定电压为3.3V,而DDR SDRAM则为2.5V。在物理结构上, DDR SDRAM采用采用184针(pin),金手指部分只有一个缺槽。

4.2 内存条外观及组成

4.3 主流内存

• 主要涉及项目有:品牌、价格、类型、容量和主频(工作 频率) • 现在市场上用于个人电脑的内存主要有三种,一种是老式 的DDR,一种是目前主流的DDR2和DDR3。

主流内存举例

4.4 识别内存方法——金 士顿为例

• KVR16N11/4,KVR即金士顿ValueRAM的 缩写,大意为金士顿入门级内存;16代表 1600MHz;N代表non-ecc,即无ecc校验 功能;11代表时序为CL11;/4为4GB容量 的意思。

第4讲 内存

11专1

数信科学系

4.1 内存概要

• 内存是计算机中重要的部件之一,它是与CPU进行沟通的 桥梁。计算机中所有程序的运行都是在内存中进行的,因 此内存的性能对计算机的影响非常大。 • 内存(Memory)也被称为内存储器,其作用是用于暂时存 放CPU中的运算数据,以及与硬盘等外部存储器交换的数 据。只要计算机在运行中,CPU就会把需要运算的数据调 到内存中进行运算,当运算完成后CPU再将结果传送出来, 内存的运行也决定了计算机的稳定运行。 • 内存是由内存芯片、电路板、金手指等部分组成的。 • 相对CPU 、主板,内存通用性强。

4.6 内存的性能指标

1.存储容量

存储容量是衡量内存非常 重要指标,是人们最为关 注的方面。

4.5.2 RAM

• DRAM(Dynamic Random Access Memory,动态随机 存储器)目前我们所说的内存。 • SRAM(Static Random Access Memory,静态随机存储器) • 差异在于DRAM需要由存储器控制电路按一定周期对存储器 刷新,才能维系数据保存,SRAM的数据则不需要刷新过程, 在加电期间,数据不会丢失。

3. DDR2

由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技术标准, 它与上一代DDR内存技术标准最大的不同就是,虽然同是采用了在时钟 的上升/下降延同时进行数据传输的基本方式,但DDR2内存却拥有两倍 于上一代DDR内存预读取能力(即:4bit数据读预取)。换句话说, DDR2内存每个时钟能够以4倍外部总线的速度读/写数据,并且能够以 内部控制总线4倍的速度运行。

4.5.3 DRAM内存的种类

1. SDRAM(Synchronous DRAM)

SDRAM(Synchronous DRAM)的中文名字是“同步动态随机存储器”, 它是PC100和PC133规范所广泛使用的内存类型,其接口为168线的 DIMM类型(这种类型接口内存插板的两边都有数据接口触片),最高速度 可达5ns, 工作电压3.3 V。SDRAM与系统时钟同步,以相同的速度同 步工作,即在一个CPU周期内来完成数据的访问和刷新,因此数据可在 脉冲周期开始传输。SDRAM也采用了多体(Bank)存储器结构和突发 模式,能传输一整块而不是一段数据,大大提高了数据传输率,最大可 达133 MHz。

• 4.5.1 ROM

– 1.ROM – 2.PROM(Programmable Rom)即可编程ROM。 – 3.EPROM(Erasable Programmable Rom)即可擦写、可编程 ROM,它可以通过特殊的装置(通常是紫外线)反复擦除,并重写 其中的信息。 – 4.EEPROM(Electrically Erasable Programmable Rom)即电可擦 写、可编程ROM,可以使用电信号来对其进行擦写。 – 5.Flash Memory