数字信号采集回放系统电路设计

实时高速高分辨率信号采集存储与回放系统

究生, 主要 从事数 字化 测试 技 术研 究。

收 稿 日期:o 6 0 — 6 2o —9 0

咨 询 编 号 :7 4 1 0 0 2

【l n o eie, c A S - 16 H R S l a gD vcs n . D P 2 2 xS A C D P Al I

维普资讯

实时高速 高分辨 率信 号采 存储 与 回放 系统

- 3 7-

●春 秋 视 讯 专 栏

实时高速高分辨率信号采集存储 与回放 系统

李 永冰

西安 春 秋 视 讯 有 限责 任 公 司. 西 西 安 7 0 6 陕 10 5

1 引 言

监 控 接 口可 以选择 为 U B 口、 口等 ; 主 D P与 S 网 而 S 从 D P之 间 的通 讯 也能 通过 其他 各类 总线 , 如并 S 例 行 的数 据, 址 总线 、 同步 串 口、C、 P 、 I K 等 , 地 F H IL N 完 全取 决于 用户 的需要 , 十分 灵 活方便 。

据 不 同 的 用户 要 求 可 以任 意 选 择 回放 数 据 的 起 始 位置 和结 束位置 。

场 采 集 的真 实 信 号 , 系统 性 能 进 行 研 究 , 省 了 对 节

大量 的外场 实验 时间 和科研 经 费 。 但是 当 AD 分辨 率 与采 样率 提 高 时 , 据 传输 / 数 率相应 也 变得 越 高 , 保持 高速 数 据 存 储过 程 的可靠 性 、 时性 将 会 成为 一个 比较棘 手 的 问题 。春秋 视 实

用 户可 以根 据 系统 需 要 和 D P所 能提 供 的 资 S 源 采用其 他 的监控方 法 :例 如 P C与 主 D P之 间 的 S

毕业设计188数字录音与回放系统的实现

数字录音与回放系统的实现目录1.引言 (1)2. 数字录音及回放系统组成及原理 (2)2.1 数字录音及回放系统的组成 (2)2.2 数字录音及回放系统原理 (3)3. 数字录音及回放系统各主要部分电路原理与接口 (4)3.1 数字录音系统芯片简介 (4)3.2 数字录音及回放系统接口电路设计与编程原理 (4)3.2.1 AD733111与ADSP-2181的接口电路 (5)3.2.2 AD733111编程 (6)3.2.3 录音系统编程 (8)4. 数字录音及回放系统控制软件设计 (10)5. 数字录音及回放系统调试 (11)6. 结论与展望 (12)参考文献: (12)摘要:本文主要介绍了数字录音系统及回放功能的实现,该系统以DSP数字信号处理器为核心,采用存储器作为数字语音数据存储器。

提出了一个基于数字信号处理器(DSP)和闪速存储器(FLASH)的数字录音与回放系统实现方案,在分析FLASH特性及其编程方法的基础上,设计了DSP与FLASH接口的硬件和软件。

关键字:数字录音语音数字处理回放系统实现1.引言随着社会经济和通信行业的迅速发展,通信已经给我们生活带来了很多方便,与我们的生活,工作已经密不可分了。

但这种方便快捷同时也带来了一个弊病,那就是有些事情事后说不清,容易造成不必要的麻烦,有些单位只得以电话录音机来暂时解决这个问题,此类设备自动化程度差,存储量小,查询不便,而且需要每条线路都配备一个相应设备,成本高,效率低。

特别是在电力调度,公安监听,防汛报警等较特殊的领域,使其对语音工作的发生过程都需要有个准确可靠的记录过程,随着社会技术的进步,这些领域自身对可靠的语音处理效果的追求,使得对老式录音设备的社会适应性出了有力的挑战。

随着数字化技术的迅速发展,语音信号数字处理技术的不断成熟,可编程器件和功能强大的数字信号处理器(DSP)的广泛应用,传统的模拟音像设备大量地被各种数字设备所代替。

毕业设计175数字存储与语音回放系统

引言语言在人类发展史中起到了至关重要的作用,它的作用并不亚于直立行走和工具的使用,怎样能把人类的语言丝毫不差地记录下来也是人们一直思考的问题。

传统的磁带语音录放系统因其体积大、使用不便,在电子与信息处理的使用中受到许多限制。

本文提出的体积小巧,功耗低的数字化语音存储与回放系统将完全可以替代它。

数字化语音存储与回放系统的基本原理是对语音的录音与放音的数字控制。

使用单片机以及外部电路的配合完全可以达到语音存储与回放的目的。

本系统采用了美国ISD公司的专利产品ISD2590(录音90秒)语音芯片,此芯片具有音质自然、使用方便、单片存储、反复录放、低功耗、抗断电等特点。

该芯片采用模拟数据直接在半导体存储器中存储的技术,不需经过A/D或D/A转换。

因此能够非常真实、自然地再现语音、音乐、音调和效果声,避免了一般固体录音电路因量化和压缩造成的量化噪声和"金属声"。

片内信息可保存100年(无需后备电源),存储单元可反复录音十万次。

语音芯片的使用大大简化了本系统的设计过程。

该芯片的一大特点就是可分段录制声音并分段播放出来,通过89C51单片机对语音芯片进行控制完成录放。

随着科学技术的飞速发展,仅仅存储和回放语音是不够的。

语音技术正朝着语音合成和语音识别的方向发展。

智能翻译机、语音拨号、语音查询、语音自动定票系统、语音工业控制等等,可以想见,凡用计算机的地方都会有语音识别。

在计算机辅助教育方面,计算机就成为专业的家庭辅导教师;在幼儿进行启蒙教育的玩具中,语音识别也将倍受欢迎。

电脑语音合成技术即CTI(Computer Telephone Integration),是用计算机技术处理电话语音。

通常是建一个信息呼叫中心,用户打来电话时计算机会自动地一层层地转给相关部门,一直到为用户解决问题为止。

可想而知,随着语音合成技术研究的突破,其对计算机发展和社会生活的重要性日益凸现出来。

其应用和经济社会效益前景非常良好。

基于单片机的语音存储与回放系统毕业设计

基于单片机的语音存储与回放系统毕业设计基于单片机的语音存储与回放系统是一种能够实现语音录制、存储和回放功能的设备。

它可以用于各种应用场景,如语音备忘录、语音留言板、语音识别系统等。

该系统的设计需要完成以下关键功能:1. 语音录制:通过麦克风或其他输入设备采集语音信号,并将其转换为数字信号。

可以使用ADC模块将模拟信号转换为数字信号。

2. 存储功能:设计合适的存储器,如EEPROM或Flash存储器,用于存储采集到的语音信号。

存储器的容量应根据实际需求确定,并能够支持快速的读写操作。

3. 控制功能:设计合适的控制电路,通过按键或其他输入设备实现对语音录制和回放功能的控制。

可以使用GPIO口或外部中断等方式实现按键输入的响应。

4. 回放功能:设计合适的音频输出电路,将存储的语音信号转换为模拟信号,并通过扬声器或耳机输出。

可以使用DAC模块将数字信号转换为模拟信号。

5. 用户界面:设计合适的显示屏幕和操作界面,用于显示当前状态和操作指令。

可以使用LCD显示屏和按键等设备实现用户交互。

在设计过程中,需要考虑系统的实时性、容错性和稳定性。

同时,还需要进行适当的电路布局和信号处理,以减少噪音和干扰对语音信号的影响。

在编程方面,可以使用C语言或汇编语言编写程序,实现语音录制、存储和回放的功能。

需要考虑存储器的管理和控制、按键输入的处理、音频数据的处理等方面。

最后,还需要进行系统的测试和调试,确保系统的稳定性和功能完整性。

可以通过模拟语音信号进行录制和回放测试,检查系统的录制和回放效果是否符合要求。

综上所述,基于单片机的语音存储与回放系统的毕业设计需要涉及硬件电路设计、嵌入式软件编程和系统测试等多个方面的知识和技能。

需要深入理解语音信号处理、存储器管理和控制、电路设计和嵌入式系统等知识,并具备一定的创新能力和解决问题的能力。

论数字化语音存储回放系统设计

论数字化语音存储回放系统设计作者:陈子毅来源:《科技资讯》2012年第33期摘要:近年来,随着科学技术水平的不断提高,各种高科技产品逐渐走进了人们的生活。

数字化语音处理技术作为高科技应用领域当中的一个热点,其从理论到相关产品现已基本趋于完善。

它与医疗卫生机构以及福利事业的生活支援系统有着十分密切的联系,并且极有可能成为下一代操作系统的用户界面。

基于此点,本文就数字化语音存储回放系统的设计进行研究。

关键词:数字化单片机语音存储回放系统设计中图分类号:TN912 文献标识码:A 文章编号:1672-3791(2012)11(c)-0028-011 数字化语音存储回放系统的基本原理1.1 语音信号采集通常情况下,人能够听到的声音频率范围为大于20 Hz、小于20000 Hz的信号,通常情况下的语音信号频率最高能达到3400 Hz。

所谓语音信号采集是指将通过麦克风和高频放大器的语音声波信息,转换为模拟量电信号,最后转变成数字量的过程。

要想确保采集信号不存在失真现象,采样频率要为模拟信号最高频率的2倍以上,即最低频率为6800 Hz,在考虑语言质量的前提下,应当将采样频率确定为8000 Hz。

1.2 语音压缩待录制信号在输入到系统中后,先被分配到各自的预放大器,直到放大到合适的电平后,转移到信号混合单元将信号进行混合,形成一路完整的信号,并交由低通滤波器将高频滤去,将处理后的语音送至A/D转换器实施模数转换,将其变为频率为8 kHz的语音信号,形成特定的串行比特流,利用串行的方式将语音信号送至语音压缩单位。

利用语言压缩单元20 ms为一帧的速率对语音信号实施40∶1的高倍压缩,最终生成2.4 kb/s的压缩语音,由此完成语音压缩流程。

1.3 语音生成原理一般情况下,由于可将语音生成过程看作是语音采集过程的反向过程,所以掌握语音生成过程能够实现回放语音信号的功能。

值得注意的是,语音生成过程并不是原原本本地将语音信息进行恢复,而是对原来语音可重组、可控制的地方进行实时恢复。

语音采集回放电路

数字化语音存储与回放系统高海春, 任开达, 孔德峰, 徐和杰, 李文瑜(华东船舶工业学院电子与信息系, 江苏镇江212003)摘要: 设计并制作了一个数字化语音存储与回放系统,由于采用了滑动平均值滤波法进行数字滤波及非失真压缩算法,该系统获得了稳定的性能。

关键词: 语音; 单片机应用; 回放系统0 引言传统的磁带语音录放系统因其体积大、使用不便,在电子与信息处理的使用中受到许多限制。

本文提出的体积小巧,功耗低的数字化语音存储与回放系统将完全可以替代它。

数字化语音存储与回放系统的基本原理是对语音的录音与放音的数字控制。

其中,关键技术在于:为了增加语音存储时间,提高存储器的利用率,采用了非失真压缩算法对语音信号进行压缩后再存储,而在回放时再进行解压缩;同时,对输入语音信号进行数字滤波以抑制杂音和干扰,从而确保了语音回放的可靠质量。

1 基本原理1) 语音采集原理人耳能听到的声音是一种频率范围为20 Hz~20 000 Hz ,而一般语音频率最高为3 400 Hz。

语音的采集是指语音声波信号经麦克风和高频放大器转换成有一定幅度的模拟量电信号,然后再转换成数字量的全过程。

根据“奈奎斯特采样定理”, 采样频率必须大于模拟信号最高频率的两倍[1 ] ,由于语音信号频率为300~3 400 Hz ,所以把语音采集的采样频率定为8 kHz。

2) 语音生成原理单片机语音生成过程,可以看成是语音采集过程的逆过程,但又不是原封不动地恢复原来的语音,而是对原来语音的可控制、可重组的实时恢复。

在放音时,只要依原先的采样值经D/ A 接口处理,便可使原音重现。

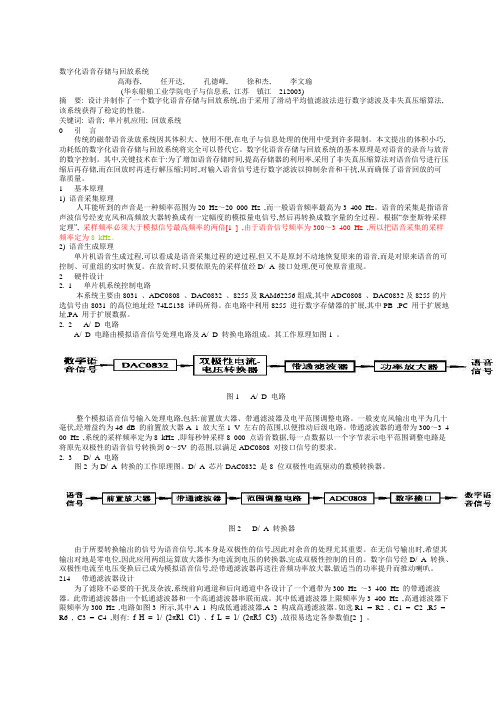

2 硬件设计2. 1 单片机系统控制电路本系统主要由8031 、ADC0808 、DAC0832 、8255及RAM62256组成,其中ADC0808 、DAC0832及8255的片选信号由8031 的高位地址经74LS138 译码所得。

在电路中利用8255 进行数字存储器的扩展,其中PB ,PC 用于扩展地址,PA 用于扩展数据。

基于TMS320C5416DSP芯片的语音录放器的设计

基于TMS320C5416DSP芯片的语音录放器的设计摘要DSP 技术在音频处理领域的应用越来越广。

目前,在很多语音处理系统中都用到了语音录放模块,采集现场的声音并存储起来供以后回放。

语音处理系统的实时性、功耗、体积、以及对语音信号的保真度都是很影响系统性能的关键因素。

因此,语音录放器的设计是非常必要的。

本设计采用的高速TMS320C5416DSP芯片,最高频率能达到160MIPS,能够很好的解决系统的实时性;采用的数字编解码芯片TLV320AIC23(以下简称AIC23)具有16~32位采样精度,录音回放模式下仅23mW的功耗。

因此,该音频编解码芯片与TMS320C5416DSP的结合是可移动数字音频录放系统、现场语音采集系统的理想解决方案。

本文首先介绍了基于TMS320C5416DSP芯片的语音录放系统的工作原理,给出了整体设计方案和工作框图,然后给出了系统的硬件设计方案;然后介绍了基于TMS320C5416DSP芯片的语音录放系统的软件设计。

在整个设计过程中,我们采用了TLV320AIC23DSP芯片为核心音频录放接口器件,结合TMS320C5416DSP芯片,语音数据存储FLASH存储器等进行了硬件设计。

软件部分则采用模块化的设计方法,用汇编语言来实现。

该语音录放器的设计能够完成语音采集,播放,存储,回放,基本实现了语音录放功能。

关键词:TMS320C5416,TLV320AIC23,DSP,语音录放THE DESIGN OF SPEECH RECORDING ANDPLAYING BASED ON TMS320C5416 DSP CHIPABSTRACTThe use of DSP technology in the field of audio processing is increasingly wider. At present, many speech processing systems are used in speech-recording module, acquisition scene speech and stored for later playback. Speech processing System with real-time, power consumption, size, and the speech signal fidelity is a key factor which is affecting system performance. Therefore, speech recording and playing design is very necessary.The design of high-speed chip used TMS320C5416 DSP, the maximum frequency can reach 160 MIPS,which is a good solution to the real-time system; the figures used in the codec chip TLV320AIC23 (hereinafter referred AIC23) is 16 ~ 32 Sampling precision, recording playback mode only 23 mw of power. Therefore, The Audio Decoder Chip and the combination TMS320C5416 DSP Mobile Digital Audio Recording and Playback System Speech Acquisition scene, is the ideal solution.This paper firstly introduces the Speech Recording and Playback System of principle based on TMS320C5416 DSP chip, given the overall design of the plan and diagram, and then gives the system hardware design program; Secondly V oice Recording and Playback System software design based on TMS320C5416 DSP chip .Throughout the design process, we used TLV320AIC23 DSP core chips for audio-recording device interface, TMS320C5416 DSP combination of chips, Speech Data Storage Flash memory, and so on the hardware design. Software is a modular design method, the assembly language to achieve.The speech recording of the design is to complete speech acquisition, broadcast, store, playback, the basic realization of the Speech Recording and Playback function.KEY WORDS:TMS320C5416,TLV320AIC23,DSP,Speech recording and playing目录前言 (1)第1章语音录放器的技术方案及硬件电路设计 (2)§1.1语音录放器的性能指标和硬件方案 (2)§1.1.1 语音录放器的主要性能 (2)§1.1.2 硬件设计方案 (3)§1.2 语音录放系统的硬件电路设计 (4)§1.2.1 TMS320C5416DSP数字信号处理接口电路模块 (5)§1.2.2 TLV320AIC23语音录放接口电路模块 (9)§1.2.3语音数据存储接口电路模块 (12)§1.2.4 音频接口电路模块 (13)§1.2.5 电源接口电路模块 (15)第2章语音录放器的应用软件设计 (17)§2.1 语音录放器应用软件系统的设计方案 (17)§2.2 主程序模块 (17)§2.3 语音录放模块程序设计 (20)§2.3.1 MCBSP的配置 (20)§2.3.2 AIC23的初始化 (22)结论 (26)参考文献 (27)致谢 (28)附录 (29)前言DSP处理速度快,功耗低,性能好,基于TMS320C5416DSP芯片的语音录放器存储容量大,语音录放时间长,具有很好的通信音质等特点,因此被广泛应用于很多领域中。

基于实测信号回放的半实物仿真系统设计

戤

1 0 8 3 2 )

之间, 因此在 将 计 算 机 和 单 片 机 的 R x D和 Tx D 交

回放 信 号

叉连 接 时 , 必 须 进 行 电 平 转 换 。这 里 使 用 的 是

MAX 2 3 2电平 转换 芯 片 , 如 图 2所示 。

VCC

图 1 系统 总体 结构 框 图

f ou nd a t i o n f o r f u r t he r s t u dy .

Ke y wo r d s : me as ur e d s i g na l ;ha r dwa r e — i n — t h e — l o o p s i mu l a t i o n;p l a y ba c k s y s t e m

Ab s t r a c t : To obt a i n r e a l me a s u r e d s i g na 1 p l a ys a v e r y i mpo r t a n t r ol e i n t he s t ud y o f c on t r o l s y s — t e n .As r r e s t r i c t e d b y v a r i ou s f a c t o r s s u c h a s e nv i r on me nt a1 f a c t or s ,t h e me a s u r e d s i g na li S o f t e n d i f f i c u l t t o ob t a i n . Onl y l i mi t e d s a m pl e s o f a di g i t a l s i g na l c a n be go t t e n,a nd i t i s d i f f i c ul t t o us e i n e x pe r i me n t s .A ki nd of ha r d wa r e — i n - t he — l o o p s i mu l a t i o n s y s t e m b a s e d on S TC8 9 C52 M CU a n d DAC0 83 2 i s d e s i gn e d i n t hi s p a p e r ,a nd t he d i gi t a l s i g na l s i n s t o r e wi l l be pl a y b a c k i nt o t h e o r i gi —

基于单片机信号采集与回放系统的设计与实现_吴宁

基于单片机信号采集与回放系统的设计与实现*吴宁1,李斌2,柴世文3(1.兰州工业高等专科学校电气工程系,甘肃兰州730050;2.兰州石化公司研究院,甘肃兰州730060)摘要:重点介绍了一种基于89C52单片机为控制核心的信号采集与回放控制系统。

该系统结合ADC0809、DAC0832数据采集模块,实现对两路外部信号进行采集、存储及回放。

系统模拟部分主要包括信号调节电路和A/D模块等:软件部分主要由主程序和子程序模块组成,主要实现了A/D转换器的启动与及对采样数据的存储,频率及幅值的计算,按键及显示屏的控制。

该系统经过测试实验,能耗低,性价比高,具有较高的实际应用价值。

关键词:信号采集与存储;信号复现;信号调节;回放系统中图分类号:TM13文献标识码:A文章编号:1007-4414(2011)06-0121-03The design and implementation of signal acquisition and playbacksystem based on microcontrollerWu Ning1,Li Bin2,Chai Shi-wen3(1.Electrical engineering department,Lanzhou polytechnic college,Lanzhou730050,China;2.Research institute of Lanzhou petrochemical corporation,Lanzhou730060,China;3.Gansu academy of mechanical science,Lanzhou Gansu730030,China)Abstract:This paper proposed a signal acquisition and playback control system based on89C52as the control unit.The sys-tem associated with ADC0809and DAC0832to achieve the two external signal acquisition,storage and playback.The analog section of the system included signal adjusting circuit and A/D module.The function of software modules consisted of main program and subroutine.It realized the start of the A/D converter,the sampling data storage,the calculation of the frequency and amplitude,the control of the buttons and display.The system has been tested to prove low energy consumption,cost-ef-fective and high practical value.Key words:signal capture and storage;signal reproduction;signal conditioning;playback system1引言很多工业现场中的电气设备在发生故障时,由于环境限制或是故障原因复杂,无法有效对系统故障进行在线的分析和判别,如果能够记录下故障设备产生的信号,再通过网络进行专家判别,将更利于系统的快速恢复与故障排除。

基于DSP的语音采集和回放系统的实现

基于DSP的语音采集和回放系统的实现王丽琴;史航【摘要】基于DSP的语音采集和回放系统,主要采用C语言进行软件编写,并在CCS环境下进行功能仿真,播放变换后语音,并给出了具体的实现方法和步骤。

实例表明,DSP满足双声道的语音信号处理的需要,具有广泛的应用价值。

【期刊名称】《时代农机》【年(卷),期】2015(000)010【总页数】2页(P57-58)【关键词】语音信号处理;DSP;语音采集和回放【作者】王丽琴;史航【作者单位】[1]常州信息职业技术学院,江苏常州213000;[2]江苏理工学院,江苏常州213000;【正文语种】中文【中图分类】TP391.42语音信号广泛存在于日常生活和工业生产过程中,具有信号频谱较全、采样速度较低、随机性强、应用场合多、实时性和稳定性等特点。

语音信号处理是一门重要的学科,在数字话音通信、声控打字机、自动语音翻译、多媒体信息处理等许多方面有重要的应用,如语音电子信箱、语音浏览、语音导航等。

随着数字信号处理算法在DSP中的实现,很多以前很难实现的语音信号处理算法都可以在DSP中实现。

1 数字信号处理器DSPDSP是数字信号处理器(Digital Signal Processing)或集成的单片数字信号处理器(Digital Signal Processor)的缩写。

DSP技术是利用计算机或专用处理设备,以数值计算的方法对信号进行采集、变换、综合、估值与识别等加工以达到提取信息和便于应用目的的一种技术。

DSP技术包括数字信号处理的理论和数字信号处理的实现。

DSP是数字信号处理系统的核心,一般由CPU、片内外设和存储空间构成。

TMS320VC5509 DSP芯片是目前集成度较高的通用型DSP,能提供完备的系统解决方案,具有96K×16位的单口 SRAM、32K×16位的双口 SRAM、32K×16位的ROM和6通道的DMA(直接存储器存储)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字信号采集回放系统电路设计

作者:李志海,潘红兵

来源:《科技传播》 2015年第19期

李志海,潘红兵

海军工程大学,湖北武汉 430032

摘要为了解决复杂数字电路板的故障诊断和维修测试问题,简化测试过程,本文设计了

一种能够进行数字信号采集和回放的系统电路。

本电路以FPGA 为核心,以NANDFLASH 芯片为

存储载体,可实现72 路数字信号采集和回放测试,支持软件操作和数据读写,为解决数字电

路板维修和现场测试不便所带来的问题,发现电路板故障,提供了新的方式或途径。

关键词数字信号测试采集回放;FPGA ;NAND-FLASH ;USB

中图分类号 TN79 文献标识码 A 文章编号 1674-6708(2015)148-0127-02

在数字电路测试技术中,基于电压测量的检测技术是多年来研究的重点。

该方法通过观察

正常电路和故障电路的输出响应来检测故障。

它主要是针对固定型故障的,改进后的电压测试

方法也可以用于检测延时故障。

该方法的优点是测试速度快,识别高低电平的精度要求不高[1]。

在电压测量技术中,还有很多基于运算的测量方法[2]。

但是,由于需要对电路做出较多的运算分析或仿真,随着电路信号数量不断增多,这种方法的便捷性和易用性往往会受到限制。

本文基于电压测量技术,设计了一种能够进行数字信号采集和回放的系统电路。

本电路以FPGA 为核心,以NAND FLASH 芯片为存储载体,可实现72 路数字信号测试,并且每通道达到100Msps 的采集(回放)速度。

1 系统电路结构和功能设计

整个系统包含存储板、系统底板、USB2.0 接口控制板、回放驱动板、采集转接板等多个组成部分,能够实现72 路数字信号的同步采集和回放。

系统结构示意图如下。

所有板卡均插装在系统底板上,通过数据及控制总线相连。

系统中的存储板有9 块,每块

可存储8 路数字信号,可实现72 路信号的数据存储。

每块存储板上有8 片8GB FLASH 芯片。

系统总存储容量为576GB,按照100M 采样率,可采集或回放10 分钟以上,数据存取速度达

900MB/S。

在采集过程中,被测数字信号通过采集转接板转移到存储板;在回放过程中,存储板中的数据首先通过回放驱动板输出到被测数字电路。

1.1 FLASH 存储板设计

每块存储板上集成了8 片NAND FLASH 芯片,分别存储8 路数字信号,并通过FPGA 芯片实现接口控制和数据存取。

器件选型方面,采用了K9HCG08U1M 型号的NANDFLASH,该芯片支持最高40MB/S 的瞬间数据存取速率,容量8GB。

FPGA 方面采用了ALTERA 公司CYCLONE 3 系列芯片,型号为EP3C25Q240C8N. 该芯片有149 个可分配IO 引脚,内部RAM 资源达608256bits,含4 个锁相环,完全满足本设计需求[4]。

存储板通过VME32 插头与底板数据总线连接,插头内包含了采集、擦除、回放等控制线和8 路数字信号线。

1.2 系统底板设计

系统底板是其它板卡互连的基础,还提供电源转换、插板接口、开关控制和指示、系统时钟选择等功能。

电源转换芯片组位于底板上侧,便于散热。

提供系统电源。

中间部分是9 块FLASH 存储卡的VME 插座位,底端是数据总线接口,用于与USB 控制板和回放驱动板等进行连接。

右侧是开关控制电路和晶振电路。

开关控制电路主要负责对来自USB 控制板的开关信号进行处理,并通过指示灯加以显示。

晶振电路则可提供25MHz 和6.25MHz两种时钟,并在FPGA 内部进行4 倍频处理。

在高速采集回放过程中,使用25MHz 时钟,可达到100MSPS 的采样率和同等回放速率。

1.3 USB 接口控制板设计

USB 接口控制板主要负责系统设备与上位机之间的数据交换,包括控制命令和采集回放数据的读写操作。

电路板的接口主要有USB2.0 接口,数据及控制总线接口,回放引脚设置总线接口。

本设计中,采用了CYPRESS 公司的USB2.0 芯片CY7C68013-128AC 作为USB 接口芯片。

该芯片最高数据速率可达48MB/S。

1.4 采集转接板设计

它的功能是将被测数字电路板转接出来,使之保持正常工作,并对其引脚信号加强驱动,以便本系统设备进行采集。

采集时,将转接口连接到待测设备的数字电路板所在位置,然后将数字电路板插在采集转接板中间的接口上,并使用排线与本系统面板的采集接口相连。

此时启动待测设备,在其进入工作状态时启动采集。

1.5 回放驱动板设计

由于FLASH 存储卡的驱动能力较弱且没有信号方向选择,所以在回放时,必须经过驱动增强和引脚输入输出的方向选择,才能使被测数字电路板正常工作起来。

本设计采用“FPGA+ 三态门”的方式,实现回放信号引脚方向选择和驱动。

USB Local Bus 通过FPGA 进行命令的接收和译码,并产生三态门控制信号。

底板总线接

口提供所有72 路数字信号,经过三态门电路选择后,产生相应的驱动信号给被测数字电路板。

2 上位机软件设计

上位机软件主要负责USB 驱动程序的调用、通信协议的实现。

系统电路的各种操作均可通

过上位机软件完成。

其通信协议包括命令设置、数据帧的收发、返回状态判断等等。

软件通过

协议控制进行采集和回放测试、数据的导入导出操作。

“触发采集”用于设置触发采集模式下

的参数。

3 系统测试

为了验证本系统设备的各项性能,针对某型72 脚数字电路板进行了现场采集。

该型电路

板的72 路信号除电源和地以外,均为数字信号,且最高工作频率为3MHz。

在采集过程中,观察被测设备和电路板是否仍能正常工作。

采集结果表明,被测设备工作

不受影响,本系统工作正常,故障灯未亮,可完成10 分钟的采集过程。

在采集结束后,进行

了回放测试,使用示波器对回放驱动板的信号进行了波形测试。

测试结果表明,回放接口能够

完整再现采集到的数字信号。

各通道回放信号之间的误差不超过10ns。

4 结论

目前市面上已有的数字信号测量工具,受限于采集速度、存储深度、可测通道数、现场易

用性、信号复现等诸多因素;另一方面,某些数字电路的维修不只是要做简单的波形测量,还

需要进行信号激励和驱动,并观察响应,以确认电路的工作是否正常。

本文设计的系统电路以FPGA 和FLASH 为核心,可以完成信号记录和回放的功能,能够对数字信号较多的电路板维修

和故障定位发挥极大的辅助作用,也为数字信号测试技术提供了一种新的方式方法。

参考文献

[1]胡敏明.几种典型的数字电路测试技术[J].管理科学,2009.

[2]杨士充.数字系统的故障诊断与可靠性设计[M].北京:清华大学出版社,2000.。