FPGA数字跑表程序

基于FPGA的数字跑表功能的数字钟设计

摘要近年来,科学技术发展飞速,人们的生活质量也不断提高。

传统的时钟已经无法满足现代人的生活要求。

多功能数字钟无论在形态还是在性能上都改变了原有的风格。

本次设计基于原始的数字钟,在此基础上增加了诸项功能。

不仅具备时,分,秒计数功能,另外增加了校时功能,整点报时功能,闹钟功能以及数字跑表功能。

设计中采用了EDA技术,使用硬件描述语言Verilog HDL对各大功能模块的逻辑功能进行代码编写。

于QuartusII软件环境下,采用层次化设计与模块化设计的方法,由各个功能模块连接建立顶层图,构成基于FPGA的多功能数字钟。

设计实验板的主芯片为EP3C25Q240C8,多功能数字钟由分频器模块,时钟计数模块,校时控制模块,闹钟模块,整点报时与音乐演奏模块,数据选择模块,译码显示模块,按键去抖动模块和数字跑表模块构成。

经过程序编译和模块仿真,在实验板上下载验证,该系统可以完成时,分,秒的正常显示,通过按键切换功能模式,进入闹钟时间设定,校时,数字跑表模式。

可以手动调整时间,设定闹钟及数字跑表计时。

关键词:FPGA;Verilog HDL;数字钟;THE DIGITAL CLOCK WITH STOPWATCH FUCTIONABSTRACTIn recent years, the rapid development of science technology, quality of life is also rising. Traditional clock has been unable to meet the requirements of modern life. Both in the form of multi-function digital clock or in the performance has changed the original style.The design is based on the original digital clock, on the basis of it increased various functions. Not only have the time, minutes, seconds count function, also add the function of adjusting time, the whole point timekeeping function, alarm function and digital stopwatch functions. EDA technology used in the design, using Verilog HDL hardware description language for logic functions in major functional modules of code to write. Under Quartus II software environment, using hierarchical design methods and modular design, the top chart established by the various functional modules connecting each other, constitute FPGA-based multifunctional digital clock.The main system chip of design experiment board is EP3C25Q240C8, multifunctional digital clock is composed of the divider module, the clock counting module, the adjust time control module, the alarm module, the whole point timekeeping and music module, the data selection module, the decoding module, the key to jitter module and digital stopwatch module. After the program compiled and module simulation, download on the breadboard validation, The system can complete hours, minutes, seconds display properly, through the key switch function mode, enter the alarm time setting, adjustment time, digital stopwatch mode. You can adjust the time manually, set the alarm and digital stopwatch timer.Keywords:FPGA;Verilog HDL;Digital clock;目录摘要 (i)ABSTRACT ............................................................... i i 第一章绪论 . (1)1.1 基于FPGA数字钟的背景和意义 (1)1.2 课题的研究方法和相关技术的发展 (1)1.3 本文的研究目的和主要研究内容 (2)第二章 FPGA简介 (3)2.1 FPGA的原理与基本结构 (3)2.2 FPGA设计流程 (3)第三章 Quartus II 简介 (4)第四章数字钟总体设计方案 (5)4.1数字钟的基本构成 (5)4.2数字钟的工作原理 (5)第五章数字钟的具体设计流程 (6)5.1 本设计的顶层图 (6)5.2 分频模块 (6)5.3 按键去抖动模块 (7)5.4 时钟模块 (8)5.4.1 模式切换功能 (9)5.4.2 时钟计数功能 (9)5.4.3 校时控制功能 (10)5.4.4 闹钟设定功能 (10)5.4.5 数字跑表功能 (11)5.5 数据选择模块 (11)5.6 译码显示模块 (13)5.7 闹钟音乐模块 (14)5.8 整点报时与音乐演奏模块 (15)结束语 (17)致谢 (18)参考文献 (19)附录A FPGA器件EP3C25_V5电路板 (21)附录B 本设计使用的EP3C25_V5管脚配置文件 (22)程序源代码 (23)第一章绪论1.1 基于FPGA数字钟的背景和意义现今的电子产品要求功能要多样,体积越小越好,且功耗应达到最低[1]。

fpga跑表课程设计

fpga跑表课程设计一、课程目标知识目标:1. 理解FPGA的基本原理,掌握跑表设计的基础知识;2. 学会使用硬件描述语言(如VHDL/Verilog)进行FPGA设计;3. 掌握跑表设计的时序逻辑和组合逻辑,并能够运用到实际设计中;4. 了解FPGA设计中时钟信号的重要性,学会合理分配时钟资源。

技能目标:1. 能够运用所学知识,独立完成FPGA跑表的设计与仿真;2. 培养学生的实际操作能力,提高问题分析和解决能力;3. 学会使用相关软件工具(如Quartus、Vivado等)进行FPGA设计;4. 培养学生的团队协作能力,提高项目完成效率。

情感态度价值观目标:1. 培养学生对电子设计及FPGA技术的兴趣,激发创新意识;2. 培养学生严谨、认真的学习态度,养成良好的学术道德;3. 引导学生关注社会发展,认识到FPGA技术在现代科技中的重要性;4. 培养学生克服困难的意志,提高面对挑战的自信心。

本课程针对高年级学生,结合学科特点,注重理论与实践相结合。

通过本课程的学习,使学生能够掌握FPGA跑表设计的核心知识,提高实际操作能力,培养学生的创新意识和团队协作精神,为今后从事相关领域工作打下坚实基础。

二、教学内容1. FPGA基础知识:- FPGA原理与结构;- 硬件描述语言基础(VHDL/Verilog);- 常用FPGA开发工具介绍。

2. 跑表设计原理:- 跑表功能需求分析;- 时序逻辑与组合逻辑设计;- 时钟信号分配与设计。

3. FPGA跑表设计实践:- 设计流程与方法;- 代码编写与仿真;- FPGA配置与测试。

4. 教学大纲安排:- 第一周:FPGA原理与硬件描述语言基础;- 第二周:跑表设计原理与时序逻辑设计;- 第三周:组合逻辑设计及时钟信号分配;- 第四周:FPGA跑表设计实践与项目指导;- 第五周:项目验收与评价。

教学内容关联教材章节:- 第一章:FPGA原理与结构;- 第二章:硬件描述语言基础;- 第三章:数字电路设计;- 第四章:FPGA设计实例。

FPGA LCD1602 时钟 跑表

en_sel <= 1'b1;

count<=0;

end

else

case(state)

clear_lcd:

end

always @(posedge clk_LCD,negedge rst)//initial

begin

if(!rst)

begin

state <= clear_lcd;

RS <= 0;

write_data=4, //and one

write_data_first= 5; //write data

assign RW = 0; //write

assign lcd_e = en_sel ? clk_LCD : 0;

reg [7:0] data_in [4:0];

always @(posedge clk)

if(mode==1)

begin

data_in[0]<=8'ha0;

data_in[1]<=8'ha0;

data_in[2]<=8'ha0;

module lcd_1602(clk,rst,mode,add,RS,lcd_e,data);

input clk, rst, mode, add;

output RS,lcd_e;

output [7:0] data ;

wire clk_LCD, clk1hz, clk1khz,clk100hz;

input [3:0] h1,h2,m1,m2;

input [2:0] modecount;

output reg RS;

基于FPGA的数字跑表设计报告

基于FPGA的数字跑表设计报告姓名:学号:指导老师:***摘要:本文详细介绍了数字秒表的设计指标,设计思路,设计方案,系统电路设计,系统单元模块设计,系统硬件实现与测试的结果。

一 引言 科技高度发展的今天,集成电路和计算机应用得到了高速发展。

尤其是计算机应用的发展。

它在人们日常生活已逐渐崭露头角。

大多数电子产品多是由计算机电路组成,如:手机、mp3等。

而且将来的不久他们的身影将会更频繁的出现在我们身边。

各种家用电器多会实现微电脑技术。

电脑各部分在工作时多是一时间为基准的。

本文就是基于计算机电路的时钟脉冲信号、状态控制等原理设计出的数字秒表。

秒表在很多领域充当一个重要的角色。

在各种比赛中对秒表的精确度要求很高,尤其是一些科学实验。

他们对时间精确度达到了几纳秒级别。

二 项目任务与设计思路 本项目的任务是掌握使用VHDL 语言的设计思想;熟悉ise 软件的使用;了解XILINX 学生EDA 实验板。

了解 EDA 技术,对计算机系统中时钟控制系统进一步了解,掌握状态机工作原理,同时了解计算机时钟脉冲是怎么产生和工作的。

在掌握所学的计算机组成与结构课程理论知识时。

通过对数字秒表的设计,进行理论与实际的结合,提高与计算机有关设计能力,提高分析、解决 计算机技术实际问题的能力。

通过课程设计深入理解计算机结构与控制实现的技术,达到课程设计的目标。

项目任务与设计思路本项目的指标:1、跑表精度为0.01秒2、跑表计时范围为:1小时3、设置开始计时/停止计时、复位两个按钮4、显示工作方式:用六位BCD 七段数码管显示读数。

显示格式:三 基于VHDL 方法设计方案 VHDL 的设计流程主要包括以下几个步骤:1.文本编辑:用任何文本编辑器都可以进行,也可以用专用的HDL 编辑环境。

通常VHDL 文件保存为.vhd文件2.功能仿真:将文件调入HDL 仿真软件进行功能仿真,检查逻辑功能是否正确。

3.逻辑综合:将源文件调入逻辑综合软件进行综合,即把语言综合成最简的布尔表达式。

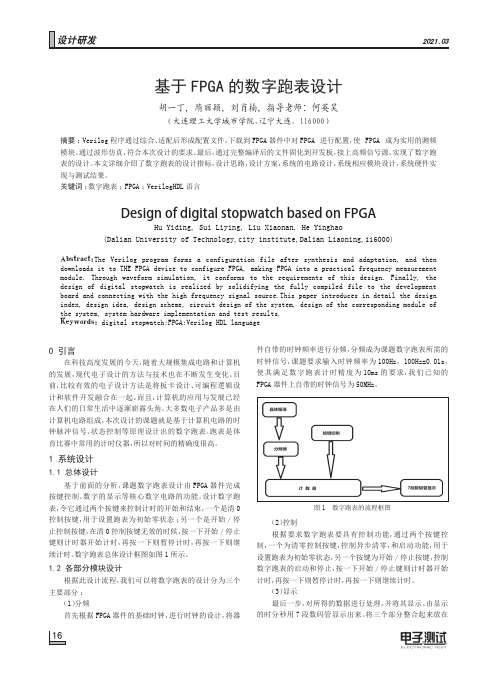

基于FPGA的数字跑表设计

0 引言在科技高度发展的今天,随着大规模集成电路和计算机的发展,现代电子设计的方法与技术也在不断发生变化。

目前,比较有效的电子设计方法是将板卡设计、可编程逻辑设计和软件开发融合在一起。

而且,计算机的应用与发展已经在人们的日常生活中逐渐崭露头角。

大多数电子产品多是由计算机电路组成,本次设计的课题就是基于计算机电路的时钟脉冲信号、状态控制等原理设计出的数字跑表。

跑表是体育比赛中常用的计时仪器,所以对时间的精确度很高。

1 系统设计1.1 总体设计基于前面的分析,课题数字跑表设计由FPGA器件完成按键控制、数字的显示等核心数字电路的功能。

设计数字跑表,令它通过两个按键来控制计时的开始和结束,一个是清0控制按键,用于设置跑表为初始零状态;另一个是开始/停止控制按键,在清0控制按键无效的时候,按一下开始/停止键则计时器开始计时,再按一下则暂停计时,再按一下则继续计时。

数字跑表总体设计框图如图1所示。

1.2 各部分模块设计根据此设计流程,我们可以将数字跑表的设计分为三个主要部分:(1)分频首先根据FPGA器件的基础时钟,进行时钟的设计,将器件自带的时钟频率进行分频,分频成为课题数字跑表所需的时钟信号,课题要求输入时钟频率为100Hz,100Hz=0.01s,使其满足数字跑表计时精度为10ms的要求,我们已知的FPGA器件上自带的时钟信号为50MHz。

图1 数字跑表的流程框图(2)控制根据要求数字跑表要具有控制功能,通过两个按键控制,一个为清零控制按键,控制异步清零,和启动功能,用于设置跑表为初始零状态,另一个按键为开始/停止按键,控制数字跑表的启动和停止,按一下开始/停止键则计时器开始计时,再按一下则暂停计时,再按一下则继续计时。

(3)显示最后一步,对所得的数据进行处理,并将其显示。

由显示的时分秒用7段数码管显示出来。

将三个部分整合起来放在index, design idea, design scheme, circuit design of the system, design of the corresponding module of the system, system hardware implementation and test results.Keywords: digital stopwatch;FPGA;Verilog HDL language始/暂停按键)输出信号:MSH,MSL,SH,SL,MH,ML(7段数码管)分频部分器件图如图4所示。

(完整版)基于FPGA的数字跑表设计毕业设计

本科毕业论文基于FPGA的数字跑表设计Digital stopwatch design based on FPGA学院名称:电子信息与电气工程学院专业班级:电子信息工程(专升本)2013级2015年5月毕业设计(论文)原创性声明和使用授权说明原创性声明本人郑重承诺:所呈交的毕业设计(论文),是我个人在指导教师的指导下进行的研究工作及取得的成果。

尽我所知,除文中特别加以标注和致谢的地方外,不包含其他人或组织已经发表或公布过的研究成果,也不包含我为获得安阳工学院及其它教育机构的学位或学历而使用过的材料。

对本研究提供过帮助和做出过贡献的个人或集体,均已在文中作了明确的说明并表示了谢意。

作者签名:日期:指导教师签名:日期:使用授权说明本人完全了解安阳工学院关于收集、保存、使用毕业设计(论文)的规定,即:按照学校要求提交毕业设计(论文)的印刷本和电子版本;学校有权保存毕业设计(论文)的印刷本和电子版,并提供目录检索与阅览服务;学校可以采用影印、缩印、数字化或其它复制手段保存论文;在不以赢利为目的前提下,学校可以公布论文的部分或全部内容。

作者签名:日期:目录摘要...................................................... Abstract ....................................................引言......................................................第一章绪论................................................1.1 设计背景与意义................................................1.2 跑表的发展趋势................................................第二章实验的软件环境.......................................2.1 MAX+plusⅡ软件................................................2.2 VHDL语言......................................................第三章跑表的设计...........................................3.1跑表的方案选择.................................................3.2跑表的程序流程图 ...............................................3.3顶层设计与VHDL源代码 ..........................................3.3.1顶层实体设计及VHDL源代码 ....................................3.3.2顶层结构体的设计 .............................................3.4跑表的各个模块分析 .............................................3.4.1键输入模块...................................................3.4.2时钟分频模块.................................................3.4.3控制模块.....................................................3.4.4跑表计时模块.................................................3.4.5跑表显示模块.................................................3.5仿真结果.......................................................结语.......................................................致谢.......................................................参考文献....................................................附录A 管脚引用表............................................附录B 跑表的程序代码........................................基于FPGA的数字跑表设计摘要:本数字跑表用于检测需要准确计时或计时场合较为精确且比较精密的环境中。

基于FPGA的数字跑表设计

摘要:本设计以Xilinx公司的XC3S200A芯片为核心,通过VHDL语言进行编程实现。

在48MHz时钟源输入下,通过分频、计数实现精度为百分之一秒的计时,最终用六位LED数码管显示,并可以通过两个按键控制跑表的复位、停止和启动。

一.引言大多数数字系统使用了两种不同的设计方法。

从硬件的角度来看,发展的动力是提高性能:更快、更小、功耗更低、价格更便宜。

这种方式需要巨额的费用,花费的时间也很长。

但是,从软件的角度看,更倾向于使用一个标准的处理器架构,这样只要开发出应用软件然后下载到这些平台即可。

但是由于对操作系统的需求、编译器的低效率等原因,也会造成大的开销。

结果,作为一种折中的方式,可编程器件就被开发出来了。

它拥有众多的优点:在高性能的平台上进行硬件设计,拥有最优化的资源,不需要操作系统,可重新配置等。

现场可编程门阵列(Field Programmable Gate Array,FPGA)是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物,不但有较高的性能,同时又具备可编程逻辑的灵活性和可重用性。

二.项目任务与设计思路跑表设计指标:1、跑表精度为0.01秒2、跑表计时范围为:1小时3、设置开始计时/停止计时、复位两个按钮4、显示工作方式:用六位BCD八段数码管显示读数。

显示格式:分秒0.01秒设计思路简述:1、按键:两个按键均采用边缘触发,其中复位键按下后将强制归零并屏蔽启停键作用,启停键每次生效将使计数器的开关状态翻转一次。

2、计数:由于原始时钟频率为48MHz,故先对源时钟进行480000进制计数,以产生间隔为1ms的进位信号,对该信号进行计数并进位,可得到百分秒的计数值,以此类推,可得到十分秒、秒、十秒、分、十分的计数值,需要注意的是,对十秒和十分的计数应是六进制的。

3、LED显示:由于LED采用动态显示,位选与段选使用同一个1KHz的时钟信号进行同步。

其中位选信号从低位到高位一次点亮各位数码管,当某位数码管被点亮时,相应的段选信号就会被送至数码管,控制其显示字符。

数字跑表实验设计

数字跑表 设计报告设计任务:在掌握了VHDL 硬件编程语言和了解了基本的FPGA 设计步骤后,设计出一个符合设计指标的数字跑表,并下载到实验板上通过验证。

设计指标:1、跑表精度为0.01秒2、跑表计时范围为:1小时3、设置开始计时/停止计时、复位两个按钮4、显示工作方式:用六位BCD 七段数码管显示读数。

显示格式:设计步骤:(1) 设计出符合设计要求的解决方案。

(2) 设计出单元电路。

(3) 利用EDA 软件对各单元电路及整体电路进行仿真。

(4) 利用EDA 软件在ELB 电子课程设计实验箱上实现设计。

(5) 撰写设计报告。

设计思路:首先,分析一个完整的数字跑表的具有哪些功能:1、计时功能 2、相应的控制按钮 3、显示计数结果的功能模块;接下来就开始考虑如何应用电路实现上述的三个模块: 1、计时模块应包括稳定、准确的时钟输入和计数模块,考虑到设计指标要求跑表精度为0.01秒,那么计数脉冲的时钟输入就应该是频率为100HZ 的脉冲,而实验板上提供的晶振是32MHZ ,所以先要设计一个320000分频器,分频器的输出才可作计数器的输入;其次计数模块设计应综合考虑跑表的计时范围(1小时)和显示输出(6位输出),6位输出中有两位是六进制输出,其余四位是十进制输出,所以可通过设计4个模10计数器和2个模6分 秒 0.01秒计数器来实现,其中较低位的进位输出就是高位的计数输入端。

2、根据设计指标的要求,控制模块应包括开始计时/停止计时、复位两个按钮,即电路设计经常用到的史能端和清零端,这两个控制端口直接接到计数器的清零和史能端即可实现、复位、开始计时/停止计时;但是外围史能输入需要经过史能转换电路后,才可变为计数器可用的史能控制信号。

3、显示计数结果的模块实现较为简单,只需将六位计数结果通过七段译码电路接到输出即可点亮数码管,无需时序控制,直接用组合逻辑电路就可以实现。

数码管显示可以采用扫描显示,用一个频率1KHz的信号扫描一个多路选择器,实现对六位已经锁存的计数结果的扫描输出。

FPGA数字跑表

电子信息工程专业FPGA与ASIC设计实践教程设计报告班级:电子信息工程1303班学号:201315110: 田佳鑫日期:2015年11月4日指导老师:何英昊目录1系统总体方案及硬件设计 (3)1.1设计容 (3)1.2 设计要求 (3)1.3 实现要求 (3)2各模块设计及电路图 (3)2.1设计项目简介 (3)2.2分块设计代码 (4)2.3总体框图设计 (7)2.4管脚锁定图 (8)3课程设计体会 (8)1系统总体方案及硬件设计1.1 设计容数字跑表电路1.2设计要求(1)跑表的计时围为0.01—59min59.99s。

(2)具有异步清零、启动。

计时和暂停功能。

(3)输入时钟频率为100Hz。

(4)要求数字跑表的输出能够直接驱动共阴极7段数码管。

1.3 实现要求(1)分析功能要求,划分功能模块。

(2)编写各模块的Verilog HDL语言设计程序。

(3)在QuartusⅡ软件或其他EDA软件上完成设计和仿真。

(4)根据实验装置上的CPLD/FPGA芯片,在适配时选择相应的芯片,将设计生成配置文件或JEDEC文件,然后将配置文件或JEDEC文件下载到实验装置上运行,操作实验装置上设定的功能开关,验证设计功能。

2各模块设计及电路图2.1 设计项目简介主控模块分别连接6个数码管显示模块和分频模块,分频模块给主控模块的计数器提供时钟源,主控模块在按键的控制下,在其中计数器的作用下输出给数码管显示装置,实现跑表功能。

2.2分块设计代码(1)分频模块:module fenpin(CLK,CLK2);//输入50MHz,输出分频到1Hzinput CLK;output CLK2;reg CLK2;reg[31:0] counter2;parameter N2=5000000; always(posedge CLK)beginif(counter2==250000)begincounter2<=0;CLK2<=~CLK2;endelsecounter2<=counter2+1;endendmodule(2)控制模块:module sz(clk,clr,pause,msh,msl,sh,sl,mh,ml); inputclk,clr;input pause;output[3:0]msh,msl,sh,sl,mh,ml;reg[3:0]msh,msl,sh,sl,mh,ml;reg1,2;always(posedgeclk or posedgeclr)beginif(clr)begin{msh,msl}<=8'h00;1<=0;endelseif(!pause)beginif(msl==9)beginmsl<=0;if(msh==9)beginmsh<=0;1<=1;endelsemsh<=msh+1;endelsebeginmsl<=msl+1;1<=0;endendalways(posedge1 or posedgeclr) beginif(clr)begin{sh,sl}<=8'h00;2<=0;endelseif(sl==9)beginsl<=0;if(sh==5)beginsh<=0;2<=1;endelsesh<=sh+1;endelsebeginsl<=sl+1;2<=0;endendalways(posedge2 or posedgeclr) beginif(clr)begin{mh,ml}<=8'h00;endelseif(ml==9)beginml<=0;if(mh==5)mh<=0;elsemh<=mh+1;endml<=ml+1;endendmodule(3)显示模块:module XS7D(DIN,DOUT);input [3:0]DIN;output [6:0]DOUT;reg [6:0]DOUT;always (DIN)begincase(DIN) 0:DOUT='b1000000;1:DOUT='b1111001;2:DOUT='b0100100;3:DOUT='b0110000;4:DOUT='b0011001;5:DOUT='b0010010;6:DOUT='b0000010;7:DOUT='b1111000;8:DOUT='b0000000;9:DOUT='b0010000; 10:DOUT='b0001000; 11:DOUT='b0000011; 12:DOUT='b1000110; 13:DOUT='b0100001; 14:DOUT='b0000110; 15:DOUT='b0001110; endcaseendendmodule2.3总体框图设计2.4管脚锁定图三、课程设计体会习制作数字跑表,我对于可编程逻辑器件有了更加深刻地体会。

数字跑表

自己做的简易数字跑表,基于de2的fpga的验证,有复位,暂停功能。

自己测试过了,成功。

只是这个算法很简单,就是一步步写的verilog语言。

现在正在设计另一种算法。

module paobiao1(CLK,CLR,PAUSE,HEX0,HEX1,HEX2,HEX3,HEX4,HEX5,HEX6,HEX7); input CLK,CLR,PAUSE;output[6:0]HEX0,HEX1,HEX2,HEX3,HEX4,HEX5,HEX6,HEX7;reg[6:0]HEX0,HEX1,HEX2,HEX3,HEX4,HEX5,HEX6,HEX7;reg[3:0] MSH,MSL,SH,SL,MH,ML,H,L;reg[18:0]count;reg [3:0]cn1,cn2,cn3;always @(posedge CLK )begincount=count+1'b1;if(count==19'd250000)beginif(CLR)begin{MSH,MSL}=8'h00;cn1=0;HEX1=7'b1000000;HEX0=7'b1000000;endelseif(!PAUSE)beginif(MSL==4'ha)beginMSH=MSH+4'h1;MSL=4'h0;case(MSH)4'h0:HEX1=7'b1000000;4'h1:HEX1=7'b1111001;4'h2:HEX1=7'b0100100;4'h3:HEX1=7'b0110000;4'h4:HEX1=7'b0011001;4'h5:HEX1=7'b0010010;4'h6:HEX1=7'b0000010;4'h7:HEX1=7'b1111000;4'h8:HEX1=7'b0000000;4'h9:HEX1=7'b0010000;4'ha:HEX1=7'b1000000;endcaseif(MSH==4'ha)beginMSH=4'h0;cn1=1;endendelsebeginMSL=MSL+1; cn1=0;case(MSL)4'h0:HEX0=7'b1000000;4'h1:HEX0=7'b1111001;4'h2:HEX0=7'b0100100;4'h3:HEX0=7'b0110000;4'h4:HEX0=7'b0011001;4'h5:HEX0=7'b0010010;4'h6:HEX0=7'b0000010;4'h7:HEX0=7'b1111000;4'h8:HEX0=7'b0000000;4'h9:HEX0=7'b0010000;4'ha:HEX0=7'b1000000;endcaseendendendendalways @(posedge cn1 or posedge CLR)beginif(CLR)begin{SH,SL}=8'h00;cn2=0;HEX2=7'b1000000;HEX3=7'b1000000;endelseif(!PAUSE)beginif(SL==4'h9)beginSH=SH+4'h1; SL=4'h0;case(SL)4'h0:HEX2=7'b1000000;endcasecase(SH)4'h0:HEX3=7'b1000000;4'h1:HEX3=7'b1111001;4'h2:HEX3=7'b0100100;4'h3:HEX3=7'b0110000;4'h4:HEX3=7'b0011001;4'h5:HEX3=7'b0010010;4'h6:HEX3=7'b1000000;endcaseif(SH==4'h6)begin SH=4'h0; cn2=1; endendelsebegin SL=SL+1; cn2=0;case(SL)4'h0:HEX2=7'b1000000;4'h1:HEX2=7'b1111001;4'h2:HEX2=7'b0100100;4'h3:HEX2=7'b0110000;4'h4:HEX2=7'b0011001;4'h5:HEX2=7'b0010010;4'h6:HEX2=7'b0000010;4'h7:HEX2=7'b1111000;4'h8:HEX2=7'b0000000;4'h9:HEX2=7'b0010000;4'ha:HEX2=7'b1000000;endcaseendendendalways @( posedge cn2 or posedge CLR)beginif(CLR)begin{MH,ML}=8'h00;cn3=0;HEX4=7'b1000000;HEX5=7'b1000000;endelseif(!PAUSE)beginif(ML==4'h9)beginMH=MH+1; ML=4'h0;case(ML)4'h0:HEX4=7'b1000000;endcasecase(MH)4'h0:HEX5=7'b1000000;4'h1:HEX5=7'b1111001;4'h2:HEX5=7'b0100100;4'h3:HEX5=7'b0110000;4'h4:HEX5=7'b0011001;4'h5:HEX5=7'b0010010;4'h6:HEX5=7'b1000000;endcaseif(MH==4'h6)begin MH=4'h0; cn3=1; endendelsebegin ML=ML+1; cn3=0;case(ML)4'h0:HEX4=7'b1000000;4'h1:HEX4=7'b1111001;4'h2:HEX4=7'b0100100;4'h3:HEX4=7'b0110000;4'h4:HEX4=7'b0011001;4'h5:HEX4=7'b0010010;4'h6:HEX4=7'b0000010;4'h7:HEX4=7'b1111000;4'h8:HEX4=7'b0000000;4'h9:HEX4=7'b0010000;4'ha:HEX4=7'b1000000;endcaseendendendalways @( posedge cn3 or posedge CLR ) beginif(CLR)begin{H,L}=8'h00;HEX6=7'b1000000;HEX7=7'b1000000;endelseif(!PAUSE)beginif(L==4'h9)beginH=H+1; L=4'h0;case(L)4'h0:HEX6=7'b1000000;endcasecase(H)4'h0:HEX7=7'b1000000;4'h1:HEX7=7'b1111001;4'h2:HEX7=7'b0100100;4'h3:HEX7=7'b0110000;4'h4:HEX7=7'b0011001;4'h5:HEX7=7'b0010010;4'h6:HEX7=7'b0000010;4'h7:HEX7=7'b1111000;4'h8:HEX7=7'b0000000;4'h9:HEX7=7'b0010000;4'ha:HEX7=7'b1000000;endcaseif(H==4'ha) H=4'h0 ;endelsebegin L=L+1;case(L)4'h0:HEX6=7'b1000000;4'h1:HEX6=7'b1111001;4'h2:HEX6=7'b0100100;4'h3:HEX6=7'b0110000;4'h4:HEX6=7'b0011001;4'h5:HEX6=7'b0010010;4'h6:HEX6=7'b0000010;4'h7:HEX6=7'b1111000;4'h8:HEX6=7'b0000000;4'h9:HEX6=7'b0010000;4'ha:HEX6=7'b1000000;endcaseendendendendmodule。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(1)跑表的计时范围为0.01s~59min59.99s,计时精度为10ms;(2)具有异步复位清零、启动、计时和暂停功能;(3)输入时钟频率为100Hz;(4) 要求数字跑表的输出能够直接驱动共阴极7段数码管显示/*信号定义CLK:时钟信号;CLR:异步复位信号;PAUSE:暂停/启动信号;MSH,MSL:百分秒的高位和低位;SH,SL:秒信号的高位和低位;MH,ML:分钟信号的高位和低位。

*/module h (clk,clr,pause,msh,msl,sh,sl,mh,ml,led1,led2,led3,led4,led5,led6);input clk,clr;input pause;output [6:0]led1;output [6:0]led2;output [6:0]led3;output [6:0]led4;output [6:0]led5;output [6:0]led6;output [3:0] msh,msl,sh,sl,mh,ml;reg [6:0]led1;reg [6:0]led2;reg [6:0]led3;reg [6:0]led4;reg [6:0]led5;reg [6:0]led6;reg[3:0] msh,msl,sh,sl,mh,ml;reg cn1,cn2; //cn1为百分秒向秒的进位,cn2为秒向分的进位//百分秒计数进程,每计满100,cn1产生一个进位1 always @(posedge clk or posedge clr)beginif(clr) //异步复位begin{msh,msl}<=8'h00; //从00开始计数cn1<=0;endelseif(!pause) //PAUSE为0时正常计数,为1时暂时计数beginif (msl==9)beginmsl<=0; //低位百分秒计数到10是归零if (msh==9)beginmsh<=0; //高位百分秒计数到10是归零cn1<=1; //CN1触发进位endelse //低位计数到10,高位未计数到10时,高位计数msh<=msh+1;endelsebegin //低位计数未到10时,继续计数msl<=msl+1;cn1<=0; //低位未计数到10时,CN1不产生进位endendend//秒计数模块,每计数满60,CN2产生一个进位always @(posedge cn1 or posedge clr)beginif (clr)begin //异步复位{sh,sl}<=8'h00;cn2<=0;endelseif(sl==9)beginsl<=0; //低位秒计数到10,低位归零if (sh==5)beginsh<=0; //低位计数到10,高位计数到6时,高位秒归零cn2<=1; //cn2触发进位endelsesh<=sh+1; //低位计数到10,高位未到6时,低位计数endelsebeginsl<=sl+1; //低位未计数到10,低位计数cn2<=0; //低位未计数到10时,CN2不产生进位endend//分钟计数模块,每计满60,系统自动清0always@ (posedge cn2 or posedge clr)beginif(clr)begin //异步复位{mh,ml}<=8'h00;endelseif(ml==9)beginml<=0; //低位分计数到10时,低位归零if (mh==5)mh<=0; //低位计数到10,高位计数到6时,高位归零elsemh<=mh+1; //低位计数到10,高位未计数到6时,高位计数endelseml<=ml+1; //低位计数未到10时,低位计数end//led显示模块always@(msl[3:0])begincase(msl[3:0]) //利用case语句控制显示低位百分秒的0~90:led1='b1000000;1:led1='b1111001;2:led1='b0100100;3:led1='b0110000;4:led1='b0011001;5:led1='b0010010;6:led1='b0000010;7:led1='b1111000;8:led1='b0000000;9:led1='b0010000;endcaseendalways@(msh[3:0])begincase(msh[3:0]) //利用case语句控制显示高位百分秒的0~90:led2='b1000000;1:led2='b1111001;2:led2='b0100100;3:led2='b0110000;4:led2='b0011001;6:led2='b0000010;7:led2='b1111000;8:led2='b0000000;9:led2='b0010000;endcaseendalways@(sl[3:0])begincase(sl[3:0]) //利用case语句控制显示低位秒的0~9 0:led3='b1000000;1:led3='b1111001;2:led3='b0100100;3:led3='b0110000;4:led3='b0011001;5:led3='b0010010;6:led3='b0000010;7:led3='b1111000;8:led3='b0000000;9:led3='b0010000;endcaseendalways@(sh[3:0])begincase(sh[3:0]) //利用case语句控制显示高位秒的0~5 0:led4='b1000000;1:led4='b1111001;2:led4='b0100100;3:led4='b0110000;4:led4='b0011001;5:led4='b0010010;endcaseendalways@(ml[3:0])begincase(ml[3:0]) //利用case语句控制显示低位分的0~9 0:led5='b1000000;1:led5='b1111001;2:led5='b0100100;3:led5='b0110000;4:led5='b0011001;5:led5='b0010010;6:led5='b0000010;7:led5='b1111000;9:led5='b0010000;endcaseendalways@(mh[3:0])begincase(mh[3:0]) //利用case语句控制显示高位分的0~5 0:led6='b1000000;1:led6='b1111001;2:led6='b0100100;3:led6='b0110000;4:led6='b0011001;5:led6='b0010010;endcaseendendmodulemodule led (ledin,ledout);//七段译码模块input[3:0] ledin;output[6:0] ledout;reg[6:0] ledout;always@(ledin) //case语句进行译码begin case(ledin) //分别对应数码管的a--g4'd0:ledout=7'b11000000;4'd1:ledout=7'b11111001;4'd2:ledout=7'b10100100;4'd3:ledout=7'b10110000;4'd4:ledout=7'b10011001;4'd5:ledout=7'b10010010;4'd6:ledout=7'b10000010;4'd7:ledout=7'b11111000;4'd8:ledout=7'b10000000;4'd9:ledout=7'b10010000;default:ledout=7'bx;endcaseendendmodule分频模块module clk(f50m,f100);input f50m;output f100;reg f100;reg [31:0]h;always@(posedge f50m)beginif(h==250000) //对计数器进行判断,确定f100信号是否反转beginh<=0; //不计数f100<=~f100;endelse //未计数到250000时,继续计数h<=h+1;endendmodule。