大规模数字集成电路习题解答

集成电路制造技术习题解答(第5单元)

复习题1. ULSI 对多层互连系统的要求?答:可从金属导电层和绝缘介质层的材料特性,工艺特性,以及互连延迟时间等多个方面来分析ULSI 对多层互连系统的要求:1、缩短互连线延迟时间,通常用电阻电容(RC )常数表征互连线延迟时间,有:ox m ox m t t l t wl wt l RC 2ρεερ=⋅= 其中,ρ为金属连线的电阻率;l 、w 、t m 分别为金属连线层的长度、宽度和厚度;为ε、t ox 分别为介质层的介电常数和厚度。

由公式式可知,金属导电层的电阻率越低,绝缘层的介电常数越小,互连线越短,互连线延迟时间也就短,电路速度也就越快。

2、金属导电材料的选取除了要求低电阻率之外,还应抗电迁移能力强,理化稳定性能、机械性能和电学性能在经过后续工艺及长时间工作之后保持不变,最好薄膜淀积和图形转移等加工工艺简单、且经济,制备的互连线台阶覆盖特性好、缺陷浓度低、薄膜应力小。

实际上完全满足上述要求的金属或金属性材料没有。

早期的ULSI 是采用铝及铝合金作为导电材料。

近年来随着工艺技术的发展,铜已成为金属导电材料的首选,在集成度更高的ULSI 中有取代铝及铝合金的趋势。

3、绝缘介质材料的选取除了要求介电常数低之外,还应击穿场强高、漏电流低、体电阻率和表面电阻率大(一般均应大于1015Ω·cm ),即电学性能好;不吸潮、对温度的承受能力在500℃以上、无挥发性残余物存在,即理化性能好;薄膜材料的应力低、与导电层的附着性好,即兼容性好;薄膜易制备、且缺陷密度低、易刻蚀、台阶覆盖特性好,即易于加工成型。

2. 简述多层互连工艺流程。

答:在互连工艺中,首先淀积介质层,通常是CVD-PSG ;接下来平坦化,即PSG 的热处理回流,以消除衬底表面因前面光刻等工艺造成的台阶;然后通过光刻形成接触孔和通孔;再进行金属化,如PVD-Al 填充接触孔和通孔,形成互连线;如果不是最后一层金属,继续进行下一层金属化的工艺流程,如果是最后一层金属,则积淀钝化层,通常是PECVD-Si 3N 4,互连工艺完成。

数字集成电路习题答案

W / L 1 根据VGS和VDS确定其处于线性、饱和还是截止状态,并求 I D

的值。

解: (1)nm os:

VGT VGS VT 0 2.5 0.43 2.07 VDS

nm os 处于饱和区 ,Vmin VGT 2.07

2 W V ' I D kn ( )(VGT Vmin min )(1 VDS ) L 2 2 2 . 07 115 (2.072 )(1 0.06 2.5) 2 283.3A

VT0(V)

NMOS PMOS 0.43 -0.4

(V0.5)

0.4 -0.4

VDSAT(V)

0.63 -1

k’(A/V2)

115×10-6 -30×10-6

(V-1)

0.06 -0.1

1.假设设计一个通用0.25m CMOS工艺的反相器,其中PMOS晶体管的 最小尺寸为(W=0.75m,L=0.25m,即W/L=0.75/0.25) , NMOS晶体管 的最小尺寸为(W=0.375m,L=0.25m,即W/L=0.375/0.25) 求出g,VIL,VIH,NML,NMH

( R1 R2 R5 )C5

DCLK 3 R1C1 R1C2 ( R1 R3 )C3 R1C4 R1C5

(b)

DCLK 1 R1C1 ( R1 R2 )C2 R1C3 ( R1 R2 R4 )C4 ( R1 R2 )C5

9 RC

DCLK 2 R1C1 ( R1 R2 )C2 R1C3 ( R1 R2 )C4

( R1 R2 R5 )C5 9 RC

DCLK 3 R1C1 R1C2 ( R1 R3 )C3 R1C4 R1C5

《超大规模集成电路设计》考试习题(含答案)完整版分析

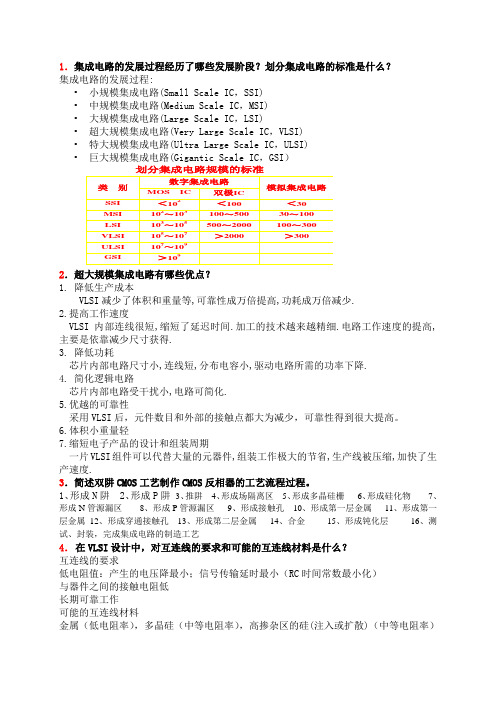

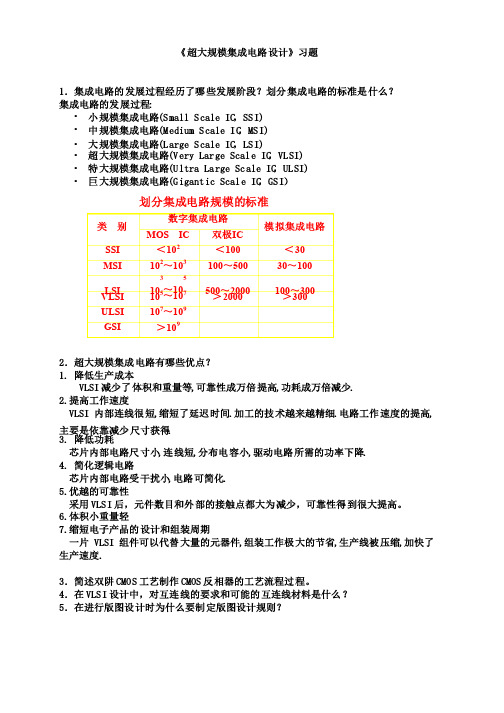

1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么?集成电路的发展过程:•小规模集成电路(Small Scale IC,SSI)•中规模集成电路(Medium Scale IC,MSI)•大规模集成电路(Large Scale IC,LSI)•超大规模集成电路(Very Large Scale IC,VLSI)•特大规模集成电路(Ultra Large Scale IC,ULSI)•巨大规模集成电路(Gigantic Scale IC,GSI)划分集成电路规模的标准2.超大规模集成电路有哪些优点?1. 降低生产成本VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少.2.提高工作速度VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得.3. 降低功耗芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降.4. 简化逻辑电路芯片内部电路受干扰小,电路可简化.5.优越的可靠性采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

6.体积小重量轻7.缩短电子产品的设计和组装周期一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。

1、形成N阱2、形成P阱3、推阱4、形成场隔离区5、形成多晶硅栅6、形成硅化物7、形成N管源漏区8、形成P管源漏区9、形成接触孔10、形成第一层金属11、形成第一层金属12、形成穿通接触孔13、形成第二层金属14、合金15、形成钝化层16、测试、封装,完成集成电路的制造工艺4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么?互连线的要求低电阻值:产生的电压降最小;信号传输延时最小(RC时间常数最小化)与器件之间的接触电阻低长期可靠工作可能的互连线材料金属(低电阻率),多晶硅(中等电阻率),高掺杂区的硅(注入或扩散)(中等电阻率)5.在进行版图设计时为什么要制定版图设计规则?—片集成电路上有成千上万个晶体管和电阻等元件以及大量的连线。

集成电路版图设计习题答案第二章集成电路制造工艺

集成电路版图设计习题答案第2章 集成电路制造工艺【习题答案】1.硅片制备主要包括(直拉法)、(磁控直拉法)和(悬浮区熔法)等三种方法。

2.简述外延工艺的用途。

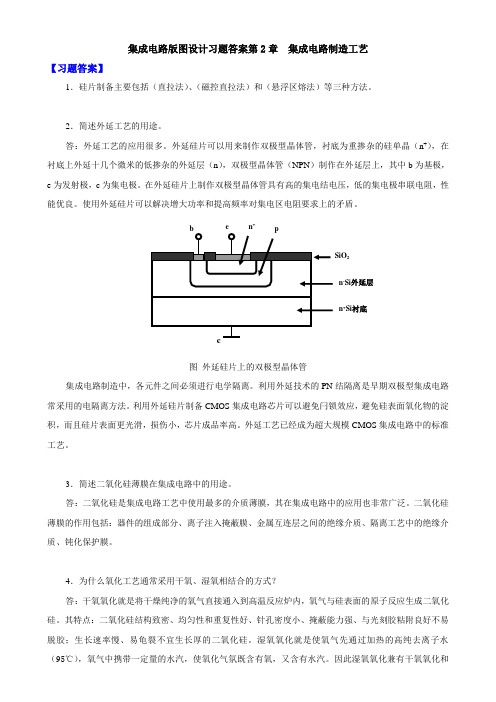

答:外延工艺的应用很多。

外延硅片可以用来制作双极型晶体管,衬底为重掺杂的硅单晶(n +),在衬底上外延十几个微米的低掺杂的外延层(n ),双极型晶体管(NPN )制作在外延层上,其中b 为基极,e 为发射极,c 为集电极。

在外延硅片上制作双极型晶体管具有高的集电结电压,低的集电极串联电阻,性能优良。

使用外延硅片可以解决增大功率和提高频率对集电区电阻要求上的矛盾。

图 外延硅片上的双极型晶体管集成电路制造中,各元件之间必须进行电学隔离。

利用外延技术的PN 结隔离是早期双极型集成电路常采用的电隔离方法。

利用外延硅片制备CMOS 集成电路芯片可以避免闩锁效应,避免硅表面氧化物的淀积,而且硅片表面更光滑,损伤小,芯片成品率高。

外延工艺已经成为超大规模CMOS 集成电路中的标准工艺。

3.简述二氧化硅薄膜在集成电路中的用途。

答:二氧化硅是集成电路工艺中使用最多的介质薄膜,其在集成电路中的应用也非常广泛。

二氧化硅薄膜的作用包括:器件的组成部分、离子注入掩蔽膜、金属互连层之间的绝缘介质、隔离工艺中的绝缘介质、钝化保护膜。

4.为什么氧化工艺通常采用干氧、湿氧相结合的方式?答:干氧氧化就是将干燥纯净的氧气直接通入到高温反应炉内,氧气与硅表面的原子反应生成二氧化硅。

其特点:二氧化硅结构致密、均匀性和重复性好、针孔密度小、掩蔽能力强、与光刻胶粘附良好不易脱胶;生长速率慢、易龟裂不宜生长厚的二氧化硅。

湿氧氧化就是使氧气先通过加热的高纯去离子水(95℃),氧气中携带一定量的水汽,使氧化气氛既含有氧,又含有水汽。

因此湿氧氧化兼有干氧氧化和en +SiO 2n -Si 外延层 n +Si 衬底水汽氧化的作用,氧化速率和二氧化硅质量介于二者之间。

实际热氧化工艺通常采用干、湿氧交替的方式进行。

数字集成电路习题

带入延迟公式可得,反相器链的延迟

t p N t p 0 (1

N

F

) 5 70 ps (1

5

2000 ) 1960 ps 2ns 1

c. 方法 a 的延迟时间

t p t p 0 (1

j 1

N

C g , j 1

C g , j

) t p 0 (1

解:VGS=VDS=2.5V,管子工作在饱和区。 栅沟电容 CGC=W*L*Cox=0.36um*0.24um*6fF/um2=0.52fF 栅与源漏区的交叠电容 Cov=CGSO=CGDO=W*Co=0.36um*0.31fF/um=0.11fF 栅电容 CG=CGC+2Cov=0.52 fF +2*0.11 fF=0.74fF 栅源电容 CGS=2CGC/3+Cov=2*0.52fF/3+0.11=0.46fF 栅漏电容 CGD=Cov=0.11fF 管子的源区和衬底都接地,所以源衬底扩散结处于零偏状态。有 Cs,bottom=W*LD*Cj0=0.36um*0.625um*2fF/um2=0.45fF Cs,sw=(W+2LD)*Cjsw0=(0.36um+2*0.625um)*0.28um/fF=0.45fF CSB= Cs,bottom + Cs,sw =0.45fF+0.45fF=0.9fF 管子的漏区接 2.5V,衬底接地,所以漏衬底扩散结处于反偏状态。有 CD,bottom=W*LD*Cj0/(1-VD/φ b)mj =0.36um*0.625um*2(fF/um2)/[1-(-2.5V)/0.9V]0.5 =0.23fF CD,sw=(W+2LD)*Cjsw0/(1-VD/φ bsw)mjsw =(0.36um+2*0.625um)*0.28(um/fF)/[1-(-2.5V)/0.9]0.44 =0.25fF CDB= CD,bottom + CD,sw =0.23fF+0.25fF=0.48fF

《超大规模集成电路设计》习题(含答案)

《超大规模集成电路设计》习题1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么?集成电路的发展过程:•小规模集成电路(Small Scale IC ,SSI)•中规模集成电路(Medium Scale IC ,MSI)•大规模集成电路(Large Scale IC ,LSI) •超大规模集成电路(Very Large Scale IC ,VLSI)•特大规模集成电路(Ultra Large Scale IC ,ULSI)•巨大规模集成电路(Gigantic Scale IC ,GSI )2.超大规模集成电路有哪些优点?1. 降低生产成本VLSI 减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少.2.提高工作速度VLSI 内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得. 3. 降低功耗芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降.4. 简化逻辑电路芯片内部电路受干扰小,电路可简化.5.优越的可靠性采用VLSI 后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

6.体积小重量轻7.缩短电子产品的设计和组装周期一片VLSI 组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.3.简述双阱CMOS 工艺制作CMOS 反相器的工艺流程过程。

4.在VLSI 设计中,对互连线的要求和可能的互连线材料是什么?5.在进行版图设计时为什么要制定版图设计规则?划分集成电路规模的标准数字集成电路类别MOS IC 双极IC 模拟集成电路SSI <102<100 <30 MSI 102~103100~500 30~100 LSI 103~105500~2000 100~300 VLSI 105~107>2000 >300 ULSI 107~109GSI >109在芯片尺寸尽可能小的前提下,使得即使存在工艺偏差也可以正确的制造出IC,尽可能地提高电路制备的成品率6.版图验证和检查主要包括哪些方面?u DRC(Design Rule Check):几何设计规则检查;对IC的版图做几何空间检查,保证能在特定的工艺条件下实现所设计的电路,并保证一定的成品率;u ERC(Electrical Rule Check):电学规则检查;检查电源(power)/地(ground)的短路,浮空的器件和浮空的连线等指定的电气特性;u LVS(Loyout versus Schematic):网表一致性检查;将版图提出的网表和原理图的网表进行比较,检查电路连接关系是否正确,MOS晶体管的长/宽尺寸是否匹配,电阻/电容值是否正确等;u LPE(Layout Parameter Extraction):版图寄生参数提取;从版图中提取晶体管的尺寸、结点的寄生电容、连线的寄生电阻等参数,并产生SPICE 格式的网表,用于后仿真验证;u POSTSIM:后仿真,检查版图寄生参数对设计的影响;提取实际版图参数、电阻、电容,生成带寄生量的器件级网表,进行开关级逻辑模拟或电路模拟,以验证设计出的电路功能的正确性和时序性能等,并产生测试向量。

集成电路制造技术习题解答(第4单元)

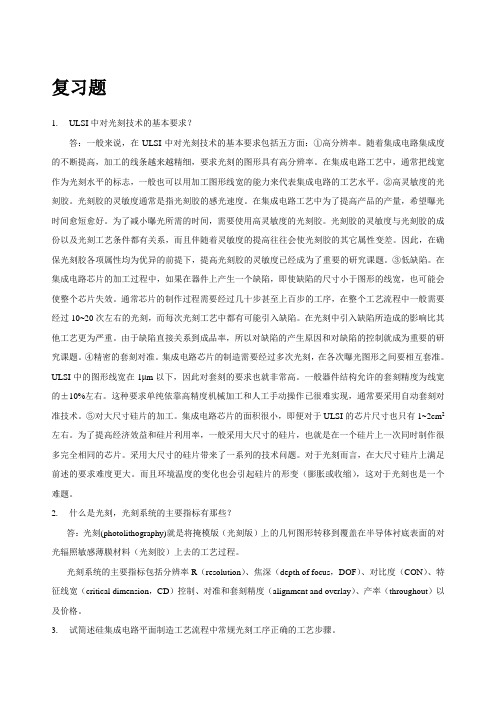

复习题1.ULSI中对光刻技术的基本要求?答:一般来说,在ULSI中对光刻技术的基本要求包括五方面:①高分辨率。

随着集成电路集成度的不断提高,加工的线条越来越精细,要求光刻的图形具有高分辨率。

在集成电路工艺中,通常把线宽作为光刻水平的标志,一般也可以用加工图形线宽的能力来代表集成电路的工艺水平。

②高灵敏度的光刻胶。

光刻胶的灵敏度通常是指光刻胶的感光速度。

在集成电路工艺中为了提高产品的产量,希望曝光时间愈短愈好。

为了减小曝光所需的时间,需要使用高灵敏度的光刻胶。

光刻胶的灵敏度与光刻胶的成份以及光刻工艺条件都有关系,而且伴随着灵敏度的提高往往会使光刻胶的其它属性变差。

因此,在确保光刻胶各项属性均为优异的前提下,提高光刻胶的灵敏度已经成为了重要的研究课题。

③低缺陷。

在集成电路芯片的加工过程中,如果在器件上产生一个缺陷,即使缺陷的尺寸小于图形的线宽,也可能会使整个芯片失效。

通常芯片的制作过程需要经过几十步甚至上百步的工序,在整个工艺流程中一般需要经过10~20次左右的光刻,而每次光刻工艺中都有可能引入缺陷。

在光刻中引入缺陷所造成的影响比其他工艺更为严重。

由于缺陷直接关系到成品率,所以对缺陷的产生原因和对缺陷的控制就成为重要的研究课题。

④精密的套刻对准。

集成电路芯片的制造需要经过多次光刻,在各次曝光图形之间要相互套准。

ULSI中的图形线宽在1μm以下,因此对套刻的要求也就非常高。

一般器件结构允许的套刻精度为线宽的±10%左右。

这种要求单纯依靠高精度机械加工和人工手动操作已很难实现,通常要采用自动套刻对准技术。

⑤对大尺寸硅片的加工。

集成电路芯片的面积很小,即便对于ULSI的芯片尺寸也只有1~2cm2左右。

为了提高经济效益和硅片利用率,一般采用大尺寸的硅片,也就是在一个硅片上一次同时制作很多完全相同的芯片。

采用大尺寸的硅片带来了一系列的技术问题。

对于光刻而言,在大尺寸硅片上满足前述的要求难度更大。

而且环境温度的变化也会引起硅片的形变(膨胀或收缩),这对于光刻也是一个难题。

数字集成电路课后习题1-4章作业解析

VOH = VGG − VT = VDD − VT 0 + γ

(

(V

SB

+ 2 φf − 2 φf

))

= VGG − VT 0 − γ VOH + 2 φ f + γ 2 φ f = 1.6 − 0.4 − 0.2 VOH + 0.88 + 0.2 0.88 = 1.388 − 0.2 VOH + 0.88

QOX 6 ×1011 ×1.6 ×10−19 0.06 V = = COX 1.6 ×10−6 VT0 =−0.99 − (−0.88) − (−0.188) − 0.060 =+0.018 V

计算 PMOS 器件的阈值电压: kT N D 3 ×1017 = φFn = ln 0.026 ln = 0.44 V q ni 1.4 ×1010

VOL 2 (0.1×10−4 )(8 ×106 )(1.6 − VOL − 0.4) 2 1 270 1.2 0.4 V − − ( ) OL = 0.1 VOL 2 (1.6 − VOL − 0.4) + 0.6 1 + 0.6

+0.99 V φGC = φFn − φG ( gate ) = 0.44 + 0.55 = QB 0 3 ×10−7 = = +0.188 V QB 0 = 3 ×10−7 C / cm 2 COX 1.6 ×10−6 QOX 6 ×1011 ×1.6 ×10−19 = = 0.06 V COX 1.6 ×10−6 VT0 =0.99 − (+0.88) − (+0.188) − 0.060 =−0.138 V

VOH = 1.11V 由此可知,VGG 实际要大于 1.6 V,接近 1.7 V,才能使 VOH 达到 1.2 V。 计算 VOL 时忽略体效应, ∴

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

自我检测题

1.在存储器结构中,什么是“字”什么是“字长”,如何表示存储器的容量

解:采用同一个地址存放的一组二进制数,称为字。

字的位数称为字长。

习惯上用总的位数来表示存储器的容量,一个具有n字、每字m位的存储器,其容量一般可表示为n ×m位。

2.试述RAM和ROM的区别。

解:RAM称为随机存储器,在工作中既允许随时从指定单元内读出信息,也可以随时将信息写入指定单元,最大的优点是读写方便。

但是掉电后数据丢失。

ROM在正常工作状态下只能从中读取数据,不能快速、随时地修改或重新写入数据,内部信息通常在制造过程或使用前写入,

3.试述SRAM和DRAM的区别。

解:SRAM通常采用锁存器构成存储单元,利用锁存器的双稳态结构,数据一旦被写入就能够稳定地保持下去。

动态存储器则是以电容为存储单元,利用对电容器的充放电来存储信息,例如电容器含有电荷表示状态1,无电荷表示状态0。

根据DRAM的机理,电容内部的电荷需要维持在一定的水平才能保证内部信息的正确性。

因此,DRAM在使用时需要定时地进行信息刷新,不允许由于电容漏电导致数据信息逐渐减弱或消失。

4.与SRAM相比,闪烁存储器有何主要优点

解:容量大,掉电后数据不会丢失。

5.用ROM实现两个4位二进制数相乘,试问:该ROM需要有多少根地址线多少根数据线其存储容量为多少

解:8根地址线,8根数据线。

其容量为256×8。

6.简答以下问题:

(1)CPLD和FPGA有什么不同

FPGA可以达到比 CPLD更高的集成度,同时也具有更复杂的布线结构和逻辑实现。

FPGA 更适合于触发器丰富的结构,而 CPLD更适合于触发器有限而积项丰富的结构。

在编程上 FPGA比 CPLD具有更大的灵活性;CPLD功耗要比 FPGA大;且集成度越高越明显;CPLD比 FPGA有较高的速度和较大的时间可预测性,产品可以给出引脚到引脚的最大延迟时间。

CPLD的编程工艺采用 E2 CPLD的编程工艺,无需外部存储器芯片,使用简单,保密性好。

而基于 SRAM编程的FPGA,其编程信息需存放在外部存储器上,需外部存储器芯片 ,且使用方法复杂,保密性差。

(2)写出三家CPLD/FPGA生产商名字。

Altera,lattice,xilinx,actel

7.真值表如表所示,如从存储器的角度去理解,AB应看为地址,F0F1F2F3应看为数据。

表

8.一个ROM 共有10根地址线,8根位线(数据输出线),则其存储容量为。

A.10×8 B.102×8 C.10×82 D.210×8

9.为了构成4096×8的RAM,需要片1024×2的RAM。

A.8片 B.16片 C.2片 D.4片

10.哪种器件中存储的信息在掉电以后即丢失

A.SRAM B.UVEPROM C.E2PROM D.PAL

11.关于半导体存储器的描述,下列哪种说法是错误的。

A.RAM读写方便,但一旦掉电,所存储的内容就会全部丢失

B.ROM掉电以后数据不会丢失

C.RAM可分为静态RAM和动态RAM

D.动态RAM不必定时刷新

12.有一存储系统,容量为256K×32。

设存储器的起始地址全为0,则最高地址的十六进制地址码为 3FFFFH 。

13.PAL是一种的可编程逻辑器件。

A.与阵列可编程、或阵列固定的 B.与阵列固定、或阵列可编程的

C.与、或阵列固定的 D.与、或阵列都可编程的

习题

1.现有如图所示的4×4位RAM若干片,现要把它们扩展成8×8位RAM。

(1)试问需要几片4×4位RAM

(2)画出扩展后电路图(可用少量门电路)。

图

解:(1)用4×4位RAM扩展成8×8位RAM时,需进行字数和位数扩展,故需要4片4×4的RAM

(2)扩展后电路如图:

D D 6D D 4A 0A 1D D 2D D 0

A 2

2.在微机中,CPU 要对存储器进行读写操作,首先要由地址总线给出地址信息,然后发出相应读或写的控制信号,最后才能在数据总线上进行信息交流。

现有256×4位的RAM 二片,组成一个页面,现需4个页面的存储容量,画出用256×4位组成1K ×8位的RAM 框图,并指出各个页面的地址分配。

解:电路连接图如图所示。

从左到右四个页面的地址为: 000H~0FFH ,100H~1FFH ,200H~2FFH ,300H~3FFH 。

D 7D 6D 5D 4D 3D 2D 1

D 0

A 8A 9

A 0~A 3.试用4×2位容量的ROM 实现半加器的逻辑功能,并直接在图中画出用ROM 点阵图实现的半加法器电路。

A

B

S i C i

图

A

B

i S i

C

A

B

i S i

C

解:由于半加器的输出B A B A S i +=

AB C i = 所以ROM 点阵图如图所示。

4.用EPROM 实现二进制码与格雷码的相互转换电路,待转换的代码由I 3I 2I 1I 0输入,转换后的代码由O 3O 2O 1O 0输出。

X 为转换方向控制位,当X =0时,实现二进制码到格雷码的转换;当X =1时,实现格雷码到二进制码的转换。

试求:

(1)列出EPROM 的地址与内容对应关系真值表;

(2)确定输入变量和输出变量与ROM 地址线和数据线对应关系。

解:真值表为:

输入变量和输出变量与ROM 地址线和数据线对应关系如图所示:

32×4 RAM D 3D 2D 1D 0

A 0

A 1A 3A 2X A 4I 3I 2I 1I 0

O 3O 2O 1O 0

5.试分析如图所示PLA 构成电路。

写出F 1、F 2的逻辑表达式。

1

2

图

解:C

A

F+

+

C

=

AB

A

B

C

1

A

=

F+

BC

C

B

A

2

6.试分析如图所示电路。

(1)列出时序PLA的状态表和状态图

(2)简述该时序PLA的逻辑功能。

图

解:(1)根据电路图写出各触发器驱动方程 n n Q Q J 120+=,10=K

n Q J 01=,n n Q Q K 021+= n n Q Q J 012=,n Q K 12=

(2)写出各触发器状态方程

n n n n n n n Q Q Q Q Q K Q J Q 010200000+=+= n n n n n n n n Q Q Q Q Q Q K Q J Q 0120111111+=+=

n n n n n n n n Q Q Q Q Q Q K Q J Q 1201222222+=+=

(3)列出状态表

(4)状态转换图

(5)功能:同步七进制加法计数器。

7.试分析如图所示由PLA 实现的时序电路,列出状态转换表,简述该时序电路的逻辑功能。

Q 0

Q 1

Q 2

X

图

解 (1)根据电路图写出各触发器状态方程:

n n n n n Q Q X Q Q Q 020112+=+

n n n n n n Q Q Q Q Q Q 0120111+=+

n n n n Q X Q Q Q 00210+=+

(2)根据特性方程列出状态真值表,如表所示。

(3)状态转换图

由状态真值表可得电路在X = 0与X = 1时的状态转换图,如图所示。

12Q Q Q X =0

X =1

(4)逻辑功能

当X =0时,该时序电路为6进制加法计数器;当X =1时,该时序电路为5进制加法计数器。

8.观察如图的可编程I/O 模块,要求把此I/O 模块配置成输入管脚,请标出数据输入通道,给出具体的5个配置比特,并给出T 的值。

I/O 引脚

输出信号

输入信号

时钟

使能使能全局请零

时钟三态控制输出反相

三态反相

锁存输出弱上拉

转换

速率

图

解:要将I/O 引脚作为输入引脚,要将输出三态缓冲器输出置成高阻态,弱上拉禁止。

因此可将三态控制T 置1,三态反相置0,弱上拉置0,其余编程位无关。