静态时序分析基本原理和时序分析模型

非常详细的静态时序分析教程

非常详细的静态时序分析教程静态时序分析是电子设计自动化领域中的重要方法之一,用于评估数字电路中的时序性能。

本教程将介绍静态时序分析的基本概念、方法和步骤,并提供一些实例来帮助读者深入了解这个领域。

一、静态时序分析的基本概念在进行静态时序分析之前,我们需要了解一些基本概念:1.时钟边沿:时钟是数字电路中的基本信号之一,它的边沿可以分为上升沿和下降沿。

时序分析通常以时钟的上升沿作为参考边沿进行分析。

2.关键路径:在一个数字电路中,存在多条路径可以连接输入和输出。

关键路径是指在特定时钟频率下,数据从输入到输出的延时最长的路径。

时序分析的目标之一就是找到并优化关键路径,以提高电路的性能。

3.时序约束:时序约束是对数字电路的时序性能要求的规定。

通常由设计者在进行时序分析之前进行设置,用于指导分析工具进行正确的分析和优化。

二、静态时序分析的方法和步骤静态时序分析的主要方法是通过对电路中的时钟域、数据路径和约束条件进行建模和分析,从而判断关键路径和优化方案。

下面是静态时序分析的基本步骤:1. 建立电路模型:首先,需要将数字电路转化为时序分析工具可以理解的模型,通常可以使用硬件描述语言(如Verilog或VHDL)对电路进行描述。

2.设定时序约束:根据设计规范和目标性能要求,制定适当的时序约束,如最大延时、最小脉冲宽度等。

时序约束的制定需要根据具体的电路应用和设计要求进行。

3.进行静态时序分析:使用时序分析工具对电路进行分析,找到关键路径,并计算出关键路径的延时。

关键路径上的最大延时指示了电路的最坏情况性能。

4.优化关键路径:在找到关键路径后,可以通过各种手段进行优化,如增加缓冲器、减少逻辑门延时等。

优化的目标是减小关键路径的延时,以提高整个电路的性能。

5.重新进行时序分析:在优化关键路径之后,需要重新进行时序分析,确保所做的优化在整个电路中得到正确应用,并满足时序约束。

三、实例分析让我们通过一个简单的例子来说明静态时序分析的具体过程。

静态时序分析(Static Timing Analysis)基础

静态时序分析(Static Timing Analysis)基础及应用◎陈麒旭前言在制程进入深次微米世代之后,芯片(IC)设计的高复杂度及系统单芯片(SOC)设计方式兴起。

此一趋势使得如何确保IC质量成为今日所有设计从业人员不得不面临之重大课题。

静态时序分析(Static Timing Analysis简称STA)经由完整的分析方式判断IC是否能够在使用者的时序环境下正常工作,对确保IC质量之课题,提供一个不错的解决方案。

然而,对于许多IC设计者而言,STA是个既熟悉却又陌生的名词。

本文将力求以简单叙述及图例说明的方式,对STA的基础概念及其在IC设计流程中的应用做详尽的介绍。

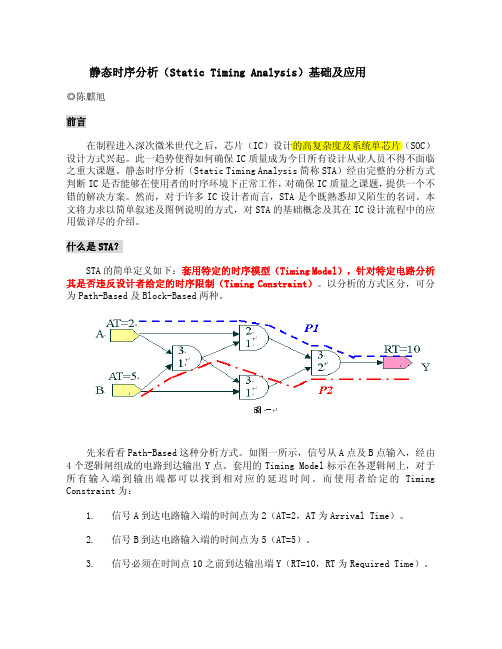

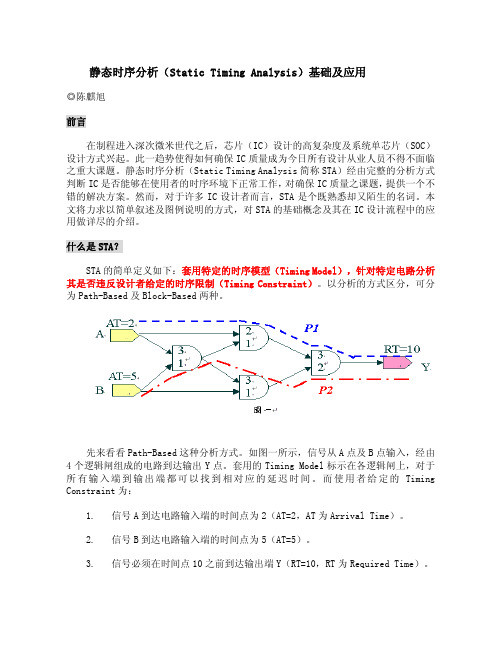

什么是STA?STA的简单定义如下:套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。

以分析的方式区分,可分为Path-Based及Block-Based两种。

先来看看Path-Based这种分析方式。

如图一所示,信号从A点及B点输入,经由4个逻辑闸组成的电路到达输出Y点。

套用的Timing Model标示在各逻辑闸上,对于所有输入端到输出端都可以找到相对应的延迟时间。

而使用者给定的Timing Constraint为:1.信号A到达电路输入端的时间点为2(AT=2,AT为Arrival Time)。

2.信号B到达电路输入端的时间点为5(AT=5)。

3.信号必须在时间点10之前到达输出端Y(RT=10,RT为Required Time)。

现在我们针对P1及P2两条路径(Path)来做分析。

P1的起始点为A,信号到达时间点为2。

经过第1个逻辑闸之后,由于此闸有2单位的延迟时间,所以信号到达此闸输出的时间点为4(2+2)。

依此类推,信号经由P1到达输出Y的时间点为7(2+2+3)。

在和上述第三项Timing Constraint比对之后,我们可以得知对P1这个路径而言,时序(Timing)是满足使用者要求的。

FPGA静态时序分析

D

Q

CLK Clock

时钟不确定性

输入时钟抖动是时钟不确定性的原因之一(Clock Uncertainty)

时钟偏斜(clock skew)

• 所有时序设计和分析都以时钟网络为参考。路径延迟分析 必须考虑时钟质量。 • 时钟偏斜是一个时钟信号沿着同一个时钟网络到达源触发 器和目标触发器的时间差。. • 所有时钟网络布线应该使用FPGA提供的专用时钟资源,否 则时钟偏斜会非常严重。 • 时钟偏斜分为负时钟偏斜和正时钟偏斜,主要对时钟周期 产生影响。时序分析器能够报告时钟偏斜问题。

14

路径和分析类型

Async Path

PRE D Q

Data Path

PRE D Q

CLR

CLR

Clock Paths Async Path

Three types of Paths: 1. Clock Paths 2. Data Path 3. Asynchronous Paths* Two types of Analysis: 1. Synchronous – clock & data paths 2. Asynchronous* – clock & async paths

Data must be valid here REG2.CLK REG2.D Data Valid

Tclk2

Tsu

Data Required Time = Clock Arrival Time - Tsu

26

数据要求时间- Hold

The minimum time required for the data to get latched into the destination re gister

静态时序分析(Static Timing Analysis)基础及应用

静态时序分析(Static Timing Analysis)基础及应用◎陈麒旭前言在制程进入深次微米世代之后,芯片(IC)设计的高复杂度及系统单芯片(SOC)设计方式兴起。

此一趋势使得如何确保IC质量成为今日所有设计从业人员不得不面临之重大课题。

静态时序分析(Static Timing Analysis简称STA)经由完整的分析方式判断IC是否能够在使用者的时序环境下正常工作,对确保IC质量之课题,提供一个不错的解决方案。

然而,对于许多IC设计者而言,STA是个既熟悉却又陌生的名词。

本文将力求以简单叙述及图例说明的方式,对STA的基础概念及其在IC设计流程中的应用做详尽的介绍。

什么是STA?STA的简单定义如下:套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。

以分析的方式区分,可分为Path-Based及Block-Based两种。

先来看看Path-Based这种分析方式。

如图一所示,信号从A点及B点输入,经由4个逻辑闸组成的电路到达输出Y点。

套用的Timing Model标示在各逻辑闸上,对于所有输入端到输出端都可以找到相对应的延迟时间。

而使用者给定的Timing Constraint为:1.信号A到达电路输入端的时间点为2(AT=2,AT为Arrival Time)。

2.信号B到达电路输入端的时间点为5(AT=5)。

3.信号必须在时间点10之前到达输出端Y(RT=10,RT为Required Time)。

现在我们针对P1及P2两条路径(Path)来做分析。

P1的起始点为A,信号到达时间点为2。

经过第1个逻辑闸之后,由于此闸有2单位的延迟时间,所以信号到达此闸输出的时间点为4(2+2)。

依此类推,信号经由P1到达输出Y的时间点为7(2+2+3)。

在和上述第三项Timing Constraint比对之后,我们可以得知对P1这个路径而言,时序(Timing)是满足使用者要求的。

时序分析(2):时序约束原理

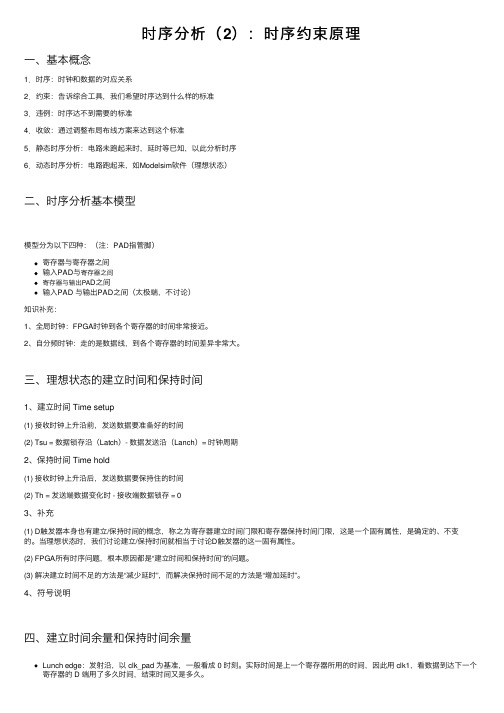

时序分析(2):时序约束原理⼀、基本概念1.时序:时钟和数据的对应关系2.约束:告诉综合⼯具,我们希望时序达到什么样的标准3.违例:时序达不到需要的标准4.收敛:通过调整布局布线⽅案来达到这个标准5.静态时序分析:电路未跑起来时,延时等已知,以此分析时序6.动态时序分析:电路跑起来,如Modelsim软件(理想状态)⼆、时序分析基本模型模型分为以下四种:(注:PAD指管脚)寄存器与寄存器之间输⼊PAD与寄存器之间寄存器与输出PA D之间输⼊PAD 与输出PAD之间(太极端,不讨论)知识补充:1、全局时钟:FPGA时钟到各个寄存器的时间⾮常接近。

2、⾃分频时钟:⾛的是数据线,到各个寄存器的时间差异⾮常⼤。

三、理想状态的建⽴时间和保持时间1、建⽴时间 Time setup(1) 接收时钟上升沿前,发送数据要准备好的时间(2) Tsu = 数据锁存沿(Latch)- 数据发送沿(Lanch)= 时钟周期2、保持时间 Time hold(1) 接收时钟上升沿后,发送数据要保持住的时间(2) Th = 发送端数据变化时 - 接收端数据锁存 = 03、补充(1) D触发器本⾝也有建⽴/保持时间的概念,称之为寄存器建⽴时间门限和寄存器保持时间门限,这是⼀个固有属性,是确定的、不变的。

当理想状态时,我们讨论建⽴/保持时间就相当于讨论D触发器的这⼀固有属性。

(2) FPGA所有时序问题,根本原因都是“建⽴时间和保持时间”的问题。

(3) 解决建⽴时间不⾜的⽅法是“减少延时”,⽽解决保持时间不⾜的⽅法是“增加延时”。

4、符号说明四、建⽴时间余量和保持时间余量Lunch edge:发射沿,以 clk_pad 为基准,⼀般看成 0 时刻。

实际时间是上⼀个寄存器所⽤的时间,因此⽤ clk1,看数据到达下⼀个寄存器的 D 端⽤了多久时间,结束时间⼜是多久。

Latch edge:接收沿,以 clk_pad 为基准,⼀般看成 0+Tcyc 时刻,要求时间是下⼀个寄存器计算的时间,所以⽤ clk2,看它⾃⾝需要的到达时间和结束时间是什么时候。

静态时序分析基本原理和时序分析模型

静态时序分析基本原理和时序分析模型静态时序分析是指对程序在其编译阶段或者运行阶段进行的一种分析方法,通过对程序的代码进行解析和推理,从而分析出程序执行的正确性、性能、资源消耗等方面的信息。

静态时序分析可以帮助开发人员在代码实现阶段尽早发现和解决问题,提高代码的可靠性和可维护性。

1.控制流分析:静态时序分析首先通过控制流分析,构建程序的控制流图。

控制流图由程序中的所有语句和它们之间的控制流关系构成,用来描述程序的执行路径和顺序。

静态时序分析可以通过控制流图来寻找潜在的执行路径问题,如死循环、无法到达的代码等。

2.数据流分析:静态时序分析还可以进行数据流分析,通过对程序中变量的定义和使用关系进行分析,确定变量在不同的执行路径上的值。

数据流分析可以帮助发现未初始化变量、未使用变量等问题。

3.依赖分析:静态时序分析可以进行依赖分析,分析程序中不同语句之间的依赖关系,确定一些语句执行的前提条件。

依赖分析可以帮助发现多线程竞争、资源争用等问题。

静态时序分析的依赖分析可以通过指针分析、函数调用分析等方式实现。

4.前向分析和后向分析:静态时序分析可以进行前向分析和后向分析。

前向分析从程序的入口点开始,根据程序的控制流图,逐个语句地分析程序的执行路径。

后向分析从程序的出口点开始,反向分析程序的执行路径。

通过前向分析和后向分析,可以找到程序的执行路径,帮助发现执行路径上的问题。

时序分析模型是静态时序分析的抽象表示,可以用来描述程序的执行顺序和时序约束。

常见的时序分析模型包括Petri网、有限状态机等。

1. Petri网:Petri网是一种常用的时序分析模型,它可以描述系统中不同活动之间的顺序和并发关系。

Petri网由节点和有向弧组成,节点表示活动,弧表示活动之间的关系。

通过对Petri网的分析,可以推理出系统的行为和时序约束。

2.有限状态机:有限状态机是描述系统行为的一种抽象模型,它可以把系统的执行顺序表示为一个状态转移图。

(转)让你彻底理解:静态时序分析

(转)让你彻底理解:静态时序分析估计⾯试的时候都会让⼤家解释⼀下建⽴时间和保持时间,⼏乎所有⼈都能背出来。

建⽴时间(setup time):时钟的有效沿到来之前数据必须提前稳定的时间。

保持时间(hold time):时钟有效沿到来之后数据必须继续保持稳定的时间。

我们知道,整个ASIC设计流程主要两个⽬的:功能和性能。

除了要保证设计的功能,另外⼀个就是要保证性能。

性能通俗的讲,主要是看电路跑得多快,也就是时钟频率有多⾼。

保证性能的⽅法就是通过静态时序分析保证电路能够跑到要求的频率。

⽽静态时序分析(Static Timing Analyze),其本质是检查电路中所有寄存器是否满⾜⼯艺库规定的固有建⽴时间和保持时间。

可咋⼀看,寄存器的建⽴保持时间跟时钟周期是没有关系的。

因此,带着这些困惑,我们⼀起来了解⼀下静态时序分析的真正原理。

⾸先,所有电路都可以抽象成上图的形式,这是因为RTL(Register Transition Level)代码描述的是寄存器的传输⾏为,信号从DFF1通过组合逻辑CMB的⾏为,传输到DFF2。

另外,静态时序分析都是假设所有信号每个周期都可能变化,也就是单周期检查。

这样,D1从时钟沿开始,DFF1出来,通过组合逻辑CMB,下⼀个时钟沿,D2要能正确寄存在DFF2中,就需要满⾜建⽴和保持时间的要求。

因此, D1从时钟CK的上升沿开始,通过DFF1的CK->Q的延时Tck,组合逻辑的延时Tcmb,在第⼆个CK上升沿分析DFF2的建⽴和保持时间。

建⽴时间:Tx1 = T – Tck -Tcmb > Tsetup Tck + Tcmb + Tsetup < T如果考虑时钟的Skew,也就是CK1和CK2的时钟沿不是同时到达,对于悲观的影响,也就是CK2⽐CK1要提前到来Tskew时间,则Tck + Tcmb + Tsetup + Tskew < T Tcmb < T – Tck – Tsetup – Tskew因此,建⽴时间与时钟周期扯上关系了,也就是约束了组合逻辑的延时不能太⼤。

静态时序分析综述报告以及primetime简介

静态时序分析综述报告——孙声震1.静态时序分析静态时序分析(STA)就是套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。

1.1 背景仿真技术是ASIC设计过程中应用最多的验证手段,然而,现在的单片集成系统设计正在将仿真时间推向无法容忍的极限。

在最后的门级仿真阶段,针对的是几十乃至几百万门的电路,对仿真器第一位的要求是速度和容量,因此,性能(仿真速度)和容量(能够仿真的设计规模)是验证中的关键因素。

传统上采用逻辑仿真器验证功能时序,即在验证功能的同时验证时序,它以逻辑模拟方式运行,需要输入向量作为激励。

随着规模增大,所需要的向量数量以指数增长,验证所需时间占到整个设计周期的50%,而最大的问题是难以保证足够的覆盖率。

鉴于此,这种方法已经越来越少地用于时序验证,取而代之的是静态时序分析技术。

1.2 分类静态时序分析以分析的方式区分,可分为Path-Based及Block-Based两种。

图1如图1所示,为Path-Based这种分析方式。

信号从A点及B点输入,经过中间的逻辑单元,从Y端输出。

套用的Timing Model标示在各逻辑器件上,对于所有输入端到输出端都可以找到相对应的延迟时间。

而使用者给定的TimingConstraint为:1. 信号A到达电路输入端的时间点为2(AT=2,AT为Arrival Time)。

2. 信号B到达电路输入端的时间点为5(AT=5)。

3. 信号必须在时间点10之前到达输出端Y(RT=10,RT为Required Time)。

针对P1及P2 两条路径(Path)来做分析。

P1的起始点为A,信号到达时间点为2。

经过第1个逻辑器件之后,由于有2单位的延迟时间,所以信号到达这个器件输出的时间点为4(2+2)。

依此类推,信号经由P1到达输出Y的时间点为7(2+2+3)。

在和上述第三项Timing Constraint比对之后,我们可以得知对P1这个路径而言,时序(Timing)是满足使用者要求的。

时间序列法 静态法

时间序列法静态法时间序列法与静态法是一种用于预测和分析数据的方法。

本文将详细介绍这两种方法的原理和应用。

一、时间序列法时间序列法是一种基于时间顺序的统计分析方法,用于预测未来的数据。

它假设未来的数据与过去的数据存在某种规律性关系,通过对过去数据的分析来预测未来数据的变化。

时间序列法的基本原理是通过观察和分析一系列连续的数据点来推断未来的趋势和模式。

它主要包括以下几个步骤:1. 数据收集:首先收集一系列连续的数据点,这些数据点可以是按照时间顺序排列的,比如每天、每月或每年的数据。

2. 数据预处理:对收集到的数据进行预处理,包括去除异常值、填补缺失值、平滑数据等。

3. 模型选择:根据数据的性质和特点选择合适的时间序列模型,常用的模型包括移动平均模型、自回归模型、ARIMA模型等。

4. 模型拟合:根据选择的模型对数据进行拟合,得到模型的参数。

5. 模型诊断:对拟合后的模型进行诊断,检验模型的合理性和可靠性。

6. 模型预测:使用拟合好的模型对未来的数据进行预测,得到预测结果。

时间序列法的优点是可以考虑到数据的时间顺序和趋势,能够较好地反映出数据的周期性和规律性。

但是它也有一些局限性,比如对于非平稳的数据和异常值的处理较为困难。

二、静态法静态法是一种基于静态数据的分析方法,它主要通过对一组静态数据的分析来预测未来的趋势和模式。

与时间序列法不同,静态法不考虑数据的时间顺序和趋势,只关注数据本身的特征。

静态法的基本原理是通过对静态数据的分析来寻找数据之间的关系和规律,然后利用这些关系和规律来预测未来的数据。

它主要包括以下几个步骤:1. 数据收集:收集一组静态数据,这些数据可以是同一时间点或者不同时间点的数据。

2. 数据预处理:对收集到的数据进行预处理,包括去除异常值、填补缺失值、标准化等。

3. 特征选择:根据数据的特征和目标变量选择合适的特征,常用的方法包括相关性分析、主成分分析等。

4. 模型选择:根据选择的特征和目标变量选择合适的模型,常用的模型包括线性回归模型、逻辑回归模型、决策树模型等。

静态时序分析课件

案例三:时钟偏差与时钟抖动问题解决

总结词

详细描述

案例四:时序违规问题解决

要点一

总结词

要点二

详细描述

时序违规问题是指在设计中的时序信号不能满足时序约束 条件,可能导致数据传输错误或系统不稳定。

在静态时序分析中,需要仔细检查设计的时序信号是否满 足约束条件,并采取相应的措施来解决时序违规问题。可 以采用优化设计、调整时序约束条件或使用静态时序分析 工具等方法来解决时序违规问题。

时钟源与负载不匹配问题

总结词

详细描述

时钟偏差与时钟抖动问题

总结词

时钟偏差与时钟抖动问题是指时钟信号 在传输过程中出现的偏差和抖动现象, 可能导致数据的不稳定和时序违规。

VS

详细描述

时钟信号在传输过程中会受到各种因素的 影响,如线路长度、连接器、时钟源的抖 动等,导致时钟信号的偏差和抖动。这种 偏差和抖动可能导致数据的不稳定和时序 违规。为了解决这个问题,需要减小传输 过程中的偏差和抖动,并加强时钟网络的 同步和稳定性。

THANKS

感谢观看

时钟偏差是指时钟信号到达不同寄存器的时间偏差,通常由时钟源、时钟网络和寄 存器本身引起。

时钟抖动和偏差是影响数字电路时序分析的重要因素,需要进行有效的管理和优化。

03

静态时序分析方法

路径延迟分析

路径延迟分析是静态时序分析中的重 要步骤,它通过计算信号在电路中传 输的延迟时间,来确定信号到达时间 是否满足时序要求。

时序违规问题

总结词

详细描述

06

静态时序分析案例研究

案例一:时钟域交叉问题解决

总结词

详细描述

案例二:时钟源与负载不匹配问题解决

总结词

时钟源与负载不匹配问题是指时钟源的频率与负载的要求不匹配,可能导致数据 传输错误或资源浪费。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Designer must enter timing requirements & exceptions

−

Used to guide fitter during placement & routing − Used to compare against actual results

PRE

PRE Q D Q

Setup Slack = Data Required Time – Data Arrival Time

Positive slack − Timing requirement met Negative slack − Timing requirement not met

© 2009 Altera Corporation Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation 13

Tsu Latch Edge

CLK Data must be valid here REG2.CLK REG2.D

Tclk2

Tsu

Data Valid

Data Required Time = Clock Arrival Time - Tsu - Setup Uncertainty

© 2009 Altera Corporation Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation 10

Setup Slack

The margin by which the setup timing requirement is met. It ensures launched data arrives in time to meet the latching requirement.

REG1

PRE

Data Required Time - Setup

The minimum time required for the data to get latched into the destination register

REG1

PRE

REG2

D

Q

Comb. Logic

PRE

D

Q

CLR

CLR

Tclk2

Together, the setup time and hold time form a Data Required Window, the time around a clock edge in which data must be stable.

Hold:

© 2009 Altera Corporation Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation 7

DATA

D PRE Q

CLK

Tsu Th

DATA Valid

CLK

CLR

Setup:

The minimum time data signal must be stable BEFORE clock edge The minimum time data signal must be stable AFTER clock edge

© 2009 Altera Corporation Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation 4

Path & Analysis Types

Tclk1 Tco

Data Valid

Tdata

REG2.D Data Valid

Data Arrival Time = launch edge + Tclk1 + Tco +Tdata

© 2009 Altera Corporation Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation 8

Launch & Latch Edges

Launch Edge

CLK DATA Data Valid

Latch Edge

Launch Edge: Latch Edge:

the edge which “launches” the data from source register the edge which “latches” the data at destination register (with respect to the launch edge, selected by timing analyzer; typically 1 cycle)

IN CLK CLR

D

OUT

CLR

CLR

combinational delays

© 2009 Altera Corporation Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation 3

Timing Analysis Basics

Launch vs. latch edges Setup & hold times Data & clock arrival time Data required time Setup & hold slack analysis I/O analysis Recovery & removal Timing models

Data Required Time - Hold

The minimum time required for the data to get latched into the destination register

REG1

PRE

REG2

D

Q

Comb. Logic

PRE

Dቤተ መጻሕፍቲ ባይዱ

Q

CLR

CLR

Tclk2

Th Latch Edge

Quartus® II Software Design Series: Timing Analysis

- Timing analysis basics

© 2009 Altera Corporation 1

Objectives

Display a complete understanding of timing analysis

Clock Arrival Time

The time for clock to arrive at destination register’s clock input

REG1

PRE

REG2

D

Q

Comb. Logic

PRE

D

Q

CLR

CLR

Tclk2 Latch Edge CLK

Tclk2

REG2.CLK

Every device path in design must be analyzed with respect to timing specifications/requirements

−

Catch timing-related errors faster and easier than gate-level simulation & board testing

Tdata

Comb. Logic

REG2

PRE

D

Q

D

Q

Tclk1

CLR

CLR

TCO Launch Edge CLK REG1.CLK REG1.Q

Tclk2

Tsu Latch Edge

Tclk1 Tco

Data Valid

Tdata

REG2.D Data Valid

Tclk2

REG2.CLK

© 2009 Altera Corporation

Hold Slack

The margin by which the hold timing requirement is met. It ensures latch data is not corrupted by data from another launch edge.

REG1

Async Path

PRE D Q

Data Path

D

PRE Q

CLR

CLR

Clock Paths Async Path

Three types of Paths: 1. Clock Paths 2. Data Path 3. Asynchronous Paths* Two types of Analysis: 1. Synchronous – clock & data paths 2. Asynchronous* – clock & async paths

© 2009 Altera Corporation Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation 2