全差分运算放大器设计

全差分运算放大器设计概要

全差分运算放大器设计概要全差分运算放大器是一种常见的电子电路,它可以将输入信号的差分放大,并在输出端提供差分信号。

全差分运算放大器广泛应用于模拟与数字信号处理中,如低噪声放大器、滤波器和交叉耦合放大器等领域。

本文将介绍全差分运算放大器的设计概要,包括电路结构、设计要点和性能指标等。

[图片]该电路由两个共模反馈放大器组成,其中一个作为正放大器,另一个作为负放大器。

输入信号通过差分输入端口加到两个反馈放大器上,经过放大后,在输出端口提供差分信号。

为了保证优良的性能,必须对电路的参数进行适当的设计和调整。

首先,需要确定全差分运算放大器的增益要求。

增益是指输出信号与输入信号之间的比例关系。

在不同的应用中,增益要求可能不同。

根据增益要求,可以选择合适的放大器型号和电路拓扑结构。

其次,需要选择适当的放大器元件。

放大器元件包括晶体管、电阻、电容等。

选择合适的元件是设计成功的关键。

晶体管的选择要考虑其增益、噪声系数、带宽等指标。

电阻和电容的选择要考虑其阻值、容值、精度等因素。

然后,需要确定电路的偏置方案。

全差分运算放大器需要提供适当的偏置电压,以确保电路能够正常工作。

偏置电压的选择要考虑元件的工作状态和参数的稳定性。

常见的偏置方案包括电流镜偏置、电流源偏置等。

设计完成后,需要对电路进行性能测试和优化。

性能测试包括增益、带宽、噪声系数、非线性失真等指标的测试。

根据测试结果,可以进行相应的电路优化,以满足设计要求。

最后,需要对电路进行可靠性分析。

可靠性分析是为了确保电路在长时间工作过程中不会出现故障。

可靠性分析包括温度分析、电路重要参数的敏感度分析等。

全差分运算放大器设计的关键在于电路的结构和元件的选择。

合理的电路结构和适当的元件选择可以使电路具有较高的增益、宽带和低噪声等性能。

此外,还需要注意电路的偏置方案和可靠性分析,以确保电路的正常工作和长时间可靠性。

总之,全差分运算放大器是一种重要的电子电路,具有广泛的应用前景。

全差分运算放大器设计

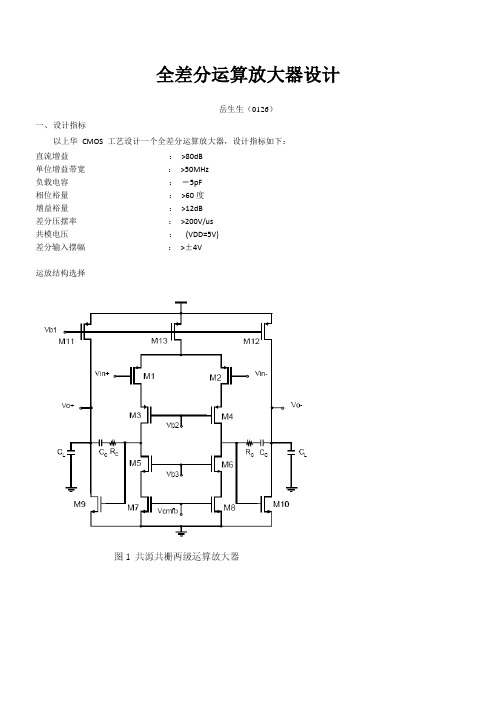

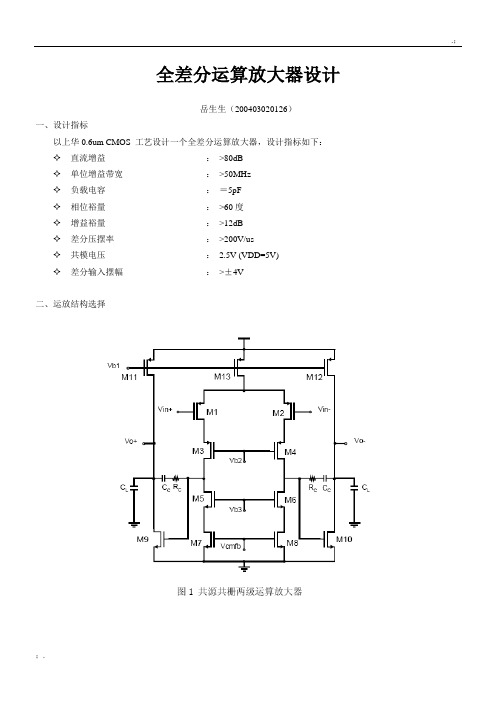

全差分运算放大器设计岳生生(0126)一、设计指标以上华CMOS 工艺设计一个全差分运算放大器,设计指标如下:直流增益:>80dB单位增益带宽:>50MHz负载电容:=5pF相位裕量:>60度增益裕量:>12dB差分压摆率:>200V/us共模电压:(VDD=5V)差分输入摆幅:>±4V运放结构选择运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。

如图2所示;(b )折叠共源共栅,folded-cascode 。

如图3所示;(c )共源共栅,telescopic 。

如图1的前级所示。

本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT NV之和小于,输出端的所有PMOS 管的,DSAT PV之和也必须小于。

对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。

另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。

考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。

两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。

性能指标分析差分直流增益 (Adm>80db)该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12)第一级增益 1351113571135135753()m m m o o o o o m m m m o o o o m m g g g g g g G A R r r r r g g r r r r=-=-=-+P第二级增益92291129911()m o o o m m o o g g G A R r r g g=-=-=-+P 整个运算放大器的增益:4135912135753911(80)10m m m m overallo o o o m m o o dB g g g gAA A g g g gr r r r ==≥++差分压摆率 (>200V/us )转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。

低电压高速CMOS全差分运算放大器设计双

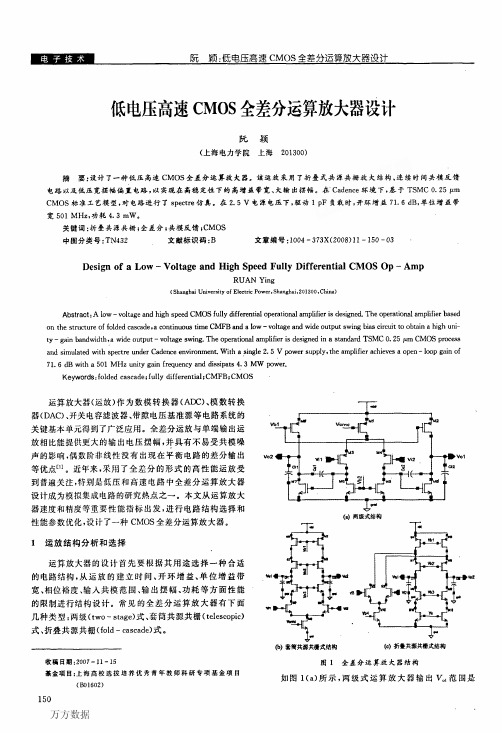

运算放大器的设计首先要根据其用途选择一种合适 的电路结构,从运放的建立时问、开环增益、单位增益带 宽、相位裕度、输入共模范围、输出摆幅、功耗等方面性能 的限制进行结构设计。常见的全差分运算放大器有下面 几种类型:两级(two—stage)式、套筒共源共栅(telescopic) 式、折叠共源共栅(fold—cascade)式。

4‘结语

本文使用TSMC公司的CM025工艺

设计并实现了一个低压高速全差分运算放

大器。采用折叠共源共栅结构,在达到较高

的带宽同时,增大了输出摆幅。连续时间共

模反馈电路以及低压宽摆幅偏置电路,实现

(1)信置电路OO半电路小信号等效模型

图3偏置电路及半电路小信号等效模型

了电路的高稳定性。该运放在2.5 V电源 电压下,’单位增益带宽可以达到501 MHz, 直流增益71.6 dB,相位裕度51。,功耗

P。《P,,更接近于原点,因此P2为折叠共源共栅运放的 主极点,P。为次极点。

要提高开环增益A。,可以采取增加M8,M9的跨导和

1 5】

沟逝长度,但将引起其源极寄生电容的增加和漏源饱和电 正减小,从而降低运放的次极点频率。同样增加M10, M11的沟道长度,会使A。增加而次极点频率减小。考虑 到M4,M5,M6,M7不在信号通路上,因此可以增加其沟 道长度球增加输出阻抗,而不降低工作速度。

△gM9(r2//rlo)r9 R。。“M7一r4+r7[1+(gM7+gM7b)^]

△gM7 r7 r4 r为MOS管的小信号输出电阻。负载电容C。远大于MOS 管各端的寄生电容,CL△cD瞰+CD曲+CD酊。。

节点1对应的极点P。:

P-=一石万勿习丽i1冠i而△一等

节点2对应的极点P。:

全差分运算放大器设计说明

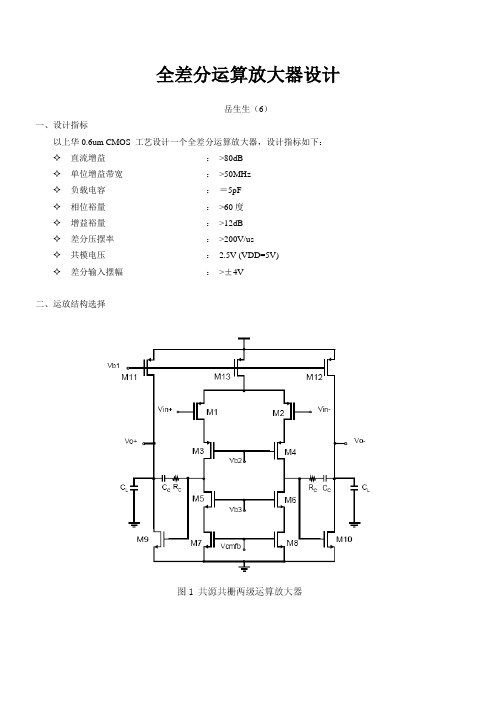

全差分运算放大器设计岳生生(6)一、设计指标以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下:✧直流增益:>80dB✧单位增益带宽:>50MHz✧负载电容:=5pF✧相位裕量:>60度✧增益裕量:>12dB✧差分压摆率:>200V/us✧共模电压:2.5V (VDD=5V)✧差分输入摆幅:>±4V二、运放结构选择运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。

如图2所示;(b )折叠共源共栅,folded-cascode 。

如图3所示;(c )共源共栅,telescopic 。

如图1的前级所示。

本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT NV之和小于0.5V ,输出端的所有PMOS管的,DSAT PV之和也必须小于0.5V 。

对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。

另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。

考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。

两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。

三、性能指标分析1、 差分直流增益 (Adm>80db)该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益1351113571135135753()m m m o o o o o m m m m o o o o m m g g gg ggG A R r r r r g g r r r r=-=-=-+P第二级增益92291129911()m o o o m m o o gg G AR r r gg=-=-=-+P整个运算放大器的增益:4135912135753911(80)10m m m m overallo o o o m m o o dB g g g gAA A g g g gr r r r ==≥++2、 差分压摆率 (>200V/us )转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。

一种高增益宽带CMOS全差分运算放大器

conlbming the s仃uctllre Offolded cascode、two d洎奄rential-pa趣CMFB aIld gain-

boos锄g technique.The operational amplifier is desi弘ed i11 TSMC 0.25叫l 2P5P

CMOS process and simulated wim cadence spec仃e llIlder the condition of 2.5V sin百e

cMOS全差分运算放大器。基于TSMc O.25岫2P5M cMOS工艺,利用cadence

spec仃e仿真工具分别对所设计的运放电路进行了仿真分析。结果表明,在2.5V的 单电源电压下,运算放大器的直流开环增益为104dB,单位增益带宽为385MHz, 达到并超出了最初提出的增益和带宽的要求。论文还分析了一种电荷定标的D缓 转换器以及带自举开关的采样保持器原理,利用本文设计的全差分运算放大器作 为口核分别应用于一个8位的D/A转换器和50MsPS的采样保持器中,并取得了

叩erational锄plifier、common mode fcedback a11d gain.boosting technique,and desi印

a cMOS fhlly di船rential operational锄plmer with hi幽gaill and wide band、Ⅳidth by

并基于TsMc 0.25岫cMOs工艺的sⅡ讧3V3模型,利用Cadence spec仃e工具对所设

计的电路进彳亍了仿真分析,其结果己满足并超出所设计的要求。 本文的结构就是按照作者在论文完成中的工作顺序进行安排的。 第二章,主要介绍了几种常用的CMOs全差分运算放大器结构以及共模反馈

全差分两级放大电路

综合课程设计研究报告课题名称:全差分两级运放研究人员:指导教师:王向展宁宁201 年1月1日微电子与固体电子学院目录一、绪论 (1)(一)研究工作的背景与意义 (1)(二)国内外现状分析 (1)二、研究目标、研究内容与技术指标 (1)(一)研究目标 (2)(二)研究内容 (2)(三)关键技术 (2)(四)技术指标 (3)三、电路工作原理 (3)(一)电路结构理论 (4)(二)关键电路模块 (4)(三)非理想效应 (5)四、电路设计与仿真 (6)(一)电路设计方案 (6)(二)电路设计结构 (9)(三)电路仿真及结果 (10)五、全文总结与展望 (12)参考文献 (13)一、绪论(一)研究工作的背景与意义随着模拟集成电路技术的发展,高速、高精度运算放大器得到广泛应用。

全差分运算放大器在输入动态范围、抑制共模信号和噪声的能力等方面,较单端输出运放有很大优势,成为应用很广的电路单元。

另外,全差分输出时的输出电压信号幅度比单端输出时增大一倍,这对低电源电压供电的现代CMOS电路尤为重要,因为这可以扩大输出信号的动态范围。

因此,本文讨论并设计了满足一定要求的全差分运算放大器。

(二)国内外现状分析从第一颗运算放大器IC问世到现在,运算放大器技术已经在半导体制造工艺和电路设计两方面取得了巨大进展。

在大约40年的发展过程中,IC制造商们利用上述先进技术设计出了近乎“完美”的放大器。

虽然什么是理想放大器很难有一个精确定义,但它却为模拟设计工程师提供了一个目标。

理想放大器应该无噪声、具有无穷大增益、无穷大输入阻抗、零偏置电流以及零失调电压,它还应该不受封装尺寸限制,不占用空间。

上述这些,都是许多教科书为了得到简单的传递函数而做出的种种假设。

未来放大器市场增长的驱动力主要有三方面:其一,便携式应用的低功耗要求将推动具有低操作电源电压/电流的放大器增长;其二,高分辨率应用需要能降低噪声和失真度的放大器;其三,由于性能和价格压力持续上扬,因此能够集成其他功能的放大器前景乐观。

全差分增益提高运算放大器的分析与设计

第28卷 第2期2005年6月电 子 器 件Chinese Journal of Elect ron Devices Vol.28 No.2J un.2005Analysis and Design of Fully Differential G ain 2Boosted OpampW A N G J i n 1,Q I U Yu 2li n 1,T I A N Ze21.I nstit ute of Microelect ronic of Chinese A cadem y of S ciences ,Bei j ing 100029,China;2.Depart ment of Elect ronic Science ,N ort hwestern Universit y ,X i ’an 710069,ChinaAbstract :The gain 2boosting technology is presented and analyzed.Wit h gain 2boosting ,a f ully differential gain 2boo sted telescopic cascode opamp is propo saled and designed.The main opamp is a f ully differential telescopic opamp and has a switched capacitor CM FB circuit.The boo sting opamp is a f ully differential fol 2ded cascode opamp and has a co ntinuous time CM FB circuit.The opamp is designed in SM IC 0.35μmixed 2signal CMOS p rocess wit h 3.3V power supply and achieved a dc gain of 129dB wit h a 161M Hz unity gain f requency.K ey w ords :f ully differential ,gain 2boo sted ;opamp EEACC :1220全差分增益提高运算放大器的分析与设计王 晋1,仇玉林1,田 泽21.中国科学院微电子研究所,北京,100029;2.西北大学电子科学系,西安,710069收稿日期:2004212203作者简介:王 晋(19732)男,博士研究生,主要从事模拟集成电路和混合集成电路设计,wangjin0215@ ;仇玉林(19422)男,研究员、博士生导师,wangjin0215@摘 要:通过增益提高技术,一个全差分增益提高套筒式共源共栅运算放大器被提出和设计。

全差分运算放大器设计

全差分运算放大器设计岳生生(200403020126)一、设计指标以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下:✧直流增益:>80dB✧单位增益带宽:>50MHz✧负载电容:=5pF✧相位裕量:>60度✧增益裕量:>12dB✧差分压摆率:>200V/us✧共模电压:2.5V (VDD=5V)✧差分输入摆幅:>±4V二、运放结构选择运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。

如图2所示;(b )折叠共源共栅,folded-cascode 。

如图3所示;(c )共源共栅,telescopic 。

如图1的前级所示。

本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT NV之和小于0.5V ,输出端的所有PMOS管的,DSAT PV之和也必须小于0.5V 。

对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。

另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。

考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。

两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。

三、性能指标分析1、 差分直流增益 (Adm>80db)该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益1351113571135135753()m m m o o o o o m m m m o o o o m m g g gg gg G A R r rr r g g r r r r=-=-=-+第二级增益92291129911()m o o o m m o o gg G AR r rgg=-=-=-+整个运算放大器的增益:4135912135753911(80)10m m m m overallo o o o m m o o dB g g g gAA A g g g gr r r r ==≥++2、 差分压摆率 (>200V/us )转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

全差分运算放大器设计

全差分运放(Fully-Differential Amplifier,简称FDA)是一种特

殊的运放,它具有两个差动输入和两个差动输出。

全差分运放具有许多优点,包括良好的共模抑制和电源抑制比,适用于高精度传感器信号放大、

功率放大和模拟信号处理等领域。

在这篇文章中,我将介绍全差分运放的

设计原理和步骤。

首先,我们需要确定设计的要求和规范。

这包括增益要求、带宽要求、电源电压和输入输出电阻等参数。

根据这些要求,我们可以选择合适的运

放器件和电路拓扑。

全差分运放的常见电路拓扑有两级差分放大器、共射共源放大器和增

益交换放大器等。

在这里,我们以两级差分放大器为例进行设计。

第一步是选择运放器件。

我们需要根据设计要求选择适合的运放器件,可以根据其增益带宽积、供电电压范围和失调电流等参数进行选择。

一般

来说,我们可以选择低失调电流、高增益带宽积和低电压噪声的器件。

第二步是确定电路拓扑。

在两级差分放大器中,第一级是差分放大器,第二级是共射共源放大器。

差分放大器的作用是提供高输入阻抗和共模抑

制比,共射共源放大器的作用是提供电流放大和驱动能力。

由于这两级放

大器要分别满足不同的要求,我们可以选择不同的放大倍数和器件参数来

优化电路性能。

第三步是确定偏置电路。

偏置电路的作用是提供恒定的工作电流,这

可以通过电流源和电阻网络来实现。

偏置电流的选择要根据运放器件的要

求和特点,可以使用恒流源或电流反馈等方法来实现。

第四步是确定反馈电路。

反馈电路的作用是控制放大倍数和增益稳定性,可以使用电阻、电容或者电流源等元件来实现。

选择适当的反馈方式

可以减小失调电压和非线性,提高性能。

第五步是进行电路仿真和优化。

通过电路仿真,我们可以验证设计的

性能和满足要求。

优化可以通过调整电路参数和进行迭代仿真来实现,以

达到设计要求。

第六步是进行电路布局和线路板设计。

在设计布局时,要注意分离放

大器电路和干扰源,减少电源和信号线的串扰。

线路板设计要保证差分信

号走线的对称性和阻抗匹配,以提高传输性能。

最后,进行性能测试和验证。

通过使用合适的测试仪器,我们可以对

全差分运放的放大性能、带宽和输出阻抗进行测试和验证。

如果发现问题,可以进行修改和优化。

总之,全差分运放的设计是一个相对复杂的任务,需要充分考虑电路

拓扑、器件选择、偏置电路、反馈电路、仿真和优化等因素。

正确的设计

方法和步骤可以帮助我们实现理想的性能和满足设计要求。