晶体管原理1

场效应管工作原理 1

场效应管工作原理(1)场效应晶体管(Field Effect Transistor缩写(FET))简称场效应管。

一般的晶体管是由两种极性的载流子,即多数载流子和反极性的少数载流子参与导电,因此称为双极型晶体管,而FET仅是由多数载流子参与导电,它与双极型相反,也称为单极型晶体管。

它属于电压控制型半导体器件,具有输入电阻高(108~109Ω)、噪声小、功耗低、动态范围大、易于集成、没有二次击穿现象、安全工作区域宽等优点,现已成为双极型晶体管和功率晶体管的强大竞争者。

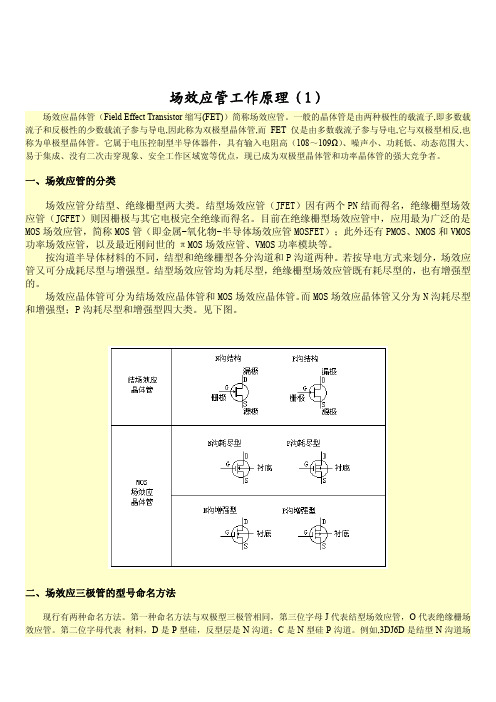

一、场效应管的分类场效应管分结型、绝缘栅型两大类。

结型场效应管(JFET)因有两个PN结而得名,绝缘栅型场效应管(JGFET)则因栅极与其它电极完全绝缘而得名。

目前在绝缘栅型场效应管中,应用最为广泛的是MOS场效应管,简称MOS管(即金属-氧化物-半导体场效应管MOSFET);此外还有PMOS、NMOS和VMOS 功率场效应管,以及最近刚问世的πMOS场效应管、VMOS功率模块等。

按沟道半导体材料的不同,结型和绝缘栅型各分沟道和P沟道两种。

若按导电方式来划分,场效应管又可分成耗尽型与增强型。

结型场效应管均为耗尽型,绝缘栅型场效应管既有耗尽型的,也有增强型的。

场效应晶体管可分为结场效应晶体管和MOS场效应晶体管。

而MOS场效应晶体管又分为N沟耗尽型和增强型;P沟耗尽型和增强型四大类。

见下图。

二、场效应三极管的型号命名方法现行有两种命名方法。

第一种命名方法与双极型三极管相同,第三位字母J代表结型场效应管,O代表绝缘栅场效应管。

第二位字母代表材料,D是P型硅,反型层是N沟道;C是N型硅P沟道。

例如,3DJ6D是结型N沟道场效应三极管,3DO6C 是绝缘栅型N沟道场效应三极管。

第二种命名方法是CS××#,CS代表场效应管,××以数字代表型号的序号,#用字母代表同一型号中的不同规格。

例如CS14A、CS45G等。

晶体管放大原理

晶体管放大原理

晶体管放大原理是通过改变晶体管的输入信号电压,从而控制其输出电流的程度来实现信号放大的过程。

晶体管主要由三个区域组成:发射区、基区和集电区。

当外加电压施加在晶体管的基极和发射极之间时,就会在发射区产生一个很小的电流,称为发射极电流。

这个电流是由基极发射极结之间的正向偏置电压引起的。

此时,发射区的能带结构会发生变化,导致与其接触的基区中形成了一个浓度较高的载流子区域,称为输运区。

这个输运区能够将来自发射区的电子输运到集电区。

当输入信号电压施加在基极和发射极之间时,它会改变发射区的能带结构,从而改变输运区内的载流子浓度。

这就导致了集电区的电流发生变化。

因此,通过改变输入信号电压,晶体管可以实现对输出电流的控制。

由于输入信号电压较小,晶体管的增益(即输出电流与输入信号电流之间的比值)很大。

所以晶体管可以将输入信号放大到较大的幅度。

此外,晶体管具有高输入电阻和低输出电阻的特性,能够将输入信号源与负载之间进行有效的匹配。

总结起来,晶体管放大原理通过控制输入信号电压来改变晶体管的输出电流,从而实现信号放大。

晶体管具有高增益、高输入电阻和低输出电阻的特性,因此在电子设备中得到了广泛的应用。

贝尔实验室晶体管 原理

贝尔实验室晶体管原理

贝尔实验室晶体管的原理主要是通过控制材料内的电子流,实现对电路的放大和控制。

1947年12月23日,威廉·肖克利、约翰·巴丁和沃尔特·布拉顿在美国贝尔实验室发现了一种新型半导体器件——晶体管。

他们在实验室中使用了一个硅片和几根金属线制作出了世界上第一个晶体管。

晶体管的基本原理是“放大”,即用小电流去控制大电流。

此外,贝尔实验室在20世纪50年代还推动了数字交换机、金属氧化物半导体场效应晶体管(MOSFET)等重大发明,这些都体现了晶体管在电子技术中的重要作用和其背后的物理原理。

晶体管原理 (1-2)

得 :

kT 将 = 0.026V, ND1 =1×1020 cm−3, ND2 =1×1016 cm−3 q 代 , : bi = 0.026ln(104 ) = 0.24V 入 得 V

7、由第6 题: kT 1 dn kT 1 dN(x) E =− ⋅ ⋅ =− ⋅ ⋅ q n dx q N(x) dx x kT 将 N(x) = N0 exp(− ) 代入,得:E = λ qλ kT 再将 = 0.026 V, λ = 0.4µm 代入,得:E = 650 V cm q 2qN0Vbi 突变结 的最大电场强度表达式为:| Emax |= εs N N kT N N N 式中: 0 = D A ≈ ND =1015 cm−3, Vbi = ln D 2 A = 0.757V, ND + NA q ni q =1.6×10−19 C, εS =1.045×10−12 F cm, 代入 | Emax | 中,得:| Emax |=1.52×104 V cm

34、 、

已知 对于 单边突 变结 , εsqN0 K CT = A = 1 2(Vbi −V ) (Vbi −V ) 2 K 当 Vbi = 0.6V, V = −3V时 CT = , =10 pF, 由此 可得 3.6 K =10 3.6, 因此 V = 0.2V时 当 , 10 3.6 CT = =10 9 = 30 (pF) 0.4

qDEni2 qVBE AEq2DEni2 qVBE JpE = WE exp kT −1 = Q exp kT −1 EO ∫ NEdx

0

再根据注入效率的定义,可得: 再根据注入效率的定义,可得:

JpE QBODE JnE JnE γ= = = 1+ = 1+ JE JnE + JpE JnE QBEDB

晶体管的结构和原理

晶体管的结构和原理

晶体管是一种电子器件,被广泛应用于现代电子技术中。

晶体管由三个区域构成,分别是P型半导体、N型半导体和一块绝缘层。

晶体管主要包括结型晶体管和场效应晶体管两种类型。

结型晶体管有两个PN结组成,其中一个PN结为基极区,另一个PN结为集电区。

这两个PN结之间的N型半导体区域为发射区。

当PN结接收到一些信号时,会在N型半导体区域内产生电子-空穴复合,使电子进入P型区域,发射区产生电流,最终进入集电区,因此实现了从基极到集电区的电流放大。

场效应晶体管包括源极、栅极和漏极。

源极和漏极之间有一段N型半导体通道,塞隆区通常用来控制源极和漏极之间的电流。

当栅极施加电压时,可以通过电子引入通道的电场来控制通道的导电性能。

这些技术可以实现信号放大以及在许多电子设备中完成控制和开关操作。

晶体管具有很多优点,例如占用空间小、高速度、低功耗、工作稳定、价格低廉等。

晶体管的应用范围非常广泛,包括计算机、计算器、电视、手机、电脑等电子设备,以及通信、医疗、航空航天、军事和科学研究等领域。

2-1结型场效应晶体管的工作原理

iD f uGS uDS C

输出特性曲线:

iD f uDS uGS C

8

结型场效应管的大信号分析(特性曲线)

(1)转移特性曲线 iD f (uGS ) uDS C

I DSS

D

iD /mA 5

4

3

UDS

P

P

2

1

UGS UGSoff-3 -2 -1 0

S 问题:若UDS增大,转移特性曲线如何变化?

时,在靠漏极处夹断——预夹断。 ④UDS再↑,预夹断点下移。

6

结型场效应管的工作原理(2)

南京邮电大学 电子科学与工程学院

结型场效应管的大信号分析(特性曲线)

特性曲线是描述场效应管各极电流与极间电压关系的曲线。在JFET工作 时,通常将UGS、IG作为输入电压、电流,而UDS和ID看作输出电压和电流。

iD

I DSS (1

uGS UGSoff

)2

式中:IDSS——饱和电流,表示uGS=0时的iD值;

UGSoff——夹断电压,表示uGS=UGSoff时iD为零。

13

iD/mA

4 3

可 变

uDS= uGS-UGSoff

UGS=0V

电 阻

恒

-0.5V

击 穿

区 2

流

-1V

区

-1.5V

区

1

-2V

0

UGSoff

流

-1V

2

区

-1.5V

1

-2V

0

5

10截止区15

20

10

击 穿 区

UGSoff uDS /V

结型场效应管的大信号分析(2)

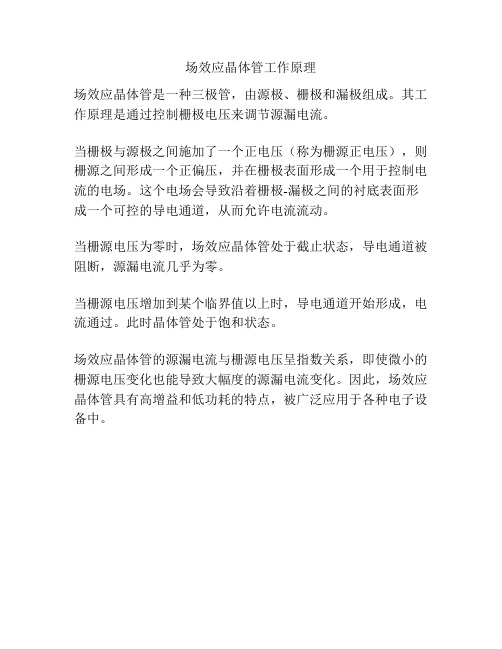

场效应晶体管工作原理

场效应晶体管工作原理

场效应晶体管是一种三极管,由源极、栅极和漏极组成。

其工作原理是通过控制栅极电压来调节源漏电流。

当栅极与源极之间施加了一个正电压(称为栅源正电压),则栅源之间形成一个正偏压,并在栅极表面形成一个用于控制电流的电场。

这个电场会导致沿着栅极-漏极之间的衬底表面形成一个可控的导电通道,从而允许电流流动。

当栅源电压为零时,场效应晶体管处于截止状态,导电通道被阻断,源漏电流几乎为零。

当栅源电压增加到某个临界值以上时,导电通道开始形成,电流通过。

此时晶体管处于饱和状态。

场效应晶体管的源漏电流与栅源电压呈指数关系,即使微小的栅源电压变化也能导致大幅度的源漏电流变化。

因此,场效应晶体管具有高增益和低功耗的特点,被广泛应用于各种电子设备中。

晶体管工作原理

晶体管工作原理

晶体管是一种半导体元件,用于控制和放大电流。

它由三个不同类型的半导体材料组成:P型半导体、N型半导体和掺杂的

中间层(一般用砷或氮等元素掺杂的硅材料)。

晶体管的工作原理基于PN结的特性,即P型和N型半导体之间形成的界面。

在晶体管中,有三个区域:发射区(Emitter)、基极区(Base)和集电区(Collector)。

发射区和集电区都是N型半导体,而基极区是P型半导体。

当正向偏置电压施加在PN结上时,形

成一个正电荷在P型半导体和N型半导体之间的空间,这使

得发射区的电流开始流动。

当一个信号电流施加在基极区时,这会改变PN结上的空间电

荷层,从而影响发射区和集电区之间的电流。

这是因为基极区的信号电流能够控制PN结的电流通过,并进一步影响整个晶

体管的电流传输。

当信号电流增加时,发射区的电流也相应增加。

晶体管的放大效果是通过控制基极区的信号电流和集电区的电压来实现的。

基极区的电流负责控制晶体管的输出,并将输入信号放大。

当信号电流增加时,集电区之间的电流也会增加。

因此,晶体管可以实现信号的放大效果。

总的来说,晶体管的工作原理是利用PN结的性质来控制和放

大电流。

通过控制基极区的电流和集电区的电压,晶体管可以放大输入信号。

这使得晶体管广泛应用于各种电子设备中,如计算机、电视、电话等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第二章 PN结填空题1、若某硅突变PN结的P型区的掺杂浓度为N A=1.5×1016cm-3,则室温下该区的平衡多子浓度p p0与平衡少子浓度n p0分别为()和()。

2、在PN结的空间电荷区中,P区一侧带()电荷,N区一侧带()电荷。

内建电场的方向是从()区指向()区。

3、当采用耗尽近似时,N型耗尽区中的泊松方程为()。

由此方程可以看出,掺杂浓度越高,则内建电场的斜率越()。

4、硅突变结内建电势V bi可表为(),在室温下的典型值为()伏特。

5、当对PN结外加正向电压时,其势垒区宽度会(),势垒区的势垒高度会()。

6、当对PN结外加反向电压时,其势垒区宽度会(),势垒区的势垒高度会()。

7、在P型中性区与耗尽区的边界上,少子浓度n p与外加电压V之间的关系可表示为()。

若硅P 型区的掺杂浓度N A=1.5×1017cm-3,外加电压V= 0.52V,则P型区与耗尽区边界上的少子浓度n p为()。

8、当对PN结外加正向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度();当对PN结外加反向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度()。

9、PN结的正向电流由()电流、()电流和()电流三部分所组成。

10、PN结的正向电流很大,是因为正向电流的电荷来源是();PN结的反向电流很小,是因为反向电流的电荷来源是()。

11、PN结扩散电流的表达式为()。

这个表达式在正向电压下可简化为(),在反向电压下可简化为()。

12、在PN结的正向电流中,当电压较低时,以()电流为主;当电压较高时,以()电流为主。

13、薄基区二极管是指PN结的某一个或两个中性区的长度小于()。

在薄基区二极管中,少子浓度的分布近似为()。

14、势垒电容反映的是PN结的()电荷随外加电压的变化率。

PN结的掺杂浓度越高,则势垒电容就越();外加反向电压越高,则势垒电容就越()。

15、扩散电容反映的是PN结的()电荷随外加电压的变化率。

正向电流越大,则扩散电容就越();少子寿命越长,则扩散电容就越()。

16、PN结的击穿有三种机理,它们分别是()、()和()。

17、PN结的掺杂浓度越高,雪崩击穿电压就越();结深越浅,雪崩击穿电压就越()。

18、雪崩击穿和齐纳击穿的条件分别是()和()。

19、PN结的低掺杂一侧浓度越高,则势垒区的长度就越(),内建电场的最大值就越(),内建电势V bi 就越(),反向饱和电流I0就越(),势垒电容C T就越(),雪崩击穿电压就越()。

问答题1、简要叙述PN结空间电荷区的形成过程。

2、什么叫耗尽近似?什么叫中性近似?3、PN结势垒区的宽度与哪些因素有关?4、写出PN结反向饱和电流I0的表达式,并对影响I0的各种因素进行讨论。

5、PN结的正向电流由正向扩散电流和势垒区复合电流组成。

试分别说明这两种电流随外加正向电压的增加而变化的规律。

当正向电压较小时以什么电流为主?当正向电压较大时以什么电流为主?第三章双极结型晶体管填空题1、晶体管的基区输运系数是指()电流与()电流之比。

为了提高基区输运系数,应当使基区宽度()基区少子扩散长度。

2、晶体管中的少子在渡越()的过程中会发生(),从而使到达集电结的少子比从发射结注入基区的少子()。

3、晶体管的注入效率是指()电流与()电流之比。

为了提高注入效率,应当使()区掺杂浓度远大于()区掺杂浓度。

4、晶体管的共基极直流短路电流放大系数 是指发射结()偏、集电结()偏时的()电流与()电流之比。

5、晶体管的共发射极直流短路电流放大系数β是指()结正偏、()结零偏时的()电流与()电流之比。

6、在设计与制造晶体管时,为提高晶体管的电流放大系数,应当()基区宽度,()基区掺杂浓度。

7、在缓变基区晶体管的基区中会产生一个(),它对少子在基区中的运动起到()的作用,使少子的基区渡越时间()。

8、小电流时α会()。

这是由于小电流时,发射极电流中()的比例增大,使注入效率下降。

9、当晶体管处于放大区时,理想情况下集电极电流随集电结反偏的增加而()。

但实际情况下集电极电流随集电结反偏增加而(),这称为()效应。

10、I ES是指()结短路、()结反偏时的()极电流。

11、I CS是指()结短路、()结反偏时的()极电流。

12、I CBO是指()极开路、()结反偏时的()极电流。

13、I CEO是指()极开路、()结反偏时的()极电流。

14、I EBO是指()极开路、()结反偏时的()极电流。

15、BV CBO是指()极开路、()结反偏,当()→∞时的V CB。

16、BV CEO是指()极开路、()结反偏,当()→∞时的V CE。

17、BV EBO是指()极开路、()结反偏,当()→∞时的V EB。

18、基区穿通是指当集电结反向电压增加到使耗尽区将()全部占据时,集电极电流急剧增大的现象。

防止基区穿通的措施是()基区宽度、()基区掺杂浓度。

19、比较各击穿电压的大小时可知,BV CBO()BV CEO,BV CBO()BV EBO。

20、要降低基极电阻r bb',应当()基区掺杂浓度,()基区宽度。

21、发射极增量电阻r e的表达式是()。

室温下当发射极电流为1mA时,r e =()。

22、随着信号频率的提高,晶体管的αω, βω的幅度会(),相角会()。

是指()。

当基区宽度加倍时,基区渡越时间增大到原23、基区渡越时间τb来的()倍。

24、晶体管的共基极电流放大系数|αω|随频率的()而下降。

当晶体管的|αω|下降到()时的频率,称为α的截止频率,记为()。

25、晶体管的共发射极电流放大系数|βω|随频率的()而下降。

当晶体管的|βω|下降到β0时的频率,称为β的(),记为()。

26、当f>>fβ时,频率每加倍,晶体管的|βω|降到原来的();最大功率增益K pmax降到原来的()。

27、当()降到1时的频率称为特征频率f T。

当()降到1时的频率称为最高振荡频率f M。

28、晶体管的高频优值M是()与()的乘积。

29、晶体管在高频小信号应用时与直流应用时相比,要多考虑三个电容的作用,它们是()电容、()电容和()电容。

中以()为主,这时提高特征频率f T的主要措施是()。

30、对于频率不是特别高的一般高频管,τec31、为了提高晶体管的最高振荡频率f M ,应当使特征频率f T(),基极电阻r bb'(),集电结势垒电容C TC()。

问答题1、画出共基极放大区晶体管中各种电流的分布图,并说明当输入电流I e经过晶体管变成输出电流I C时,发生了哪两种亏损?2、倒向晶体管的电流放大系数为什么小于正向晶体管的电流放大系数?3、说明特征频率f T的测量方法。

12、在材料种类相同,掺杂浓度分布相同,基区宽度相同的条件下,PNP晶体管和NPN晶体管相比,哪种晶体管的发射结注入效率γ较大?哪种晶体管的基区输运系数β* 较大?13、有人在测晶体管的I CEO的同时,错误地用一个电流表去测基极与发射极之间的浮空电势,这时他声称测到的I CEO实质上是什么?15、在某偏置在放大区的NPN晶体管的混合π参数中,假设Cπ完全是中性基区载流子贮存的结果,Cμ完全是集电结空间电荷区中电荷变化的结果。

试问:(1) 当电压V CE维持常数,而集电极电流I C加倍时,基区中靠近发射结一侧的少子浓度n B(0)将加倍、减半、还是几乎维持不变?基区宽度W B将加倍、减半、还是几乎维持不变?(2) 由于上述参数的变化,参数R bb'、Rπ、g m、Cπ、Cμ将加倍、减半、还是几乎维持不变?(3) 当电流I C维持常数,而集电结反向电压的值增加,使基区宽度W B减小一半时,n B(0)将加倍、减半还是几乎维持不变?第五章绝缘栅场效应晶体管填空题1、N沟道MOSFET的衬底是()型半导体,源区和漏区是()型半导体,沟道中的载流子是()。

2、P沟道MOSFET的衬底是()型半导体,源区和漏区是()型半导体,沟道中的载流子是()。

3、当V GS=V T时,栅下的硅表面发生(),形成连通()区和()区的导电沟道,在V DS的作用下产生漏极电流。

4、N沟道MOSFET中,V GS越大,则沟道中的电子就越(),沟道电阻就越(),漏极电流就越()。

5、在N沟道MOSFET中,V T>0的称为增强型,当V GS=0时MOSFET处于()状态;V T<0的称为耗尽型,当VGS=0时MOSFET处于()状态。

6、由于栅氧化层中通常带()电荷,所以()型区比()型区更容易发生反型。

7、要提高N沟道MOSFET的阈电压V T ,应使衬底掺杂浓度n A(),使栅氧化层厚度T ox()。

8、N沟道MOSFET饱和漏源电压V Dsat的表达式是()。

当V DS>=V Dsat时,MOSFET进入()区,漏极电流随V DS的增加而()。

9、由于电子的迁移率μn 比空穴的迁移率μp(),所以在其它条件相同时,()沟道MOSFET的I Dsat比()沟道MOSFET的大。

为了使两种MOSFET的I Dsat相同,应当使N沟道MOSFET的沟道宽度()P沟道MOSFET 的。

10、当N沟道MOSFET的V GS<V T时,MOSFET()导电,这称为()导电。

11、对于一般的MOSFET,当沟道长度加倍,而其它尺寸、掺杂浓度、偏置条件等都不变时,其下列参数发生什么变化:V T()、I Dsat()、R on()、g m()。

12、由于源、漏区的掺杂浓度()于沟道区的掺杂浓度,所以MOSFET源、漏PN结的耗尽区主要向()区扩展,使MOSFET的源、漏穿通问题比双极型晶体管的基区穿通问题()。

13、MOSFET的跨导g m的定义是(),它反映了()对()的控制能力。

14、为提高跨导g m的截止角频率ωgm,应当()μ,()L,()V GS。

15、阈电压V T的短沟道效应是指,当沟道长度缩短时,V T变()。

16、在长沟道MOSFET中,漏极电流的饱和是由于(),而在短沟道MOSFET中,漏极电流的饱和则是由于()。

17、为了避免短沟道效应,可采用按比例缩小法则,当MOSFET的沟道长度缩短一半时,其沟道宽度应(),栅氧化层厚度应(),源、漏区结深应(),衬底掺杂浓度应()。

问答与计算题1、画出MOSFET的结构图和输出特性曲线图,并简要叙述MOSFET的工作原理。

2、什么是MOSFET的阈电压V T?写出V T的表达式,并讨论影响V T的各种因素。

3、什么是MOSFET的衬底偏置效应?4、什么是有效沟道长度调制效应?如何抑制有效沟道长度调制效应?5、什么是MOSFET的跨导g m?写出g m的表达式,并讨论提高g m的措施。