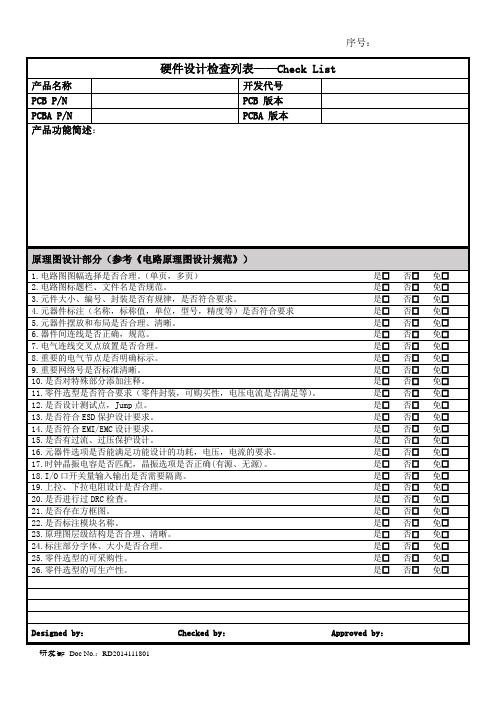

原理图checklist

硬件-原理图布线图-设计审核表

23.当前版本的BOM是否需要变更确认。BOM 版本:_______, ECN:_________

是否免

24.过流保护是否工作正常,是否可靠

25.过压保护是否工作正常,是否可靠

Designedby:

Checkedby:

Approvedby:

是否免

4.元器件标注(名称,标称值,单位,型号,精度等)是否符合要求

是否免

5.元器件摆放和布局是否合理、清晰。

是否免

6.器件间连线是否正确,规范。

是否免

7.电气连线交叉点放置是否合理。

是否免

8.重要的电气节点是否明确标示。

是否免

9.重要网络号是否标准清晰。

是否免

10.是否对特殊部分添加注释。

是否免

11.零件选型是否符合要求(零件封装,可购买性,电压电流是否满足等)。

是否免

5.去耦电容摆放位置是否符合要求。

是否免

6.线宽,线距,GAP是否满足要求。

是否免

7.走线是否存在锐角、直角。

是否免

8.高频信号走线是否符合标准。

是否免

9.是否存在阻抗匹配要求。 阻抗匹配要求:

是否免

10.电源,GND是否符合要求。

是否免

11.器件PAD、焊盘大小是否符合要求。

是否免

12.过孔,通孔是否符合要求。

是否免

19.是否进行长时间可靠性测试(>=48H)。

是否免

20.当前版本是否需要Rework。ECN:___________________

是否免

21.当前版本原理图是否需要变更。原理图版本:________

是否免

22.当前版本PCB布线图是否需要变更。PCB版本:_______, ECN:_________

手机射频原理图和Layout的部分Checklist

手机射频原理图和Layout的部分Checklist1.电源(给相关器件供电):滤波电容靠近相关器件的管脚。

滤波电容:在直流电源正负极之间,用于滤除交流,使直流电平滑。

导线越长,电阻、电感、电容就会越大,这些都是不利于电源的输送,所以导线越短越好、越粗越好,滤波电容靠近芯片能最好地滤除干扰,如果离得太远就会受到二次干扰。

2.电源(给相关器件供电):滤波电容的摆放顺序为低容值靠近芯片。

小电容如果放的很远的话,由于导线是有电感、电阻的,这时对高频信号就会滤波不良,效果不好,也就是用错了。

因此,小电容则必须尽量靠近IC引脚放置。

大的滤低频,小的滤高频因为大电解是卷起来的长铝箔,自身电感很大,高频阻抗很大;而小的则自身分布电感小很多,所以能过高频;3.PA,2G_PA电源上面预留0603封装22uF大电容。

(备注10uF)在Buzz6T 4G Gophone项目中,预留位置,但是并没有使用,NC。

(给PA供电的)PA电源PA对电源的要求比较高,加上这个大电容是为了提高电源的性能。

大电容滤掉PA产生的217Hz的电源纹波,使PA的供电电压保持稳定。

否则输出的功率会变化,引起功率的振荡。

考虑1:容值一般是越大约好,这个大电容是储能电容(bulk capacitor), 不是高频电容,理论上是越大PA电源纹波就会越小。

GSMPA 用几十uF就够了。

一般使用较多的6.3V/22uF的就可以。

如果考虑成本,差不多大就可以了。

这个电容体积大,一般不放在射频屏蔽罩里。

放在电池接触点附近。

现在一般新的PA,靠近电源脚放一个10UF的电源就可以兼顾TX 杂散的性能了,不过靠近电源连接器还是需要22UF左右的TAN电容,是防止bb或其他电路的电流回灌。

考虑2:耐压大一些,高于电池的电压加些余量,一般耐压>=6.3V。

考虑3:材质。

陶瓷或者钽电容都可。

成本为先。

考虑4:注意 ESR must low enough 一般<150u比较好此电容对功放的线性有很大的影响,以CDMAPA为例,如果没有这电容,ACPR 要坏几个dB.此电容值通常uF级,因为要对低频滤波,象CDMA,邻道间隔(offsetfrequency)<1MHz,此电容阻抗要对1MHz足够小。

流片前的checklist

流片前的Check List◆驱动/负载检查1.要对金属线、via,contact的电流负载能力进行检查;2.检查输出管脚的驱动能力是否足够。

可在仿真时在输出端追加5p 电容为负载(作为PAD的等效电容),观察驱动能力是否足够;3.信号线接到数字PAD之前至少要添加一个W/L为20的buffer以提高驱动能力。

4.在面积允许的情况下,via和contact打越多越好,尤其是input/output部分;◆IO检查1.对IO分类,不同供电电位的IO分开接不同电位的IO power ring.混合信号电路尤其要注意这点;2.检查IO上的IO power ring是否正确接到电源和地上;3.检查各PAD上的pin是否和core里的pin正确连接;4.IO的布局要注意不要将输入弱信号和强信号的IO放置在一起,这样弱信号会受到强信号的干扰。

5.根据PAD连接到core的金属层次确保连接PAD与core。

6. IO PAD间距除要满足设计规则外,还必须满足封装厂的要求,比如最小压焊尺寸(60um*60um),最小中心间距(80um)等。

7.IO直接相连的输出管要保证Drain到Poly足够的距离,大于等于1.5um为宜,或者加上SAB层,以保证足够的ESD可靠性。

8.数字要通过带IO的后仿真,防止发生IO上使能端的连接错误。

9.从自动布局布线软件(如Astro)导出GDS文件,再导入Virtuso 做DRC前,要将版图中得IO替换为Foundry(如smic)提供的完整的IO gds文件导出来的IO库单元中的IO(包括PADFILLER),防止出现额外的逻辑操作层,如HTNWL。

走线检查1.金属连线不宜过长,如果不得已需要长连线可以在中间添加buffer 提高驱动能力;2.数字电路的走线不要经过模拟电路的器件,否则容易引入强干扰,影响模拟电路正常工作。

反之模拟电路走线也不要经过数字电路。

3.数模混合信号电路中模拟电路外边最好加入隔离环,必要时需要用单独的管脚为隔离环接地或接电源电压。

手机硬件设计Checklist-1

人工检查

15

FPC的设计应该保证每4~8根信号线就有一个地线, 如果有些信号的电流比较大,或者频率比较高,还 需要额外的包地线。

基带硬件 PCB

电源模块 布局布线 设计

原理图设 计

人工检查

对于有串联滤波网络的接口,除非滤波网络有特殊

ESD/EMI防

16

要求,并且滤波网络有足够的通流能力。否则防护 器件应该放在滤波网络和连接器之间,避免防护器

基带硬件 各种接口 原理图 功能模块

各种接口 功能模块

人工检查

电路中的MLCC电容耐压需要满足以下要求:当工作

27

电压大于等于5V时,所选电容要求降额达到60%,低 于5V,电容降额要求达到80%。Polymer钽电容耐压 要求:电压降额要求满足80%。电感、磁珠等的温升

基带硬件 原理图

电源管理 模块

计

11

ห้องสมุดไป่ตู้

防护器件要放在接口最入口处,但和射频天线冲突

时,可以适当调整。比如串联电感到Speaker,可以 把电感放在防护器件和Speaker之间,但必须考虑电 感的防静电能力,并且电感要放在Speaker附近,周

基带硬件 PCB

围没有其他可能间接放电的静电路径(地除外)

ESD/EMI防 护电路布 局布线设 计

序号

设计准则

主题 子主题 技术类别 检查方式

1

如果充电底座接口没有防呆结构设计防止正负极反 基带硬件 电源管理

接,则接口电路设计应该包含防反接保护电路

原理图 模块

原理图设 计

人工检查

2

在固定台手机中,要在听筒螺旋线接口处使用TVS或 基带硬件 音频功能

者对地并接电容进行防护;

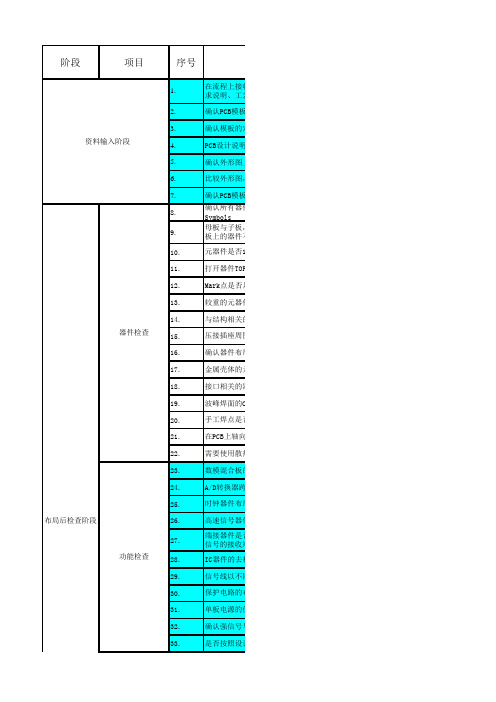

很全面的PCB_checklist_表格

5.

确认外形图上的禁止布放器件和布线区已在PCB模板上体现

6.

比较外形图,确认PCB所标注尺寸及公差无误, 金属化孔和非金属化孔定义准确

7.

确认PCB模板准确无误后最好锁定该结构文件,以免误操作被移动位置

8.

确认所有器件封装是否与公司统一库一致,是否已更新封装库(用viewlog检查运行结果) Symbols

0805及其以下封装求的丝印添加是否正确置有防静电和射频板标识射频板使用的插板方向标识是否对应确标识了槽位名槽位号端口名称护套方向否遗漏位置是否能正确标识器件否符合公司标准要求管脚排列顺序第1脚标志器件的极性标志连接器的方向标识的正确性盘安装的chip元件0805及其以下封装如电阻电容与其焊盘连接的印制线最好从焊盘中心位置对与焊盘连接的印制线必须具有一样的宽度对于线宽小于03mm12mil的引出线可以不考虑此条规定从soicplccqfpsot等器件的焊盘的两端引出板边推荐为大于2mm最小为05mm皮到板边12mm最小为05mm孔径最好不小于板厚的110是否100布通率是否100没有达到100的需要在备注中说明测试点的网络都是经确认可以进行精简的时应该尽量避免出现没有网络连接的死铜孤岛还需注意是否有非法连线未报告的drcottom上的大面积铜箔如无特殊的需要应用网格铜单板用斜网背板用正交网线宽03mm12距05mm20mil区的元件焊盘应设计成花焊盘以免虚焊

29.

信号线以不同电平的平面作为参考平面,当跨越平面分割区域时,参考平面间的连接电容

30.

保护电路的布局是否合理,是否利于分割

31.

单板电源的保险丝是否放置在连接器附近,且前面没有任何电路元件

32.

确认强信号与弱信号(功率相差30dB)电路分开布设

CHECKLIST- EE原理图设计检查

一、Power SCH

Item Number 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 检查项目 确保所有的电源转换模块OCP/OVP点设定正确 MLCC电容耐压值至少要按照2倍选择 相数是否足够,能提供足够大的电流、功率給CPU,Chipset等 PWM单相频率范围是200K-600K;集成MOS的可以达到1MHz Input ECAP的Ripple current(参考2700mA) Output ECAP的ESR是否足够小 所有用在12V电源上的Ecap耐压值>=16V H-Side MOSFET要选择导通速度快的 L-Side MOSFET要选择Rds(on)低的 Linear mode 的损耗P=Δv*i,一般,1颗LDO可承受的功率损耗 Pmax*Junction=器件Temp,保证器件temp与环境Temp之和小于 MOS的最大工作温度的80%。 单板上同一电源和地名称要统一 单相PWM driver 的BOOT Pin与phase端接0.1uF电容.核对BOOT电 容,是否耐压值为50V H-side Gate上预留0ohm电阻. Feedback电路设置是否准确 GND和AGND电路要分开,但最后要通过一点进行连接。如果是 chipset的 AGND电流很大,可直接与GND相连,不需要连接0OHM, 否则通流不够。 PWROK的Pull high要用本身的power去做。 第一次画power原理图要加上GAP,方便调试。(所有Power的 Enable信号可以预留一个Gap,方便Power调试) 有些模块线路copy过来后,需要注意AGND属性要更改,最好能赋 予net名字,比如经常会遇到两个P1V1的AGND起的名字一样。 确认电感封装,核对饱和电流是否满足电路需求。电感封装越 大,过电流能力越强,电感的饱和电流应该大于电路的OCP电流 。 确认补偿线路,保证足够的穿越频率,以及相位裕度。 核对LDO的最大压差是否满足SPEC要求(input&output) Designer Check OK NG

Hi3535 硬件设计 Checklist

文档版本 00B04 (2014-04-02)

海思专有和保密信息 版权所有 © 深圳市海思半导体有限公司

i

Hi3535 硬件设计 Checklist

修订日期 2013-11-12

2013-09-30

2013-08-31

版本 00B03 00B02 00B01

修订说明

第 1 章 Checklist 1.1 芯片电源地的设计要求修改描述。 第 1 章 Checklist 1.1 芯片电源地的设计要求修改上电顺序。 初始版本。

修订记录累积了每次文档更新的说明。最新版本的文档包含以前所有文档版本的更新 内容。

修订日期 2014-04-02

版本 00B04

修订说明

第 1 章 Checklist 1.7 VO 接口与视频接口电路设计要求中新增 BT.1120 信号 高 8bit 和低 8bit 关于 Y\C 信号的描述。 1.15 EFuse 模块设计要求中修改下拉电阻的阻值。

深圳市海思半导体有限公司

地址: 网址: 客户服务电话: 客户服务传真: 客户服务邮箱:

深圳市龙岗区坂田华为基地华为电气生产中心 +86-755-28788858 +86-755-28357515 support@

邮编:518129

1.5 SPI/Nand flash

1.1 芯片电源地的设计要求 ................................................................................................................................. 1 1.2 主芯片时钟电路设计要求 ............................................................................................................................. 1 1.3 复位电路设计要求......................................................................................................................................... 2 1.4 小系统设计要求............................................................................................................................................. 2 1.5 SPI/Nand flash ................................................................................................................................................. 2 1.6 I2C 电路设计要求............................................................................................................................................ 2 1.7 VO 接口与视频接口电路设计要求 ............................................................................................................... 3 1.8 I2S 音频电路设计要求 .................................................................................................................................... 3 1.9 USB2.0 电路设计要求 .................................................................................................................................... 3 1.10 USB3.0 电路设计要求 .................................................................................................................................. 4 1.11 SATA 接口电路要求 ..................................................................................................................................... 4 1.12 ETH 电路设计要求 ....................................................................................................................................... 4 1.13 JTAG 和系统控制电路设计要求.................................................................................................................. 5 1.14 UART 电路设计要求 .................................................................................................................................... 5 1.15 EFuse 模块设计要求..................................................................................................................................... 5 1.16 HDMI 设计 .................................................................................................................................................... 6 1.17 散热设计....................................................................................................................................................... 6

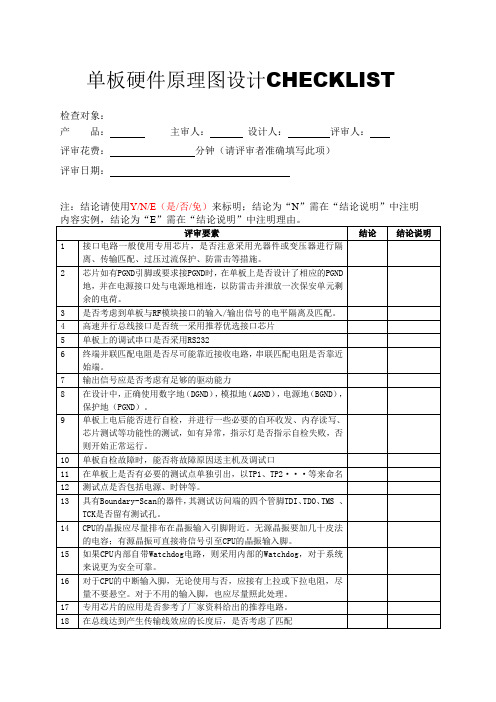

硬件原理图设计-CHECKLIST

在防雷、瞬态抑制保护的前级是否有合理的过流保护

40

在设计方案中是否采用了共模、差摸噪波抑制措施

41

在输入回路中是否设计了过、欠压保护

42

单板器件的工作温度是否控制在允许的范围内

43

单板上的散热设计是否安全可靠

44

电源EMI滤波器是否安装在系统屏蔽体的入口

45

需要进行防护的电信号接口是否都具备防护电路;

15

如果CPU内部自带Watchdog电路,则采用内部的Watchdog,对于系统来说更为安全可靠。

16

对于CPU的中断输入脚,无论使用与否,应接有上拉或下拉电阻,尽量不要悬空。对于不用的输入脚,也应尽量照此处理。

17

专用芯片的应用是否参考了厂家资料给出的推荐电路。

18

在总线达到产生传输线效应的长度后,是否考虑了匹配

26

所有器件功率、频率、驱动能力已降额设计

27

TVS等保护器件应和被保护器件接同一个地(一般是GND)

28

CMOS器件其不用输入端应接上拉/下拉电阻使其输入电平固定,既不能悬空也不应直接接VCC或GND

29

CMOS器件和TTL器件的电平兼容,TTL输出不能驱动CMOS输入

30

两个电源的输出不能直接并联使用

19

关键信号是否引到接插件或预留了测试点

20

PCB、单板软件的版本信息是否都在各自范围内设计,并可上报

21

单板的关键芯片是否支持自测试计是否统一考虑;

23

单板上电后的芯片的初始状态是否固定

24

单板上接插件的间距和位置是否参考同类成熟单板

25

单板所有器件选型是否通过品质和商务清单评审。

46

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

滤波电容的设计要关注对控制管脚的影响。

电容

没有使用的管脚如何使用需要参考芯片手册和demo板的设计去关注这些管脚的设计是否合理。

特征阻抗

对PCB布线的特征阻抗有特殊要求时,需要在原理图或者给互连工程师的需求文档中进行特殊说明。

复位设计

关键功能器件应该预留独立的复位设计。

复位设计

很多Flash都有rst的管脚,为满足启动阶段的软件功能实现要求,在

OD门

芯片的OD门或者OC门的输出管脚需要上拉

匹配

高速信号的始端和末端需要预留串阻

三极管

三极管电路需要考虑通流能力

可测试性

在单板的关键电路和芯片附近增加地孔,便于测试

连接器防呆

连接器选型时需要选择有防呆设计的型号

仿真

低速时钟信号,一驱动总线接口下挂器件的驱动能力、匹配方式、接口时序必须经过仿真确认,例如MDC/MDIO、IIC、PCI、Local bus

缓启

热插拔电路要进行缓启动设计

磁珠

小电压大电流(安培级)值电源输出端口的磁珠,需要考虑磁珠压降

连接器

板间电源连接器通流能力及压降留有预量

标识

扣板与母板插座网络标识是否一致,前后插卡连机器管脚信号要一一对应。

电平匹配

一驱多信号要根据仿真结果进行阻抗匹配,确定是否加始端或末端匹配电阻

匹配电平

原理图设计要关注厂家器件资料的说明,输入输出都会有明确的匹配要求。

时钟

确认信号摆幅,jitter等是否超出器件要求。

时钟

确认时钟器件在中心频率、工作电压、输出电平、占空比、相位等各项指标上能完全满足要求。

DDR

DDR等存储器接口都要有时钟RAM开发中满足ECC设计规则要求。

DDR

DDR的VTT电源滤波要做到Vtt电阻和绿宝电容的搭配。

散热器

选择散热器时,要考虑到散热器的重量和与设备的结合方式。

I2C

设备通过I2C进行互联时,可以使用芯片I2C模块,也可以通过I2C模块。

电容

单板中射频相关部分设计的时候,需要旁路,滤波电容,针对不同的干扰频率要选择不同容值的滤波电容。

电容

电容并联设计时,要计算或通过仿真分析谐振点,避免可能会出现的谐振问题。

PHY

MDC/MDIO采用一驱多的匹配方式,主器件经过串阻-》上拉电阻-》串阻到从器件,串阻要放置在两端。

PHY

1对多的控制,PHY需要预留地址信号,用于控制。

PHY

CAM等芯片功耗根据访问条件和温度,功耗变化较大,设计时要要仔细查询器件手册,明确功耗和厂家芯片的关系。

PHY

设备有光模块接口是,光模块部串接10nf电容,链路不需要进行重复设计。

单网络

原理图中所有单网络需要做一一确认。

空网络

原理图中所有空网络需要做一一确认。

网格

1、原理图绘制中要确认网格设置是否一致。

2、原理图中没有网格最小值设置不一致造成网络未连接的情况。

网络属性

确认网络是全局属性还是本地属性

封装库

1、原理图中器件的封装与手册一致。

2、原理图器件是否是标准库的symbol。

原理图checklist

类别

描述

检视规则

原理图需要进行检视,提交集体检视是需要完成自检,确保没有低级问题。

检视规则

原理图要和公司团队和可以邀请的专家一起进行检视。

检视规则

第一次原理图发出进行集体检视后所有的修改点都需要进行记录。

检视规则

正式版本的原理图在投板前需要经过经理的审判。

差分网络

原理图中差分线的网络,芯片管脚处的P和N与网络命令的P和N应该一一对应。

复位信号设计

(1)依据芯片要求进行上下拉

(2)确认芯片复位的默认状态

(3)Peset信号并联几十PF的电容滤波,优化信号质量。

(4)复位信号保证型号完整性。

复位

所有接口和光模块默认处于复位状态。

电平匹配

不同电平标准互连,关注电压、输入输出门限、匹配方式。

功耗

详细审查各个芯片的功耗设计,计算出单板各个电压的最大功耗,选择有一定余量的电源。

绘制要求

原理图中器件的封装与手册一致。

指示灯

设计默认由电源点亮的指示灯和由MCU点灭的指示灯,便于故障时直观判断电源问题还是MCU问题

网口连接器

确认网口连接器的开口方向、是否带指示灯以及是否带PoE

网口变压器

确认变压器选型是否满足需求,比如带PoE

按键

确认按键型号是直按键还是侧按键

电阻上下拉

同一网络避免重复上拉或者下拉

244/245

244/245如果不带保持功能,则必须将不用的输入管脚上下拉。

时钟

晶振管脚直接输出的信号禁止直接1驱多,多个负载会影响信号质量,建议采用1对1的方式。

时钟

晶体的xt-out和时钟驱动器相连需要0402串阻,阻值选择不能影响单板起震。

时钟

锁相环电路及参数的选取必须经过专项计算。

时钟

时钟环路滤波瓷电容优选NPO介质电容。

射频电路

射频器件功率放大器的中心散热焊盘在原理图上必须接地。

射频电路

具备on/off的射频器件功能,在off状态下隔离度有问题,隔离度影响收发的干扰情况,干扰信号需要保持在合理电平,否则影响套片正常工作。

射频电路

PA的RF发送端链路PA外围电路正价负反馈设计防止烧PA。

二级管

使用在控制、检测、电源合入等电路中的二极管,必须考虑二极管反向漏电流是否满足设计要求。

MOS

CMOS器件未使用的输入/输出管脚需按照器件手册要求处理,手册未要求的必须与厂家确认处理方式。

温感

关键器件尤其的温度要进行监控

244/245

有上、下拉需要的信号在经过没有输出保持功能的总线驱动器后,需要在总线驱动器的输入、输出端加上下拉。

仿真

电路中使用电感、电容使用合适Q值,可以通过仿真。

时序

确认上电时序是否满足芯片手册和推荐电路要求。

时序

确认下电时序是否满足芯片手册和推荐电路要求。

时序

确认复位时序是否满足芯片手册和推荐电路要求。

复位开关

单板按键开关设计,要防止长按按键,单板挂死问题,建议按键开关设计只产生一段短脉宽低电平。

复位设计

射频滤波

视频放大器的电源设计时要添加合适的滤波电容,防止电源噪声对射频信号质量造成本良影响。

射频滤波

电源、功率电路设计是应用电需要考虑电阻的功率特性的选择。

可测试性

部分功能模块要保持可以长工状态,利于进行硬件测试。

射频电路

直流偏置电路是否需要使能控制,控制电压精度是否满足放大器的要求。

射频电路

保证前级可能输出的最大RF峰值功率小于后级级联器件的最大极限输入功率3dB左右,需要关注信号峰值和过冲对器件过功率的影响。