封装制程-PPT精选

合集下载

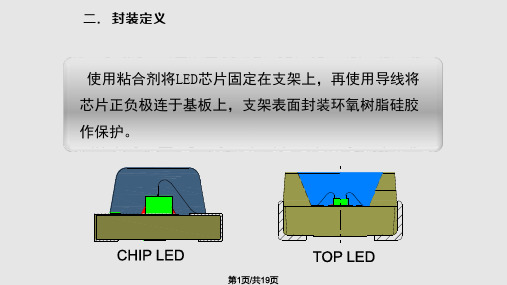

SMDLED封装流程介绍PPT课件

IV: (xxx-xxx) mcd

BIN: XX

VF: (xx-xx) V

LOT: |||||||||||||||||||||||||||||||||

QC:

QC PASS

xxxx

FOSHAN NATIONSTAR OPTOELECTRONICS CO., LTD

佛山市国星光电股份有限公司

TOP LED

RoHS

IF = x mA

TYPE: XX-XXXXX-XX Color Bin:xxxx

QTY: XXXX

IV: (xxx-xxx) cd

BIN: XX

VF: (xx-xx) V

LOT: |||||||||||||||||||||||||||||||||

xxxxxxx

QC:

QC PASS

FOSHAN NATIONSTAR OPTOELECTRONICS CO., LTD

5.0 抽检进仓

• 由质量部对准备入库的产品进行抽检,以确保产品符合质量标准。

LED应用

LED光源模块

LED面板灯

LED日光灯管

LED射灯、球泡灯

LED背光源

• 将PCB板划片一颗一颗的LED或是将支架冲切单颗的LED。

4.5 测试

• 根据产品特性,客户要求按给定电流进行分光分色测试,同时剔除光电性能不良 的产品。

• 测试参数通常有光强Iv,波长λd,色座标(X,Y),正向电压Vf和反向漏电Ir。 • 分光标准一般为光强1:1.2,波长2.5nm,电压0.2V作为一档,Ir控制小于10μA

佛山市国星光电股份有限公司

单色管按波长、光强、电压分档

白管按色坐标、光强、电压分档

色区分档标准

IC封装工艺流程ppt课件

精选课件ppt

5

傳統 IC 主要封裝流程-2

精选课件ppt

6

芯片切割 (Die Saw)

目的:用切割刀将晶圆上的芯片切 割分离成单个晶粒(Die)。

其前置作业为在芯片黏贴(Wafer Mount),即在芯片背面贴上蓝膜 (Blue Tape)并置于铁环(Wafer Ring) 上,之后再送至芯片切割机 上进行切割。

精选课件ppt

7

晶粒黏贴 (Die Bond)

目的:将晶粒置于框架(Lead Frame) 上,并用银胶(Epoxy)黏着固定。

导线架是提供晶粒一个黏着的位置 (称作晶粒座,Die Pad),并预设有 可延伸IC晶粒电路的延伸脚。黏晶完 成后之导线架则经由传输设备送至金 属匣(Magazine)内,以送至下一制 程进行焊线。

Dam Bar

去胶位置

精选课件ppt

18

去纬 (Trimming)

去纬(Trimming)的目的: 去纬是指利用机械模具将脚间金属连接杆切除。

去纬位置

外腳位置

精选课件ppt

19

去框 (Singulation)

去框(Singulation)的目的: 將已完成盖印(Mark)制程 的Lead Frame,以沖模的方 式将Tie Bar切除,使 Package与Lead Frame分开, 方便下一个制程作业。

型

精选课件ppt

22

检验 (Inspection)

在制程当中,为了确保产品之质量,也需要做一些检测

(In-Process Quality Control)。如于焊线完成后会进行 破坏性试验,而在封胶之后,则以X光(X-Ray)来检视胶 体内部之金线是否有移位或断裂之情形等等。一颗已完

半导体封装工艺讲解——芯片制造流程课件PPT

到L/F的运输过程; 3、Collect以一定的力将芯片Bond在点有银浆的L/F

的Pad上,具体位置可控; 4、Bond Head Resolution:

X-0.2um;Y-0.5um;Z-1.25um; 5、Bond Head Speed:1.3m/s;

FOL– Die Attach 芯片粘接

Thickness Size

FOL– 3rd Optical Inspection三 光检查

检查Die Attach和Wire Bond之后有无各种废品

EOL– End of Line后段工艺

EOL

Annealing 电镀退火

Trim/Form 切筋/成型

Molding 注塑

Laser Mark 激光打字

• QFN—Quad Flat No-lead Package 四方无引脚扁平封装 • SOIC—Small Outline IC 小外形IC封装 • TSSOP—Thin Small Shrink Outline Package 薄小外形封装 • QFP—Quad Flat Package 四方引脚扁平式封装 • BGA—Ball Grid Array Package 球栅阵列式封装 • CSP—Chip Scale Package 芯片尺寸级封装

IC Package Structure(IC结构 图)

Lead Frame 引线框架

Die Pad 芯片焊盘

Gold Wire 金线

Epo

TOP VIEW

银浆

Mold pound 环氧树脂

SIDE VIEW

Raw Material in Assembly(封装 原材料)

【Wafer】晶圆

……

Raw Material in Assembly(封装 原材料)

的Pad上,具体位置可控; 4、Bond Head Resolution:

X-0.2um;Y-0.5um;Z-1.25um; 5、Bond Head Speed:1.3m/s;

FOL– Die Attach 芯片粘接

Thickness Size

FOL– 3rd Optical Inspection三 光检查

检查Die Attach和Wire Bond之后有无各种废品

EOL– End of Line后段工艺

EOL

Annealing 电镀退火

Trim/Form 切筋/成型

Molding 注塑

Laser Mark 激光打字

• QFN—Quad Flat No-lead Package 四方无引脚扁平封装 • SOIC—Small Outline IC 小外形IC封装 • TSSOP—Thin Small Shrink Outline Package 薄小外形封装 • QFP—Quad Flat Package 四方引脚扁平式封装 • BGA—Ball Grid Array Package 球栅阵列式封装 • CSP—Chip Scale Package 芯片尺寸级封装

IC Package Structure(IC结构 图)

Lead Frame 引线框架

Die Pad 芯片焊盘

Gold Wire 金线

Epo

TOP VIEW

银浆

Mold pound 环氧树脂

SIDE VIEW

Raw Material in Assembly(封装 原材料)

【Wafer】晶圆

……

Raw Material in Assembly(封装 原材料)

半导体封装制程及其设备介绍-PPT

Substrate

Solder paste pringting

Stencil

Chip shooting

Nozzle Capacitor

Reflow Oven

Hot wind

DI water cleaning

Automatic optical

inpection

DI water

Camera

PAD PAD

Wafer tape

Back Grind

Wafer Detape

Wafer Saw

Inline Grinding & Polish -- Accretech PG300RM

Coarse Grind 90%

Fine Grind 10%

Centrifugal Clean

Alignment & Centering

Die distance Uniformity

4。PICKING UP

3。EXPANDING

No contamination

TAPE ELONGATION

WEAK ADHESION

3.Grinding 辅助设备

A Wafer Thickness Measurement 厚度测量仪 一般有接触式和非接触式光学测量仪两种;

Solder paste

Die Prepare(芯片预处理) To Grind the wafer to target thickness then separate to single chip

---包括来片目检(Wafer Incoming), 贴膜(Wafer Tape),磨片(Back Grind),剥膜(Detape),贴片(Wafer Mount),切割(Wafer Saw)等系列工序,使芯片达到工艺所要求的形状,厚度和尺寸,并经过芯片目 检(DVI)检测出所有由于芯片生产,分类或处理不当造成的废品.

集成电路封装技术-封装工艺流程介绍(ppt 123页)

三种导电胶的特点是:化学接合、具有导电功能。

第二章 封装工艺流程

导电胶贴装工艺

膏状导电胶: 用针筒或注射器将粘贴剂涂布到芯

片焊盘上(不能太靠近芯片表面,否则 会引起银迁移现象),然后用自动拾片 机(机械手)将芯片精确地放置到焊盘 的粘贴剂上,在一定温度下固化处理 (150℃ 1小时或186℃半小时)。 固体薄膜:

第二章 封装工艺流程

2.2.2减薄工艺

先划片后减薄和减薄划片两种方法

DBG(dicing before grinding) 在背面磨削之前,将硅片 的正面切割出一定深度的切口,然后再进行磨削。

DBT(dicing by thinning) 在减薄之前先用机械的或化学 的方法切割出一定深度的切口,然后用磨削方法减薄到一 定厚度后,采用常压等离子腐蚀技术去除掉剩余加工量。。

这两种方法都很好地避免了或减少了减薄引起 的硅片翘曲以及划片引起的边缘损害,大大增强了 芯片的抗碎能力。

第二章 封装工艺流程

2.3 芯片贴装 芯片贴装,也称芯片粘贴,是将芯片固定于封装基板

或引脚架芯片的承载座上的工艺过程。

贴装方式

• 共晶粘贴法 • 焊接粘贴法 • 导电胶粘贴法 • 玻璃胶粘贴法

第二章 封装工艺流程

第二章 封装工艺流程

金凸块制作的传统工艺

金凸块制作的传统工艺: 第一步,对芯片进行清洁处理 第二步,通过真空溅散的方法,在芯片键合的上表面形

成粘着层和阻挡层。粘着层提供IC芯片上的铝键合点与凸块 间良好的键合力与低的接触电阻特性。常用的材料是Ti、Cr、 和Al,这几种金属的与铝和氧化硅的粘着性很好。扩散阻挡 层的作用是阻止芯片上的铝与凸块材料之间的扩散反应而形 成金属间化合物。

基带材料:要求耐高温,与金属箔粘贴性好,热匹配性 好,抗化学腐蚀性强,机械强度高,吸水率低。例如,聚酰亚胺

第二章 封装工艺流程

导电胶贴装工艺

膏状导电胶: 用针筒或注射器将粘贴剂涂布到芯

片焊盘上(不能太靠近芯片表面,否则 会引起银迁移现象),然后用自动拾片 机(机械手)将芯片精确地放置到焊盘 的粘贴剂上,在一定温度下固化处理 (150℃ 1小时或186℃半小时)。 固体薄膜:

第二章 封装工艺流程

2.2.2减薄工艺

先划片后减薄和减薄划片两种方法

DBG(dicing before grinding) 在背面磨削之前,将硅片 的正面切割出一定深度的切口,然后再进行磨削。

DBT(dicing by thinning) 在减薄之前先用机械的或化学 的方法切割出一定深度的切口,然后用磨削方法减薄到一 定厚度后,采用常压等离子腐蚀技术去除掉剩余加工量。。

这两种方法都很好地避免了或减少了减薄引起 的硅片翘曲以及划片引起的边缘损害,大大增强了 芯片的抗碎能力。

第二章 封装工艺流程

2.3 芯片贴装 芯片贴装,也称芯片粘贴,是将芯片固定于封装基板

或引脚架芯片的承载座上的工艺过程。

贴装方式

• 共晶粘贴法 • 焊接粘贴法 • 导电胶粘贴法 • 玻璃胶粘贴法

第二章 封装工艺流程

第二章 封装工艺流程

金凸块制作的传统工艺

金凸块制作的传统工艺: 第一步,对芯片进行清洁处理 第二步,通过真空溅散的方法,在芯片键合的上表面形

成粘着层和阻挡层。粘着层提供IC芯片上的铝键合点与凸块 间良好的键合力与低的接触电阻特性。常用的材料是Ti、Cr、 和Al,这几种金属的与铝和氧化硅的粘着性很好。扩散阻挡 层的作用是阻止芯片上的铝与凸块材料之间的扩散反应而形 成金属间化合物。

基带材料:要求耐高温,与金属箔粘贴性好,热匹配性 好,抗化学腐蚀性强,机械强度高,吸水率低。例如,聚酰亚胺

封装制程补充教材(封装前段)ppt课件

Type

CD 4N Au

HAZ Length (um)

100 ~ 130 120 ~ 150

Ball Neck Grain (um)

6.0 ~ 8.0 3.0 ~ 4.0

Wire Grain (um)

3.0 ~ 4.0 1.5 ~ 2.0

11

封裝製程補充教材

HAZ (Heat Affected Zone)

Image Observation (SEM) Photographing from the ball to wire using SEM

Grain Size Measurement Measure grain sizes at every 20㎛

Determination of HAZ

Determine the grain size decreasing point

B.吸嘴型式 C.L/F材质 D.D/B作业机台

(1)共金-ILB(圖片/影檔) (2)导电/非导电胶-AD828/AD830/AD898/AD8930

/CPS-100VX(圖片/影檔) (3)共锡-NEC CPS-510/ASM SD890A(圖片/影檔) E.导电性 F.散热性

4

封裝製程補充教材

佳

缺點

易裂(L/F與die膨脹係數差異)

使用之L/F

SOT-23R

膠黏合 依膠固化條件 ASM/NEC 差(導電膠) 差 同上

all package

軌道加蓋 solder熔點305℃

ASM/NEC 中 中 vold/小die易傾斜 "D-PAK SOT-89

5

TO-220/263 SOT-223"

封裝製程補充教材

IC_芯片封装流程 ppt课件

分割

AVI 自动检查

8

Taping 贴膜

Operation:Taping on the front side of wafer 操作:在晶圆的正面贴上一层蓝膜 Purpose:Protect wafer front side 目的:保护晶圆正面

9

Backside Grinding 背面磨晶

Operation:Grinding backside of the wafer 操作:磨晶圆的背面 Purpose:Thinning the wafer 目的:减小晶圆的厚度

Front side

14

Wire Bond 焊线

Operation:bonding wire on die pad and lead

操作:在芯片和管脚上焊线

Purpose:interconnect lead and die

目的:芯片和管脚的内连接

15

Molding 模封

Operation:To encapsulate the substrate and the bonded die in compound 操作:用模封材料将基板和焊过线的芯片连接起来 Purpose:To protect the die and the bonded wire from damage 目的:防止芯片和线受到损伤

10

Wafer Mount & Detaping 去膜贴片

Operation:Detaping and wafer mount 操作:将晶圆背面贴在钢圈固定的蓝膜上,然后 去除正面的保护膜 Purpose:fix the wafer on the ring 目的:将晶圆用钢圈固定

11

Die Saw 切片

6

AVI 自动检查

8

Taping 贴膜

Operation:Taping on the front side of wafer 操作:在晶圆的正面贴上一层蓝膜 Purpose:Protect wafer front side 目的:保护晶圆正面

9

Backside Grinding 背面磨晶

Operation:Grinding backside of the wafer 操作:磨晶圆的背面 Purpose:Thinning the wafer 目的:减小晶圆的厚度

Front side

14

Wire Bond 焊线

Operation:bonding wire on die pad and lead

操作:在芯片和管脚上焊线

Purpose:interconnect lead and die

目的:芯片和管脚的内连接

15

Molding 模封

Operation:To encapsulate the substrate and the bonded die in compound 操作:用模封材料将基板和焊过线的芯片连接起来 Purpose:To protect the die and the bonded wire from damage 目的:防止芯片和线受到损伤

10

Wafer Mount & Detaping 去膜贴片

Operation:Detaping and wafer mount 操作:将晶圆背面贴在钢圈固定的蓝膜上,然后 去除正面的保护膜 Purpose:fix the wafer on the ring 目的:将晶圆用钢圈固定

11

Die Saw 切片

6

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

封裝製程-PPT精學 材料工程研究所碩士班 • 台灣大學 電機工程研究所博士班

• 曾任

– 淡江大學 兼任講師 – 博達科技 MOCVD 製造處副理

• 現任

– 矽格股份有限公司 光電事業處經理

矽格股份有限公司

成立時間: 1988年12月 資本額 : 新台幣14.19億元 主要營業項目: 半導體封裝測試 員工人數 : 約850人 無塵室等級: Class10, Class1K, Class10K 投資者: 矽品精密、經營團隊、員工、其他股東

LED 封裝形式

• 依外型分類

– 插件式, Lamp type ( DIP)

• 佔80% 市場 • 屬傳統LED封裝方式

– 表面黏著式 surface mount device (SMD)

• 佔20% 市場 • 約1980開始發展, 有逐步取代DIP 之趨勢 • 適用於密集電路設計

LED 封裝形式

2. 封裝的基石: 固晶 3. 對外的橋樑: 銲線 4. 美麗的外衣: 成型樹酯

LED 封裝材料- 基板

基板成型之分析

PCB Ceramic

Metal

取得 O O O

加工 X X O

成型 X X O

污染 X O O

價格 中 高 低

LED 封裝材料- 基板

基板材料特性:

導電性 導熱性 精確度

PCB

白光 LED

Blue LED 激發YAG螢光粉

Blue LED 基板

白光 LED

UV LED 激發RGB螢光粉

UV LED 基板

白光 LED

ZnSe LED

ZnSe 基板 CdZnSe 薄膜

螢光粉 Phosphor

• YAG : 580nm yellow • SrGa2S4 : Eu2+ ; 540nm Green • SrS : Eu2+ ; 610nm Red • Ba2MgSiO7 : CaSrEuZn forUV LED

– 根據晶片進行頂針, 吸嘴, 吸力參數調整 – 根據晶片與基座進行銀膠參數調整 – 晶粒位置, 偏移角及推力製程調整

固晶機台各部系統

• 進出料系統 • 晶粒辨識系統 • 晶粒擷取系統 • 基座輸送系統 • 點膠系統 • 固化系統

固晶機台各部系統

進料系統

點 膠 系 統

基座輸送系統

基座輸送方向

晶

晶

散熱層

LED 熱力學-主動式散熱

風扇 致冷晶片 液態冷煤系統

成本 技術 效果 耗能 壽命 低易好好 好 很高 難 好 尚可 好 極高 極難 極佳 高 好

高功率LED-Flip Chip

Al2O3 n-GaN p-GaN n-metal

n-metal

Solder

Solder

Si 基板

白光 LED

白光LED之優點

• 省電 • 耐震 • 應答速度快 • 壽命長 • 低電壓啟動 • 演色性佳 • 溫度低 • 商品設計自由度高

白光 LED

色光之混合

白光 LED

RGB LED 混光

Red LED Green LED Blue LED 基板

白光 LED

Blue LED 激發RG螢光粉

Blue LED 基板

V

X

X

Ceramic V

O

O

Metal O

O

O

LED 封裝材料- 基板

基板於各製程中之加工特性:

Component

Ag epoxy

PCB

O

Ceramic

O

Metal

O

固晶

All metal

Coating Preform Solder

V

X

X

O

O

O

O

O

O

打線

Al Au

OV OV OO

成型

V O O

LED 封裝材料- 基板

• 白光LED

LED 封裝製程

固晶 (die attached) 烘烤 (epoxy curing) 打線 (wire bonding) 成型 (molding) 分割 (singluration) 測試 (testing) 分類 (sorting)

LED 封裝材料

1. 封裝核心: 基板 •基板的性能對於非晶粒性之失效有決定性之影響

晶粒輸送方向

粒

粒

辨

擷

識

取

系

系

統

統

晶圓

固化系統 進料系統

固晶半成品輸送方向

固晶十二大品質異常項目

• 漏固 • 掉晶片 • 晶片破損 • 晶片沾銀膠 • 晶片倒置 • 銀膠量異常 • 晶片傾斜 • 基座變形 • 固位不正 • 晶片旋轉角偏移 • 銀膠偏移 • 推粒不足

LED 封裝製程-銲線

• 銲線(Wire Bonding) • 銲線之目的為將晶粒固著於基板之上 • 銲線之製程重點:

• 依發光功率分類

– 傳統20 mA LED – High power LED ( >350mA)

• 依光點數分類 • 單點LED • 多點LED (matrix LED)

LED 封裝形式

• 依用途分類

– 傳統顯示型LED

• 七區顯示器 • 號誌用LED

– 光傳輸LED

• IR LED

– 照明用LED

– 根據晶片進行銲線參數調整 – 拉力參數調整 – 線弧製程調整

LED 熱力學

電極

晶粒

銀膠 基板

LED 熱力學

保護層

H HH 晶片層

H 銀膠層 H H

H 金屬層 H

H

H

絕緣層 H

H

H

LED 熱力學

亮

度

電

阻

熱

晶片面積

LED 熱力學

溫

溫

度

度

LED 熱力學

溫

溫

度

度

LED 熱力學-高散熱封裝

保護層 晶片層 銀膠層 金屬層 絕緣層

固化精確度 O O X

LED 封裝材料- 固晶

基板於客戶端加工特性:

Solding Process Reflow 溫控

SMT Manual

有機高分子銀膠 O

O

O

V

無機高分子銀膠 O

O

O

V

合金

O

V

X

O

LED 封裝材料- 銲線

金線 鋁線 金屬片

取得 O O O

加工 W/B W/B Heater

成型 易 易 難

基板於客戶端加工特性:

Solding Process Reflow 溫控

SMT Manual

PCB

V

V

V

X

Ceramic V

O

O

V

Metal O

V

X

O

Alignment

V O O

LED 封裝材料- 固晶

有機高分子銀膠 無機高分子銀膠

合金

取得 O O O

加工 O O O

成型 O O O

污染 X X O

獲利能力

OUTLINE

• LED 封裝簡介 • LED 封裝之形式 • LED 封裝材料與封裝製程 • 白光LED封裝技術

LED 封裝簡介

• LED 封裝之目的:

– 將半導體晶片封裝程可以供商業使用之電子元件 – 保護晶片防禦輻射, 水氣, 氧氣, 以及外力破壞 – 提高元件之可靠度 – 改善/提升晶片性能 – 提供晶片散熱機構 – 設計各式封裝形式, 提供不同之產品應用

• 依製程可分為:

– 灌注型: 材料常溫呈液態 – 射出型: 材料常溫呈固態 – 燒結型: 通常為玻璃類 – 帽蓋型: 以金屬為封裝材料

LED 封裝製程介紹

LED 封裝製程介紹

LED 封裝製程-固晶

• 固晶(Die Attachment or Die Bonding) • 固晶之目的為將晶粒固著於基板之上 • 固晶之製程重點:

價格 高 高 低

LED 封裝材料- 固晶

固晶材料特性:

有機高分子銀膠 無機高分子銀膠

合金

導電性 V V O

導熱性 X V O

精確度 V V O

耐溫性 X V O

LED 封裝材料- 固晶

固晶於製程加工特性:

烤箱固化

有機高分子銀膠 O

無機高分子銀膠 O

合金

V

機台固化 O O V

其他方式固化 O O V

螢光粉 Phosphor-特性要求

• 長時間使用性質穩定 • 光色不因溫度, 時間, 日照, 晶片效率而改變 • 反應時間快, ~120ns • 吸收短波長光, 放出常波長光,且過程可逆

谢 谢 大 家 !

價格 高 中 低

LED 封裝材料- 銲線

銲線材料特性:

金線 鋁線 金屬片

導電性 O O O

導熱性 V V O

抗撓性 X X O

LED 封裝材料- 銲線

銲線對元件特性影響:

Pulse DC

金線

O

V

鋁線

O

X

金屬片

O

O

高輸入 V X O

高輸出 V X O

惡劣環境 V X O

LED 封裝材料- 成型材料

• 曾任

– 淡江大學 兼任講師 – 博達科技 MOCVD 製造處副理

• 現任

– 矽格股份有限公司 光電事業處經理

矽格股份有限公司

成立時間: 1988年12月 資本額 : 新台幣14.19億元 主要營業項目: 半導體封裝測試 員工人數 : 約850人 無塵室等級: Class10, Class1K, Class10K 投資者: 矽品精密、經營團隊、員工、其他股東

LED 封裝形式

• 依外型分類

– 插件式, Lamp type ( DIP)

• 佔80% 市場 • 屬傳統LED封裝方式

– 表面黏著式 surface mount device (SMD)

• 佔20% 市場 • 約1980開始發展, 有逐步取代DIP 之趨勢 • 適用於密集電路設計

LED 封裝形式

2. 封裝的基石: 固晶 3. 對外的橋樑: 銲線 4. 美麗的外衣: 成型樹酯

LED 封裝材料- 基板

基板成型之分析

PCB Ceramic

Metal

取得 O O O

加工 X X O

成型 X X O

污染 X O O

價格 中 高 低

LED 封裝材料- 基板

基板材料特性:

導電性 導熱性 精確度

PCB

白光 LED

Blue LED 激發YAG螢光粉

Blue LED 基板

白光 LED

UV LED 激發RGB螢光粉

UV LED 基板

白光 LED

ZnSe LED

ZnSe 基板 CdZnSe 薄膜

螢光粉 Phosphor

• YAG : 580nm yellow • SrGa2S4 : Eu2+ ; 540nm Green • SrS : Eu2+ ; 610nm Red • Ba2MgSiO7 : CaSrEuZn forUV LED

– 根據晶片進行頂針, 吸嘴, 吸力參數調整 – 根據晶片與基座進行銀膠參數調整 – 晶粒位置, 偏移角及推力製程調整

固晶機台各部系統

• 進出料系統 • 晶粒辨識系統 • 晶粒擷取系統 • 基座輸送系統 • 點膠系統 • 固化系統

固晶機台各部系統

進料系統

點 膠 系 統

基座輸送系統

基座輸送方向

晶

晶

散熱層

LED 熱力學-主動式散熱

風扇 致冷晶片 液態冷煤系統

成本 技術 效果 耗能 壽命 低易好好 好 很高 難 好 尚可 好 極高 極難 極佳 高 好

高功率LED-Flip Chip

Al2O3 n-GaN p-GaN n-metal

n-metal

Solder

Solder

Si 基板

白光 LED

白光LED之優點

• 省電 • 耐震 • 應答速度快 • 壽命長 • 低電壓啟動 • 演色性佳 • 溫度低 • 商品設計自由度高

白光 LED

色光之混合

白光 LED

RGB LED 混光

Red LED Green LED Blue LED 基板

白光 LED

Blue LED 激發RG螢光粉

Blue LED 基板

V

X

X

Ceramic V

O

O

Metal O

O

O

LED 封裝材料- 基板

基板於各製程中之加工特性:

Component

Ag epoxy

PCB

O

Ceramic

O

Metal

O

固晶

All metal

Coating Preform Solder

V

X

X

O

O

O

O

O

O

打線

Al Au

OV OV OO

成型

V O O

LED 封裝材料- 基板

• 白光LED

LED 封裝製程

固晶 (die attached) 烘烤 (epoxy curing) 打線 (wire bonding) 成型 (molding) 分割 (singluration) 測試 (testing) 分類 (sorting)

LED 封裝材料

1. 封裝核心: 基板 •基板的性能對於非晶粒性之失效有決定性之影響

晶粒輸送方向

粒

粒

辨

擷

識

取

系

系

統

統

晶圓

固化系統 進料系統

固晶半成品輸送方向

固晶十二大品質異常項目

• 漏固 • 掉晶片 • 晶片破損 • 晶片沾銀膠 • 晶片倒置 • 銀膠量異常 • 晶片傾斜 • 基座變形 • 固位不正 • 晶片旋轉角偏移 • 銀膠偏移 • 推粒不足

LED 封裝製程-銲線

• 銲線(Wire Bonding) • 銲線之目的為將晶粒固著於基板之上 • 銲線之製程重點:

• 依發光功率分類

– 傳統20 mA LED – High power LED ( >350mA)

• 依光點數分類 • 單點LED • 多點LED (matrix LED)

LED 封裝形式

• 依用途分類

– 傳統顯示型LED

• 七區顯示器 • 號誌用LED

– 光傳輸LED

• IR LED

– 照明用LED

– 根據晶片進行銲線參數調整 – 拉力參數調整 – 線弧製程調整

LED 熱力學

電極

晶粒

銀膠 基板

LED 熱力學

保護層

H HH 晶片層

H 銀膠層 H H

H 金屬層 H

H

H

絕緣層 H

H

H

LED 熱力學

亮

度

電

阻

熱

晶片面積

LED 熱力學

溫

溫

度

度

LED 熱力學

溫

溫

度

度

LED 熱力學-高散熱封裝

保護層 晶片層 銀膠層 金屬層 絕緣層

固化精確度 O O X

LED 封裝材料- 固晶

基板於客戶端加工特性:

Solding Process Reflow 溫控

SMT Manual

有機高分子銀膠 O

O

O

V

無機高分子銀膠 O

O

O

V

合金

O

V

X

O

LED 封裝材料- 銲線

金線 鋁線 金屬片

取得 O O O

加工 W/B W/B Heater

成型 易 易 難

基板於客戶端加工特性:

Solding Process Reflow 溫控

SMT Manual

PCB

V

V

V

X

Ceramic V

O

O

V

Metal O

V

X

O

Alignment

V O O

LED 封裝材料- 固晶

有機高分子銀膠 無機高分子銀膠

合金

取得 O O O

加工 O O O

成型 O O O

污染 X X O

獲利能力

OUTLINE

• LED 封裝簡介 • LED 封裝之形式 • LED 封裝材料與封裝製程 • 白光LED封裝技術

LED 封裝簡介

• LED 封裝之目的:

– 將半導體晶片封裝程可以供商業使用之電子元件 – 保護晶片防禦輻射, 水氣, 氧氣, 以及外力破壞 – 提高元件之可靠度 – 改善/提升晶片性能 – 提供晶片散熱機構 – 設計各式封裝形式, 提供不同之產品應用

• 依製程可分為:

– 灌注型: 材料常溫呈液態 – 射出型: 材料常溫呈固態 – 燒結型: 通常為玻璃類 – 帽蓋型: 以金屬為封裝材料

LED 封裝製程介紹

LED 封裝製程介紹

LED 封裝製程-固晶

• 固晶(Die Attachment or Die Bonding) • 固晶之目的為將晶粒固著於基板之上 • 固晶之製程重點:

價格 高 高 低

LED 封裝材料- 固晶

固晶材料特性:

有機高分子銀膠 無機高分子銀膠

合金

導電性 V V O

導熱性 X V O

精確度 V V O

耐溫性 X V O

LED 封裝材料- 固晶

固晶於製程加工特性:

烤箱固化

有機高分子銀膠 O

無機高分子銀膠 O

合金

V

機台固化 O O V

其他方式固化 O O V

螢光粉 Phosphor-特性要求

• 長時間使用性質穩定 • 光色不因溫度, 時間, 日照, 晶片效率而改變 • 反應時間快, ~120ns • 吸收短波長光, 放出常波長光,且過程可逆

谢 谢 大 家 !

價格 高 中 低

LED 封裝材料- 銲線

銲線材料特性:

金線 鋁線 金屬片

導電性 O O O

導熱性 V V O

抗撓性 X X O

LED 封裝材料- 銲線

銲線對元件特性影響:

Pulse DC

金線

O

V

鋁線

O

X

金屬片

O

O

高輸入 V X O

高輸出 V X O

惡劣環境 V X O

LED 封裝材料- 成型材料