直接数字合成技术综述报告

直接数字频率合成技术DDS

相位/幅度变换装置 图3-11 相位 幅度变换装置 假设DAC的输入幅度码是四位,则它的输出幅度与输 的输入幅度码是四位, 假设 的输入幅度码是四位 入幅度码之间的关系是按线性变化的,如表 所示 所示。 入幅度码之间的关系是按线性变化的,如表3-1所示。

表 3-1

二进制幅度码 0000 0001 0010 0011 0100 0101 0110 0111 十进制幅度 0.0000 0.0625 0.1250 0.1875 0.2500 0.3125 0.3750 0.4375 二进制幅度码 1000 1001 1010 1011 1100 1101 1110 1111 十进制幅度 0.5000 0.5265 0.6250 0.6875 0.7500 0.8125 0.8750 0.9375

若频率控制字 K = A4A3A2A1 = 0010,则在时钟脉冲作 , 用下, 用下,累加器输出的相位码依次是 0000→0010→0100→0110→ … →1110→0000,只需 个时钟 ,只需8个时钟 脉冲累加器输出相位码即可完成一次循环。 脉冲累加器输出相位码即可完成一次循环。可见频率控制字 加大一倍,累加器的增长速率随之加大一倍, 加大一倍,累加器的增长速率随之加大一倍,输出信号频率 也就加大一倍。 也就加大一倍。

直接数字式频率合成( 直接数字式频率合成( DDS )

随着技术和器件水平的提高, 随着技术和器件水平的提高,称之为直接数字 式频率合成器( 式频率合成器(DDS)的新的频率合成技术得到飞 ) 速的发展。 在相对带宽、频率转换时间、 速的发展。 DDS 在相对带宽、频率转换时间、相 位连续性、正交输出、高分辨力以及集成化等等一 位连续性、正交输出、 系列指标方面, 系列指标方面,已远远超过了传统频率合成器所能 达到的水平,完成了频率合成技术的又一次飞跃。 达到的水平,完成了频率合成技术的又一次飞跃。 DDS 与传统的 DS 和 IS 一起构成了现代频率合成 技术体系,将频率合成技术推向了一个新阶段。 技术体系,将频率合成技术推向了一个新阶段。

基于FPGA的直接数字合成器的设计

基于FPGA的直接数字合成器的设计

华金;姜伟;李存兵

【期刊名称】《机电工程》

【年(卷),期】2007(024)012

【摘要】介绍了直接数字合成器(DDS)的基本组成及工作原理,采用QUARTUSⅡ软件提供的模块和VHDL语言自行设计的寄存器,实现了现场可编程门阵列(FPGA)的相位累加器和波形存储表的设计.通过频谱分析研究了DDS的输出频谱,分析讨论了引起输出杂散的原因及改善杂散的方法.研究结果表明,该设计具有较高的实际应用价值.

【总页数】3页(P38-40)

【作者】华金;姜伟;李存兵

【作者单位】浙江工业大学,机械制造及自动化省部共建教育部重点实验室,浙江,杭州,310014;浙江工业大学,机械制造及自动化省部共建教育部重点实验室,浙江,杭州,310014;浙江工业大学,机械制造及自动化省部共建教育部重点实验室,浙江,杭州,310014

【正文语种】中文

【中图分类】TN99

【相关文献】

1.基于FPGA直接数字频率合成器DDS的设计 [J], 王静

2.基于FPGA的直接数字频率合成器设计 [J], 王元华

3.基于单片机和FPGA的直接频率数字合成器设计 [J], 任玲芝;李岩岩;刘丽

4.基于FPGA的直接数字频率合成器设计 [J], 胡鹏飞;沈力;韩锋

5.基于FPGA的直接数字频率合成器的设计 [J], 平淞元;

因版权原因,仅展示原文概要,查看原文内容请购买。

文献综述与开题报告(样例)

文献综述与开题报告1.文献综述1.1 频率合成技术简介频率合成是指从一个高稳定的参考频率, 经过各种技术处理, 生成一系列稳定的频率输出。

频率合成的概念就是由一个或几个参考频率通过一些转换, 产生一个或多个频率信号的过程。

频率合成技术一般分为直接式(DS)、间接式(PLL)和直接数字式(DDS)三种基本形式。

早期的频率合成采用直接式的方式, 是由一个或多个晶体震荡器经分频、倍频、混频对一个或几个基准频率进行加、减、乘、除运算产生所需要的频率信号, 并通过滤波器产出, 这是最早的频率合成信号源的方法。

目前该方法仍在使用, 主要是因为它频率转换速度、相位噪声低, 比较容易实现。

但是该方式涉及的合成器体积过于庞大, 而且成本较高, 结构复杂、产生任意波形的可控性较低。

间接合成式是基于锁相环的原理, 即PLL。

它与前者相比, 输出频率的稳定度和准确度都有明显的提高, 频谱纯度等性能也有较大改善。

主要是因为信号源的振荡频率被固定在频率计数器的时基上, 也就是说以稳定度高的振荡器为基准。

因此, 锁相环的输出频率就与基准频率一致, 振荡器输出信号和参考信号之间的相位差为固定的常数, 而且锁相环的突出优点是能够抑制叠加到输入信号上的噪纠。

这是直接式频率合成方法所不能达到的。

PLL还有体积小、性价比较高等一系列优点。

但是PLL技术也有明显的缺点, 采取闭环控制, 系统的输出频率改变后, 重新达到稳定的时间也就比较长, 一般为毫秒级, 很难满足高频率分辨率与快速转换率同时具备的要求, 因此也有明显瑕疵。

直接数字频率合成技术从原理上实现了突破。

前两种方法都是通过对基准频率进行运算得出, 而DDS技术则是从相位的概念进行频率合成。

它按一定的相位间隔, 将待产生的波形幅度的二进制数据存储于高速存储器作为查找表, 用参考频率源(一般为晶体振荡器)作为时钟, 用频率控制字决定每次从查找表中取出波形数据的相位间隔, 以产生不同的输出频率, 对取出的波形数据通过高速D/A转换器来合成出存储在存储器内的波形。

直接数字频率合成技术及其设计方案

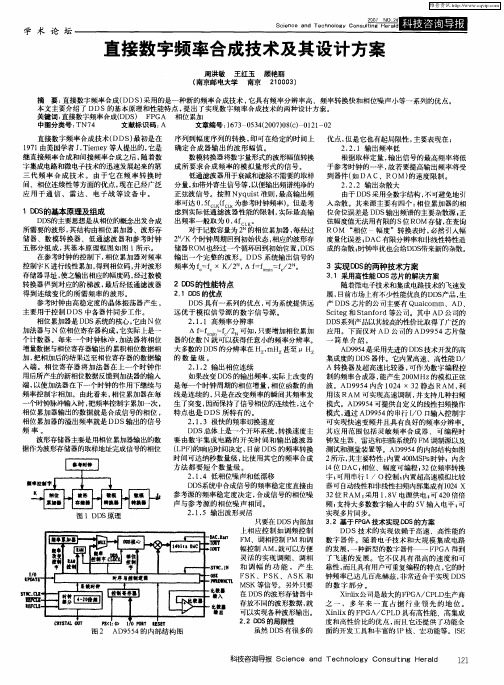

直接数字 频率合成技 术( DDS 最初是在 ) 1 7 由美 国学者 J T e y等人提出的 , 91 .i me 它是 继直接 频率合成和 间接 频率 合成之后 , 随着数 字集成 电路和微电子技 术的迅速发展起来的第 三 代 频 率 合 成技 术 。 由于 它 在 频率 转 换 时 间、相 位连续性等方面 的优 点 , 现在 已经广泛 应 用 干 通 信 、雷 达 、 电子 战 等 设备 中 。

3实现 D S O 的两种技术方案

3 1采用高性能 D S 片的解决方案 . D芯

随着徽电子技 术和集成 电路技术的飞速发 展 , 前市场上有不少 l能优 良的D S 目 生 D 产品 , 生 产 D S芯片的公 司主要有 Q ac mm、AD、 D ul o S i g和 Sa fr 公司。其 中 AD公司的 ce t tnod等 DS D 系列产品以其较高的性价 比取得 了广泛 的 应用 。下面仅对 AD 公司的 A 9 4 D9 5 芯片做 简 单 介绍 。 A 9 5 是采用先进的 D S D 94 D 技术开发 的高 集成度的 D S器件 。它 内置高速 、高性能 D D / A 转换器及超高速 比较 器 , 可作为数字 编程 控 制的频率合成 器 , 能产生 2 0 0 MHz 的模 拟正 弦 波 。AD 9 4内含 12 2 态 RAM , 95 0 4X3 静 利 用该 RA 可实现高速调制 , 支持几种扫频 M 并 模式 。A 9 5 可提供 自定义的线性扫频操作 D 94 模式 , 通过 AD 94的串行 IO 口输入控制字 95 / 可实现快速 变频 并且具有 良好的频率分辨率 。 其 应 用范 围包括 灵敏频 率合 成器 、可 编程时 钟 发生器、雷达和扫描 系统的 F 调制源以及 M 测试和测量装置等 。AD 94 内部结构如 图 95 的 2 所示 , 其主要特性 : 内置 4 0 P 时钟 ;内含 0 MS s l 位 DA 相位 、幅度可编程 ;2 4 C; 3 位频率转换 字; 可用串行 I /O控制 ; 内置超高速模拟 比较 器可 自 动线性和非线性扫频内部集成有 12 04x 3 2位 RAM ; 采用 1 8 . V电源供电 ; 4 0倍倍 可 2 频; 支持大多数数字输入 中的 5 V输 入电平 ; 可 实现 多片 同步 。 3 2基于 FG . P A技术实现 D S D 的方案 D DS技术 的实现依赖 干高速 、高性能的 数 字器件 。随 着 电子技 术和 大规模 集成 电路 的发展 , 一种新型的数字器件—— F G P A得到 了飞速 的发展 。 它不仅具 有 很高 的速度 和可 靠性 , 而且具有用户可重复编程的特点 , 它的时 钟频率 已达 几百 兆赫兹 , 常适 合干实现 D S 非 D 的数字部分。 Xni il x公司是最大的 F GA/C L P P D生产商 之 一 , 多年 来 一 直 占据 行 业 领 先 的 地 位 。 X ni F G / P D具 有高性 能、高集成 il x的 P A C L 度和 高性价 比的优 点, 而且 它还 提供 了功能全 面的开发工具和丰富的 I 、宏功能 等。IE P核 S

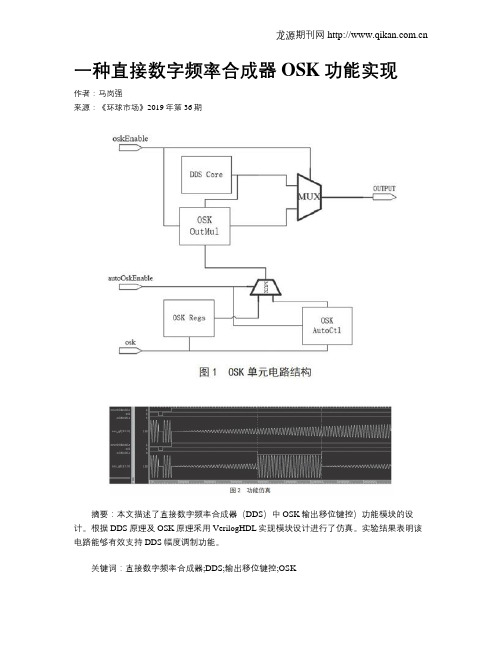

一种直接数字频率合成器OSK功能实现

一种直接数字频率合成器OSK功能实现作者:马岗强来源:《环球市场》2019年第36期摘要:本文描述了直接数字频率合成器(DDS)中OSK输出移位键控)功能模块的设计。

根据DDS原理及OSK原理采用VerilogHDL实现模块设计进行了仿真。

实验结果表明该电路能够有效支持DDS幅度调制功能。

关键词:直接数字频率合成器;DDS;输出移位键控;OSK直接数字频率合成器(Direct DigitalFrequency Synthesizer,DDS)是一种新型的用于输出任意波形的电路,其具有频率分辨率高、频率切换快、输出频率带宽较宽等特点,已经成为通信、探测系统中的关键单元。

[1-3]直接数字频率合成器通常需要支持调频、调相和调幅功能,其中利用DDS的输出移位键控(OSK)功能进行各类驱动信号的OSK调制在通讯、探测等领域广一泛应用。

本文呈现了一种OSK数字电路设计。

一、直接数字频率合成技术(DDS)DDS基本原理是通过频率字累加得到相位,再将相位转换成正余弦信号对应的幅度值,即非线性映射,通常采用数字方式实现,幅度信号最后经过DAC转换及平滑滤波后输出。

将幅度、频率和相位进行数字化以后,可以通过程序控制轻松实现常见的调幅、调频、调相等单一调制信号,也可以通过编写一些函数来实现如线性调频、非线性调频、BPSK等复杂信号[2-3]。

常见的单片DDS电路结构一般包含DDS核、相位频率和幅度控制、滤波模块、高速DAC等。

其核心一般为一个DDS核,用于产生基本的余弦或正弦信号;相位频率和幅度控制实现扫频、OSK等功能;DAC用于数模转换,输出模拟波形。

二、输出移位键控(OSK)电路设计本文所描述的输出移位键控(OSK)功能模块用于DDS控制输出信号幅度,支持选择手动或自动模式。

手动模式下,允许通过串口或并口通信,对幅度控制寄存器进行连续写操作而改变输出幅度。

输出信号幅度变化率受接口速度限制。

自动模式下,通过幅度斜变实现自动调幅,即OSK模块自动生成随时间线性变化的幅度。

直接数字频率合成技术DDS..56页PPT

56、极端的法规,就是极端的不公。 ——西 塞罗 57、法律一旦成为人们的需要,人们 就不再 配享受 自由了 。—— 毕达哥 拉斯 58、法律规定的惩罚不是为了私人的 利益, 而是为 了公共 的利益 ;一部 分靠有 害的强 制,一 部分靠 榜样的 效力。 ——格 老秀斯 59、假如没有法律他们会更快乐的话 ,那么 法律作 为一件 无用之 物自己 就会消 灭。— —洛克

60、人民的幸福是至高无个的法。— —西塞 罗

谢谢

11、越是没有本领的就越加自命不凡。——邓拓 12、越是无能的人,越喜欢挑剔别人的错儿。——爱尔兰 13、知人者智,自知者明。胜人者有力,自胜者强。——老子 14、意志坚强的人能把世界放在手中像泥块一样任意揉捏。——歌德 15、最具挑战性的挑战莫过于提升自我。——迈克尔·F·斯特利

直接数字频率合成心得体会

直接数字频率合成心得体会

我懂得了随着高速数字电路技术的发展,以前模拟波形产生方法已逐渐被数字产生方法所取代。

模拟方法的最大缺点是不能实现波形捷变,而数字的方法不仅能实现多种波形的捷变,而且还可以实现幅相补偿以提高波形的质量。

基于直接数字频率合成(Direct Digital Frequency Synthesis, DDS)技术的波形产生方法就是近些年来数字波形产生方法的典型代表。

频率合成技术是指由一个或多个具有高稳定度和高精准度的参

考频率源,在某一频段内通过线性运算得到大量具有同样性质的频率点的过程。

而完成这一过程的电路被称为频率合成器,简称频综。

数字技术合成实验报告

一、实验目的1. 熟悉数字信号处理的基本原理和数字合成技术;2. 掌握数字信号处理器的使用方法;3. 学会数字信号处理器的编程技巧;4. 了解数字信号处理器的应用领域。

二、实验原理数字信号处理(DSP)技术是一种将模拟信号转换为数字信号,再对数字信号进行处理的技术。

数字合成技术是数字信号处理的一种重要应用,通过数字信号处理器(DSP)对数字信号进行合成,实现对模拟信号的产生、调制、解调等功能。

三、实验设备1. 数字信号处理器(DSP)实验平台;2. 示波器;3. 信号发生器;4. 计算机及实验软件。

四、实验内容1. 数字信号处理器(DSP)的硬件平台搭建;2. 数字信号处理器的编程与调试;3. 数字合成技术的实现;4. 数字合成信号的测试与分析。

五、实验步骤1. 数字信号处理器(DSP)的硬件平台搭建(1)按照实验平台说明书,搭建数字信号处理器(DSP)实验平台;(2)连接示波器、信号发生器等测试设备。

2. 数字信号处理器的编程与调试(1)根据实验要求,编写数字信号处理器的程序;(2)在实验软件中编译程序,生成可执行文件;(3)将可执行文件上传到数字信号处理器(DSP)实验平台;(4)在实验平台上调试程序,确保程序正常运行。

3. 数字合成技术的实现(1)根据实验要求,设计数字合成算法;(2)在数字信号处理器(DSP)实验平台上实现数字合成算法;(3)观察实验平台上的输出信号,分析数字合成效果。

4. 数字合成信号的测试与分析(1)使用示波器测试数字合成信号的波形、频率等参数;(2)使用信号发生器产生模拟信号,与数字合成信号进行对比分析;(3)根据实验结果,评估数字合成技术的性能。

六、实验结果与分析1. 数字信号处理器(DSP)的硬件平台搭建成功,能够正常运行;2. 数字信号处理器(DSP)的编程与调试顺利,程序能够正常运行;3. 数字合成技术的实现成功,数字合成信号质量较高;4. 数字合成信号的测试与分析结果表明,数字合成技术能够满足实验要求,具有良好的性能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

[4]Laemmle, B. , Wagner, C. , Knapp, H. , Jaeger, H. , Maurer, L. ,Weigel, R.A Differential Pair-Based Direct Digital Synthesizer MMIC With 16.8-GHz Clock and 488-mW Power Consumption[J].Microwave Theory and Techniques, IEEE Transactions on,2010,58(5):1375-1383.

上图为幅度调制的基本方法,该方法的主旨是采用了改良过的相位加抖的PDDS,通过这个PDDS来产生两个具有相同频率但相位d(t)却不同的信号,数据流的信息s(t)被编码到d(t)中,接着通过两个电阻器两个1位的信号在模拟网络中相加即得到AM调制信号,数据编码的模式是d(t)=2*acrcos(s(t/2))

直接数字频率合成技术综述报告

摘要:频率源是现代电子设备的重要组成部分,对系统功能有着举足轻重的作用,而直接数字频率合成技术(directdigital synthesis techno理等,以及DDS技术在国内外的实例等。

背景:频率合成是现代电子系统的心脏,是影响电子系统的关键因素之一,广泛用于通信,导航,电子战,遥控遥测,仪器仪表等行业中[2]。在诸多频率合成技术中,直接数字频率合成技术将在下一代雷达与通信系统中发挥至关重要的作用,雷达系统的不断发展使频率合成器产生了对低功耗,高输出频率,良好的频率分辨率,快速的信道切换和良好的调制功能等一系列性能指标产生了越来越高的要求,而DDS合成器表现出的优秀性能相较于其他频率合成器很难被取代。

[2]张涛,陈亮.现代DDS的研究进展与概述[J].电子科技,2008,21(3):46-51

[3]Xueyang Geng , Fa Foster Dai , Irwin, J.D. ,Jaeger, R.C.24-Bit 5.0 GHzDirect Digital Synthesizer RFICWith Direct Digital Modulations in 0.13 m SiGeBiCMOS Technology[J].

DDS结构如图所示,累加器输出端的三位最低有效位可能被截断,而截断将导致芯片尺寸和功耗的减小,并且只会导致微量的杂散的增加。1st最高有效位的输出被用作吉尔伯特单元的输入。2nd最高有效位被用作在编码表之前的正弦波形第三第四象限的剩余三位输出的补充。在这之后7位的编码表的输入将作为正弦加权DAC的输入。所有电流相加并被转化为电压信号来作为吉尔伯特单元的第二输出。吉尔伯特单元的输出就组成了DDS的输出。

如图所示为DDS结构,该结构有四部分组成:一个D-bit正弦加权数模转换器,一个被用作相位调制的P-bit加法器,和被用作N-bit线性调频斜坡信号发生器的一个N-bit相位累加器和另一个N-bit的累加器。线性调频控制字(CCW),频率控制字(FCW)和相位控制字(PCW)分别用来控制线性调频累加器,相位累加器和相位调制。通过对这种数字控制字的直接应用,可以很轻易的改变在DDS寄存器中的数据路径,在这种不需要ROM的DDS结构中,加权正弦DAC同时起到相幅转换器和数模转换器的作用,在突破了ROM的速度瓶颈后,DDS可以很轻易的输出去GHz以上的频率。

[6]Galanopoulos, K. ,Sotiriadis, P.P.Modulation Techniques for All-Digital Transmitters based on Pulse Direct Digital Synthesizers[R].Frequency Control Symposium (FCS), 2012 IEEE International,2012:1-4.

该DDS可用于脉冲压缩雷达,包含一个用于相位累加的24位行波进位加法器(RCA),一个用于相位调制的12位RCA,一个10位的正弦DAC,并采用了一种避免使用ROM的DDS结构。这个DDS结构有超过20000个晶体管并具有最高5GHz的时钟频率,最差的无杂散动态范围为45dBc并具有50MHz的带宽,当输出等于1.246258914GHz的情况下,该带宽范围内的无杂散动态范围为82dBc。

上图为幅度调制的改良结构,该结构是通过两个相互独立的加抖源的基于PDDS的微分相位AM调制拓扑结构。在这个结构中,输出的本低噪声降低了3dB/Hz加抖相位并不是直接加在相位累加器上而是加在了两个相互独立地生成相位上,对于每个相位,都会使用一个相互独立的完全随机的发生器。

参考文献:

[1]戴晴,黄纪军,莫锦军.现代微波与天线测量技术[M].北京:电子工业出版社,2012:17.

上图所示为FM/FSK调制PDDS,调制是通过向频率控制字加入数据流而得以实现的,数据流中的幅度信息是FCW中很小的一部分。

上图为PM/PSK调制PDDS,因为PDDS的n位相位寄存器输出就带有所产生信号的相位信息,所以我们可以通过对相位寄存器的输出加数据流而实现PM/PSK。如果需要,我们还可以通过对最低有效位的位置信息中加入零点而使数据流转换成一个n位的信号,如果这么做的话,整个360度的相位范围都可以被用到等距的相位调制步骤中来。

理想的正弦波信号v(t)可以表示成

在振幅和初始相位确定后,频率由相位唯一确定

于是可得每个时钟周期内的相位增量 。DDS就是利用这个原理进行频率合成的,满 时溢出,由上式可知在采样时钟一定的情况下,频率和相位增量构成映射关系。

上式中 表示一个相位周期内的相位点采样个数,用M表示,而一个N位的相位累加器所能存储的相位个数最多为 个,所以最小步进为 ,可以用频率控制字K控制相位累加的步进。

相对于普通DDS,在这个DDS中设计了一个DET8阶的管道型累加器,该累加器的每一阶都是一个1位的累加器,采用这种技术,能大幅度提高DDS的速度。

4.基于脉冲DDS的针对全数字发射机的调制技术[2]。

脉冲DDS是一种压缩和简化了的直接全数字合成结构,相较于传统的DDS,脉冲DDS并没有正弦查询表和数模转换器。数字射频发射机要想获得小的封装体积和功耗以及一个相对可以接受的较宽的应用范围,就必须构建在具有杂散抑制抖动和调制能力的脉冲DDS上。为了获得一个完整的调制发射机结构结构,我们需要考虑诸如FM/FSK/PM/PSK/AM/ASK在脉冲DDS上的应用。

原理:DDS原理图如图所示,它包含相位累加器,波形存储器,数模转换器,低通滤波器和参考时钟五个部分。其工作原理是:在参考时钟的作用下,相位累加器按照预先设置好的频率控制码进行线性累加,其输出在波形存储器中进行寻址使之输出相应的幅度码。再由数模转换器将这些数字码变换成模拟电压/电流输出,最后经过低通滤波器平滑输出波形。假设要输出的频率是固定的,那么相位增量就是一个常数,在每个时钟周期,相位累加器的数值就按照这个相位增量累加一次,相位增量的大小由频率控制字决定,如果相位增量大,则相位累加器的增加就比较快,输出的频率就比较高,反之亦然[1]。

相对于非线性DAC,线性DAC更加成熟并且易于定性,因此我们倾向于选择线性DAC,并且经过研究已经发现6位的DAC已经足够达到满意的频谱结果。

3.基于砷化镓材料的异质性双极晶体管的10GHz8位DDS合成器[5]。

该DDS采用一种双边沿触发的八级管道累加器和不采用ROM结构的正弦加权DAC,正是由于采用了这种结构,可以最大程度利用HBT所带来的速度上的优势。在输出频率为5GHz的同时,DDS的无杂散动态范围为23.24dBc。

根据奈奎斯特采样定理,每个想为周期内至少需要两个采样点才能形成输出波形,所以DDS的最大输出频率只有本振频率的一半,实际应用中,为了保证输出波形的质量和更好的滤波,通常将DDS的输出频率限制在 以下。

国内外实例:

1.基于0.13微米锗硅BiCMOS工艺的具有直接数字解调功能的24位5GHz的DDS合成器[3]:

2.具有16.8GHz和488mW功耗的MMIC集成的基于差分对的DDS合成器[4]。

该DDS合成器基于双极化锗硅工艺,并具有8位的相位分辨率和6位的幅度分辨率,在是时钟频率位16.8GHz的条件下最大的输出功率为8.3344GHz,频率分辨率为65.625MHz

如图所示为DDS结构,该结构包含一个输入寄存器,一个8位相位累加器,一个6位的数模转换器,一个矩形转换正弦波的模拟波形转换器,一个差分100欧姆输出缓冲区。相幅映射通过微分对饱和体现在模拟域上,这个想法之前已经成功应用在低速模拟信号的发生上。而在这里信号在数字域产生,并由DAC转换至模拟域。这个系统的数字部分只能产生数字三角波并不需要额外的解码。

[5]Gaopeng Chen ,Danyu Wu, Zhi Jin , Jin Wu ,Xinyu Liu.A 10GHz 8-bit Direct Digital Synthesizer Implemented in GaAs HBT Technology[R].Radio Frequency Integrated Circuits Symposium (RFIC), 2010 IEEE,2010:425-428.