超大规模集成电路2017年秋段成华老师第四次作业

浙江省舟山市金衢山五校联盟2022-2023学年第一学期八年级12月月考科学试题(含答案)

浙江省舟山市2022-2023学年金衢山五校联盟校八年级第一学期12月月考科学试题卷注意事项:1.本试题卷分卷I(选择题)和卷II(非选择题)两部分。

考试时间120分钟。

2.本卷共有10页,4大题,35小题,满分为180分。

3.本卷答案必须做在答题卷的相应位置上,做在试卷上无效。

4.g取10牛/千克第I卷(选择题)一、选择题(本题有15小题,第1-10小题,每小题3分;第11-15小题,每小题4分,共50分。

请选出各题中一个符合题意的正确选项,不选、多选、错选,均不给分)1.水是人类不可缺少的宝贵资源,以下是我国“节水标志”的是()A.B.C.D.2.下列有关粗盐提纯的各个步骤,操作规范的是()A.取粗盐B.溶解C.过滤D.蒸发结晶3.如图所示电路中,开关不能同时控制两盏灯的是()A.B.C.D.4.下列四种情景都与气压有关,只有一种情景与其他三种的原理不同,这种情景是()A.刮大风时,玻璃钢瓦的屋B.等候列车的乘客应站在安全线以外,顶被大风“掀”起否则会被“吸”向列车C.打开的窗户外有平行于墙壁的D.将吸盘按压在光洁的瓷砖表面,风吹过时,窗帘会“飘”出窗外放手后吸盘会被“吸”在瓷砖上5.下图表示先天性行为与学习行为的相同点和不同点,其中阴影部分表示相同点。

下列哪一项可以写在阴影部分( )A.与生俱有B.由生活经验和学习获得C.有利于生存和繁殖D.能伴随动物一生6.下列是有关科学问题中的因果关系,其中说法正确的是( )A.浮在水面上的铁球一定是空心的,那么空心的铁球一定会浮在水面上B.溶液是均一的,稳定的,那么均一的,稳定的物质一定是溶液C.饱和溶液恒温蒸发后有固体析出,那么能恒温蒸发析出固体的溶液一定是饱和溶液D.密度比液体小的固体漂浮在液体中,那么漂浮在该液体中的实心固体的密度一定比液体小7.如图所示,两端开口的气缸水平固定,A、B是两个厚度不计的活塞,可在气缸内无摩擦滑动,面积分别为S1=20cm2,S2=10cm2,它们之间用一根细杆连接,B通过水平细绳绕过光滑的定滑轮与质量为M=2kg的重物C连接,活塞的初始状态为静止,已知大气压强P0=1×105Pa,取g=10N/kg,下列说法不正确的是()A.活塞初始静止时,活塞A受到细杆的作用力水平向右B.活塞初始静止时,气缸内压强为1.2×103PaC.若升高气缸内气体温度,活塞B向左移动D.若降低缸内气体温度10℃,活塞运动-段距离L就停止,停止时气缸内压强比初始状态时气缸压强要小8.计算机运行的基础是集成电路,超大规模集成电路是指在在一块极小的芯片上集成的元件数超过10万个,或门电路数超过万门的集成电路,主要用于计算机制造存储器和微处理机。

四川省2017年普通高校职教师资和高取班对口招主统一考试(附答案)

四川省2017年普通高校职教师资和高取班对口招主统一考试―、单项选择题(每小题3分,在每小题列出的四个选项中,只有一个正确答案)1.通用电子数字计算机ENIAC使用的主要电子元器件是()。

A.集成电路B.晶体管C.电子管D.超大规模集成电路2.“48X CD-ROM”中“48X”表示光盘驱动器()。

A.读盘速度为48倍速B.写盘速度为48倍速C.读写速度均为48倍速D.转速为每分钟48转3.Windows 7中,下列方法不能将窗口切换为活动窗口的是()。

A.单击任务栏上对应的图标B.单击窗口的可见区域C.按Alt+Tab组合键进行切换D.按Ctrl+Esc组合键进行切换4.下列只支持256种颜色的图形文件格式是()。

A. BMPB. JPGC. GIFD. PNG5.下列值最大的是()。

A. (58)10B. (111011)2C. (71)8D. (3A)166.Windows 7的“计算器”程序带有数值进制转换的是()。

A.标准型模式B.科学型模式C.程序员模式D.统计信息模式7.计算机病毒通常会附着在正常程序中,使用户不易察觉。

这反映计算机病毒具有()。

A.隐蔽性B.针对性C.破坏性D.传染性8.下列不是操作系统名称的是()。

A.Windows 7B.AppleC.AndroidD.Mac OS9.下列主文件名符合Windows 7命名规则的是()。

A.夏天:2017B.2017/夏天C.夏天<2017>D.夏天_201710.按住鼠标左键将C盘中的文件F1.TXT拖动到D盘后( )。

A.C盘和D盘均有文件F1.TXTB.C盘有F1.TXT文件但D盘没有C.D盘有F1.TXT文件但C盘没有D.C盘和D盘均没有F1.TXT文件11.关于邮件合并,下列说法正确的是()。

A.邮件合并的数据源可以是Excel表格B.若数据源中的数据有更新,则主文档中的数据域会立即自动更新C.邮件合并的结果在主文档中D.主文档中插入的合并域不能设置格式12.下列说法不正确的是()。

超大规模集成电路秋段成华老师第三次作业精编版

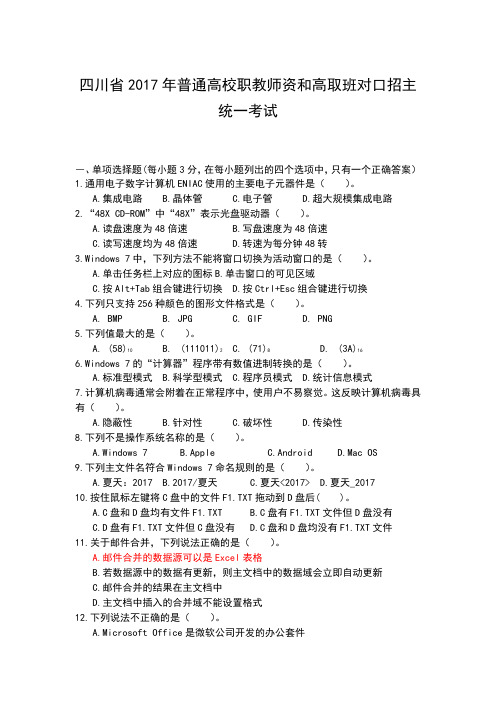

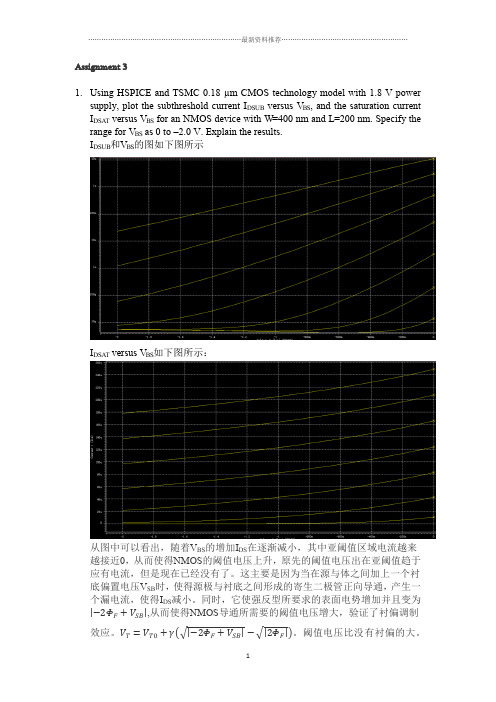

Assignment 3ing HSPICE and TSMC 0.18 µm CMOS technology model with 1.8 V powersupply, plot the subthreshold current I DSUB versus V BS, and the saturation currentI DSAT versus V BS for an NMOS device with W=400 nm and L=200 nm. Specify therange for V BS as 0 to –2.0 V. Explain the results.I DSUB和V BS的图如下图所示I DSAT versus V BS如下图所示:从图中可以看出,随着V BS的增加I DS在逐渐减小,其中亚阈值区域电流越来越接近0,从而使得NMOS的阈值电压上升,原先的阈值电压出在亚阈值趋于应有电流,但是现在已经没有了。

这主要是因为当在源与体之间加上一个衬底偏置电压V SB时,使得源极与衬底之间形成的寄生二极管正向导通,产生一个漏电流,使得I DS减小。

同时,它使强反型所要求的表面电势增加并且变为,从而使得NMOS导通所需要的阈值电压增大,验证了衬偏调制效应。

阈值电压比没有衬偏的大。

* SPICE INPUT FILE: problem.sp ID-VBS.param Supply=1.8 * Set value of Vdd.lib 'C:\synopsys\Hspice_A-2007.09\tsmc018\mm018.l' TT * Set 0.18um library .opt scale=0.1u * Set lambda*.model pch PMOS level=49 version=3.1*.model nch NMOS level=49 version=3.1mn Vdd gaten Gnd bn nch l=2 w=4 ad=20 pd=4 as=20 ps=4Vdd Vdd 0 'Supply'Vgsn gaten Gnd d cVbsn bn Gnd d c.dc Vbsn 0 -2 -0.05 Vgsn 0.6 1.8 0.2.print dc I1(mn).ending HSPICE and TSMC 0.18 um CMOS technology model with 1.8 V powersupply, plot log I DS versus V GS while varying V DS for an NMOS device withL=200 nm, W=800 nm and a PMOS with L=200 nm, W= 2 µm. Explain theresults.图中红线表示NMOS的I DS对V GS的曲线,从图中可以看出,随着V GS的增大I DS 的电流先为0,到后来逐渐增大,最后I DS对V GS的关系接近一个线性变化,且NMOS的导通电压约为0.43V,当V GS=0.43V的时候NMOS导通。

超大规模集成电路2017年秋段成华老师第四次作业

1.Shown below are buffer-chain designs.(1) Calculate the minimum delay of a chain of inverters for the overall effectivefan-out of 64/1.(2) Using HSPICE and TSMC um CMOS technology model with V powersupply, design a circuit simulation scheme to verify them with their correspondent parameters of N, f, and t p.N=3.6 ∴N=3.246(1)γ=1 F=64∴f=√F所以最佳反相器数目约为3通过仿真可以得到tphl= tplh= tp0=(2)N=1时,tphl= tplh= tpd=N=2时,tplh= tphl= tpd=N=3时,tphl= tplh= tpd=N=4时,tplh= tphl= tpd=从仿真结果可以看出N=3或者N=4时延迟时间最优,且N=2、3、4得到的仿真延迟时间与理论推导的时间比较接近,比例基本上是18、15、,而N=1时仿真得到的延迟时间远小于理论推导的时间,但是最优结果依旧是N=3,f=4,tp=15。

* SPICE INPUT FILE: chain of inverters.param Supply=.lib 'C:\synopsys\\tsmc018\' TT.option captab.option list node post measout.tran 10p 6000p************************************************************.param tdval=10p.meas tran tplh trig v(in) val= td=tdval rise=2+targ v(out) val= rise=2.meas tran tphl trig v(in) val= td=tdval fall=2+targ v(out) val= fall=2.meas tpd param='(tphl+tplh)/2'*macro definitions**************************************************************nmos1.subckt nmos1 n1 n2 n3mn n1 n2 n3 Gnd nch l= w= ad=^2 pd= as=^2 ps= .ends nmos1**pmos1*.subckt pmos1 p1 p2 p3mp p1 p2 p3 Vcc pch l= w= ad=^2 pd= as=^2 ps= .ends pmos1*.subckt inv1 in outxmn out in Gnd nmos1xmp out in Vcc pmos1vcc Vcc Gnd Supply.ends inv1**nmos2*.subckt nmos2 n1 n2 n3mn n1 n2 n3 Gnd nch l= w= ad=^2 pd= as=^2 ps= .ends nmos2**pmos2*.subckt pmos2 p1 p2 p3mp p1 p2 p3 Vcc pch l= w= ad=^2 pd= as=^2 ps= .ends pmos2*.subckt inv2 in outxmn out in Gnd nmos2xmp out in Vcc pmos2vcc Vcc Gnd Supply.ends inv2**nmos3*.subckt nmos3 n1 n2 n3mn n1 n2 n3 Gnd nch l= w= ad=^2 pd= as=^2 ps= .ends nmos3**pmos3.subckt pmos3 p1 p2 p3mp p1 p2 p3 Vcc pch l= w= ad=^2 pd= as=^2 ps=.ends pmos3*.subckt inv3 in outxmn out in Gnd nmos3xmp out in Vcc pmos3vcc Vcc Gnd Supply.ends inv3**nmos4*.subckt nmos4 n1 n2 n3mn n1 n2 n3 Gnd nch l= w= ad=^2 pd= as=^2 ps=.ends nmos4**pmos4*.subckt pmos4 p1 p2 p3mp p1 p2 p3 Vcc pch l= w= ad=^2 pd= as=^2 ps=.ends pmos4*.subckt inv4 in outxmn out in Gnd nmos4xmp out in Vcc pmos4vcc Vcc Gnd Supply.ends inv4*main circuit netlistxinv1 in out1 inv1xinv2 out1 out2 inv2xinv3 out2 out3 inv3xinv4 out3 out inv4cl out GndVin in Gnd pulse 219p 40p 40p 1100p 2400p).print tran v(in) v(out).end2.Consider the logic network below, which may represent the critical path of a morecomplex logic block. The output of the。

中国科学院大学 段成华 VLSI 超大规模集成电路 期末复习笔记(1到10章)

MOS 管 耗尽区电荷以及宽度

阈值电压的定义,饱和区线性区等阶段的电流

阈值电压:强反型发生时

饱和区: 与 Vgs-Vt 平方成正比

线性区:

ID

n

(VGS

VT

)VDS

VDS 2

2

Vds 较小时忽略平方项,就是线性关系

沟调效应

增加 Vds 会使漏结的耗尽区变大,缩小了有效沟道长度。 影响为:Vds 会增大 ID

Vdd Vdd 0 'Supply' VgspVdd gatep dc='Supply' Vgsngaten Gnd dc='Supply'

.dc Vgsp0 'Supply' 'Supply/20' .dc Vgsn0 'Supply' 'Supply/20'

.print dc I1(mp) .print dc I1(mn)

* Set TSMC 0.18um library

*.model pch PMOS level=49 version = 3.1 *.model nch NMOS level=49 version = 3.1

.options list node post measout * Option List: Prints a list of netlist elements, node connections, and values for components, voltage and current sources, parameters, and more. * Option Node: Prints a node cross-reference table. * Option Post: Saves simulation results for viewing by an interactive waveform viewer. * Option Measout: Outputs .MEASURE statement values and sweep parameters into an ASCII file.

超大规模集成电路秋段成华老师第三次作业

超大规模集成电路2017年秋段成华老师第三次作业work Information Technology Company.2020YEARAssignment 3ing HSPICE and TSMC 0.18 µm CMOS technology model with 1.8 V powersupply, plot the subthreshold current I DSUB versus V BS, and the saturation currentI DSAT versus V BS for an NMOS device with W=400 nm and L=200 nm. Specify therange for V BS as 0 to –2.0 V. Explain the results.I DSUB和V BS的图如下图所示I DSAT versus V BS如下图所示:从图中可以看出,随着V BS的增加I DS在逐渐减小,其中亚阈值区域电流越来越接近0,从而使得NMOS的阈值电压上升,原先的阈值电压出在亚阈值趋于应有电流,但是现在已经没有了。

这主要是因为当在源与体之间加上一个衬底偏置电压V SB时,使得源极与衬底之间形成的寄生二极管正向导通,产生一个漏电流,使得I DS减小。

同时,它使强反型所要求的表面电势增加并且变为|−2ΦF+V SB|,从而使得NMOS导通所需要的阈值电压增大,验证了衬偏调制效应。

V T=V T0+γ(√|−2ΦF+V SB|−√|2ΦF|)。

阈值电压比没有衬偏的大。

* SPICE INPUT FILE: problem.sp ID-VBS.param Supply=1.8 * Set value of Vdd.lib 'C:\synopsys\Hspice_A-2007.09\tsmc018\mm018.l' TT * Set 0.18umlibrary.opt scale=0.1u * Set lambda*.model pch PMOS level=49 version=3.1*.model nch NMOS level=49 version=3.1mn Vdd gaten Gnd bn nch l=2 w=4 ad=20 pd=4 as=20 ps=4Vdd Vdd 0 'Supply'Vgsn gaten Gnd dcVbsn bn Gnd dc.dc Vbsn 0 -2 -0.05 Vgsn 0.6 1.8 0.2.print dc I1(mn).ending HSPICE and TSMC 0.18 um CMOS technology model with 1.8 V powersupply, plot log I DS versus V GS while varying V DS for an NMOS device withL=200 nm, W=800 nm and a PMOS with L=200 nm, W= 2 µm. Explain the results.图中红线表示NMOS的I DS对V GS的曲线,从图中可以看出,随着V GS的增大I DS的电流先为0,到后来逐渐增大,最后I DS对V GS的关系接近一个线性变化,且NMOS的导通电压约为0.43V,当V GS=0.43V的时候NMOS导通。

超大规模集成电路第九次作业秋-段成华

超大规模集成电路第九次作业2016秋-段成华-CAL-FENGHAI.-(YICAI)-Company One1Assignment 91. Design an 8-bit up and down synchronous counter in VHDL with the following features:(1)The same ports are used for signals to be inputted andoutputted. The ports are bi-directionally buffered (three-state).(2)The counter is with an asynchronous reset that assigns aspecific initial value for counting.(3)The counter is with a synchronous data load control input fora new value of counting and an enable control input forallowing the up and down counting. The load control input hasa priority over the enable control input. This implies thatwhen the load operation is in process the counter operation is prohibited.(4)Some data types, such as STD_LOGIC, UNSIGNED, SIGNED andINTEGER, may be used.Synthesize the design. Create a set of reasonable input waveforms for your design and complete both behavioral and post-place&route simulations with internal signals and/or variables included in waveform or list windows.Solution:代码如下:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating---- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity count_8_bidir isPort (clk : in STD_LOGIC;rst : in STD_LOGIC;load : in STD_LOGIC;enable : in STD_LOGIC;cnt : inout STD_LOGIC_VECTOR (7 downto 0));end count_8_bidir;architecture Behavioral of count_8_bidir issignal cnt_in: STD_LOGIC_VECTOR (7 downto 0);signal cnt_out: STD_LOGIC_VECTOR (7 downto 0);beginpro0:process(oe,cnt_out,cnt)beginif(load='1')thencnt <= (others=>'Z');cnt_in <= cnt;elsecnt <= cnt_out;end if;end process;pro1:process(clk,rst)beginif(rst='1')thencnt_out <= (others=>'0');elsif rising_edge(clk)thenif(load='1')thencnt_out <= cnt_in;elsif(enable='1')thencnt_out <=cnt_out + 1;elsecnt_out <= cnt_out - 1;end if;end if;end process;end Behavioral;解释代码:这里有两个进程,进程0时是用来控制三态门控制的双向端口。

武汉理工大学《超大规模集成电路设计》考试习题及答案

15.什么是可测性设计?可测性设计包括哪些技术?可测试性包括哪些 重要方面? • 在尽可能少地增加附加引线脚和附加电路, 并使芯片性能损失最小的 情况下,满足电路可控制性和可观察性的要求 • 可测性设计技术:主要包括分块测试技术、扫描测试技术、特征量分 析分块测试技术、边界扫描分块测试技术等。 测试生成、测试验证和测试设计 16.目前 VLSI 系统设计普遍采用的方法是什么?它的基本思想什么?试 列举几种设计方法。 目前 VLSI 系统设计最流行的是自顶向下(Top-Down)的结构设计. 它的基 本思想是将一个复杂系统的功能分成可以独立的简单部分,然后将各部分 拼接起来,可完成整个系统的设计,实际上就是模块化的结构设计.根据不 同要求,现有许多方法,如:全定制设计方法、半定制设计方法、定制设计 方法、可编程设计方法等。 17.半定制设计方法可分为哪几种方法?它们各自的特点和不足之处是 什么? 半定制设计方法分为门阵列法和门海法 .门阵列方法的设计特点:设计周 期短,设计成本低,适合设计适当规模、中等性能、要求设计时间短、 数 量相对较少的电路 • 不足:设计灵活性较低;门利用率低;芯片面积浪费 ;速度较低;功 耗较大。 门海法具有门利用率较高、 集成密度较大、 布线灵活和保证布线布通率等 方面的优点,并能实现存储器这类电路。但它也有不足之处,一是它仍有 布线通道, 而且增加的布线通道只能是基本单元高度内所含通道数的整倍 数,这往往使增加的通道数超过实际的需要,造成面积浪费,另一是布线 通道下的晶体管不能再用来实现逻辑,因此门的利用率仍不很高。 18.试分析提高 MOS 管工作速度方法。 1. 提高 IC 加工精度 减小沟道长度. 2. 加强 MOS 管的驱动电压 (Vgs-Vt) , 可以减小管子的内阻,加快工作速 度。 3. 由于 µn ≈ 2.5µ p ,所以 NMOS 管的工作速度比 PMOS 管快得多。 可以用 NMOS 工艺代替 PMOS 工艺。 19.画出 19.画出 CMOS 反相器电压传输特性曲线图,并写出相应的电流方程。 反相器电压传输特性曲线图,并写出相应的

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.Shown below are buffer-chain designs.(1) Calculate the minimum delay of a chain of inverters for the overall effectivefan-out of 64/1.(2) Using HSPICE and TSMC 0.18 um CMOS technology model with 1.8 Vpower supply, design a circuit simulation scheme to verify them with their correspondent parameters of N, f, and t p.N=3.6 ∴N=3.246(1)γ=1 F=64∴f=√F所以最佳反相器数目约为3通过仿真可以得到tphl=1.3568E-11 tplh=1.7498E-11 tp0=1.5533E-11(2)N=1时,tphl= 5.2735E-10 tplh= 8.1605E-10 tpd= 6.7170E-10N=2时,tplh=2.2478E-10 tphl=2.5567E-10 tpd=2.4023E-10N=3时,tphl=2.0574E-10 tplh=2.1781E-10 tpd=2.1178E-10N=4时,tplh=2.1579E-10 tphl=2.2189E-10 tpd=2.1884E-10从仿真结果可以看出N=3或者N=4时延迟时间最优,且N=2、3、4得到的仿真延迟时间与理论推导的时间比较接近,比例基本上是18、15、15.3,而N=1时仿真得到的延迟时间远小于理论推导的时间,但是最优结果依旧是N=3,f=4,tp=15。

* SPICE INPUT FILE: Bsim3demo1.sp--a chain of inverters.param Supply=1.8.lib 'C:\synopsys\Hspice_A-2007.09\tsmc018\mm018.l' TT.option captab.option list node post measout.tran 10p 6000p************************************************************.param tdval=10p.meas tran tplh trig v(in) val=0.9 td=tdval rise=2+targ v(out) val=0.9 rise=2.meas tran tphl trig v(in) val=0.9 td=tdval fall=2+targ v(out) val=0.9 fall=2.meas tpd param='(tphl+tplh)/2'*macro definitions**************************************************************nmos1.subckt nmos1 n1 n2 n3mn n1 n2 n3 Gnd nch l=0.2u w=0.4u ad=0.2p^2 pd=0.4u as=0.2p^2 ps=0.4u.ends nmos1**pmos1*.subckt pmos1 p1 p2 p3mp p1 p2 p3 Vcc pch l=0.2u w=0.8u ad=0.4p^2 pd=0.8u as=0.4p^2 ps=0.8u.ends pmos1*.subckt inv1 in outxmn out in Gnd nmos1xmp out in Vcc pmos1vcc Vcc Gnd Supply.ends inv1**nmos2*.subckt nmos2 n1 n2 n3mn n1 n2 n3 Gnd nch l=0.2u w=1.12u ad=0.56p^2 pd=1.12u as=0.56p^2 ps=1.12u .ends nmos2**pmos2*.subckt pmos2 p1 p2 p3mp p1 p2 p3 Vcc pch l=0.2u w=2.24u ad=1.12p^2 pd=2.24u as=1.12p^2 ps=2.24u .ends pmos2*.subckt inv2 in outxmn out in Gnd nmos2xmp out in Vcc pmos2vcc Vcc Gnd Supply.ends inv2**nmos3*.subckt nmos3 n1 n2 n3mn n1 n2 n3 Gnd nch l=0.2u w=3.2u ad=1.6p^2 pd=3.2u as=1.6p^2 ps=3.2u.ends nmos3**pmos3.subckt pmos3 p1 p2 p3mp p1 p2 p3 Vcc pch l=0.2u w=6.4u ad=3.2p^2 pd=6.4u as=3.2p^2 ps=6.4u.ends pmos3*.subckt inv3 in outxmn out in Gnd nmos3xmp out in Vcc pmos3vcc Vcc Gnd Supply.ends inv3**nmos4*.subckt nmos4 n1 n2 n3mn n1 n2 n3 Gnd nch l=0.2u w=9.04u ad=4.52p^2 pd=9.04u as=4.52p^2 ps=9.04u.ends nmos4**pmos4*.subckt pmos4 p1 p2 p3mp p1 p2 p3 Vcc pch l=0.2u w=18.08u ad=9.04p^2 pd=18.08u as=9.04p^2 ps=18.08u .ends pmos4*.subckt inv4 in outxmn out in Gnd nmos4xmp out in Vcc pmos4vcc Vcc Gnd Supply.ends inv4*main circuit netlistxinv1 in out1 inv1xinv2 out1 out2 inv2xinv3 out2 out3 inv3xinv4 out3 out inv4cl out Gnd 154.24fVin in Gnd 0.9 pulse(0.0 1.8 219p 40p 40p 1100p 2400p).print tran v(in) v(out).end2.Consider the logic network below, which may represent the critical path of a morecomplex logic block. The output of the。

network is loaded with a capacitance which is 5 times larger than the input capacitance of the first gate, which is a minimum-sized inverter. The effective fanout of the path hence equals F = C L/Cg1= 5.Using HSPICE and TSMC 0.18 um CMOS technology model with 1.8 V power supply, design a circuit simulation scheme to verify(1) the OPTIMAZATIOM parameters of g, f, and s for each of the inverter and gates andThe path logical effort G=1∗53∗53∗1=259The total path effort H=GFB=259∗5∗1=1259The optimal gate effort h=H14⁄=(1259)⁄14⁄=1.93f1g1=f2g2=f3g3=f4g4=1.93g1=1 g2=53⁄ g3=53⁄ g4=1f1=1.93 f2=1.16 f3=1.16 f4=1.93s1=1 s2=1.16 s3=1.34 s4=2.6在所有的nmos和pmos均采用最小尺寸晶体管的情况下tplh=1.9047E-10 tphl=2.2742E-10 tpd=2.0895E-10在所有所有的mos管尺寸均是前一个mos管尺寸的2倍的情况下tplh=1.8353E-10 tphl=2.4356E-10 tpd=2.1355E-10在参数最优的情况下tplh= 1.7151E-10 tphl=2.2853E-10 tpd=2.0002E-10 所以最优参数为上面的推到过程。

* SPICE INPUT FILE: Bsim3demo1.sp--a chain of inverters.param Supply=1.8.lib 'C:\synopsys\Hspice_A-2007.09\tsmc018\mm018.l' TT.option captab.option list node post measout.tran 10p 6000p************************************************************ .param tdval=10p.meas tran tplh trig v(in) val=0.9 td=tdval rise=2+targ v(out) val=0.9 rise=2.meas tran tphl trig v(in) val=0.9 td=tdval fall=2+targ v(out) val=0.9 fall=2.meas tpd param='(tphl+tplh)/2'*macro definitions************************************************************ **nmos1.subckt nmos1 n1 n2 n3mn n1 n2 n3 Gnd nch l=0.2u w=0.4u ad=0.2p^2 pd=0.4u as=0.2p^2 ps=0.4u .ends nmos1**pmos1*.subckt pmos1 p1 p2 p3mp p1 p2 p3 Vcc pch l=0.2u w=0.8u ad=0.4p^2 pd=0.8u as=0.4p^2 ps=0.8u .ends pmos1*.subckt inv1 in outxmn out in Gnd nmos1xmp out in Vcc pmos1vcc Vcc Gnd Supply.ends inv1**nmos2*.subckt nmos2 n1 n2 n3 n4mn n1 n2 n3 n4 nch l=0.2u w=0.772u ad=0.386p^2 pd=0.772u as=0.386p^2 ps=0.772u.ends nmos2**pmos2*.subckt pmos2 p1 p2 p3 p4mp p1 p2 p3 p4 pch l=0.2u w=1.544u ad=0.772p^2 pd=1.544u as=0.772p^2 ps=1.544u.ends pmos2*.subckt nand in1 in2 in3 outxmn1 d1 in1 Gnd Gnd nmos2xmn2 d2 in2 d1 d1 nmos2xmn3 out in3 d2 d2 nmos2xmp1 out in1 Vcc Vcc pmos2xmp2 out in2 Vcc Vcc pmos2xmp3 out in3 Vcc Vcc pmos2vcc Vcc Gnd Supply.ends nand**nmos3.subckt nmos3 n1 n2 n3 n4mn n1 n2 n3 n4 nch l=0.2u w=0.9u ad=0.45p^2 pd=0.9u as=0.45p^2 ps=0.9u .ends nmos3**pmos3*.subckt pmos3 p1 p2 p3 p4mp p1 p2 p3 p4 pch l=0.2u w=1.79u ad=0.895p^2 pd=1.79u as=0.895p^2 ps=1.79u.ends pmos3*.subckt nor in1 in2 outxmn1 out in1 Gnd Gnd nmos3xmn2 out in2 Gnd Gnd nmos3xmp1 out in1 d1 d1 pmos3xmp2 d1 in2 Vcc Vcc pmos3vcc Vcc Gnd Supply.ends nor**nmos4*.subckt nmos4 n1 n2 n3mn n1 n2 n3 Gnd nch l=0.2u w=1.044u ad=0.522p^2 pd=1.044u as=0.522p^2 ps=1.044u.ends nmos4**pmos4*.subckt pmos4 p1 p2 p3mp p1 p2 p3 Vcc pch l=0.2u w=2.0764u ad=1.0382p^2 pd=2.0764u as=1.0382p^2 ps=2.0764u.ends pmos4*.subckt inv2 in outxmn out in Gnd nmos4xmp out in Vcc pmos4vcc Vcc Gnd Supply.ends inv2*main circuit netlistxinv1 in out1 inv1xnand out1 Vcc Vcc out2 nandxnor out2 Gnd out3 norxinv2 out3 out inv2cl out Gnd 12.05fvcc Vcc Gnd SupplyVin in Gnd 0.9 pulse(0.0 1.8 219p 40p 40p 1100p 2400p).print tran v(in) v(out).end(2) the minimum delay of the chain.在参数最优的情况下tplh= 1.7151E-10 tphl=2.2853E-10 tpd=2.0002E-10 3.Shown below is a level restore circuit of pass transistor.(1) Without trans3istor M r,4 verify by using HSPICE and TSMC 0.18 um CMOStechnology model with 1.8 V power supply that the high input to the signal- restoring inverter only charges up to V DD - V Tn.通过仿真,我们得到V(x)=1.38V,V Tn=0.445V,所以V x≈1.8V−0.445V≈V DD−V Tn,无法达到VDD的最大值1.8V。